(54) ШЛЬТА-МОДУЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1983 |

|

SU1129732A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Адаптивный дельта-модулятор со слоговым компандированием | 1991 |

|

SU1785078A1 |

| Дельта-модулятор | 1979 |

|

SU815907A1 |

| Дельта-кодер | 1984 |

|

SU1197087A1 |

| Устройство слежения за дорожкой дискового носителя информации | 1987 |

|

SU1614031A1 |

| УСТРОЙСТВО ДЛЯ ЗАРЯДКИ НАКОПИТЕЛЬНОГО КОНДЕНСАТОРА | 1989 |

|

RU2030098C1 |

| ЭЛЕКТРОННЫЙ ИЗМЕРИТЕЛЬ ЭЛЕКТРОЭНЕРГИИ | 1995 |

|

RU2097773C1 |

| Дельта-декодер | 1986 |

|

SU1392619A1 |

| Аналого-цифровой преобразователь | 2021 |

|

RU2760906C1 |

Изобретение относится к импульсной технике и может быть использовано для цифровой передачи сообщений,

Известен депьта-мояулятор, содержащий компаратор, первый вход которого соединен с шиной входного сигнала, второй вход соединен с выходом интегратора, а выход соединен с выходом регистра сдвига, эквивапентор и инвертор 11 .

Недостатком этого устройства является низкая точность.

Известно устройство, содержащее компаратор, первый вход которого соединен с шиной входного сигнала, второй вхой через двойной интегратор соединен с выходом перектожителя, а выход подключен ко входу регистра сдвига, синхронизирующий вход которого соединен с шиной тактового ситнала, а выходы всех разрядов соединены с соответствующими входами первого экыизалентора, первый вход nepeMHOKHTOiH соединен с шиисЛ выходного сигнала и с выходом первого разряда регистра сдвт-а, выход первого

ключа объединен с выходом: вт() ключа в через конденсатор соединен с общей шиной, вход второго ключа соединен через источник тока разряда с общей шиной, управляющий вход первого ключа соединен с выходом инвертора t23 .

Недостатком этого устройства также является его низкая точность.

Цель изобретения - повышение точности,

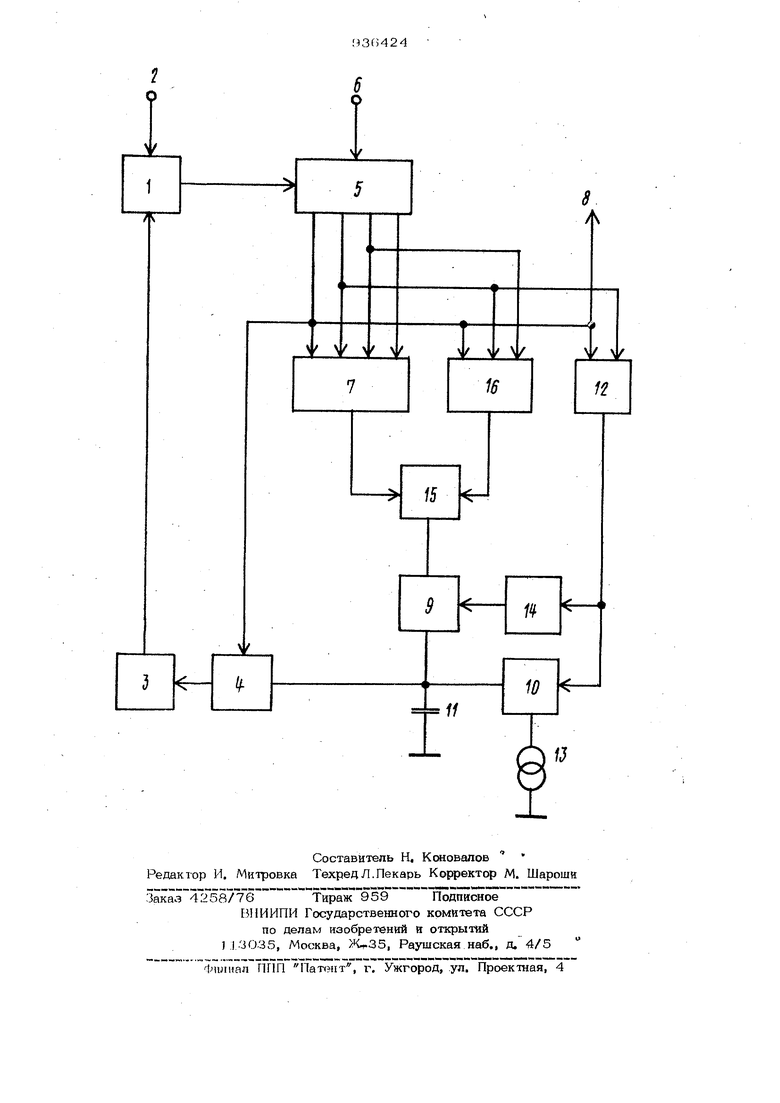

Поставленная цель достигается тем, что в дельта-модулятор, содержащий компаратор, первый вход которого соединен с шиной входного сигнала, второй вход через двойной интегратор соединен с выходом перемножитетш, а выход поАключен ко входу регистра сдвига, синхрон изиру16щий вход которого соединен с шиной тактов;ого сигнала, а выходы всех разрядов соединены с соответствующими первого эквивалентора, первый вход перемножителя соединен с шиной выходного сигнала и с выходом первого разряда регистра сдвига, выход первого ключа объетшен с выходом второго ключа и через кс 1Денсатор соединен с общей шийой, вход второго ключа схэединен через источник тока разряда с общей шиной, управляющ(тй вход первого ключа соединен с выходом инвертора, введены второй и третий эквиваленторы и управляемый источник тока, причем второй вход Перемножителя соединен с выходом первого ключа, вход которого соединен с выходом управляемого источника тока, первый вход которого соединен с выходом первого эквивалентора, а второй вхоа соединен с выходом второго эквивалентора, входы которого соединены соответст - (5 ных венно с выходами первого, второго и тре тьего разрядов регистра сдвига, выход третьего эквивалентора соединен со входами инвертора и второго ключа, входы третьего эквивалентора соединены соответственно с выходами первого и второго разрядов регистра сдвига. На чертеже представлена блок-схема дельта-модулятора. Дельта-модулятор содержит компарато 1, первый вход которого соединен с ш,ино 2 входного сигнала, второй вход через двойной интегратор 3 соединен с выходом перемножителя 4, а выход подключен ко входу регистра 5 сдвига, синхронизирующий вход которого соединен сОшиной. 6 тактового сигнала, а выходы всех раз- рядов соединены с - .сответствующими входами эквивалентора 7, Первый вход пере множителя 4 соединен с выходом первого разряда регистра 5 сдвига и с шиной 8 выходного сигнала, выход ключа 9 соединен с выходом ключа Ю, со вторым входом перемножителя 4 и через конденсатор 11 соединен с общей щиной, вход ключа Ю соединен с выходом эквивалентора 12, через источник 13 токи разряда с общей шиной и через инвертор 14 с управляющим входом ключа 9., вход которого соединен с выходом управляемого источника 15, первый вход которого соединен с выходом эквивалентора 7, а второй вход соединен с выходом эквивалентора 16, входы которого соеди}1ены соответственно с первым, вторым и третьим разрядами регистра 5, входы эквивалонтора 12 соединены с первым и вторым разрядами регистра 5 сдвига. Дельта-модулятор работает следующим образом. Входной аналоговый сигнал, подвергаемый цифровому преобразованию подается на шяну 2 на первый вход компаратора 1, на пюрой вход которого поступает оД93

мал, то частота появления четырех и трех следующих подряд символов одного знака на выходе дельта-модулятора неве44новременно аппроксимирующее напряжение, которое вьфабатывается интегратором 3 модулятора. Входной сигнал и аппроксимирующее faпpяжeниe сравниваются и сигнал ошибки квантуется по уровню компаратором .1, Квантованный сигнал ошибки пбступает на один вход регистра 5 сдвига, на синхронизирующий вход которого с щины б подается сигнал с тактовой частотой дискретизации. В регистре 5 сдвига накапливается четыре последних решения компаратора 1, с квивалентор 7 формирует сигнал с соответствующим логическим уровнем при наличии в выхолсигналах регистра 5 четырех симво- лов одного знака. Аналогично, эквивален- торы 16 и 12 формируют сигналы с соответствующими уровнями при наличии в выходных сигналах регистра 5 трех и двух символов одного знака соответственно. Сигналы с выходов эквиваленторов 7 и 16 поступают на соответствующие входы управляемого источника 15 тока со ступенчатой характеристикой. Последний может иметь три значения выходного тока i «ift , где 1X) - ток при отсутствии сигнала на выходах эквиваленторов 7 и 16, Ilj ток, при наличии сигнала на выходе эквивалентора 16, ij - ток, при наличии сигнала на выходе эквивалентора 7. Сигнал с выхода эквивалентора 12 поступает на управляющий вход ключа Ю и на вход инвертора 14, инвертированный сигнал с выхода последнего поступает на управл5пощий вход ключа 9. Интегрирующий конденсатор 11 через ключ 9 и 10 подсоединяется либо к выходу источника 15 тока со ступенчатой характеристикой при заряде, либо к источнику 13 тока разряда в зависимости от логического уровня на выходе эквивалентора 12. Напряжение с интегрирующего конденсатора 11 поступает на второй вход перемножителя 4, выходной ток которого пропорционален напряжению на интегрирующем конденсаторе 11, а затем выходного тока определяется логическим уровнем сигнала, с выхода первого разряда регистра 5 сдвига. Выходной ток пepe fflЬжйтeля 4 поступает на двойной интегратор 3, на котором формируется аппроксимирующее напряжение, непрерывно поступающее на вход компаратора 1. Если уровень входного сигнала

59

лика, поэтому на вькодах эквиваленторов 7 и 16 имеются такие потенциалы, что источник 15 тока генерирует ток { , линейно заряжая через ключ 9 интегрирующий конденсатор 11. Если амплитуда входного сигнала увеличивается, то увеличивается частота появления трех следующих подряд символов одного знака на выходе устройства, поэтому соотвв - атвующий потенциал с выхода эквиваленгора 16 устанавливаег источник 15 тока в такое состояние, что он генерирует ток in , а интегрирующий конденсатор 11 заряжается с большей скоростью, 4 обеспечивая тем самым большую скорост нарастания аппроксимирующего напряжения и возможность сложения без перегрузки за входным аналоговым сигналом. Аналоги шым образом, с дальнейшим ростом амплитуды входного сигнала происходит компандирование по четырем символам одного знака на выходе дельтамодулятора, при этом интегрирующий конденсатор 11 линейно заряжается током ij . Если на вход дельта-модутмтора сигнал подан со спектральными составляющими, лежащими в области верхней граничной частоты передаваемых сообщений, то компандирование осуществляется по двум и трем символам одного знака, при эток источник 15 тока со ступенчатой характеристикой генерирует ток, равный cl i +ctij ifj , где й и q - коэффициенты, зависящие от уровня спектрал1 ных составляющих входного сигнала. В общем случае ток заряда интегрирующего конденсатора 11 равен (-c( где q , С(п 1 ci - коэффициенты, зависящие от уровня и частоты входного сигнала, изменяющиеся таким образом гфи соответствующем подборе соотношения токов 1, 1о и ij, что закон ком пандирования повторяет с достаточной степенью точности перегрузочную характеристику дельта-модулятора, что позволяет улучшить точность дельта-модулятора.

246

Формула изобретения

Дельта модулятор, содержащий компаратор, первый вход которого соед|гаен с ш{шой входного сигнала, второй вход через двойной интегратор соединен с выходом перемножителя, а выход подключен к входу регистра сдвига, синхрониз фующнй вход которого соединен с шиной тактового сигнала, а выходы всех разрядов сое- с соответствующими входами первого эквивалентора, первый вход перемножителя соедвден с шиной выходного сигнала и с выходом первого разряда регистра сдвига, выход первого ключа объединен с выходом второго ключа и через конденсатор соединен с общей шиной, вход второго ключа соединен через источник тока разряда с общей шиной управляющий вход первого ключа соединен с выходом инвертора, отличающийся тем, что, с целью повышени точности, в него введены второй и третий эквиваленторы и управляемый источник тока, причем второй вход перемножителя соединен с выходом первого ключа, вход которого соединен с выходом управляемого источника тока, первый вход которого соединен с выходом первого эквивалентора, а второй вход соединен с выходом второго эквивалентора, входы которого соединены соответственно с выходами первого, второго и третьего ра рядов регистра сдвига, выход третьего эквивалентора соединен с входами инвертора и второго ключа, входы третьего эквивалентора соединены соответственно с выходами первого и второго разрядов регистра сдвига.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР № 752799, кл. Н 03 К 13/22,10.07.7

l.Proc.Dnt. lupicb Seminar Dicritae Commun xDicj HdC Trans miss and Swicli Nefworks -1913, Mew Jor4,№ 4, -1978, H. 3.2

, (прогогип).

Авторы

Даты

1982-06-15—Публикация

1980-10-31—Подача