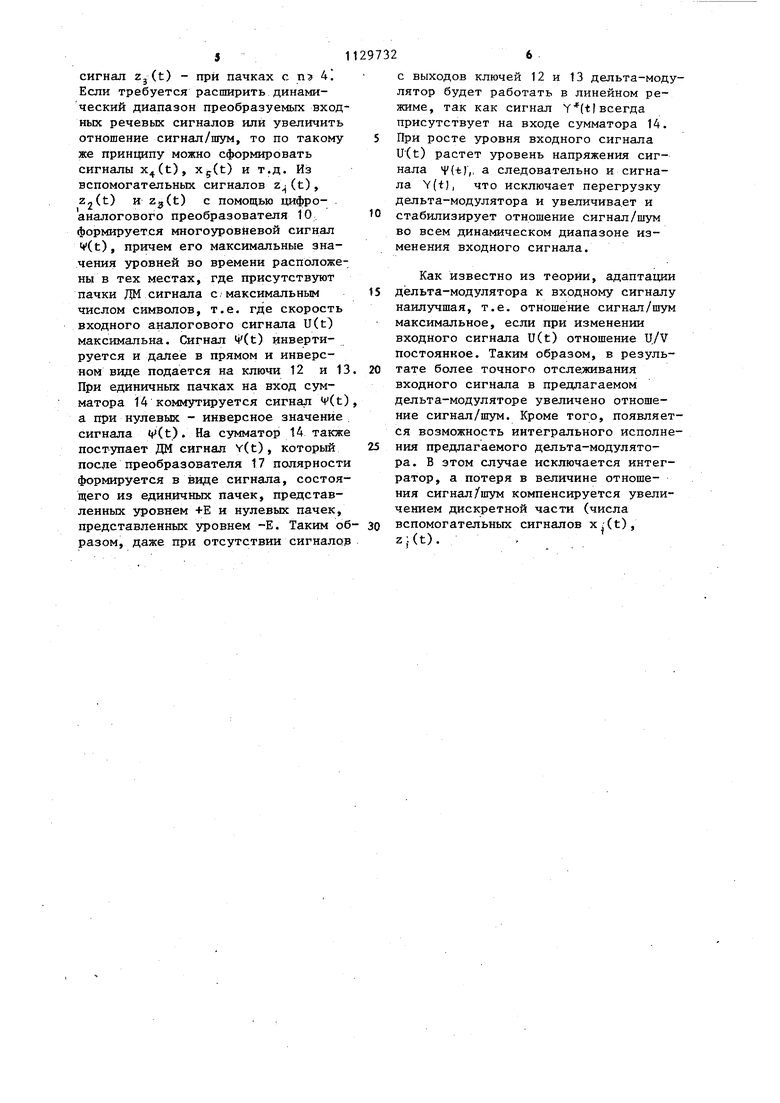

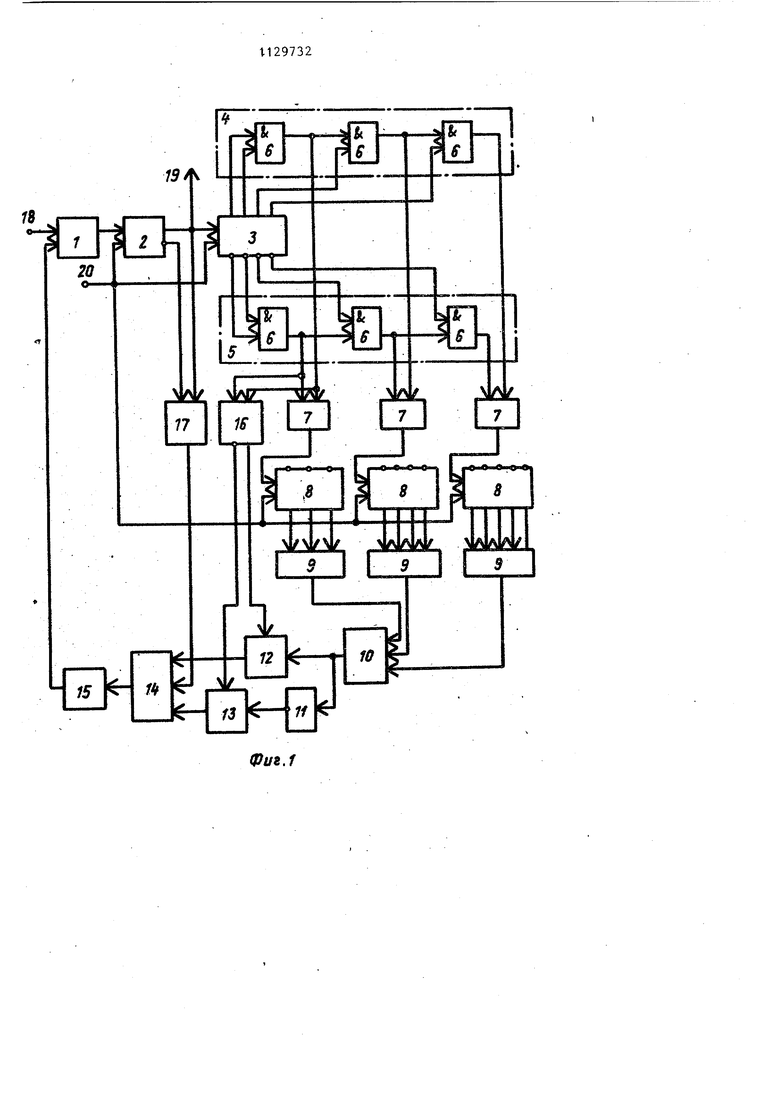

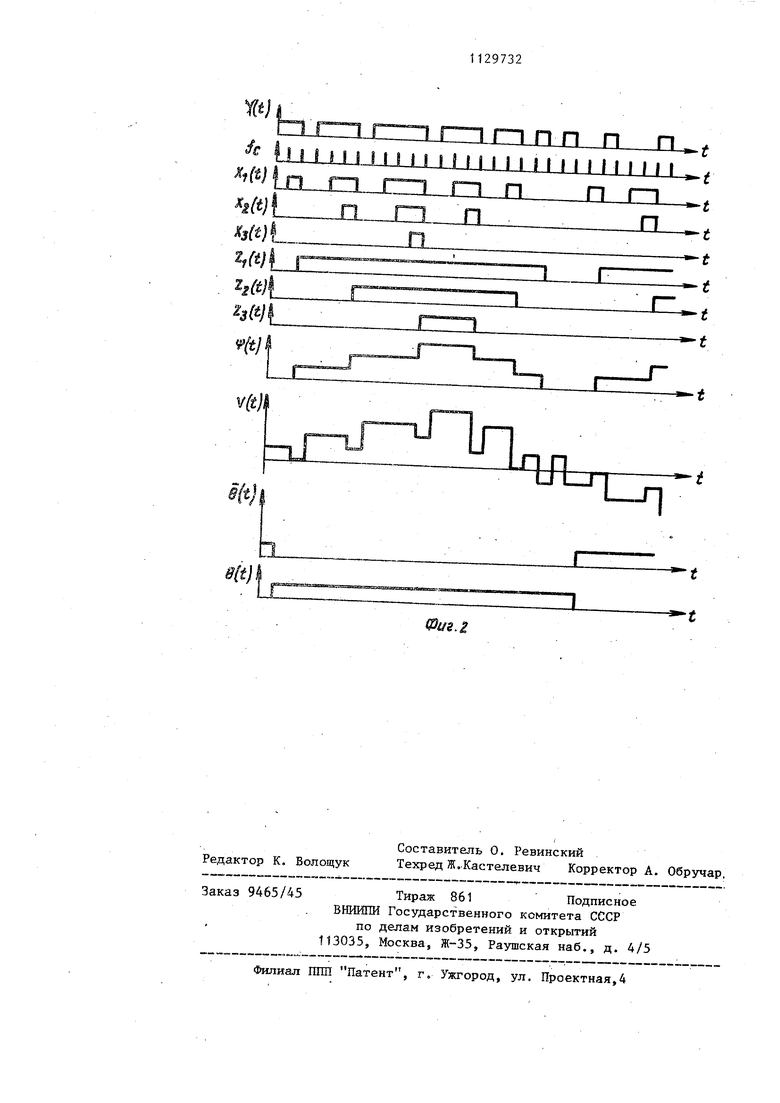

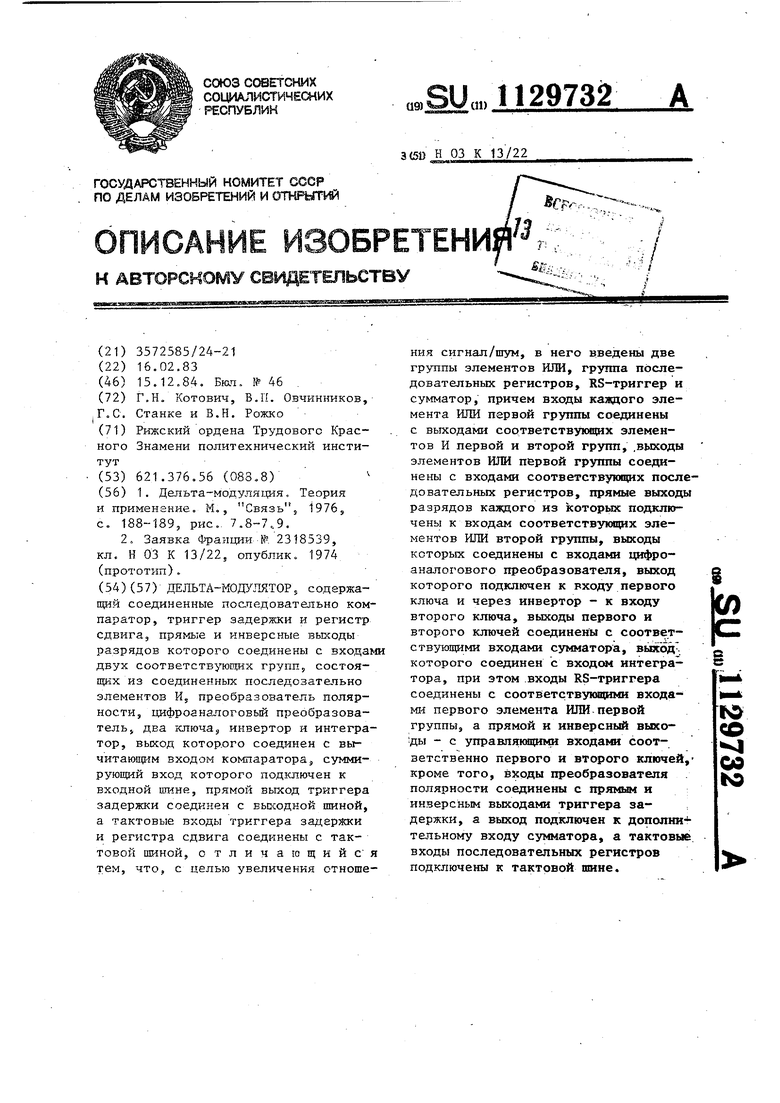

Изобретение относится к импульсн технике и может быть использовано в цифровых линиях передачи информации. Известен дельта-модулятор с инерционным компандированием, содер жащий соединенные последовательно компаратор формирователь импульсов и регистр сдвига, два элемента И, соединенные последовательно элемент ИЛИ, сглаживакнций фильтр, сумматор с постоянным смещением, ампли тудно-импульсный модулятор и интегратор TI JНедостатком этого дельта-модулятора является невысокое отношение сигнал/шум. Наиболее близким техническим решением к предлагаемому является дельта-модулятор, содержащий соединенные последовательно компаратор, триггер задержки и регистр сдвига, прямые и инверсные выходы разрядов которого соединены с входами двух соответствующих групп, состоящих яз соединенных последовательно элементов И, преобразователь полярност цифроаналоговьш преобразователь,два ключа, инвертор и интегратор,выход которого соединен с вычитающим входом компаратора, суммирующий вход .к торого подключен к входной шине, прямой выход триггера задержки соед нен с выходной шиной, а тактовые входы триггера задержки и регистра сдвига соединены с тактовой шиной, а также содержащий логическую схему состоящую из JK-триггеров, инверто ров и элементов И 2 . Недостатком известного устройств является также, невысокое отношение сигнал/шум. Цель изобретения увеличение отношения сигнал/шум. Указанная цель достигается тем, что в дельта-модулятор, содержащий соединенные последовательно компара тор, триггер задержки и регистр сдв га, прямые и инверсные выходы разря дов которого соединены с входами двух соответствующих групп, состоящих из соединенных последовательно элементов И, преобразователь полярности, цифроаналоговый преобра.зователь, два ключа, инвертор и интегратор, выход которого соединен с вычитающим входом компаратора, суммирукяций вход которого подключен 22 к входной шине, прямой выход триггера задержки соединен с выходной шиной, а тактовые входы триггера задержки и регистра сдвига соединены с тактовой шиной, введены две группы элементов ИЛИ, группа последовательных регистров, RS-триггер и сумматор, причем входы каждого элемента РШИ первой группы соединены с выходами соответствующих элементов И первой и второй групп, выходы элементов ИЛИ первой группы соединены с входами соответствующих последовательных регистров, прямые выходы разрядов каждого из которых подключены к входам соответствующих элементов ИЛИ второй группы, выходы которых соединены с входами дифроаналогового преобразователя, выход которого подключен к входу первого ключа и через инвертор - к входу второго ключа, выходы первого и второго ключей соединены с соотвегствующими входами сзтматора, выход которого соединен с входом интегратора, при этом входы RS-триггера соединены с соответствуюш;ими входами первого элемента ИЛИ первой группы, а прямой и инверсньй выходы - с управляющими входами соответс-г-венно первого и второго ключей, кроме того,входы преобразователя полярности соединены с прямым и инверсным выходами триггера задержки, а выход подключен к дополнительному входу сумматора, а тактовые входы последовательных регистров подключены к тактовой шине. На фиг.1 представлена блок-схема устройстваi на фиг.2 - временные диаграммы его работы. Устройство содержит компаратор 1, триггер 2 задержки, регистр 3 сдвига, первую и вторую группы 4 и двухвходовых элементов 6 И, первую группу элементов 7 ИЛИ, группу последовательных регистров 8, вторую группу элементов 9 ИЖ, цифроаналоговьй преобразователь 10, инвертор 11, первьй и второй ключи 12 и 13, сумматор 14, интегратор 15, RS-триггер 16, преобразователь 17 полярности, входную шину 18, выходную шину 19, тактовую шину 20. Выход компаратора 1 соединен с входом триггера 2 задержки, прямой выход которого подключен к входу регистра 3 сдвига и к выходной шине 19. Прямые выходы разрядов 3 регистра 3 подключены к входам первой группы 4, а инверсные выходы - к входам второй группы 5, каждая из этих групп состоит из сое диненных последовательно двухвходовых элементов 6 И. Выходы одинаковых по порядку элементов 6 обеих групп 4 и 5 соединены с входами соответствующих элементов 7 ИЛИ первой группы, выходы которых подключены к входам последовательных регистров 8. Выходы разрядов каждог регистра 8 соединены с входами соот ветствующего элемента 9 ИЛИ второй группы. Выходы элементов 9 ИЛИ подключены к входам цифроаналогового преобразователя 10, выход которого соединен с входагГ; инвертора 11 и первого ключа 12. Вход второго ключа 13 соединен с выходом инвертора 11. Выходы обоих ключей 12 и 13 сое динены с входами сумматора 14, к дополнительному входу которого подключен выход преобразовате: Я 17 полярности. Выход сумматора 14 соединен с входом интегратора 15, выход которого подключен к вычитающему входу компаратора 1, суммирзпощий вход которого соединен с входной шиной 18. Выходы триггера 2 задержки подключены к входам преобразователя 17 полярности. Входы RS-триггера 16 подключены к входам первого элемента 7 ИЛИ первой группы.Прямой и инверсный выходы RS-триггера 16 соединены с управляющими входами соответственно первого и второго ключей 12 и 13. Тактовая шина 20 соединена с тактовыми входами триггера 2 и регистров 3 и 8. Первьш последовательный регистр 8 имеет столько разрядов, сколько элементов 7 РИГИ содержится в первой группе, или на один разряд меньше, чем регистр. 3 сдвига.Каждый последующий регистр 8 имеет на один разряд больше, чем предьщущий. На фиг.2 обозначено: U(t) входной сигналу Yt - сигнал на выходной шине 19 дельта-модулятора fc - тактовые импульсы x(t)., XjCt), Xj(t) - укороченньй на один, два и три символа дельта-модулированный (дм) сигнал Y(t) на выходах элементов 7 ИЛИ; Z;,(t), ZjCt), Zj(t) - сигналы, сформированные из сигналов x(t), x.j(t), Xj(t) на выходах элементов 9 ИЛИ в тех случаях 324 когда в ДМ сигнале V(t) имеют место пачки единиц или нулей; (t) сигнал на выходе цифроаналогового преобразователя 10-, V(t) - сигнал управления шагом квантования на выходе сумматора.14; 0(t), &(t) сигналы управления с выходов RS-триггера 16, указывающие соответственно на возрастание или убьшание входного сигнала U(t), т.е. наличие единичных или нулевых пачек; Yf(t)сигнал на выходе преобразователя 17 полярности; U(t) - аппроксимирующее напряжение с выхода интегратора 15. Устройство работает следующим образом. Пусть на щине 18 имеется синусоидальный входной сигнал U(t). В результате сравнения в компараторе 1 входного U(t) и аппроксимирующего U(t) напряжений на выходе его вырабатывается единичный или нулевой уровень напряжения,который по приходу тактового импульса записывается в триггер 2 задержки и хранится в течение одного такта. Вследствие этого на выходе триг гера 2 задержки формируется ДМ сигнал Y(t). Г На фиг.1 изображен четырехразрядный регистр 3 сдвига. В зависимости от числа символов в пачках ДМ сигнала Y(t) на выходах элементов 6 И происходит укорочение пачек на 1, 2 и 3 символа, а также исключаются чередующиеся паузные комбинации типа 1,0, 1,0, характерные для режима холостого хода. Вследствие этого на выходах элементов 7 ИЛИ первой группы получаются сигналы x(t), ), XjCt) разной длительности и с разным, весом. Сигнал x.j(t) указьгоает на необходимость большего увеличения шага квантования, чем сигнал ), XjCt) - большего, чем x(t). Далее из сигналов x(t), Xj (t) , XgCt) формирукггся с помощью последовательных регистров 8 и элементов 9 ИЛИ второй группы вспомогательные сигналы управления шагом квантования z (t) , z(t), Zj (t) no такому закону: сигнал z(t) должен присутствовать на всех интервалах времени, пока в ДМ сигнала Y(t) присутствуют пачки с числом символов . Сигнал z.j(t) должен присутствовать на всех интервалах времени, пока в ДМ Y(t) присутствуют пачки с числом символов п / 3, 5 сигнал Zj(t) - при пачках с пэ 4. Если требуется расширить динамический диапазон преобразуемых входных речевых сигналов или увеличить отношение сигнал/шум, то по такому же принципу можно сформировать сигналы x(t), x(t) и т.д. Из вспомогательных сигналов z(t), ZjCt) и Zg(t) с помощью цифроаналогового преобразователя 10 формируется многоуровневой сигнал V(t), причем его максимальные значения зфовней во времени расположены в тех местах, где присутствуют пачки ДМ сигнала с максимальным числом символов, т.е. где скорость входного аналогового сигнала U(t) максимальна. Сигнал (.t) инвертируется и далее в прямом и инверсном виде подается на ключи 12 и 13 При единичных пачках на вход сумматора 14 коммутируется сигнал (t) а при нулевых - инверсное значение сигнала (t). На сумматор 14 также поступает ДМ сигнал Y(t), который после преобразователя 17 полярности формируется в виде сигнала, состоящего из единичных пачек, представленных уровнем +Е и нулевых пачек, представленных уровнем -Е. Таким об разом, даже при отсутствии сигналов 6 . с выходов ключей 12 и 13 дельта-модулятор будет работать в линейном режиме, так как сигнал Y(-t| всегда присутствует на входе сумматора 14. При росте уровня входного сигнала U(t) растет уровень напряжения сигнала {-fc),, а следовательно и сигнала V(t), что исключает перегрузку дельта-модулятора и увеличивает и стабилизирует отношение сигнал/шум во всем динамическом диапазоне изменения входного сигнала. Как известно из теории, адаптации дельта-модулятора к входному сигналу наилучшая, т.е. отношение сигнал/шум максимальное, если при изменении входного сигнала U(t) отношение U,/V постоянное. Таким образом, в результате более точного отслеживания входного сигнала в предлагаемом дельта-модуляторе увеличено отношение сигнал/шум. Кроме того, появляется возможность интегрального исполнения предлагаемого дельта-модулятора. В этом случае исключается интегратор, а потеря в величине отношения сигнал/шум компенсируется увеличением дискретной части (числа вспомогательных сигналов xKt), z;.(t).

/S

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1980 |

|

SU917339A1 |

| Дельта-модулятор | 1984 |

|

SU1203707A1 |

| Дельта-модулятор | 1978 |

|

SU752799A1 |

| Устройство для регистрации сейсмических сигналов | 1989 |

|

SU1681288A1 |

| Дельта-модулятор | 1983 |

|

SU1121777A2 |

| Система связи с асинхронной дельта-модуляцией | 1989 |

|

SU1624695A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Дельта-модулятор | 1984 |

|

SU1352654A1 |

| Устройство слежения за дорожкой дискового носителя информации | 1987 |

|

SU1614031A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

ДЕЛЬТА-МОдаФЛТОР5 содержащий соединенные пос-ледовательно компаратор, триггер задержки и регистр сдвига, прямые и инверсные выходы разрядов которого соединены с входами двух соответствующих групп, состоящих из соединенных последовательно элементов И, преобразователь полярности, цифроаналоговьй преобразователь два ключа инвертор и интегратор, выход котор.ого соединен с выгчитающим входом компаратора, суммирующий вход которого подключен к входной шине, прямой выход триггера задержки соединен с выходной шиной, а тактовые входы триггера задержки и регистра сдвига соединены с тактовой шиной, отличающий С я тем, что, с целью увеличения отношения сигнал/шум, в него введены две группы элементов ШШ, группа последовательных регистров, RS-триггер и сумматор, причем входы каждого элемента ИЖ первой группы соединены с выходами соответствукщих элементов И первой и второй групп, .выходы элементов ИЛИ первой группы соединены с входами соответствукицих последовательных регистров, прямые выходы разрядов калдого из которых подключены к входам соответствующих элементов ИЛИ второй группы, выходы которых соединены с входами цифроаналогового преобразователя, выход которого подключен к входу первого ключа и через инвертор - к входу второго ключа, выходы первого и второго ключей соединены с соответствующими входами су1 матора, вьвсод которого соединен с входом интегратора, при этом входы RS-триггера соединены с соответствукш1ими входами первого элемента ИЛИ первой ю со группы, а прямой и инверсный выходы - с управлякищпот входами соот ветственно первого и второго ключей,ОЭ кроме того, входы преобразователя ю полярности соединены с прямым и инверсным выходами триггера задержки, а выход подключен к дополнительному входу сумматора, а тактовые входы последовательных регистров подключены к тактовой шине.

w

1S

77

LXJ ГТП LZJ

/5

«

0US.l

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дельта-модулягщя | |||

| Теория и применение | |||

| М., Связь, 1976, Со 188-189, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| СПОСОБ ПОЛУЧЕНИЯ ДЕЗИНФИЦИРУЮЩЕ-МОЮЩЕГО СРЕДСТВА ДЛЯ ИЗДЕЛИЙ ИЗ ЧЕРНЫХ ТКАНЕЙ | 2006 |

|

RU2318539C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1984-12-15—Публикация

1983-02-16—Подача