(Б) УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования маршрутов сообщений и управления процессом коммутации в сети связи | 1980 |

|

SU922757A1 |

| Устройство для адресного управления коммутацией сообщений | 1977 |

|

SU708387A1 |

| Многоканальный коммутатор | 1981 |

|

SU963046A1 |

| Устройство для приема информации | 1982 |

|

SU1022204A1 |

| Система коммутации | 1985 |

|

SU1317449A1 |

| Многоканальный матричный коммутатор | 1981 |

|

SU964690A1 |

| Вычислительное устройство для формирования маршрута сообщения | 1982 |

|

SU1037269A1 |

| Многоканальное устройство для управления коммутацией сообщений | 1981 |

|

SU1012304A1 |

| Устройство для распределения потоков информации | 1979 |

|

SU881752A1 |

| Устройство для выбора адреса узла коммутации сообщений | 1980 |

|

SU935940A2 |

. . Изобретение относится к технике

связи и может найти применение при построении систем и сетей передачи дискретной информации, в которых реализованы игровые методы динамического децентрализованного управления коммутацией сообщений, позволяющие наиболее эффективно использовать емкости канального оборудования сетей связи.

Известно устройство для передачи информации по нескольким каналам, содержащее распределитель, накопитель и блок управления, выходы которого соединены с одним из входов элементов И, объединенных в группы в соответствии с направлением передачи, выход накопителя подключен к другим входам первых элементов И каждой группы, другие входы остальных элементов И каждой группы через первые элементы ИЛИ соединены с выходами распределителя, а выходы каждой группы элементов И через соответст,вующие вторые элементы ИЛИ соединены с входом канала соответствующего направления lЛ.

Известное устройство обладает недостатком, заключающимся в том, что не учитывается адрес назначения коммутируемого сообщения, а также тем, что при выборе направления не учитываются параметры, сети связи (структура, марштуры, время передами по каналам и т. д.), что увеличивает время доставки сообщения адресату.

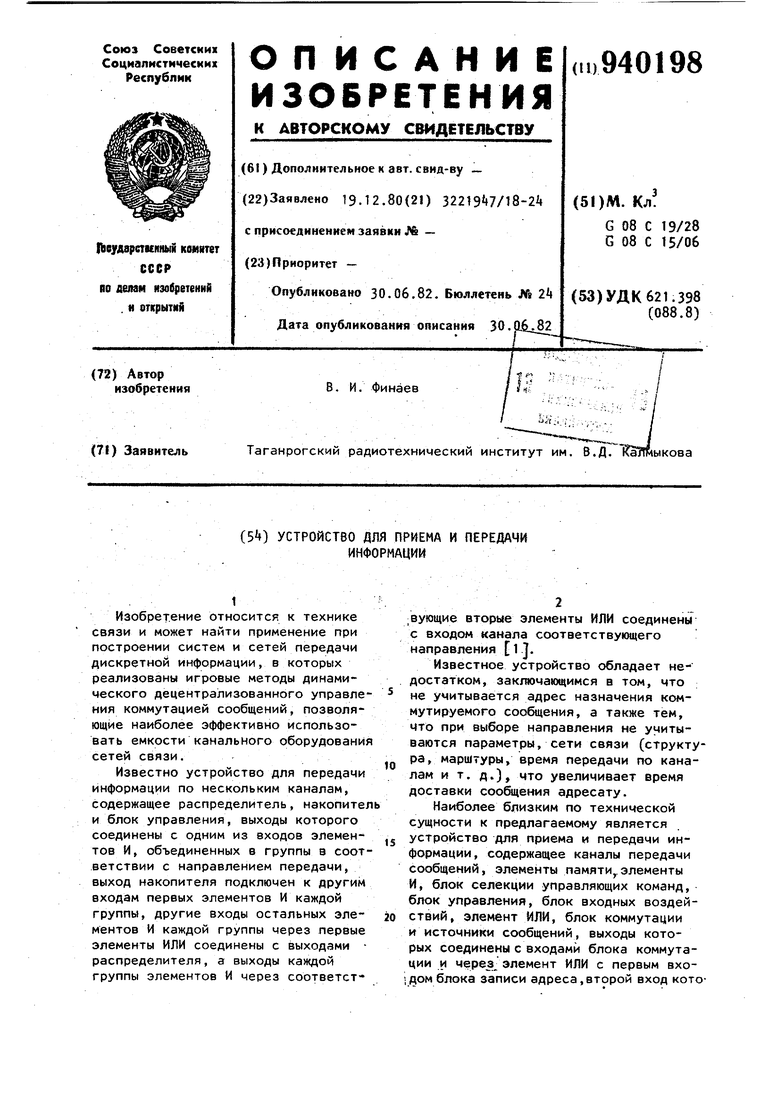

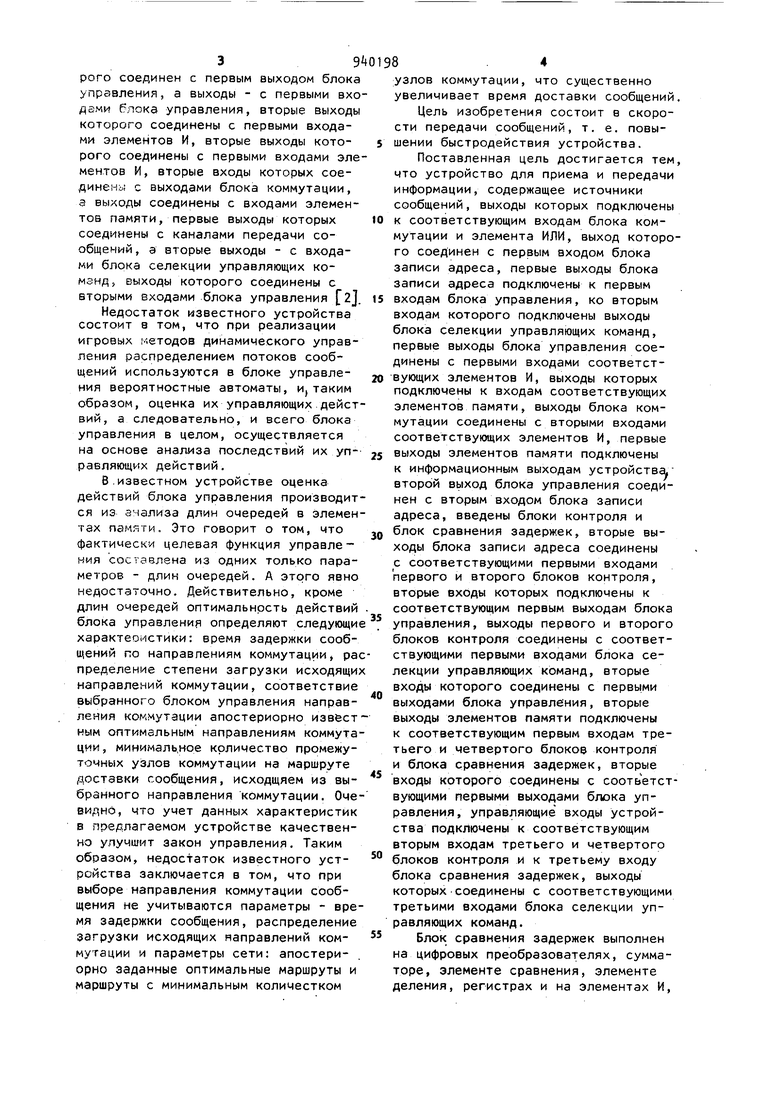

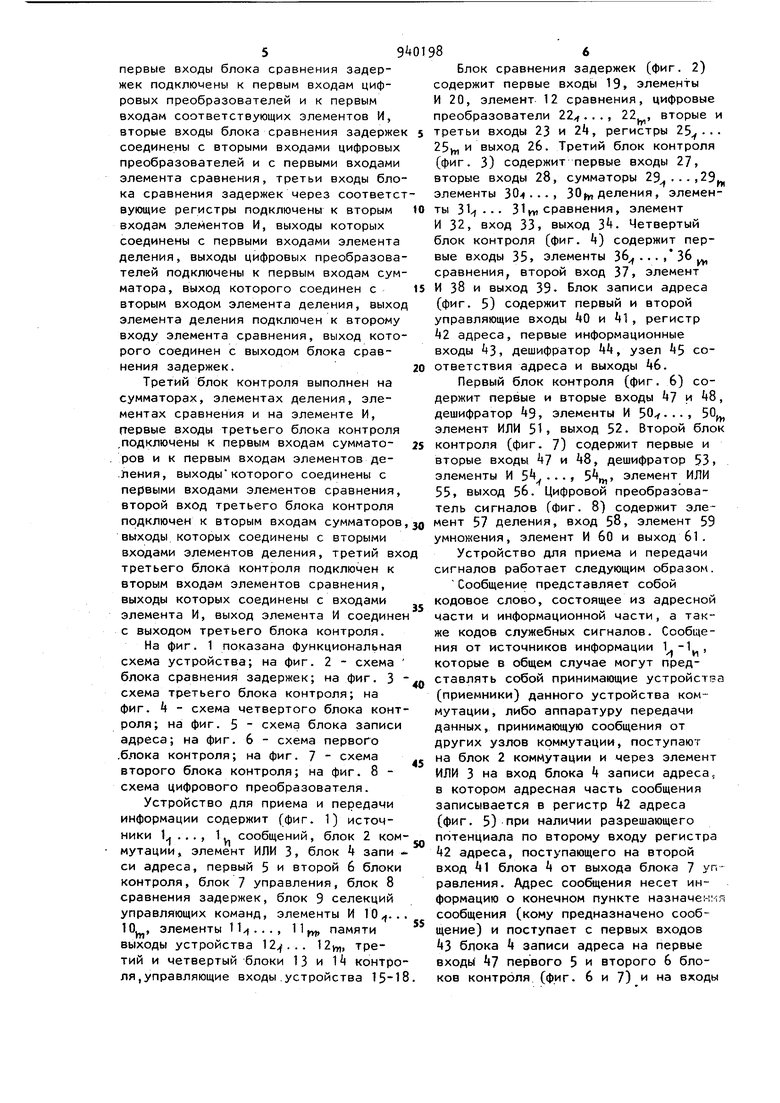

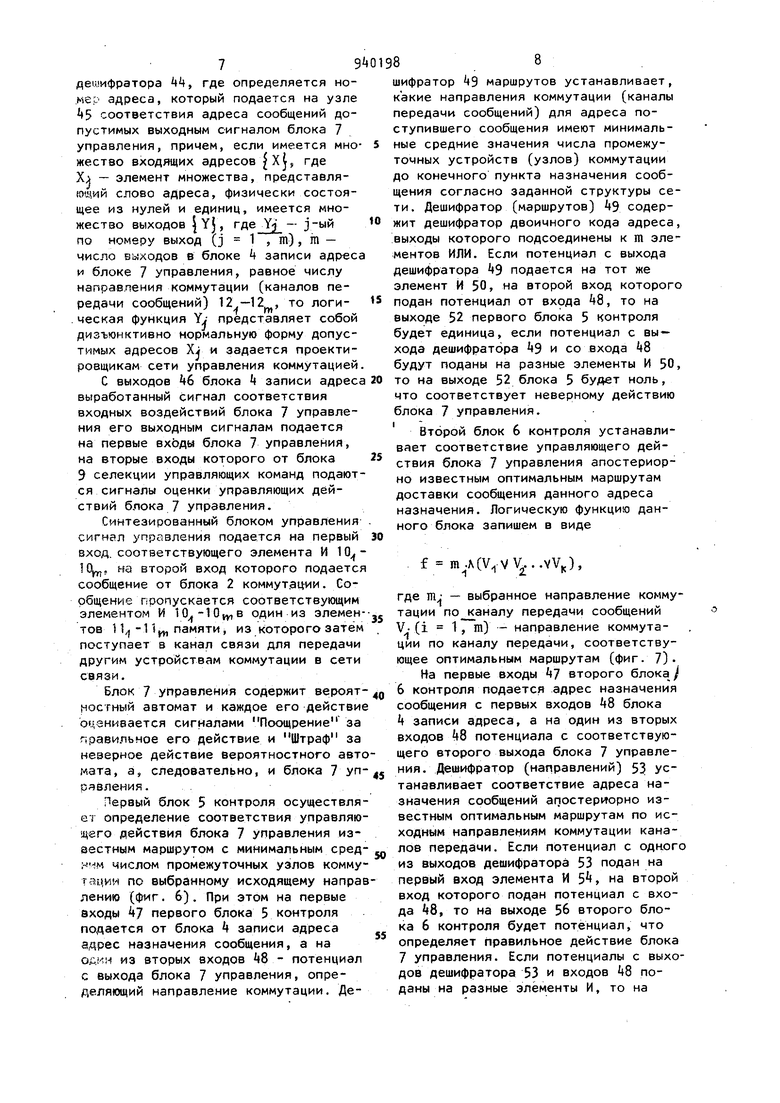

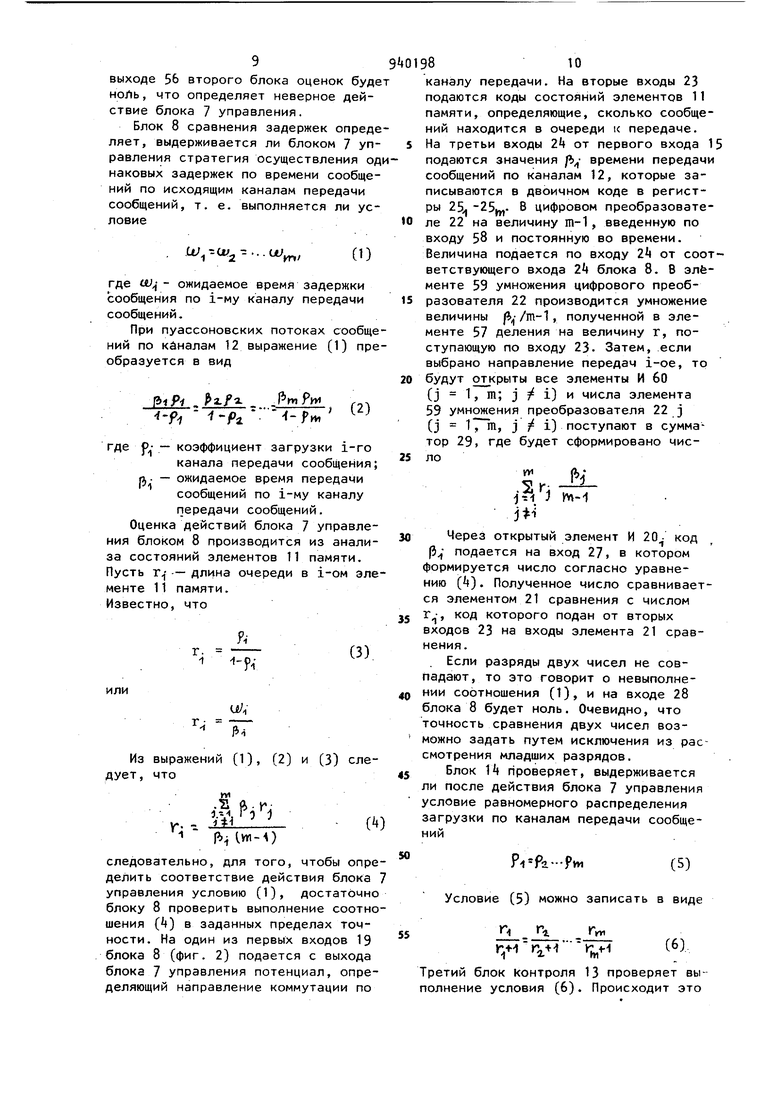

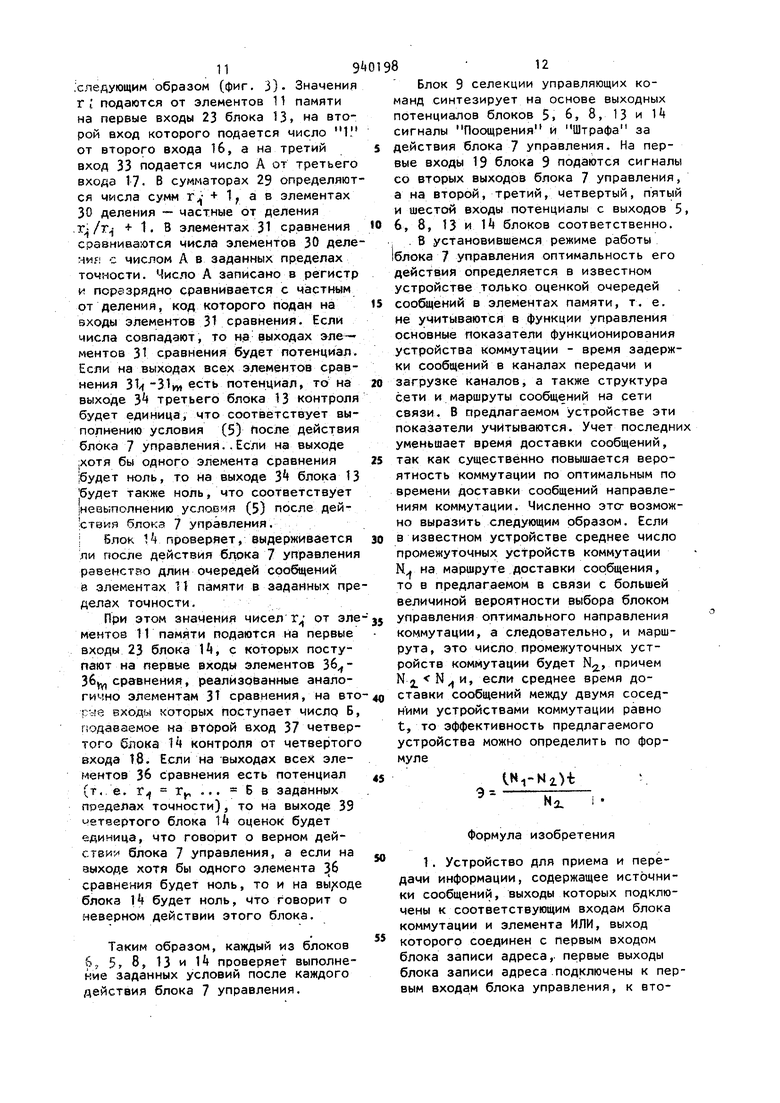

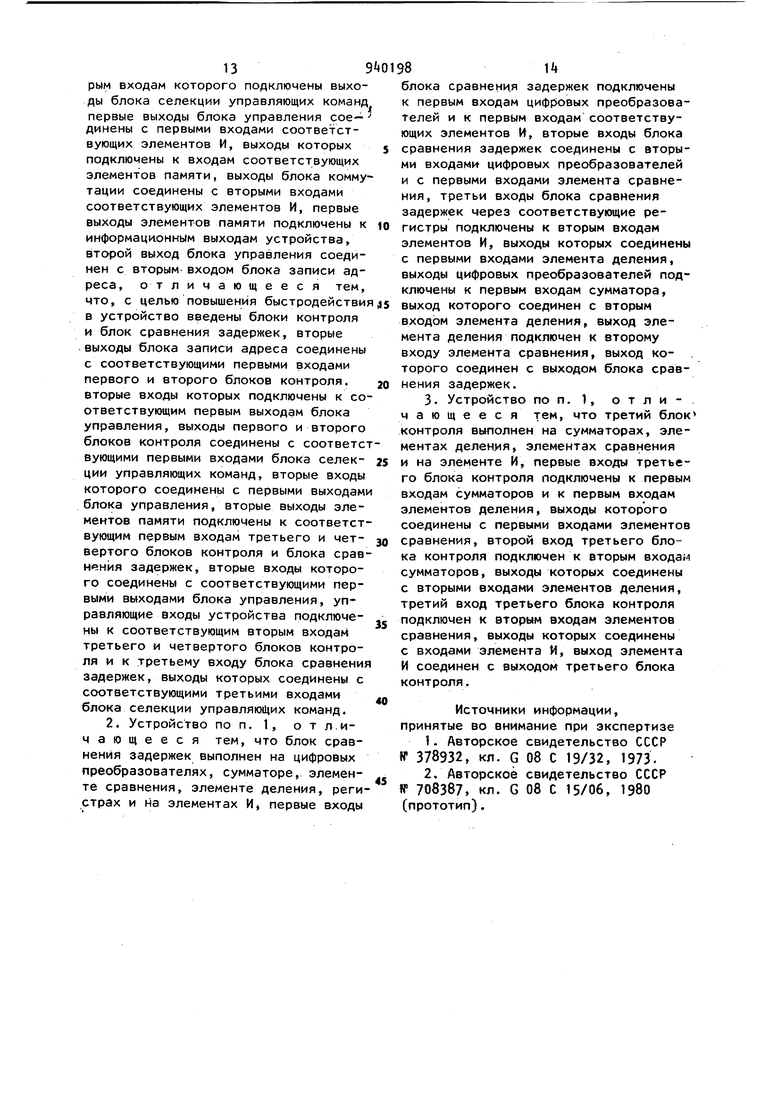

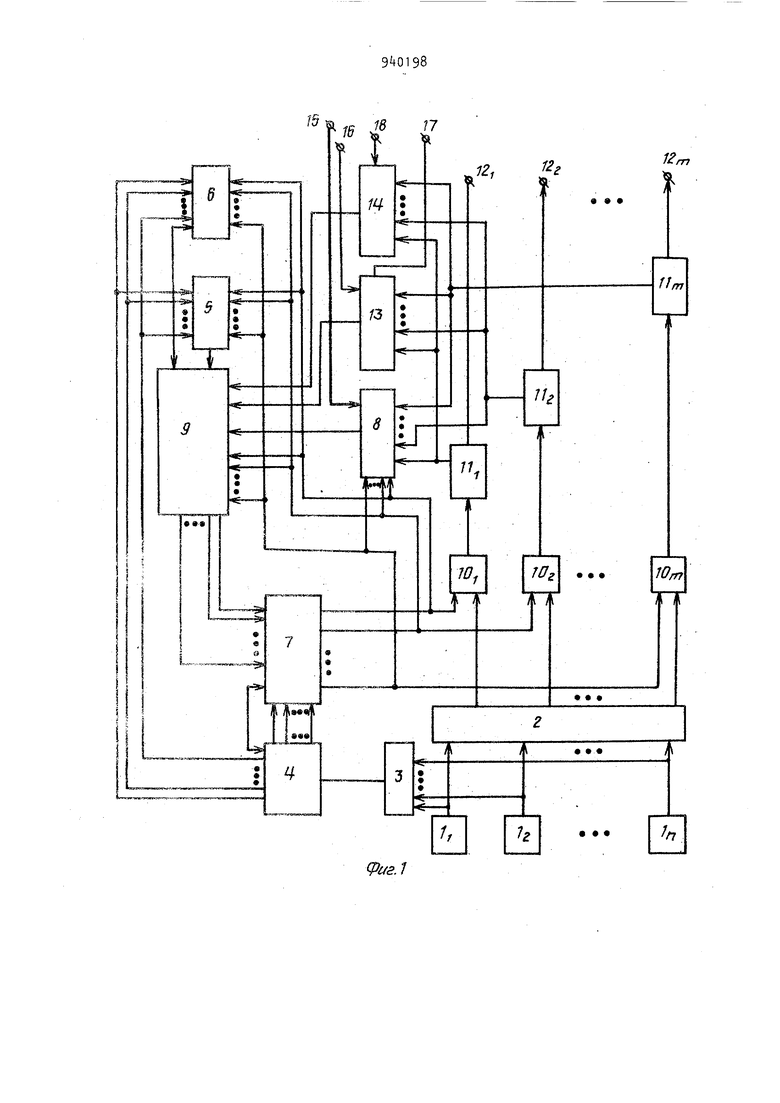

Наиболее близким по технической сущности к предлагаемому является устройство для приема и передачи информации , содержащее каналы передачи сообщений, элементы памяти,.элементы И, блок селекции управляющих команд, блок управления, блок входных воздействий, элемент ИЛИ, блок коммутации и источники сообщений, выходы которых соединены с входами блока коммутации и через элемент ИЛИ с первым входом блока записи адреса,второй вход которого соединен с первым выходом блока управления, а выходы - с первыми вхо дами блока управления, вторые выходы которого соединены с первыми входами элементов И, вторые выходы которого соединены с первыми входами эле ментов И, вторые входы которых соединены с выходами блока коммутации, а выходы соединены с входами элементов памяти, первые выходы которых соединены с каналами передачи сообщений, а вторые выходы - с входами блока селекции управляющих комзнд, выходы которого соединены с вторыми входами блока управления zj. Недостаток известного устройства состоит в том, что при реализации игровых методов динамического управления распределением потоков сообщений используются в блоке управлеНИЛ вероятностные автоматы, И|таким образом, оценка их управляющих дейст вий, а следовательно, и всего блока управления в целом, осуществляется на основе анализа последствий их управляющих действий. В.известном устройстве оценка действий блока управления производит ся из зчализа длин очередей в элемен тах памяти. Это говорит о том, что фактически целевая функция управления составлена из одних только параметров - длин очередей. А этого явно недостаточно. Действительно, кроме длин очередей оптимальность действий блока управления определяют следующи характеоистики: время задержки сообщений по направлениям коммутации, ра пределение степени загрузки исходящи направлений коммутации, соответствие выбранного блоком управления направления коммутации апостериорно извест ным оптимальным направлениям коммута ции, минималь,ное количество промежуточных узлов коммутации на маршруте доставки сообщения, исходщяем из выбранного направления коммутации. Оче видно, что учет данных характеристик в предлагаемом устройстве качественно улучшит закон управления. Таким образом, недостаток известного устройства заключается в том, что при выборе направления коммутации сообщения не учитываются параметры - вре мя задержки сообщения, распределение загрузки исходящих направлений коммутации и параметры сети: апостериорно заданные оптимальные маршруты и маршруты с минимальным количестком узлов коммутации, что существенно увеличивает время доставки сообщений. Цель изобретения состоит в скорости передачи сообщений, т. е. повышении быстродействия устройства. Поставленная цель достигается тем, что устройство для приема и передачи информации, содержащее источники сообщений, выходы которых подключены к соответствующим входам блока коммутации и элемента ИЛИ, выход которого соединен с первым входом блока записи адреса, первые выходы блока записи адреса подключены к первым входам блока управления, ко вторым входам которого подключены выходы блока селекции управляющих команд, первые выходы блока управления соединены с первыми входами соответствующих элементов И, выходы которых подключены к входам соответствующих элементов памяти, выходы блока коммутации соединены с вторыми входами соответствующих элементов И, первые выходы элементов памяти подключены к информационным выходам устройства второй выход блока управления соединен с вторым входом блока записи адреса, введены блоки контроля и блок сравнения задержек, вторые выходы блока записи адреса соединены с соответствующими первыми входами первого и второго блоков контроля, вторые входы которых подключены к соответствующим первым выходам блока управления, выходы первого и второго блоков контроля соединены с соответствующими первыми входами блока селекции управляющих команд, вторые входы которого соединены с первцми выходами блока управления, вторые выходы элементов памяти подключены к соответствующим первым входам третьего и четвертого блоков контроля и блока сравнения задержек, вторые входы которого соединены с соответствующими первыми выходами блока управления, управляющие входы устройства подключены к соответствующим вторым входам третьего и четвертого блоков контроля и к третьему входу блока сравнения задержек, выходы которых-соединены с соответствующими третьими входами блока селекции управляющих команд. Блок сравнения задержек выполнен на цифровых преобразователях, сумматоре, элементе сравнения, элементе деления, регистрах и на элементах И, 59 первые входы блока сравнения задержек подключены к первым входам цифровых преобразователей и к первым входам соответствующих элементов И, вторые входы блока сравнения задержек соединены с вторыми входами цифровых преобразователей и с первыми входами элемента сравнения, третьи входы блока сравнения задержек через соответст вующие регистры подключены к вторым входам элементов И, выходы которых соединены с первыми входами элемента деления, выходы цифровых преобразователей подключены к первый входам сумматора, выход которого соединен с вторым входом элемента деления, выход элемента деления подключен к второму входу элемента сравнения, выход которого соединен с выходом блока сравнения задержек. Третий блок контроля выполнен на сумматорах, элементах деления, элементах сравнения и на элементе И, первые входы третьего блока контроля .подключены к первым входам сумматоров и к первым входам элементов де.Ления, выходыкоторого соединены с первыми входами элементов сравнения, второй вход третьего блока контроля подключен к вторым входам сумматоров выходы которых соединены с вторыми входами элементов деления, третий вх третьего блока контроля подключен к вторым входам элементов сравнения, выходы которых соединены с входами элемента И, выход элемента И соединен с выходом третьего блока контроля. На фиг. 1 показана функциональная схема устройства; на фиг. 2 - схема блока сравнения задержек; на фиг. 3 схема третьего блока контроля; на фиг. 4 - схема четвертого блока конт роля; на фиг. 5 - схема блока записи адреса; на фиг. 6 - схема первого .блока контроля; на фиг. 7 - схема второго блока контроля; на фиг. 8 схема цифрового преобразователя. Устройство для приема и передачи информации содержит (фиг. 1) источНИКИ }...., . сообщений, блок 2 ком мутации, элемент ИЛИ 3, блок 4 запи си адреса, первый 5 и второй 6 блоки контроля, блок 7 управления, блок 8 сравнения задержек, блок 9 селекции управляющих команд, элементы И 10/j.. 10., элементы 11у..., 11 памяти выходы устройства 12.... 12уу„ третий и четвертый блоки 13 и 14 контро ля, управляющие входы .устройства 15-1 86 Блок сравнения задержек (фиг. 2) содержит первые входы 19, элементы И 20, элемент 12 сравнения, цифровые преобразователи 22..., 22, вторые и третьи входы 23 и 2k, регистры 25.. 25у„ И ВЫХОД 26. Третий блок контроля (фиг. 3) содержит первые входы 27, вторые входы 28, сумматоры 29..-,29 элементы 30..., 30, деления , элементы 31... сравнения, элемент И 32, вход 33, выход З. Четвертый блок контроля (фиг. ) содержит первые входы 35, элементы 3 . сравнения, второй вход 37, элемент И 38 и выход 39- Блок записи адреса (фиг. 5) содержит первый и второй управляющие входы 40 и Ц, регистр k2 адреса, первые информационные входы , дешифратор kk, узел 5 соответствия адреса и выходы 46. Первый блок контроля (фиг. 6) содержит первые и вторые входы 47 и 48, дешифратор 49, элементы И 50..., 50 элемент ИЛИ 51 выход 52, Второй блок контроля (фиг. 7) содержит первые и вторые входы 47 и 48, дешифратор 53, элементы И 54..., 54, элемент ИЛИ 55, выход 5б. Цифровой преобразователь сигналов (фиг. 8) содержит элемент 57 деления, вход 58, элемент 59 умножения, элемент И 60 и выход 61. Устройство для приема и передачи сигналов работает следующим образом. Сообщение представляет собой кодовое слово, состоящее из адресной части и информационной части, а также кодов служебных сигналов. Сообщения от источников информации L -1, , которые в общем случае могут представлять собой принимающие устройства (приемники) данного устройства коммутации, либо аппаратуру передачи данных, принимающую сообщения от других узлов коммутации, поступают на блок 2 коммутации и через элемент ИЛИ 3 на вход блока 4 записи адреса, в котором адресная часть сообщения записывается в регистр 42 адреса (фиг. 5) при наличии разрешающего потенциала по второму входу регистра 42адреса, поступающего на второй вход 41 блока 4 от выхода блока 7 управления. Адрес сообщения несет информацию о конечном пункте назначения сообщения (кому предназначено сообщение) и поступает с первых входов 43блока 4 записи адреса на первые входы 47 первого 5 и второго 6 блоков контроля (фиг. 6 и 7) и на входы дешифратора 4, где определяется но,мер адреса, который подается на узле i соответствия адреса сообщений допустимых выходным сигналом блока 7 управления, причем, если имеется множество входящих адресов Xjy где ХА - элемент множества, представлятадий слово адреса, физически состоящее из нулей и единиц, имеется множество выходов Yj, где Yj - j-ый по номеру выход (j 1 , m), га - число выходов в блоке записи адреса и блоке 7 управления, равное числу направления коммутации (каналов передачи сообщений) 12 -12 , то логи.ческая функция Y; представляет собой дизъюнктивно нормальную форму допустимых адресов Х и задается проектировщикам сети управления коммутацией. С выходов 6 блока Ц записи адреса выработанный сигнал соответствия входных воздействий блока 7 управления его выходным сигналам подается на первые входы блока 7 управления, на вторые входы которого от блока 9 селекции управляющих команд подаются сигналы оценки управляющих действий блока 7 управления. Синтезированный блоком управления сигнал управления подается на первый вход, соответствующего элемента И на второй вход которого подается сообщение от блока 2 коммут.. Сообщение пропускается соответствующим элементом И 10,,в один из элеменл л J - тов , памяти, из которого затем поступает в канал связи для передачи другим устройствам коммутации в сети связи. Блок 7 управления содержит вероятмостный автомат и каждое его действие оценивается сигналами Поощрение за правильное его действие и Штраф за неверное действие вероятностного авто мата, а, следовательно, и блока 7 упрявления... Первый блок 5 контроля осуществля ет определение соответствия управляющего действия блока 7 управления известным маршрутом с минимальным сред числом промежуточных узлов коммутации по выбранному исходящему направ лению (фиг. 6). При этом на первые аходы 47 первого блока 5 контроля подается от блока 4 записи адреса адрес назначения сообщения, а на САКИ из вторых входов 48 - потенциал с выхода блока 7 управления, определяющий направление коммутации. Дешифратор Э маршрутов устанавливает , какие направления коммутации (каналы передачи сообщений) для адреса поступившего сообщения имеют минимальные средние значения числа промежуточных устройств (узлов) коммутации до конечного пункта назначения сообщения согласно заданной структуры сети. Дешифратор (маршрутов) 9 содержит дешифратор двоичного кода адреса, выходы которого подсоединены к m эле ментов ИЛИ. Если потенциал с выхода дешифратора 49 подается на тот же элемент И 50 на второй вход которого подан потенциал от входа kS, то на выходе 52 первого блока 5 контроля будет единица, если потенциал с вы хода дешифратора 9 и со входа 48 будут поданы на разные элементы И 50, то на выходе 52 блока 5 будет ноль, что соответствует неверному действию блока 7 управления. Второй блок 6 контроля устанавливает соответствие управляющего действия блока 7 управления апостериорно известным оптимальным маршрутам доставки сообщения данного адреса назначения. Логическую функцию данного блока запишем в виде m.A(...vV), где т.- - выбранное направление коммуляЫтациипо каналу передачи сообщений - . . -4 V-(i 1, m) - направление коммутации по каналу передачи, соответствующее оптимальным маршрутам (фиг. 7). На первые входы kj второго блока 6 контроля подается адрес назначения сообщения с первых входов 48 блока 4 записи адреса, а на один из вторых входов 48 потенциала с соответствующего второго выхода блока 7 управления . Дешифратор (направлений) 53 устанавливает соответствие адреса назначения сообщений апостериорно известным оптимальным маршрутам по исходным направлениям коммутации каналов передачи. Если потенциал с одного из выходов дешифратора 53 подан на -го первый вход элемента И Sf, на второй вход которого подан потенциал с входа 48, то на выходе 56 второго блока 6 контроля будет потенциал, что определяет правильное действие блока 7 управления. Если потенциалы с выходов дешифратора 53 и входов 48 поданы на разные элементы И, то на 9 выходе 56 второго блока оценок буд ноль, что определяет неверное действие блока 7 управления. Блок 8 сравнения задержек опред ляет, выдерживается ли блоком 7 уп равления стратегия осуществления о наковых задержек по времени сообще ний по исходящим каналам передачи сообщений, т. е. выполняется ли ус ловие u;,--a/2 где UJ - ожидаемое время задержки сообщения по i-му каналу передачи сообщений. При пуассоновских потоках сообщ ний по кйналам 12 выражение (1) пр образуется в вид 2.fi. -r-f fi - -Рг где р- - коэффициент загрузки i-ro канала передачи сообщения ft - ожидаемое время передачи сообщений по i-му каналу передачи сообщений. Оценка действий блока 7 управле ния блоком 8 производится из анали за состояний элементов 11 памяти. Пусть -- длцна очереди в i-ом эл менте 11 памяти. Известно, что Y -- - jii (2) и (3) сле Из выражений (1), дует, что m i IWl-t)

следовательно, для того, чтобы определить соответствие действия блока 7 управления условию (1), достаточно блоку 8 проверить выполнение соотношения () в заданных пределах точности. На один из первых входов 19 блока 8 (фиг. 2) подается с выхода блока 7 управления потенциал, определяющий направление коммутации по

50

Pi Pa-Pw,

(5)

Условие (3) можно записать в виде г Гг

Ггч

(6)..

ч,

гн

П,И

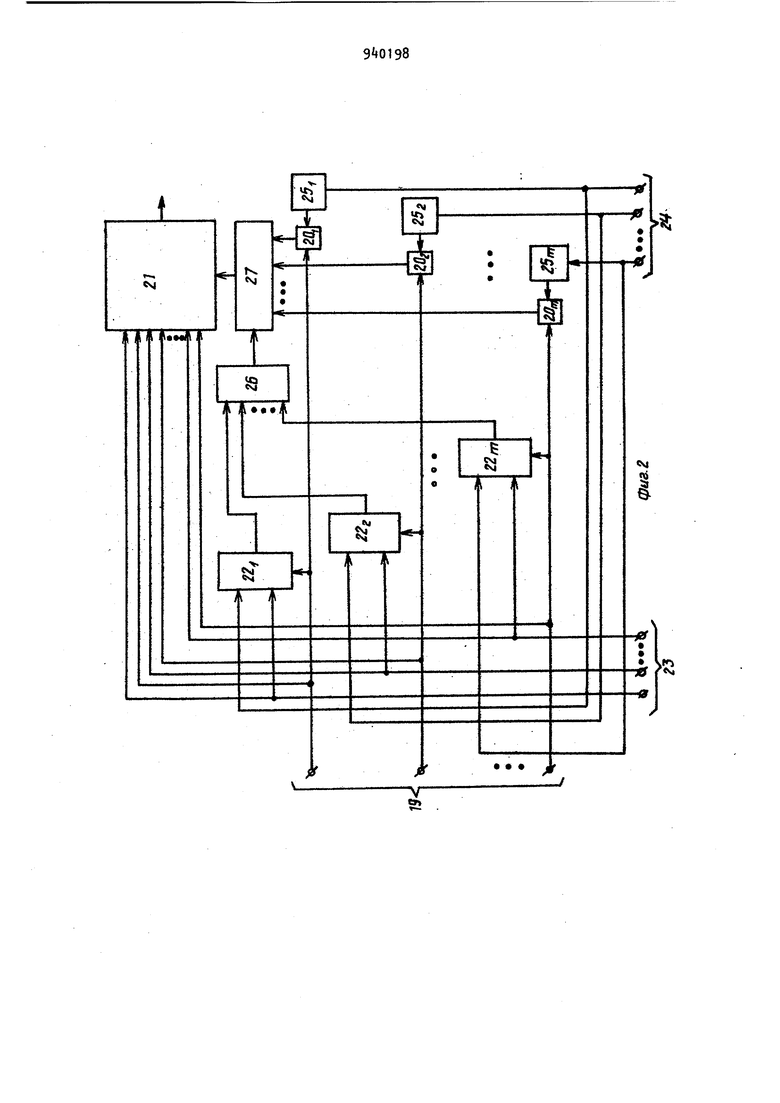

Третий блок контроля 13 проверяет выполнение условия (6). Происходит это 8 каналу передачи. На вторые входы 23 подаются коды состояний элементов 11 памяти, определяющие, сколько сообщений находится в очереди к передаче. На третьи входы 2 от первого входа 15 подаются значения времени передачи сообщений по каналам 12, которые записываются в двоичном коде в регистры 25 25. В цифровом преобразователе 22 на величину т-1, введенную по входу ЗЗ и постоянную во времени. Величина подается по входу 2 от соот ветствующего входа 2 блока 8. В элементе 59 умножения цифрового преобразователя 22 производится умножение величины ji -/m-1, полученной в элементе 57 деления на величину г, поступающую по входу 23. Затем, если выбрано направление передач i-oe, то будут открыты все элементы И 60 (J 1, т; j i) и числа элемента 59 умножения преобразователя 22 j (j 1, m, j j i) поступают в сумматор 29, где будет сформировано числоЧерез открытый элемент И код ( подается на вход 27, в котором формируется число согласно уравнению С). Полученное число сравнивается элементом 21 сравнения с числом , код которого подан от вторых входов 23 на входы элемента 21 сравнения. Если разряды двух чисел не совпадают, то это говорит о невыполнении соотношения (1), и на входе 28 блока 8 будет ноль. Очевидно, что точность сравнения двух чисел возможно задать путем исключения из рассмотрения младших разрядов. Блок Н проверяет, выдерживается ли после действия блока 7 управления условие равномерного распределения загрузки по каналам передачи сообщений

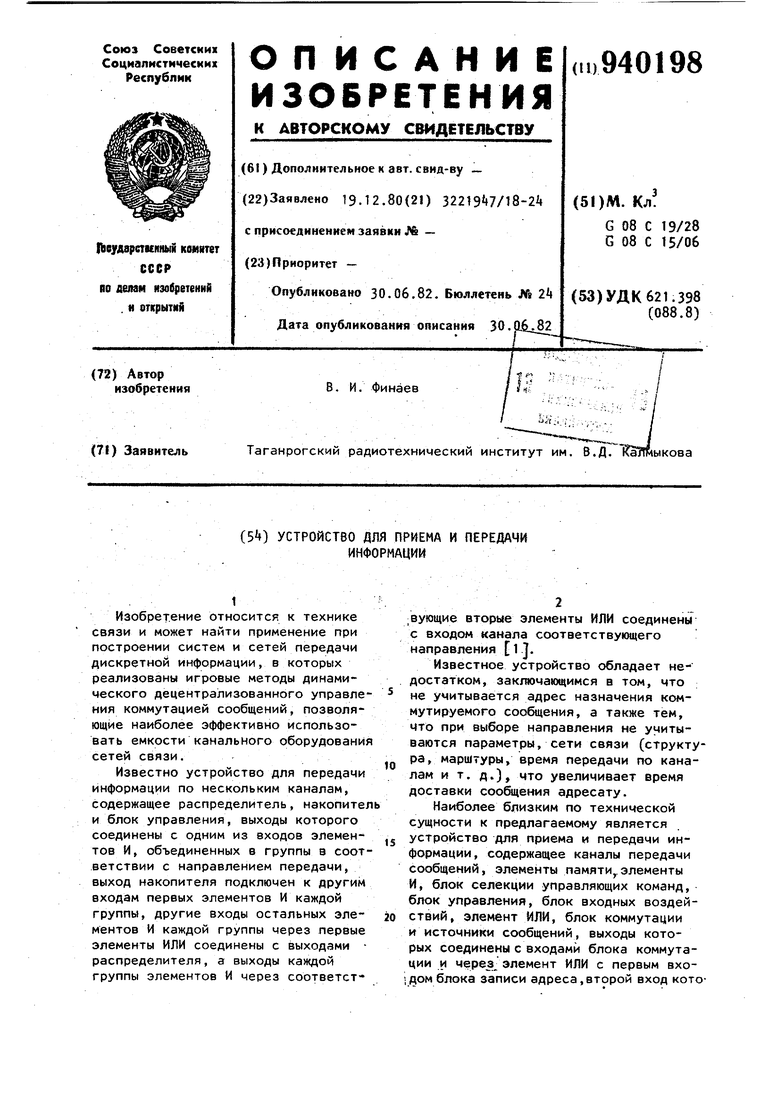

.следующим образом (фиг. 3)- Значения г I подаются от элементов 11 памяти на первые входы 23 блока 13, на второй вход которого подается число 1 от второго входа 16, а на третий вход 33 подается число А от третьего входа 17. В сумматорах 29 определяются числа сумм + 1, а в элементах 30 деления частные от деления . + 1. В элементах 31 сравнения сравниваются числа элементов 30 делени с числом А в заданных пределах точности. Число А записано в регистр и порезрядно сравнивается с частным от деления, код которого подан на входы элементов 31 сравнения. Если числа совпадают, то навыходах элементов 31 сравнения будет потенциал. Если на выходах всех элементов сравнения 31/f есть потенциал, то на выходе З третьего блока 13 контроля будет единица, что соответствует выполнению условия (5) Лосле действия блока 7 управления..Если на выходе ;хотя бы одного элемента сравнения ;будет ноль, то на выходе 3 блока 13 будет также ноль, что соответствует |невь полнению условия (5) после действия блока 7 управления. i блок 17- проверяет, выдерживается ли после действия блока 7 управления равенстзо длин очередей сообщений в элементах 1} памяти в заданных пределах точности.

при этом знамения чисел от элементое 11 памяти подаются на первые входы 23 блока И, с которых поступают на первые входы элементов , сравнения, реализованные аналогично элементам 31 сравнения, на вторуе входы которых поступает число Б, подаваемое на второй вход 37 четвертого блока 1ч контроля от четвертого входа t8. Если на выходах всех элементов 36 сравнения есть потенциал (т. е. г -Б в заданных пределах точности), то на выходе 39 четвертого блока lA оценок будет единица, что говорит о верном действиг блока 7 управления, а если на аыходе хотя бы одного элемента 6 сравнения будет ноль, то и на блока И будет ноль, что говорит о неверном действии этого блока.

Таким образом, каждый из блоков

6 5, 8, 13 и И проверяет выполнение заданных условий после каждого действия блока 7 управления.

Блок 9 селекции управляющих команд синтезирует на основе выходных потенциалов блоков 5, 6, 8, 13 и Tt сигналы Поощрения и Штрафа за действия блока 7 управления. На первые входы 19 блока 9 подаются сигналы со вторых выходов блока 7 управления, а на второй, третий, четвертый, пять1Й и шестой входы потенциалы с выходов 5,

6, 8, 13 и блоков соответственно.

. 8 установившемся режиме работы блока 7 управления оптимальность его действия определяется в известном устройстве только оценкой очередей

сообщений в элементах памяти, т. е. не учитываются в функции управления основные показатели функционирования устройства коммутации - время задержки сообщений в каналах передачи и

загрузке каналов, а также структура сети и маршруты сообщений на сети связи, В предлагаемом устройстве эти показатели учитываются. Учет последних уменьшает время доставки сообщений,

так как существенно повышается вероятность коммутации по оптимальным по времени доставки сообщений направлениям коммутации. Численно это- возможно выразить следующим образом. Если

в известном устройстве среднее число промежуточных устройств коммутации N на маршруте доставки сообщения, то в предлагаемом в связи с большей величиной вероятности выбора блоком

управления оптимального направления коммутации, а следовательно, и маршрута, это число промежуточных устройств коммутации будет N, причем N 2 N и, если среднее время доставки сообщений между двумя соседними устройствами коммутации равно t, то эффективность предлагаемого устройства можно определить по формуле

iHi-Na:)i Na, iФормула изобретения

которого соединен с Первым входом блока записи адреса, первые выходы блока записи адреса подключены к первым входам блока управления, к вторым входам которого подключены выходы блока селекции управляющих команд первые выходы блока управления сое- динены с первыми входами соответствующих элементов И, выходы которых подключены к входам соответствующих элементов памяти, выходы блока комму тации соединены с вторыми входами соответствующих элементов И, первые выходы элементов памяти подключены к информационным выходам устройства, второй выход блока управления соединен с вторым входом блока записи адреса, отличающееся тем, что, с целью повышения быстродействи в устройство введены блоки контроля и блок сравнения задержек, вторые выходы блока записи адреса соединены с соответствующими первыми входами первого и второго блоков контроля. вторые входы которых подключены к со ответствующим первым выходам блока управления, выходы первого и второго блоков контроля соединены с соответс вующими первыми входами блока селекции управляющих команд, вторые входы которого соединены с первыми выходам блока управления, вторые выходы элементов памяти подключены к соответст вующим первым входам третьего и четвертого блоков контроля и блока срав нения задержек, вторые входы которого соединены с соответствующими первыми выходами блока управления, управляющие входы устройства подключены к соответствующим вторым входам третьего и четвертого блоков контроля и к третьему входу блока сравнени задержек, выходы которых соединены с соответствующими третьими входами блока селекции управляю1Цих команд. 2. Устройство по п. 1, отличающееся тем, что блок сравнения задержек выполнен на цифровых преобразователях, сумматоре, элементе сравнения, элементе деления, реги страх и на элементах И, первые входы блока сравнения задержек подключены к первым входам цифровых преобразователей и к первым входам соответствующих элементов И, вторые входы блока сравнения задержек соединены с вторыми входами цифровых преобразователей и с первыми входами элемента сравнения, третьи входы блока сравнения задержек через соответствующие регистры подключены к вторым входам элементов И, выходы которых соединены с первыми входами элемента деления, выходы цифровых преобразователей подключены к первым входам сумматора, выход которого соединен с вторым входом элемента деления, выход элемента деления подключен к второму входу элемента сравнения, выход которого соединен с выходом блока сравнения задержек. 3. Устройство по п. 1, отличающееся тем, что третий блок контроля выполнен на сумматорах, элементах деления, элементах сравнения и на элементе И, первые входы третьего блока контроля подключены к первым входам сумматоров и к первым входам элементов деления, выходы которого соединены с первыми входами элементов сравнения, второй вход третьего блока контроля подключен к вторым входам сумматоров, выходы которых соединены с вторыми входами элементов деления, третий вход третьего блока контроля подключен к вторым входам элементов сравнения, выходы которых соединены с входами элемента И, выход элемента И соединен с выходом третьего блока контроля. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР V 378932, кл. G 08 С 19/32, 19732.Авторское свидетельство СССР fP 708387, кл. G 08 С 15/06, 1980 (прототип).

фиг. 5

7ч

Sff

Я

Авторы

Даты

1982-06-30—Публикация

1980-12-19—Подача