(54) УСТРСЙСТВО СЖАТИЯ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Устройство для обработки термограмм паронагнетательных скважин | 1989 |

|

SU1745913A1 |

| Устройство для сжатия последователь-НОСТи СигНАлОВ | 1979 |

|

SU842911A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для вычисления тео-РЕТичЕСКОгО BECA издЕлий | 1979 |

|

SU798871A1 |

| Устройство для передачи телеметрической информации | 1985 |

|

SU1262553A1 |

| Устройство для анализа потоков случайных чисел | 1990 |

|

SU1775724A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для контроля качества проводного монтажа | 1983 |

|

SU1108466A1 |

1

Изобретение относится к вычисгштепьной технике и может быть испопьзовано в телеметрических системах, в частности в системах сбора и обработки информации о научном- эксперименте дпя уменьшения объема информации при отсутствии априорных сведений о возможных фпуктуациях исспедуемого процесса.

По основному авт. св. № 842911 известно устройство дпя сжатия поспедоватепьности сигналов, содержашее компаратор, один из входов которого подключен к выходу интерполятора, а выход - ко входу аналого-цифрового преобразователя, выход которого подключен к выхо- 15 ду интерпопятора, и кодер длинных серий, дешифратор, вход которого подключен к выходу аналого-цифрового преобразователя и выходы подключены к счетным входам счетчиков и первым входам пер- 20 вой группы элементов И, к вторым входам которой подключен выход первого управпяюшего ключа, объединенный с синхронизирующим входом кодера длинных

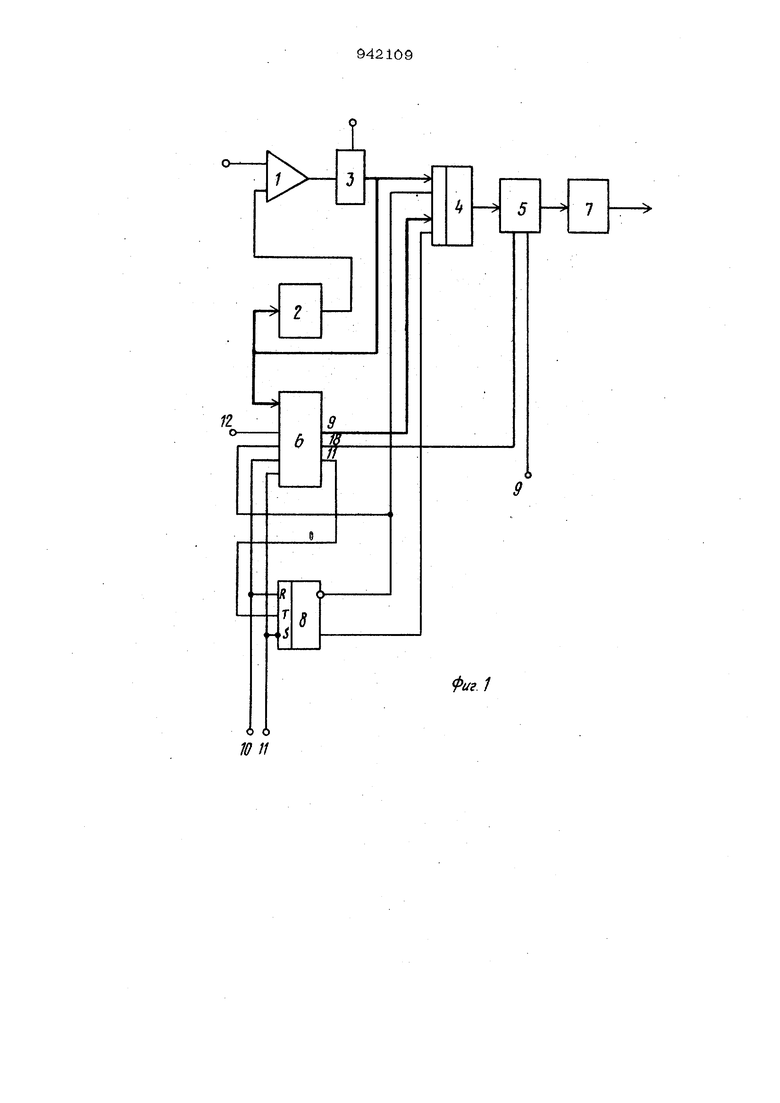

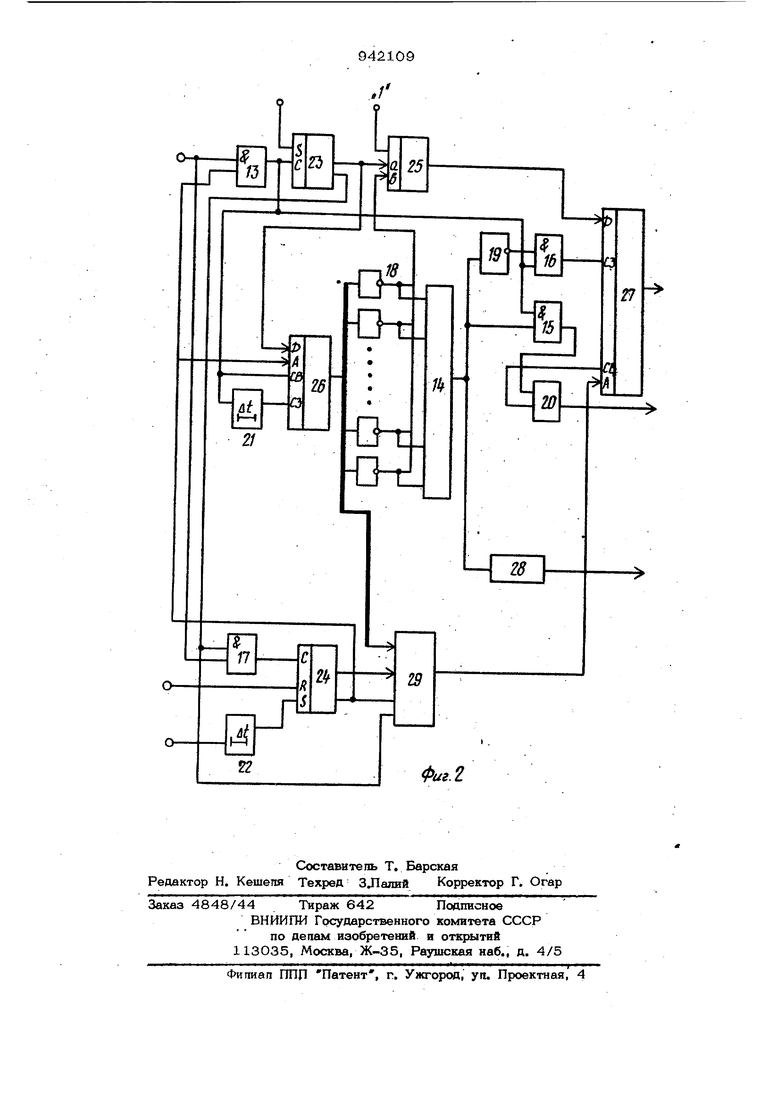

серий, выходы первой группы элементов И подключены к сдвиговым входам циклических сдвигающих регистров, выходы последних разрядов которых подключены к входам элемента ИЛИ, выход которого подключен к входу кодера длинных серий, выход второго управляющего ключа подключен к синхронизирующему входу блока: сравнения кодов, к счетным входам двоичного счетчика опроса и кольцевого счетчика опроса, выходы которого подключены к D-входам первого буферного регистр а и к вторым входам мультиплексора, к первым входам которого подключены разрядные выходы счетчиков, а его выходы подключены к первым входам блока сравнения кодов и к D -входам запоминающего регистра, выходы разрядов которого подключены к вторым входам блока сравнения кодов, выход которого подключен к входам записи запоминающего регистра, первого и второго буферных регистров; к D-входам второго буферного регистра подключены выходы двоичного счетчика опроса, выходы разрядов первого и второго буферных регистров подключены соответственно к первым входам второй и третьей группы элементов И, к вторым входам которых подклю- чек выход последнего разряда кольцевого счетчика опроса, который подключен к R-входу запоминающего {зегистра и к входу элемента задержки, выход которого подключен к счетному входу генератора кодов, выходы разрядов которого подключены к Р-входам циклических сдвигающих регистров; выходы второй группы элементов И подключены и к R-входам счетчиков и входам записи циклических сдвигающих регистров, выходы третьей группы элементов И подключены к выходам шин устройства, выход последнего разряда генератора кодов подключен к первому входу триггера режима, второй вход которой соединен с управляющим входом устройства, выходы триггера режима подключены к первым входам перво го и второго управляющих Ключей, вторые входы которых подключены к генераторуV тактовых импульсов лНедостатком данного устройства явпяется то, что оно не сжимает последова тельности сигналов, в которых имеет место равновероятное распределение ошиб ки предсказания, т.е. при Р(Р: )- 9оИ9Ь(где Р (B-J ) - вероятность появления ошибки 6), В частности, этот недостаток проявляется, если ошибка интерполирования носит близкий к периодическому во времени характер, т.е. для последовательностей, у которых AViJrH (е )-vi (е ) сои91, ) - номер выборки, на котором ошибка В встречается в -t -товый раз. Цель изобретения - расширение функционапьных возможностей устройства. Поставленная цель достигается тем, что в устройство сжатия информации введены мультиплексор, триггер и второй предварительный кодер, первый выход которого соединен с первым входом мульти плексора, выход которюго подключен к первому входу первого предварительного кодеоа, выход которого соединен с пер ВОЙ управляющей шиной, выход аналогоцифрового преобразователя соединен с вто рым входом мультиплексора с входом интерполятора и спервым входом второго предварите гшного кодера, второй выход которого подключен к второму входу первого предварительного кодера.третий выход к первому входу триггера, первый, второй выходы которого подключены соответственно к третьему и четвертокгу входам мультиплексора и к второму входу второго предварительного кодера, третий и четвертый входы которого соединены соответственно с вторым и третьим входами триггера и второй и третьей управляющими шинами, I пятый вход второго предварительного кодера соединен с шиной синхронизации. Кроме того, второй кодер содержит элементы И, группу элементов И, элементы НЕ, элементы ИЛИ, счетчик импульсов, сумматор, мультиплексор, элементы задержки, формирователь импульсов и элементы памяти, выход первого элемента И подключен к первым входам первого счетчика импульсов первого элемента памяти и к входу первого элемен-м задержки, выход которого соединен с вторым входом первого элемента памяти, выход которого подключен к первому входу му 1ьтиппексора и к входам группы элементов НЕ, выходы которых соединены с первым входом сумматора и с входами второго элемента И, выход которого соединен с входом формирователя импульсов, с входом третьего элемента И и с входом первого элемента ИЛИ, выход которого подключен к первому входу четвертого элемента И, выход которого соединен с первым входом второго элемента памяти, первый выход первого счетчика импульсов подключен к третьему входу первого элемента памяти и к второму входу сумматора, выход которого соединен с вторым входом второго элемента памяти, второй выход первого счетчика импульсов соединен с первым входом пятого элемента И и .с вторым входом мультиплексора, выход которого подключен к третьему входу второго элемента памяти, выход пятого элемента И подкгаочен к первому входу второго счетчика импульсов, к второму входу которого подключен выход второго элемента задержки, первый выход второго счетчика импульсов соединен с (третьим входом мультиплексора, второй выход - с четвертым входом мультиплексора и с первым входом первого элемента И, выход третьего элемента И подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с четвертым входом второго элемента памяти, выход первого элемента И подключен к вторым входам третьего и четвертого элементов И, вторые входы первого и пятого элементов И соединены с пятым выходом второго предваритепьного кодера, второй вход счетчика импульсов соединен с третьим выходом второго предварительного кодера, третий выход счетчика импупьсов и вход Второго элемента задержки соединены с вторым и четвертым выходами второго предварительного кодера, выходы формирователя импульсов, второго элемента ИЛИ и второго элемента памяти подключены соответственно к третьему, второму и первому выходам второго предварительного кодера.. На фиг. 1 дана структурная схема устройства; на фиг. 2 - структурная схе ма второго предварительного кодерй. f. Устройство состоит из компаратора 1 интерполятора 2, аналого-цифрового преобразователя 3 (АЦП), мультиплексора 4 первого предварительного кодера 5, второго предварительного кодера 6, кодера 7 длинных серий, триггера 8, первой, второй и третьей управляющих.шин 9-11 шины 12 синхронизации. Второй предварительный кодер состоит (фиг. 2) из элементов И 13-17, группы элементов НЕ 18, элементов ИЛИ 19-2О; элементов 21-22 задержки, первого и второго счетчиков 23-24 импупьсов, сумматора 25, первого и второго элементов 26-27 памяти, формирователя 28 импульсов и мультиплексора 29. Устройство работает в двух режимах. Для ввода в первый режим по шине . 10 (фиг. 1) подается импульс, который устанавливает триггер 8 в состояние логического О, счетчик 23 (фиг. 2) в состояние логической , при этом триггер 8 разрешает подачу кода с АИП 3через мультиплексор 4 на вход кодера 5, а логическая на первом выходе счетчика 23 открывает элемент 17 и синхроимпульсы с его выхода через элемент ИЛИ 20 поступают на второй вход кодера 5. Первый элемент И 13 при этом закрыт. Первый режим включает в себя режи- мы сжатия и переподготовки. Переключение этих режимов и управление работой устройства осуществляется согласно описанию основного устройства сжатия последовательности сигналов. Переход во второй режим осуществляется подачей по шине 11 импульса, кото рый устанавливает триггер 8 в состояние логической и, в свою очередь, открывает первый вход мультиплексора 4и закрывает его второй вход, а также задержавшись элементом 22 на время,, н обходимое для срабатыЕШния триггера 8 И снятия потенциала с третьего входа счетчика 24, он поступает на второй вход счетчика 24, на втором выходе которого появляется положительный потенциал, отпирающий первый элемент И 13. Счетные импульсы начинают поступать на вход счетчика 23, а также на первый вход элемента 26, входы элементов 21, 15 и 16, а через элемент 21 - на второй вход элемента 26. До начала вторюго режима элементы 26 и 27 обнулены Рассмотрим работы схемы в И-ый такт (, где К - емкость счетчиков 23 и 24). Код, записанный в ячейку с выхода элемента 26 в течение времени срабатывания элемента 21 в режиме выборки, инвертируется элементами 18 и поступает на вход сумматора 25. Поскольку на третий вход сумматора 25 подается логическая , то на его выходе появляется код y M-V- где V величина разности на выходе сумматора 25 в и-м такте; V - код, записанный fk началу, yi-ого такта в ячейке номер. Если 0, то на выходе элемента И 14 появляется положительный потенциал, который отпирает элемент 15 и пропускает через элемент ИЛИ 20 на второй выход кодера импульс который поступает на второй вход кодера 5 (фиг. 1). Формирователь 28 формирует импупьс, который, поступая на вход триггера 8, перекидывает его в состояние логического О и коммутирует через мультиплексор 4 выход АЦП 3 с входом кодера 5, который в соответствии с поступакхцим по второму входу синхроимпульсом считывает код Р и обрабатывает его. После окончания времени задержки элемента 21 на выходе элемента И 14 появляется фронт , из которого формирователь 23 формирует импульс, поступающий на вход триггера 8, перекидывая его в состояние логической . Если код на выходе элемента 26 V-:t О, то элемент И 14 держит запертым элемент 15, открывает элемент 16, протускает синхроимпульсы на вход элемента 27 и записывает код с выхода сук1матора 25 в элемент 27. В обоих случаях после окончания времени задержки первого элемента 21 код И. с выхода счетчика 23 записыгается в элемент 26 по адресу -f, Таким образом, по адресу t всегда, записан номер выборки, по которой вепичина С встретилась предыдущий раз, т. е.. В случае, если записйн О, то это означает, что ошибка 6 в поспедова- . тепьности входных выборок еще не встречапась. и тогда и в элемент 27 по адресу ЦР записывается величинаУ -ДИ и, кроме того, на вход кодера 5 одновременно с сянхроимпульсами по второму входу поступает последовательность неповторяющихся кодов общим числом не более 2к (где к - разрядность АЦП 3), расположенных в том порядке, в котором они встречались в исходной последовател ности ошибок предсказания. Схема работает в течение N тактов до переполнения счетчика 23. Как только счетчик 23 переполняется, на его выходе возникает потенциал, который открывает элемент 17, четвертый вход мультиплексора 29. Счетные импульсы начинают поступать на счетчик 24, а код с его выхода через мультиплексор 29 поступает на элемент 27. В это вуюмя на первый вход элемента 26 ничего не поступает, поскольку элемент 26 закрыт, а на первый вход элемента 27 поступают счетные импульсы и выдают последовательность кодов, записанных в элементе 27, на первый выход кодера 6 и через мультиплексор 4 поступают одновременно с синхроимпульсами через эле- мент ИЛИ 20 на вход кодера З.Лсоторый сжимает их. Таким образом, на вход кодера 5 в течение первы; Ы тактов асинхронно поступает последовательность из 2 неповторяющихся ошибок i , а затем в те чение следующих тактов синхронно поступает последовательность |дИ (и)}, причем, если появление ошибки f. близко к периодическому, то последовательность ЛИ(и)5 имеет резко колоколообразную верюятностную кривую, т.е. в ней сущест вуют элементы,J встречающиеся гораздо чаще других. , В предельном случае, когда ошибка. - периодична, в этой последовательности всего один элемент, ра ный периоду-следования ошибки. Это обстоятельство позволяет эффективно сжимать последовательность | Vl (я) с помощью кодера л 5 и 7. На приемном пункте по последователь ности Jt ( является по сути алфавитом, и по последовательности ЛИ (и) | легко восстанавливается исходная последовате льность. Введение второго предварительного кодера создает возможности для сжатия последовательности сигналов с квазипериодиЧеским изменением ошибки на выходе АЦП, которая не может сжиматься в известном устройстве, так как, имеет вероятность распределения, близкую к постоянной величине. В случае, когда число выборок,Ху,4,испопьзуемое интерполятором, для предсказания, невелико, а на измеряемый сигнал действует квазипериодическое возмущение, имеющее разные амплитуды и распрямляющее кривую распределения вероятностей появления ошибки Р Предлагаемое устройство может быть использовано, .в частности, для обнаружения действия периодического возмущения без повторения и анализа кривых изменения измеряемого сигнала во времени, а только по изменению коэффициента сжатия при работе устройства во втором режиме. . Формула изо.бретения 1.Устройство сжатия информации по авт. св. № 842911, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены мультиплексор, триггер и второй предварительный кодер, первый выход которого соединен с первым входом мультиплексора, выход которого подключен к первому входу первого предварительного кодера, выход которого соединен с первой управляющей шиной, выход аналого-цифрового преобразователя соединен с вторым входом мультиплексора, с входом интерплятора и с первым входом второго предварительного кодера, второй выход которого подключен к второму входу первого предварительного кодера, третий выход - к первому входу триггера, первый, второй выходы .которого подключены соответственно к третьему и четвертому входам мультиплексора и к второму входу второго предварительного кодера, третий и четвертый входы которого соединены соответственно с вторым и третьим входами триггера и второй и третьей управляющими шинами, пятый вход второго предва ритепьного кодера соединен с шиной синхронизации. 2,Устройство по п. 1, отличающее с я тем, что второй кодер содержит элементы И, группу элементов И, элементы НЕ, элементы ИЛИ, счетчики импульсов, сумматор, мультиплексор, элементы задержки, формирователь импульсов и элементы памяти, выход первого эпемента И подключен к первым входам первого счетчика импупьсов первого элемента памяти и к входу первого эпемента задержки, клход которого соединен с вторым входом пержого элемента памяти, выход которого подкточен к пер вому входу мультиплексора и к входам группы элементов НЕ, ВЁ1Ходы которых соединены с первым входом Ьумматора и с входами второго элемента И, выход которого соединен с входом формирователя Импульсов,с входом третьего эпемента И и с входом первого элемента ИЛИ, выход которого подключен к первому вхогду четвертого эпемента И, выход кото- рого соединен с первым входом второго элемента памяти, первый выход первого счетчика импульсов подключен к третьему входу первого эпемента памяти и к второму входу сумматора, выход которого соединен с вторым входом второго элемента памяти, второй выход первого счетчика импульсов соединен с первым входом пятого элемента И и с вторым входом мультиплексора, выход которого подключен к третьему входу второго элемента памяти, выход пятого элемента И подключен к первому входу второго счет чика импупьсов, к второму входу которого подключен выход второго элемента за

держки, первый выход второго счетчика импульсов соединен с третьим входом мультиплексора, второй выход - с четвертым .входе мультиплексора и с первым ъкой(ял первого элемента И, выход 1ретьего элемента И подкшочен к первому входу второго элемента ИЛИ, второй вход которого соединен с четвертым входсй .второго элемента памяти, выход первого элемента И подключен к вторым входам третьего в четвертого элементов И, вторые входы первого и пятого элементов И соединены с пятым выходом втсфо го предв|1рительного кодера, второй вход счетчика импульсов соединен с третьим выходом второго предварительного кодера, третий выход счетчика импульсов и вход второго элемента задержки соеданены соответственно с вторым и четвертым выходами второго предварительного кодера, выходы формироватепп импульсов, второго элемента ИЛИ и второго эпемента памяти подключены соответственно к третьему, второму и первому выходам Второго предварительного кодера.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-07-07—Публикация

1980-06-27—Подача