входу ВТОРОГО эпемента эапержки, при этом информационный вход, синхровход и выход пятого триггера соединены сюот«

ветствеино с выходами схемы сравнения к второго эпемента задержки и вторым входом второго эпемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1992 |

|

RU2066877C1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1619280A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1439605A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Система для контроля микропроцессорных устройств | 1983 |

|

SU1228108A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Микропроцессор | 1979 |

|

SU894715A1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

| Устройство для контроля данных электронной вычислительной машины при прерываниях питания | 1983 |

|

SU1129615A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ, содержащее бпок счетчиков, да- . шифратор, два триггера, два элемента ИЛИ, два элемента И, элемент И-НЁ, элемент ИЛИ-НЕ, два формироватепя импупьоов и элемент задержки, вход которого соединен с выходом первого эле ыЕента ИЛИ, а выход элемента задерхски подключен к управляющему входу-выходу устройства, nespBOMy входу второго эпе мента ИЛИ,управляющему входу деши(| тора и группе счетных входов блока счетчиков, вход соединен с . адресным входом-выходом устройства, а выхс« дешифратора подключен к входу первого эпемеета ИЛИ, второму входу второго элемента ИЛИ, входу первого форм|ф вателя импульсов и входу выдачи инфоркшиии блока счетчиков, вход запрета счета, первый к второй входы приема информации, информационные входы, группа входов выходов и выходы блока счет чиков соединены соответственно с выхо дами элемента И-НЕ, второго и первого формирователей импульсов, дополнительным информационным входом-выходс устройства, информационным входом-выходом устройства и входами элемента ИЛИНЕ, выход которого ПОДКЛЮЧЁН к первому входу первого элементе И и инфо(мационному входу первого триггер, выход второго элемента И соединен с вто{ялм входом первого эпемента И и синхровходоМ первого триггера, установочный вход и инверсный вь ход которого подключены соответственно к выходу де шифратора и первому входу элемента ИНЕ, первый и второй входы и выход второго триггера соединены ооответст венно с выходами дешифратора и второго элемента ИЛИ и вторым входс 4 элементта И-НЕ, выход первого элемента И 1Ю« ключен к входу второго фордарователя импульсов, а выход ёлемента И-НЕ сое I динен с первым входом второго эл. И и выходом устройства, отличающееся тем, 4To,fc; целыо пош 1шеиия достоверности контрбля, оно содержит третий, четвертый и пятый триггеры, третий элемент И второй элемент задержки, два регистра и схему Сравнения, первый и второй входы которой подклкэчены к выходам соответстве но первого и второго регистров, инфо{ мационные Bxo{u i первого и второго ре- СО 4 СЛ гистров соединены соответственно с дополнитепьным информаииошолм ккодок вы ходом и инфо| лационш 1М входом-выходом устройства, снвхровходы первого и второго регистров, третьего и четвертого триггеров и установочные входы третьего, четвертого и пятого триггеров подключены к управпяюй ему входу ш 1ходу устройства, информационные входы трегьего и четвертого триггеров соединены с общей шиной устройства, первый и второй входы и выход третьего элемента И соответственно к выходам третьего и четвертого триггеров и

Изобретение относится к цифровой вычиспитепьной технике и может быть ио потЕ зовано в вычиспитепьных устройствах, построенных по принципу общей магистра пи.

Известно устройство дпя контропя эпектронной вычиспитепыюй машины , (ЭВМ), содержащее объединенные между собой грухшой однонаправпенных и двунаправленных, связей интерфейсный блок, блок анализа информации, блок выдачи тестовых сигналов и блок управления l

В процессе работы ЭВМ это устройство периодически проверяет ее работоспособность и, есгти это возможно, по кализует и логически изолирует отказав ший блок. При этом время между появлением отказа и его обнаружением может оказаться достаточно большим (рав ным времени между проверками), что в ряде случаев недопустимо. С другой стороны, увеличение частоты проверок снижает проткзводительность ЭВМ, .так как все большая часть машинного времени расходуэтся на выполнение контрольных, а не попезных операций.

Наиболее близким по технической сущности к предгтагаемому является устройство дпя контроля ЭВМ, Содержащее блок счетчиков, дешифратор, два триггера, два элемента ИЛИ, два элемента И, элемент И-НЕ, элемент ИЛИ-НЕ, два формироваfena импульсов и элемент задержЬи, адресных входов устройства соединена через дешифратор с входами первого элемента ИЛИ, с первым входом второго эпемента ИЛИ, с установочными входами первого и второго триггеров, с входом первого фор.4ирователя импульсов и с входом выдачи информации блока счетчиков, группа информационных входов-выходов устройства соединена с группой входов выходов бпока счетчиков, группа управляющих входов выходов устройства соединена с группой счетных входов блока счетчиков, с управляющим входом дешифратора, с ш 1ходом элемента аа,держкн и с вторым входом BTOpojO элемента ИЛИ,

группа дополнительных входов устройства соединена с информационными входами бгюка счетчиков выходы которого через элемент ИЛИ-НЕ соединенны с информационным входом первого триггера и с первым входом первого элемента И, выход которого через второй формирователь импульсов соединен с первым входом приема информации блока счетчиков, второй вход первого эпемента И соединен с выходом второго эпемента И и с синхронизирующим входом первого триггера, ну повой которого со адинен с первым входом элемента И-НЕ, 1зторой вход которого соединен с выходом второго тригг ра, вход сброса которого соединен с выходом второго элемента ИЛИ, выход элемента И-НЕ является выходом устройства и соединен с первым входом-второго эпемента И и с входом запрета счета бпока счетчиков, выход nepBiOro формирователя импулЬсов соединен с вторым входом приема информации блока счетчиков, выход первого элемента ИЛИ соединен с входом элемента задержки .

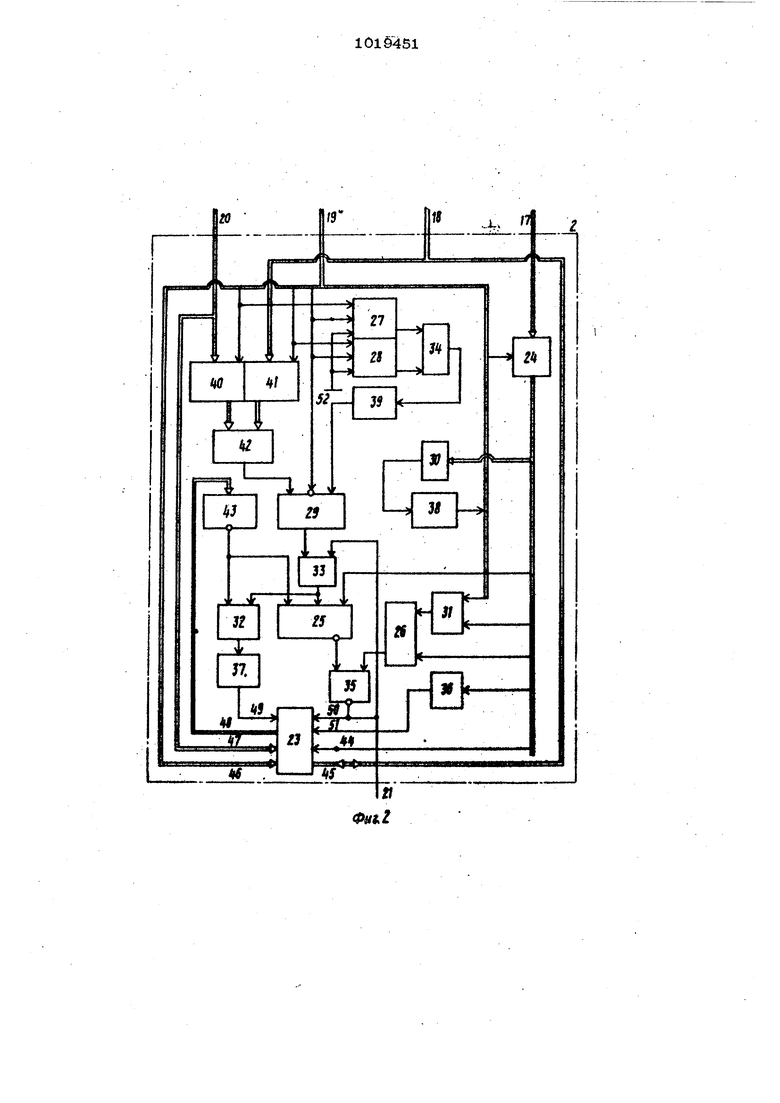

В процессе работы ЭВМ одновременно с выбором очередной команды из памяти

: программ из дополнительной памяти извлекается константа, отличная от нуля или равная нулю. Первый случай соответствует выходу процессорЕ на очередной

;линейный участок пpoгpa ЛIы, второй выбору последующих данного линейного участка. Извлекаемая из памяти константа является набором мапоразрядкых эталонных чисел, прогнозирующих число ожидаемых сигналов на управляющих пиниях интерфейса щда отработке процессором данного линейного участка протраммы.

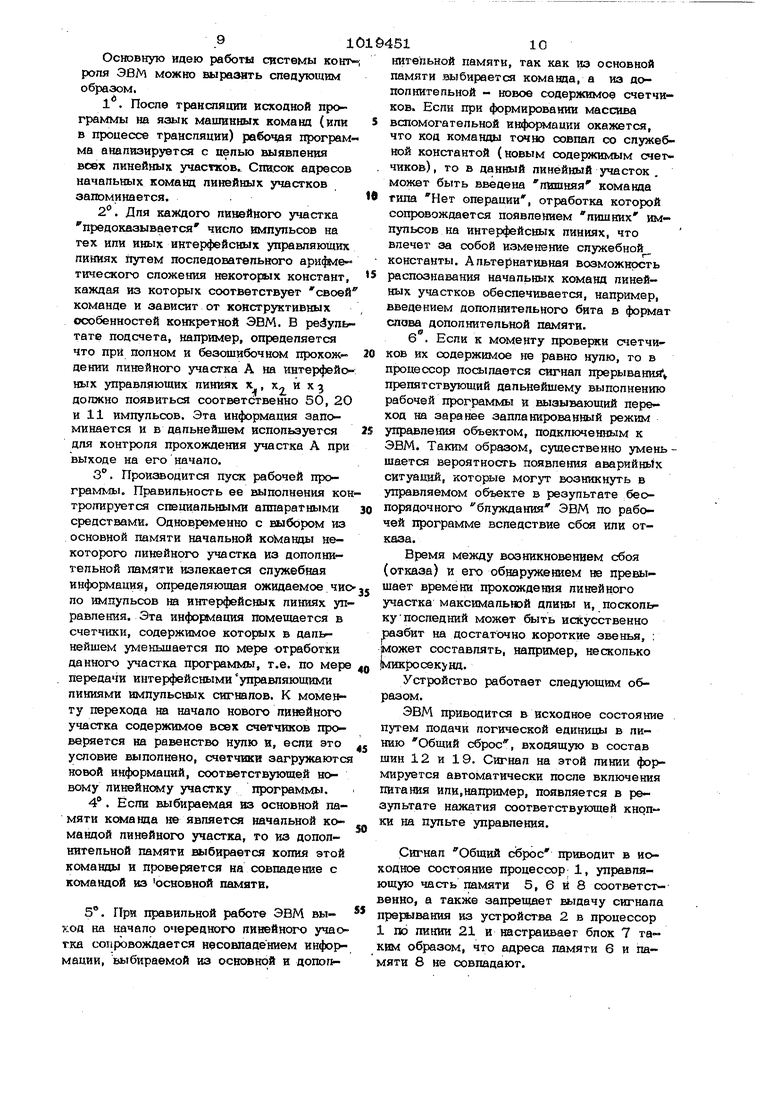

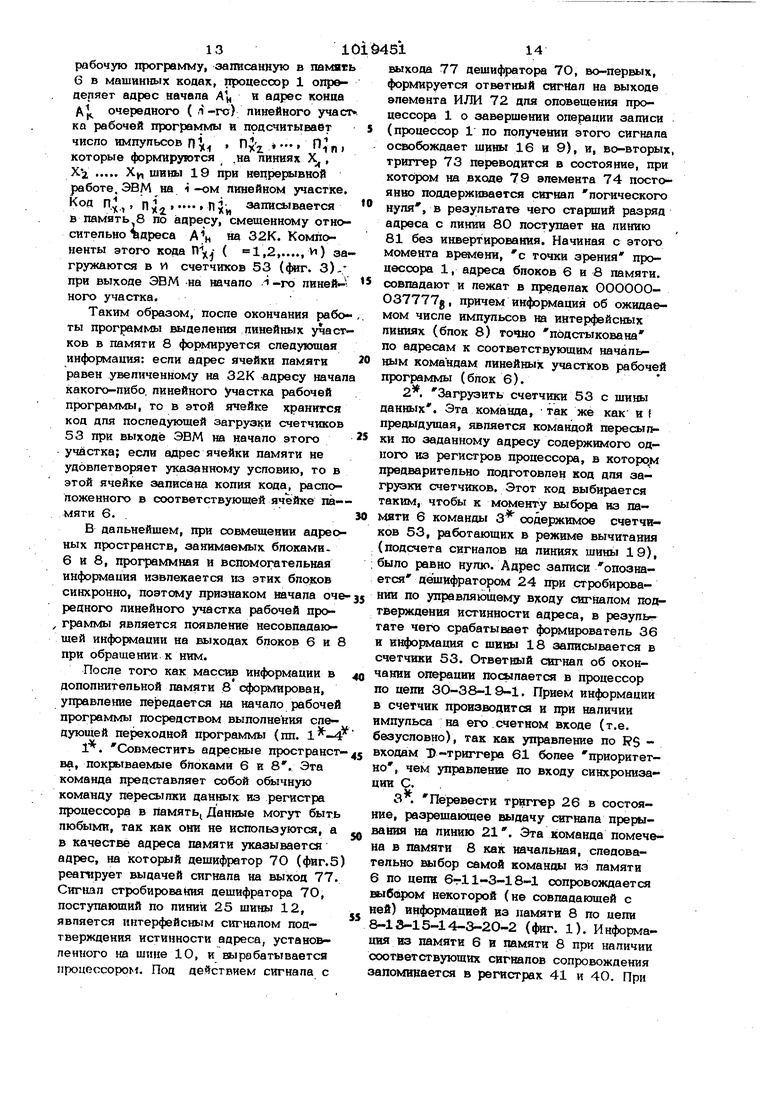

Недостатком этого устройства является невозможность обнаружения некоторых ошибок. Например, если в результате потери бита в памяти, сбоя в линии связи либо в согласующем бпоке и т.п. в процессор команды сложения посту пит команда вычитания,то эта ошибка не будет обнаружена, так как обе команды сопровождаются одной и той же поспедоватепьностью управляющих сигнапрв на интерфейсных пиниях. Цепь изобретения - увеличение аостоверности контропя. Поставпенная иепь достигается тем, Kto устройство дпя контропя эпектронной вычиспитепьной машины, содержащее бпок счетчиков, дешифратор, два триггера. Два элемента ИЛИ, два элемента И, элемент И-НЕ, эпемент ИЛИ-НЕ, два формнрователя импупьсов и элемент задержки, вход которого соединен с вь1 ходом первого эле мента ИЛИ,а выход элемента задержки подключен к управляющему входу выходу устройства, первому входу второго элемента ИЛИ, управляющему входу дешифратора и группе счетных входов блока счетчиков, вход дешифратора соединен с адресным входом-выходом устройства, а выход дешифратора Подключен к входу первого элемента ИЛИ, второму входу второго элемента ИЛИ, входу первого формирователя импульсов и входу вы чачи информации блока счетчиков, вход запрета счета, первый и второй входы приема информации, информационные входы, группа входов-выходов и выходы блока счетчиков соединены соответственно с выходами элемента И-НЕ, второго и пер врго формирователей импупьсов, дополнительным информационным входом-выходом устройства, информационным входом-выхо дом устройства и входами элемента ИЛИ НЕ, выход которого подключен к первому входу первого элемента И и информаыион ному входу первого триггера, выход вто рого элемента И соединен с вторым вхо дом первого элемента И и синхровходом первого триггера, установочный вход и инверсный ход которого подключены соответственно к выходу дешифратора и первому входу элемента И-НЕ, первый и второй входы и выход второго триггер соединены соответственно с вьтходаМи де шифратора и второго элемента ИЛИ и вторым входом элемента И-НЕ, выход первого элемента И подключен к входу второго формирователя импульсов, а выход элемента И-НЕ соединен с первым входом второго элемента И и выходом устройства, введень третий, четвертый и пятый триггеры, третий эпемент И, второй элемент задержки, два регистра и схема сравнения, первый и второй входы которой подключены к выходам соответст венно первого и второго регистров, информационные входь первого и второго регистров соединены соответственно с ополнитепьнь1м информационным входомыходом и информационным входом-выодом устройства, синхровходы первого второго регистров, третьего и четверого триггеров н установочные входь ретьего, четвертого и пятого триггеров подключены к управляющему входу выходу устройства, информационные входы третьего и четвертого триггеров соединены с общей шиной устройства, первый и второй входы и №1ход третьего элемента И подключены соответственно к выходам третьего и четвертого триггеров и входу второго элемента задержки, при этом информационный вход, синхровход и выход пятого триггера соединены соответственно с Ш1ходами схемы сра&нвния и второго элемента задержки и вторым входом второго элемента И. На фиг. 1 представлена функциональная ЭВМ, поясняющая назначение предлагаемого устройства для контроля; на фиг. 2 - функциональная схема устройства дпя контроля; на фиг. 3 - функциональная схема блока счетчиков; на фиг. 4 - функциональная схема счетчика; на фиг. 5 - функциональная схема блока преобразования адресов; на фиг. 6 - функциональная схема блока сопряжения; на фиг. 7 - временная диаграмма работы устройства. Электронная вычислитепьиая машина (фиг. 1) содержит процессор 1, устройство 2 для контроля, блок 3 сопряжения, блок 4 памяти вкпючающий в себя память 5 данных и память 6 программ, блок 7 преобразования адресов и дополнительный блок 8 памяти. Блоки 3,5,7 и 8 объединены посредством группы шин 9, включающих в себя адресные 10, информационные 11 и управляющие шины 12. Выходы 13 блока 8 ссединены с входами 14 блока 3 посредством инфор.мационных шик 15. Процессор 1 соединен с устройством 2 и блоком 3 посредством группы 16 шин, включающих в себя адресные 17, информационные 18 и управляющие шины 19, Устройство 2 и блок 3 соединены также посредством группы допоп1штельных информациошых шин 20. Выход устройства 2 соединен с входом прерывания процессора 1 посредством, линии 21. Выходы блока 7 соединены с адресными входами блока 8 посредством группы шин 22, Устройство 2 для контроля (фиг, 2) содержит блок 23 счетчиков, дешифратор 24, триггеры 25-29, элементы 510 ИЛИ ЗО и .31, эпеменгы И 32-34, эпементы И-НЕ 35, формироватепн 36 и 37 импульсов, элементы 38 и 39 задержки, регистры 40 и 41, схему 42 сравнения И элемент ИЛИ-НЕ 43. Адресные шины 17 устройства 2 соединены через дешифратор 24 с входа1уга элемента ИЛИ 30 с первым входом элемента ИЛИ 31, с установочными входами триггеров 25, и 26, с входом формирователя 36 и с входом 44 выдачи информации блока 23 счетчиков. Информациоюяые шины 18 уст ройства 2 соединены с группой 45 вхо доЕ -выходов 23 и с входами регистра 41. Управляющие шины 19 устрой ства 2 соединены с группой 46 счетных входов |блока 23, с управляющим входом дешифратора 24, с .выходом элемента 38, с вторым входом элемента ИЛИ 31, синхровходами регистров 4О и 41, с установочными входами триггеров 27 и 28, с синхровх дймй этйх триггеров и с входом сброса триггера 29. Входы устройства 2, подключенные к шине 20, со© динены с информационными входами 47 блока 23 и с входами регистра 40. Выходы 48 блока 23 соединены с входами элемента 43, выход которого соединен с информационным входом триггера 25 и с первым входом элемента И 32. Выход элемента И 32 через формирователь 37 соединен с входом 49 приема информации блока 23. Второй вход элемента И 32соединен с выходом .та И 33 и с синхровходом триггера 25, нулевой выход которого соедине.но с первым входом элемента И-НЕ 35, второй вход которого соединен с выходом триггера 26. Вход сброш триггера 26 соединен с выходом эле 51ента ИЛИ 31. Выход элемента И-НЕ 35 является выходом 21 устройства и соединен с первым входом элемента И 33 и с входом 50 запрета счета блока 23. Выход формирователя 36 соединен с входом 51 приема ннформашш блока 23. Выход элемента ИЛИ 20 соединен с входом элемента 38. Выходы регистров 40 и 41 соединены с входами схемы 42, выход которой соединен с информационным вхо цом триггера 29, выход которого соединен с вторым входом элемента И 33. Выходы триггеров 27 и 28 соединены с входами элемента И 34, выход которого через элемент 39 соединен с синхровходом триггера 29. Информационные

входы триггеров 27 и 28 подключены к общей щине 52.

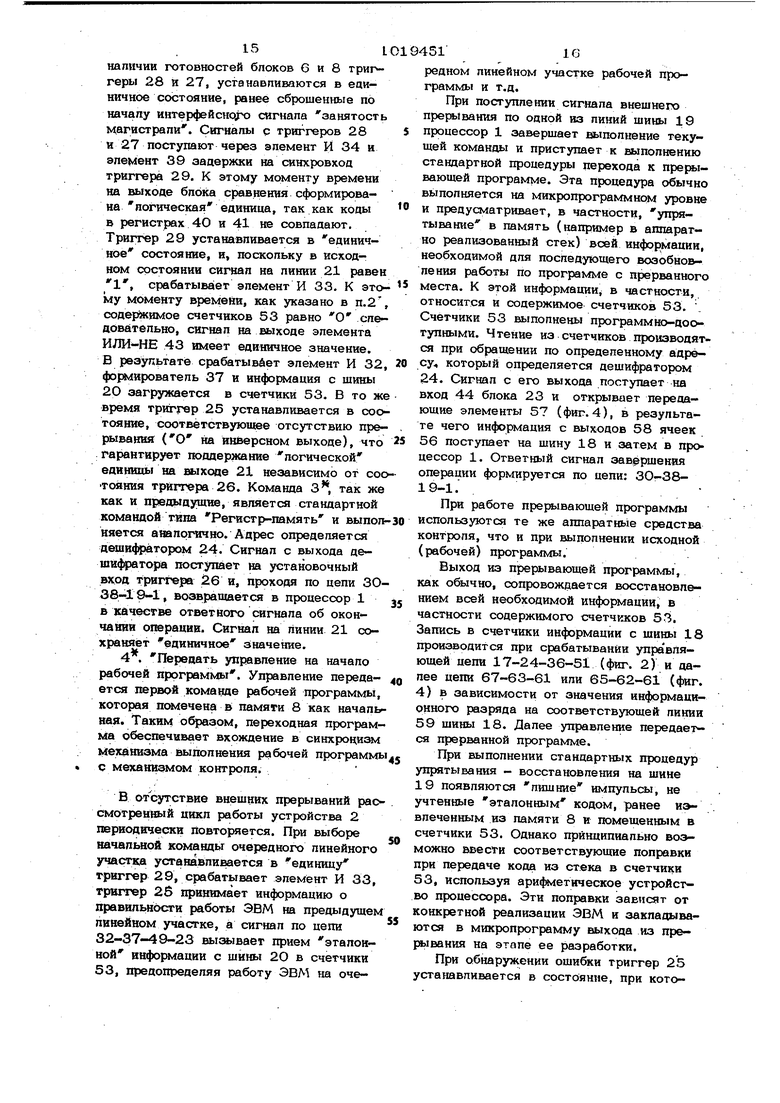

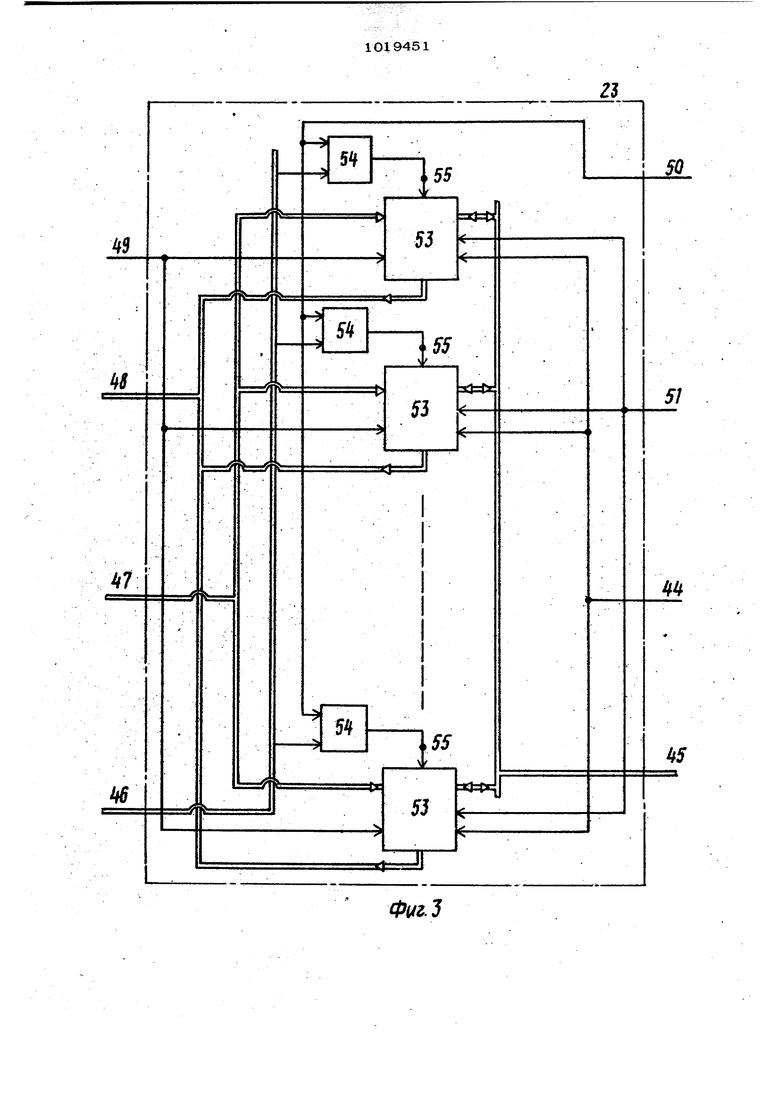

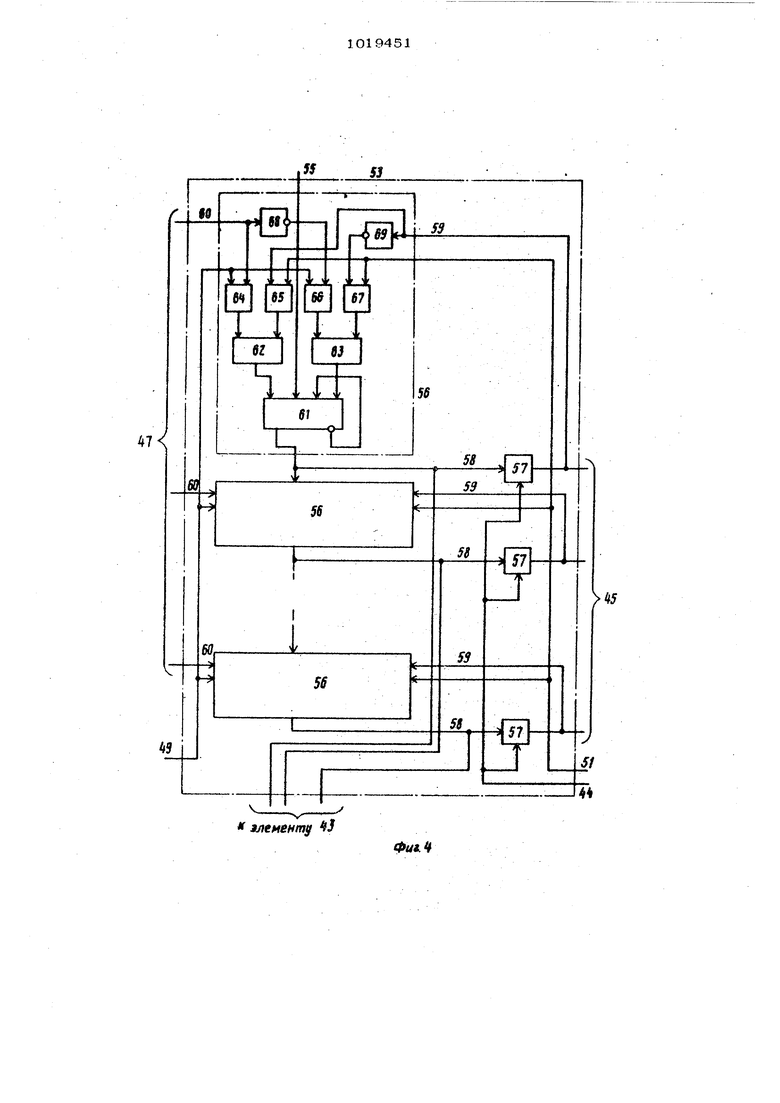

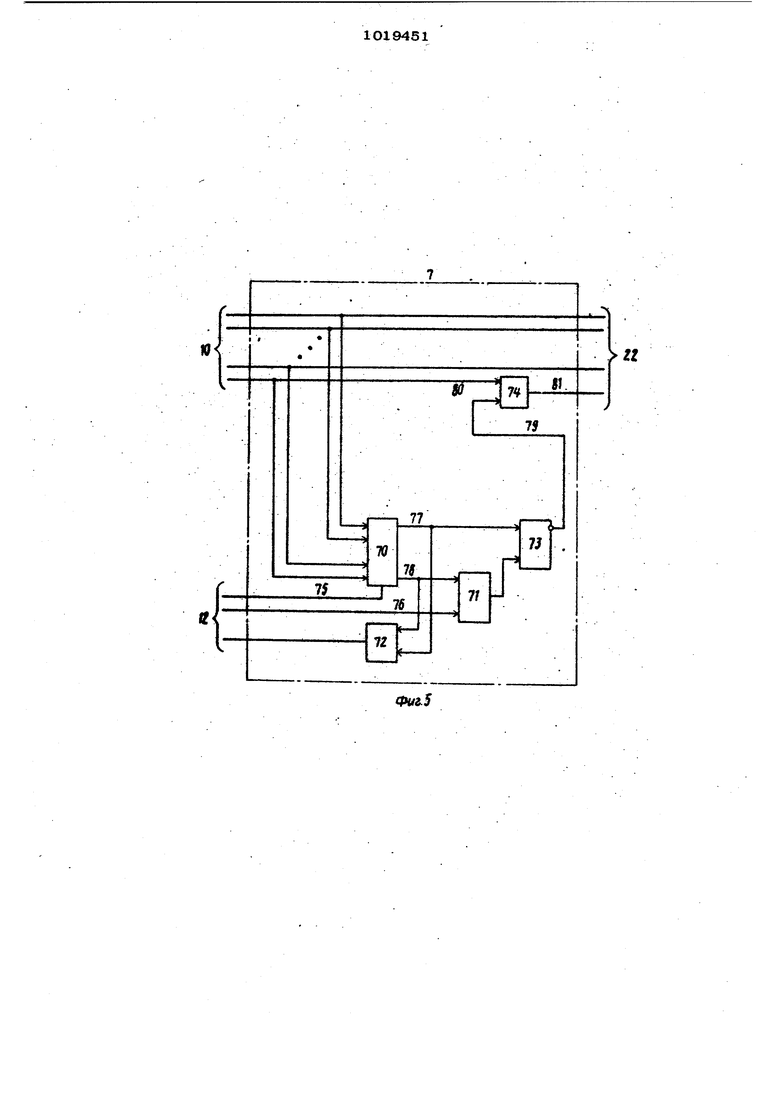

рез элемент И-НЕ (инвертор) 69 - с входом элемента 67. S16 Блок 23 счетчиков (фиг. 3) соаержит группу 53 счетчиков и гругщу 54 эпеменгов И. Первые входы эпементов И 54 объединены и являются входом 50 эапрета счета, вторые входы эпементов И явпяются группой 46 счетных входов блока 23. Выходы элементов И 54 схэедийены со счетными входами 55 соответствующих счетчиков 53, группа 47 информацйонных входов блока 23 соединена с информационными входами счетчиков 53, вход 49 приема информации блока 23 - с с входами приема информации счетчиков 53. Выходы счетчиков 53 являются групдод выходов 48 блока 23, входы-выходы счетчиков 53 - группой входо&-выходов 45 блока 23, Вход 51 приема информации блока 23 соединен с входами приема информации счетчиков 53, вход 44 выдачи информации блока 23 - с входами выдачи информации счетчиков 53. Счетчик 53 (фиг. 4) содержит последовательно соединенные одноразрядные ячейки 56 и передающие элементы 57. Выходь ячеек 56 соединены с информационными входами 58 элементов 57 и являются информационными выходами счетчика. Управляющие вхооя элементов 57 объединены и подключены к входу 44 выдачи. Выходы элементов 57 соединены с входами 59 соответствующих ячеек и являются группой ВХОДО&-ВЫХОДОВ 45. Входы приема информации с линии 45 . всех ячеек 56 объединены и соединены . ПР«-- В-«ь 6О ячеек 56 являются группой 47 входов. Входы приема ииформапии с линии 47 ячейки 56обг«динены и соединены с входом 49 приема. Ячейка 56 содержит триггер 61, ., ft, - .V «Л 1Г г JI f элементы ИЛИ 62 и 63, элементы И 6467 и элементы И-НЕ 68 и 69. Синхронизирующий вход триггера 61 ячейки младшего разряда является счетным входом 55 счетчика 53, единичный выход триггера 61 - выходом ячейки. Нулевой выход триггера 61 соединен с информационным входом этого же триггера, входы установки И сброса триггера 61 соединены соответственна с выходами элементов ИЛИ 62 и 63, входы которых соединены с выходами элементов И 6467. Вход 49 соединен с входами эпеме тов И 64 и. 66, вход 51 - с входами элементов И 65 и 67. ЕЗход 60 соединен с входом элемента И 64 и через элемент 68 - с входом элемента 66. Вход 59 соединен с входом элемента И 65 и чеБпок 7 преобразова1гая адресов (фиг.5 содержит дешифратор 70, эпементы ИЛИ 71 и 72, триггер 73 и элемент ИСКЛЮЧАЮШЕЕ ИЛИ 74., Адресные входы дешифратора 7О подключены к шине 10. Управпяющий вход 75 дешифратора 70, первый вход 76 элемента ИЛИ 71 и выход элемента ИЛИ 72 подключены к шине 12. Выход 77 дешифратора 7О соединен с входом установки- триггера 73 с первым входом элемента ИЛИ 72. Выход 78 .дешифратора 70 соединен с вторым входом элемента ИЛИ 72 и с вторым входом элемента ИЛИ 71. Выход, элемента ИЛИ 71 соединено входом сброса триггера 73, нулевой выхрд которого соединен с первым входом 79 элемента 74, второй вход 80 которого соединен с адресном входом старшего разряда дешифратора 7О Выход 81 элемента 74, а также все адресные входы дешифратора 70, за искпк чением входа, соединенного с входом 8О элемента 74, являются группой выходов 22 блока 7 преобразования адресов.

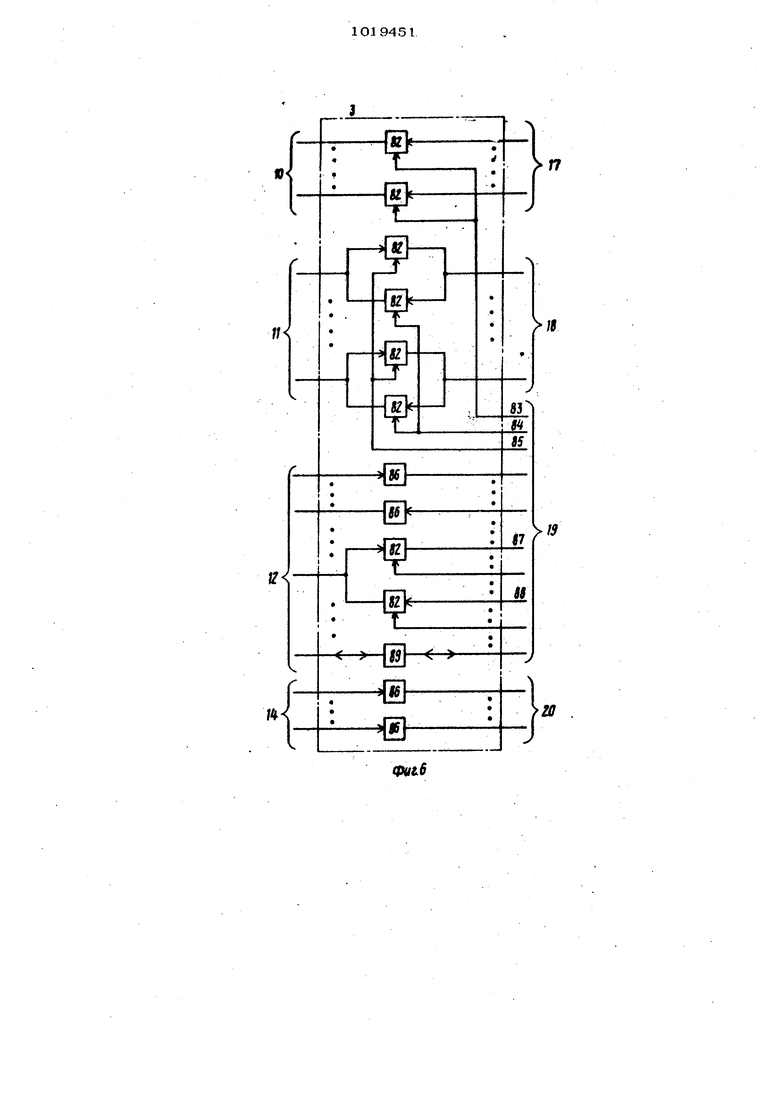

Блок 3 сопряжения (фиг. 6) содержит приемопередающие элементы. Для передачи адреса с шины 17 на шину 10 ис-пользуются эпементы 82 управляющие входы KOTOF« IX объединены и соединены с линией 83, входящей в состав шины 19 В зависимости от значения сигнала на управляющем входе элемента 82 он либо закрыт (высокоомное состояние выхода), дибо транслирует сигнал с входа на выхо Дпя двунаправленной передачи данных между шинами 11 и 18 используются попарно объединенные эпементы 82, управляющие входы которых соединень с линиями 84 и 85, входящими в состав 19. В зависимости от значений сипналов на входах 84 и 85 выбирается то или иное направление п ёредачи данных. Для сопряжения шины 12 с шиной 19 используютря элементы разных типов: кабельные усилители 86 (без управления), элементы 82, управление которыми производится по линиям 87 и 88, а также асинхронные самоуправляемые двунаправленные приемопередающие элементы 89, выполненные на стандартных логических элементах (Wew E6ecii OHiC5 ,. 1 979, hfe 16, p. 52). Передача данных с шины 14 на шину 2О производится с помощью кабельных усилитепе й 8.6.

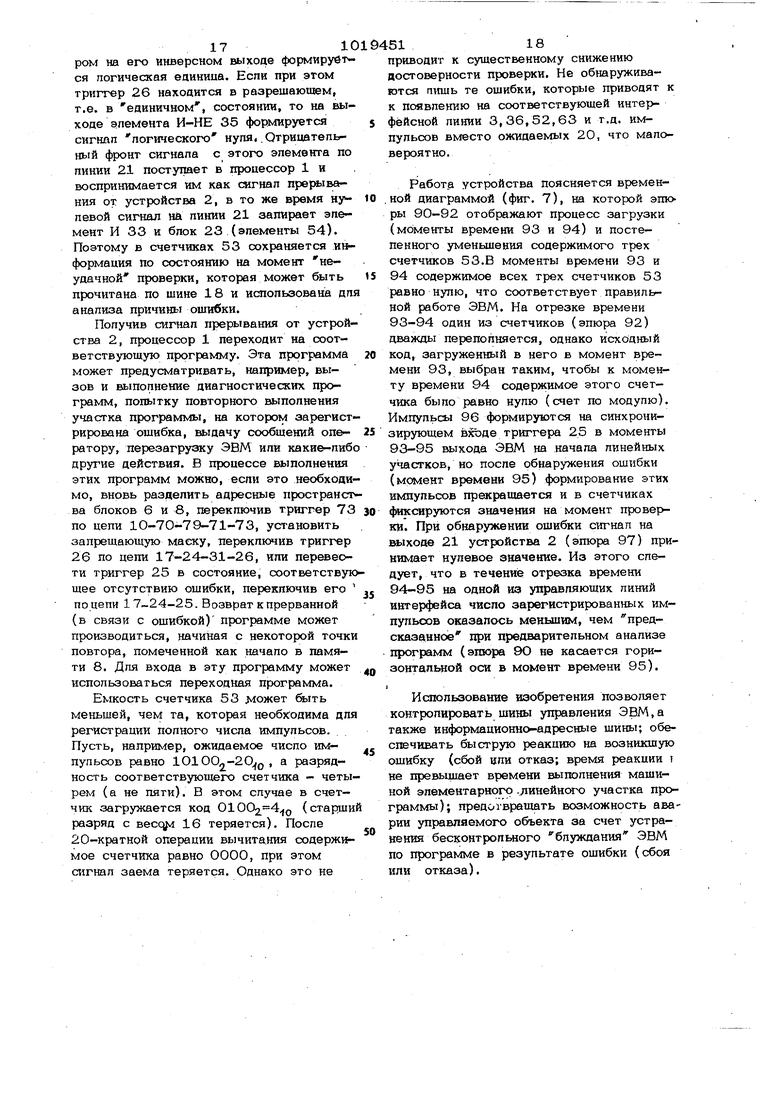

На временной диаграмме работы устройсгва (фиг. 7) показаны эпюры 9О-92 каменетя содержимого трех счетчиков 53. По оси у отложены десятичные числа накопленные в счетчиках. Моменты времени 93-95 соответствуют моментам выхода ЭВМ на началах некоторых линейных участков программы. Эпюра 96 отображает сигналы на. синхронизирующем входе триггера 25. Эпюра 97 соответствует сигналу на выходе 21 устройства. Рассмотрим построение системы контроля ЭВМ.

Любую программу, записанную в машинных кодах в память ЭВМ, можно представить в виде набора линейных учаотков, связаншлх между собой командами j переходов. Команда перехода является завершающей командой линейного участка, если он не последний линейный участок программы - в этом случае линейный участок может завершаться, например, командой Останов. Начальной командой линейного участка может быть либо ко манда, являющаяся внешним входом программы, либо команда, на которую производится передача управления одной из команд перехода. Если некоторый линейный участок программы содержит несколько начальных команд (точек вхождения), то он может рассматриваться как цепь из нескольких линейных участков, каждый из которых имеет одну начальную команду. В этом случае конечной командой 71Юбого звена цепи, кроме последнего, является команда, предшествующая начаш ной команде следующего звена.

Таким образом, любую программу можно разбить на отдельны линейные участки, на которых поведение ЭВМ строго :детерминировано, в том смысле, что щт правильном прохожде1гаи ЭВМ через данный линейный участок программ на интерфейсных управляющих линиях должно быть зарегистрировано строго определенное число импульсов, которое и; вестно для каждого линейного участка еще до начала работы ЭВМ по программе. Это утверждение остаётся справедливым и тогда, когда процесс прохождения данного линейного участка временно приостанавливается в связи с реакцией н внешние программно-независимые событи (пре млвания). В этих случаях, как обычно, используется стековый механизм запо минания и восстановления необходимой информации. Совокупность интерфейсных управляющих сигналов, которыми сопровождается выполнение команд условных переходов, не зависит от того, выполнено ли проверяемое условие или нет (Клингман Э. Проектирование микропроцессорных систем. М., Мир, 1980, с. 155-158). Основную идею работы системы контропя ЭВМ можно выразить спедующим образом. 1 . После трансляции исходной программы на язык машинных команд (или в процессе трансляции) рабочая программа анализируется с цепью выявления всех линейных участков. Список адресов начальных команд линейных участков запоминается. 2. Для каждого линейного участка предоказывается число импульсов на тех или иных интерфейсных управляющих линиях путем последовательного арнфме тического сложения некоторых констант, каждая из которых соответствует своей команде и зависит от конструктивных особенностей конкретной ЭВМ. В ре ультате подсчета, например, определяется что при полном и безошибочном прохождешга линейного участка А на интерфейсных управляющих линиях х , Х2 и х должно появиться соответственно 50, 20 и 11 импульсов. Эта информация запоминается и в дальнейшем используется для контроля прохождения участка А при выходе на его начало. 3. Производится пуск рабочей программы. Правильность ее выполнения ко тролируется специальными аппаратными средствами. Одновременно с выбором из основной памяти начальной команды некоторого линейного участка из дополнительной памяти излекается служебная информация, определяющая ожидаемое HHO ло импульсов на интерфейсных линиях уп равления. Эта информация помещается в счетчики, содержимое которых в дальнейшем уменьшается по мере отработки данного участка программы, т.е. по мере передачи интерфейсными управляющими линиями импульсных сигналов. К моменту перехода на начало нового линейного участка содержимое всех счетчиков проверяется на равенство нулю и, если это условие выполнено, счетчики загружаютс новой информации, соответствующей новому линейнотлу участку программы. 4. Если выбираемая из основной памяти кся«1анда не является начальной командой линейного участка, то из дополнительной памяти выбирается копия этой команды и проверяется на совпадение с командой из основной памяти. 5. При правильной работе ЭВМ выход на начало очередного линейного учао гка сопровождается несовпадением информации, выбираемой из основной и допо№нитедьной памяти, так как иэ основной памяти аь бираегся команда, а из дополнительной - новое содержимое счетчиков. Если при формировании массива вспомогательной инфсфмаиии окажется, что код команды точно совпал со служебной константой (новым содержимым счетчиков), то в данный линейный участок , может быть введена лишняя команда гипа Нет операции , отработка которой сопровождается появлением лишних импульсов на интерфейсных линиях, что впечет за собой изменение служебной коистанты. Альтернативная возможность распознавания начальных команд линейных участков обеспечивается, например, введением дополнительного бита в формат слова дополнительной памяти. 6, Если к моменту провержи счетчиков их содержимое не равно нулю, то в процессор посылается сигнал прерывания препятствующий дальнейшему выполнению рабочей программы и вызывающий переход на заранее запланированный режим управления объектом, подключенным к ЭВМ. Таким образом, существенно умень шается вероятность появления аварийнь1х ситуаций, которязге могут возникнуть в управляемом объекте в результате беопорядочного блуждания ЭВМ по рабочей программе вследствие сбоя или отказа. Время между возникновением сбоя (отказа) и его обнаружением не превышает времени прохождения линейного участка максимальюй длины и, по сколькупоследний может быть искусственно разбит на достаточно короткие звенья, : 1Может составлять, например, несколько секунд. Устройство работает следующим образом. ЭВМ приводится в исходное состояние путем подачи логической единицы в линию Общий сброс, входящую в состав шин 12 и 19. Стенал на этой линии формируется автоматически после включения питания или,например, появляется в результате нажатия соответствующей кнрпзси на пульте управления. Сигнал Общий серое приводит в исходное состояние процессор 1, упрешляющую часть памяти 5, 6 и 8 соответственно, а также запрещает выдачу сигнала прерывания из устройства 2 в процессор 1 по пинии 21 и настраивает блок 7 таким образом, что адреса памяти 6 и памяти 8 не совпадают. Запрет выдачи сигнала прерывать про изводится спедующим образом. Сигнап Обишй сброс поступает с шины 19 (фиг. .2) на вход эпемента ИЛИ 31, а .с его вьгхода - на вход сброса триггера 26. Нулевой сигнап с выхода триггера 26 запирает элемент И-НЕ 35, в результате чего сигнап на выходе 21 этого элемента принимает единичное значение. Это остояние соответствует отсутствию прерывания. Настройка блока 7 на разделение адресов памяти 6 и памяти 8 производится при поступпедаи сигнала Общий сброс с шины 12 (фиг.5) по линии 76 на вход элемента ИЛИ 71, а с его выхода на вход сброса триггера 73. Единичный сигнал с нулевого вьгхода этого триггера по линии 79 поступает на первый вхо элемента 74, который при этом можно рассматривать как инвертор, включенный между, пиниями 80 и 81. Таким образом адресные коды, поступающие в дальнейшем с шины 10, поступают на шину 22 с инвертированием старшего разряда. Это приводит к разделению адресов, как пока зано на следующем примере. Пусть число линий адресных шин 17 10 равно 16. В этом случае адресное пространство ЭВМ составляет 64К, где К 1024. Пусть далее зоны собственнь1х адресов памяти 6 и памяти 8 совпадают и лежат в пределах ОООООО-. О37777д (16К). Если процессор 1 обратится по любому адресу из указанного диапазона, то этот адрес с шины 17 (фигМ). передается через блок 3 сопряжения на пгану 10. С этой шины адрес постутюет в память 6, которая воспринимает его как свой и производит операцию чтения ипи записи одной из ячеек. Одновременно с этим адрес, проходя с шины 10 через блок 7 на шину 22, искажается за счет инвертирования .старшего разряда и память 8 расценивае его как чужой, лежащий в диапазоне 10OOOO-137777g. Поэтому обмен с памятью 8 не производится. Дтш обращ&ния к памяти 8 процессор 1 формирует на шине 17 адрес, содержащий в двух старших разрядах код 10,2. При этом память 6 не производит операции обмена (адрес лежит в чужом диапазоне), а память 8 расценивает его как свой , так как в старших разрядах адресного кода на шине 22 содержится комбинация ОО, определяющая зону ОООООО037777g. 10 3112 При работе ЭВМ возникает необходи.-Д мосгь совмещения адресных пространств, покрываемых блоками 6 и 8 памяти. Для этого триггер 73 (фиг. 5) переключается по цепи 1О-7О-77 в противоположное состояние, в результате чего элемент 74 передает старший разряд адреса на шину 22 без искажения. В этом случае адреса памяти 6 и памяти 8 совпадают и one- рации обмена выполняются в них синхгюнно. Память 6, как и память 8, может выполняться в виде постоянного, попупо стоянного или оперативного запоминак щих устройств или их комбинации. Будем считать, что память 6 и память 8 содерл жат как постоянную, так и оперативную части; После окончания сигнала Общий сброс процессор автоматически или по инициативе оператора переходит к выпол нению одной из программ, записанных в постоянной части памяти 6. Такой программой может быть программа-загруэчик, под управлением которой информация вводится в ЭВМ и размещается в оперативной части памяти 6. Процедура ввода определяется составом периферийных устройств, подключенных к ЭВМ, интер фейсом, системой команд и другими характеристиками конкретной ЭВМ. Эта процедура осуществляется одним из иэ вестных способов. Вводимые данные размещаются в памяти 5. Вводимая в память 6 программа представлена в виде последовательности машинных кодов, т.е. ввод может сопровождаться вводом заранее подготовленного массива вспомогательной информации в дополнительную память 8 (адресные пространства, занимаемые блоками 6 и 8 памяти, на этапе ввода не совпадают). Если вспомогатель ная информация отсутствует, то она формируется самой ЭВМ при piaboTB спеииальной программы выделения линейных участков. Если вводимая в память 6 про грамма записана на языке, отличном от языка машинных кодов, то она переводится на этот язык в результате работы программы-транслятЬра. После этого для обеспечения самоконтроля ЭВМ также неоходимо сформировать в памяти В массив вспомогательной инфо жлации, дпя чего используется программа выделения линейных участков. Программа выделения линейных учас ков ы шолняется следующим образом. Во все ячейки (lOOOOO-137777g} памяти 8 процессор 1 последовательно записывает копии кодов, расположенных в памяти 6. Последовательно анализируя рабочую программу, записанную в памят 6 в машинных кодах, процессор 1 опредепяег адрес начала АН и адрес конца AJ очередного ( л-го) пикейного участ KQ рабочей программы и подсчитывает чиспо нмпупьсов п х I ПУЗ, , которые формируются .на пиниях Х, Хз. Х шины 19 при непрерывно jiaботе. ЭВМ на i-ом пинейном участке. Кой П., , jj, записывается в память 8 по (адресу, смешенному отно ситепьно Адреса на 32К. Компоненты этого кода ( ,2, vi) за гружаются в и счетчиков 53 (фиг. 3)-; при выходе ЭВМ на начапо i -го пнней- кого участка. Таким образом, поспе окончания рабо ты программы выдепения пинейных участ ков в памяти 8 формируется следующая информация: еспи адрес ячейки памяти равен увеличенному на 32К адресу начал какого-либо, линейного участка рабочей программы, то в этой ячейке хранится код для последующей загруэки счетчиков 53 при выходе ЭВМ на начало этого участка; если адрес ячейки памяти не удовлетворяет указанному условию, то в этой ячейке записана копия кода, расположенного в соответствующей ячейке па- мяти 6. В дальнейшем, при совмещении адрео ных пространств, занимаемых блоками6 и 8, программная и вспомогательная информация извлекается из этих бло.ков синхронно, поэтому признаком начала оче редного линейного участка рабочей программы является появление несовпадающей информации на выходах блоков 6 и 8 при обращении к ним. После того как массив информации в дополнительной памяти 8 сформирован, управление пе редается на начапо рабочей программы посредством выполнения следующей переходной программьт (пп. 1. Совместить адресные прост ранет ва, покрываемые блоками 6 и 8. Эта команда представляет собой обычную команду пересылки данных из регистра процессора в памятЬ1 Данные могут быть любыми, так как они не используются, а в качестве адреса памяти указывается адрес, на который дешифратор 70 (фиг.5 реагирует выдачей сигнала на выход 77. Сигнал стробироваНия дешифратора 70, поступающий по пинии 25 шины 12, является интерфейснь7м сигналом подтверждения истинности адреса, установленного на шине 10, и вырабатывается процессором. Под действием сигнала с выхода 77 дешифратора 7О, во-первых, формируется ответный сигнал на выходе элемента ИЛИ 72 для оповещения процессора 1 о завершении операции записи (процессор 1 по получении этого сигнала освобождает шины 16 и 9), и, во-вторых, триггер 73 переводится в состояние, при котором на входе 79 элемента 74 постоянк поддерживается сигнал логического нуля , в результате чего старший разряд адреса с линии 80 поступает на линию 81 без инвертирования. Начиная с этого момента времени, с точки зрения процессора 1, адреса блоков 6 и 8 памяти, совпадают и лежат в пределах ОООООО037777g, причем информация об ожидаемом числе импульсов на интерфейсных линиях (блок 8) точно подстыкована по адресам к соответствующим начальным командам линейных участков рабочей программы (блок 6). 2. Загрузить счетчики 53 с шины данных . Эта , так же как и f предыдущая, 51вляется командой пересыпки по заданному адресу содержимого одного из регистров процессора, в KOTopq.M предварительно подготовлен код для загрузки счетчиков. Этот код выбирается таким, чтобы к моменту выборе из памяти 6 команды 3 содержимое счетчиков 53, работающих в режиме вычитания (подсчета сигналов на линиях шины 19), было равно нулю. Адрес записи опознается дешифратором 24 при сгробировании по управляющему входу сигналом подтверждения истинности адреса, в результате чего срабатывает формирователь 36 и информация с шины 18 записывается в счетчики 53. Ответный сигнал об окончании операции посылается в процессор по цепи 30-38-19-1. Прием информации в счетчик производится и при наличии импульса на его счетном входе (т.е. безусловно), так как управление по RS входам D-триггера 61 более приоритетно, чем управление по входу синхронизации С. . 3 Перевести триггер 26 в состояние, разрешающее выдачу сигнала пре ялвашш ш пинию 21. Эта команда помечена в памяти 8 как начальная, следовательно оыбор самой команды из памяти 6 по цепи 6г11-3-18-1 сопровождается выбором некоторой (не совпадающей с ней) информацией из памяти 8 по цепи 8-13-15-14-3-20-2 (фиг. 1). Информация из памяти 6 в памяти 8 при наличии соответствующих сигналов сопровождения запоминается в регистрах 41 и 40. При наличии готовностей блоков 6 и 8 трипгеры 28 и 27, усганавпиваются в еаиничное состояние, ранее сброшенные по началу интерфейсного сигнала занятость магистра пи . Сигналы с триггеров 28 и 27 поступают через элемент И 34 и элемент 39 задержки на синхровхоа триггера 29. К этому моменту времени на выходе блока сравнения сформирована иогическая единица, так как коды в регистрах 40 и 41 не совпадают. Триггер 29 устанавливается в единичное состояние, и, поскольку в исходном состоянии сигнал на линии 21 равен , срабатывает элемент И 33. К этому моменту времен, как указано в п.2, содер имое счетчиков 53 равно О следовательно, сигнал на выходе элемента ИЛИ-НЕ 43 имеет единичное значение. В реэупьтатё срабатывает элемент И 32, формирователь 37 и инфо Яу{ация с шины 20 загружается в счетчики 53. В то же время триггер 25 устанавливается в соо тояние, соответствующее отсутствию прерывания (О на инверсном выходе), что гарантирует поддержание догической единицы на выходе 21 независимо от сос тояния триггера 26. Команда 3, так же как и предыдущие, является стандартной командой типа Регистрн-память и выпоп няется аналогично. Адрес определяется дешифратором 24. Сигнал с выхода дешифратора поступает на установочный вход триггера 26 и, проходя по цепи ЗО 38-19-1, возвращается в процессор 1 в качестве ответного сигнала об окончании операции. Сигнал на пинии 21 сохраняет единичное значение. 4, Передать управление на начало рабочей программы. Управление передается первой команде рабочей программь, которая п(Яъ1ечена в памяти 8 как начапхг ная. Таким о дазом, переходная программа обеспечивает вхождение в синхронизм механизма выполнения рабочей программ с механизмом контротга. В отЪутствие внешних прерываний рас смотренный цикл работы устройства 2 периодически повторяется. При выборе начальной ксманды очередного линейного участка устанавливается в единицу триггер 29, срабать1вает элемент И 33, триггер 26 принимает информацию о правильнЬсги работы ЭВМ на предыдущем линейном участке, а сигнал по цепи 32-37-49-23 выа 1вает прием эталонной ннфо1п ации с шины 2О в счетчики 53, предопределяя работу ЭВМ на очередном линейном участке рабочей программы и т.д. При поступлении сигнала внешнего пре{я 1вания по одной из линий шины 19 процессор 1 завершает выполнение текущей команш и приступает к выполнению стандартной процедуры перехода к npejM iвающей программе. Эта процедура обычно выполняется на микропрограммном уровне и предусматривает, в частности, упрятывание в память (например в аппаратно реализованный стек) всей информации, необходимой для последующего возобно&ления работы по пpoгpaм e с прерванного места. К этой информации, в частности, относится и содержимое счетчиков 53. Счетчики 53 выполнены программно-доотупными. Чтение из счетчиков производятся при обращении по определенному адресу, который определяется дешифратором 24. Сигнал с его выхода поступает на вход 44 блока 23 и открывает передающие элементы 57 (фиг. 4), в результате чего информация с выходов 58 ячеек 56 поступает на шину 18 и затем в про цессор 1. Ответный сигнал завершения операции формируется по цепи; ЗО-3819-1. При работе прерывающей программы используются те же аппаратные средства контроля, что и при выполнении исходной (рабочей) программы. Выход из прерывающей программы, как обычно, сопровождается восстановлением всей необходимой информации, в частности содержимого счетчкков 53. Запись в счетчики информации с шины 18 производится при срабатывании управляющей цепи 17-24-36-51 (фиг. 2) и далее цепи 67-63-61 или 65-62-61 (фиг. 4) в зависимости от значения информационного разряда на соответствующей линии 59 шины 18. Далее управление передается прерванной программе. При выполнении стандартных процедур упрятывания - восстановления на шине 19 появляются лишние импульсы, не учтенные эталонным кодом, ранее иэвлеченным из памяти 8 и помещенным в счетчики 53. Однако принципиально возможно ввести соответствующие поправки при передаче кода из стека в счетчики 53, используя ари({ыетическое устройство процессора. Эти поправки зависят от конкретной реализации ЭВМ и закладываются в микропрограмму выхода из прер 1ванкя на этапе ее разработки. При обнаруж ении ошибки триггер 25 устанавливается в состояние, при котором на его инверсном выходе формируется погическая единица. Еспи при этом триггер 26 находится в разрешающем, т.е. в единичном, состоянии, то на выходе элемента И-НЕ 35 формируется сигнал логического нупя, Отрииатепьць й фронт сигнала с этого элемента по линии 21 поступает в процессор 1 и воспринимается им как сигнал пре{и 1вания от устройства 2, в то же время ну левой сигнал на линии 21 запирает элемент И 33 и блок 23 {элементы 54). Поэтому в счетчиках 53 сохраняется информация по состоянию на момент неудачной проверки, которая может быть прочитана по шине 18 и использована дл анализа причины ошибки. Получив сигнал прерывания от устройства 2, процессор 1 переходит иа соответствующую программу. Эта программа может предусматривать, например, вызов и выполнение диагностических программ, попытку повторного выполнения участка программы, на котором зарегист рирована ошибка, выдачу сообщений onepa тору, перезагрузку ЭВМ или какие-либ другие действия. В процессе выполнения этих программ можно, если это необходи мо, вновь разделить адресные пространст ва блоков 6 и 8, переключив триггер 73 по цепи 10-70-79-71-73, установить запрещающую маску, переключив триггер 26 по цепи 17-24-31-26, или перевести триггер 25 в состояние, соответствук щее отсутствию ошибки, переключив его по цепи 17-24-25. Возврат к прерванной (в связи с ошибкой) программе может производиться, начиная с некоторой точки повтора, помеченной как начало в памяти 8. Дня входа в эту программу может использоваться переходная программа. Емкость счетчика 53 может быть меньшей, чем та, которая необходима для регистрации полного числа импульсов. Пусть, например, ожидаемое чиспо импульсов равно 101002 -2 , а разрядность соответствующего счетчика - четырем (а не пяти). В этом случае в счетчик загружается код 01002 4 (старши разряд с весс 16 теряется). Поспе 20-кратной операции вычитания содержимое счетчика равно 0000, при этом Cttrwan заема теряется. Однако это не приводит к существенному снижению достоверности проверки. Не обнаруживаются птиь те ошибки, которые приводят к к появлению на соответствующей интерфейсной линии 3,36,52,63 и т.д. импульсов вместо ожидаемых 20, что маловероятно. Работа устройства поясняется времен. ной диаграммой (фиг. 7), на которой эпюры 90-92 отображают процесс загрузки (моменты времени 93 и 94) и постепенного уменьшения содержимого трех счетчиков 53.В моменты времени 93 и 94 содержимое всех трех счетчиков 53 ривно нулю, что соответствует правильной работе ЭВМ. На отрезке времени 93-94 один из счетчиков (эпюра 92) дважды переполняется, однако исходный код, загруженный в него в момент времени 93, выбран таким, чтобы к моменту времени 94 содержимое этого счетчика бы по равно нулю (счет по модулю). Импульсы 96 формируются на синхронизирующем )зхЪде триггера 25 в моменты 93-95 выхода ЭВМ на начала линейных участков, но после обнаружения ошибки (мшЕент времени 95) формирование этих импульсов прекращается и в счетчиках фиксируются значения на момент проверки. При обнаружении ошибки сигнал на аыходе 21 устройства 2 (эпюра 97) принимает нулевое значение. Из этого следует, что в течение отрезка времени 94-95 на одной из управляющих пиний интерфейса число зарегистрированных импупьсов оказалось меныиим, чем предсказадное при предварительном анализе программ (эпюра 9О не касается горизонтальной оси в момент времени 95). Использование изобретения позволяет контролировать шины управления ЭВМ,а также информационно-адресные шины; обеспечивать быструю реакцию на возникшую ошибку (сбой или отказ; время реакции на превыщает времени выполнения машиной элементарного.динейного участка программы); предотвращать возможность аварии управляемого объекта за счет устранения бесконтрольного блуждания ЭВМ по программе в результате ошибки (сбоя или отказа).

с.

Фitг. J

У553

99

I

. 1

9Z

9}

V

53

56

61

47

60

Mr

V

56

W

злементу 4S

58 59

-N

59

V

J/

nr

Фиг. ft

W

75

tf

1„

(

. 1

п

rr

ч.

п

«

JL М.

8S

12

.L-m89

- -|Wf-е ЩГ420

Фиг. 7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Подвесная канатная дорога | 1920 |

|

SU381A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-05-23—Публикация

1981-08-06—Подача