Изобретение относится к вычисли- тельной технике и технике связи может быть использовано в цифровых системах передачи, хранения и воспроизведения звуковых сигналов.

Цель изобретения - повышение точности преобразования при сохранении пропускной способности и упрощение устройства.

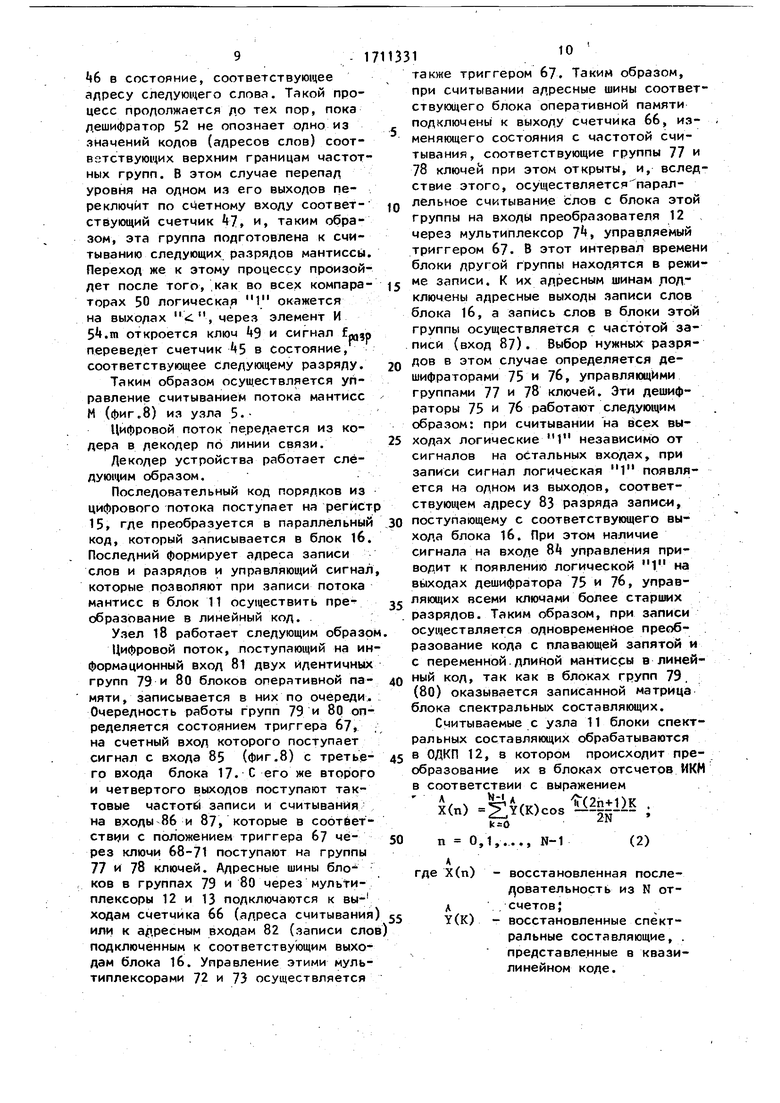

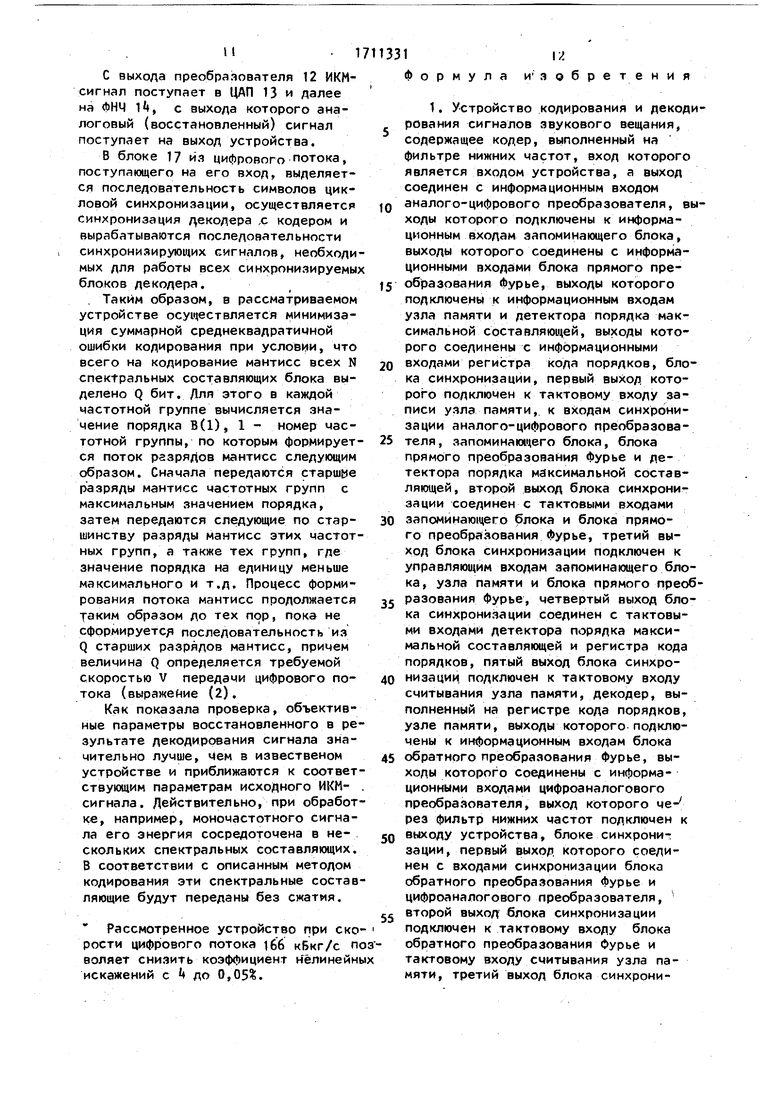

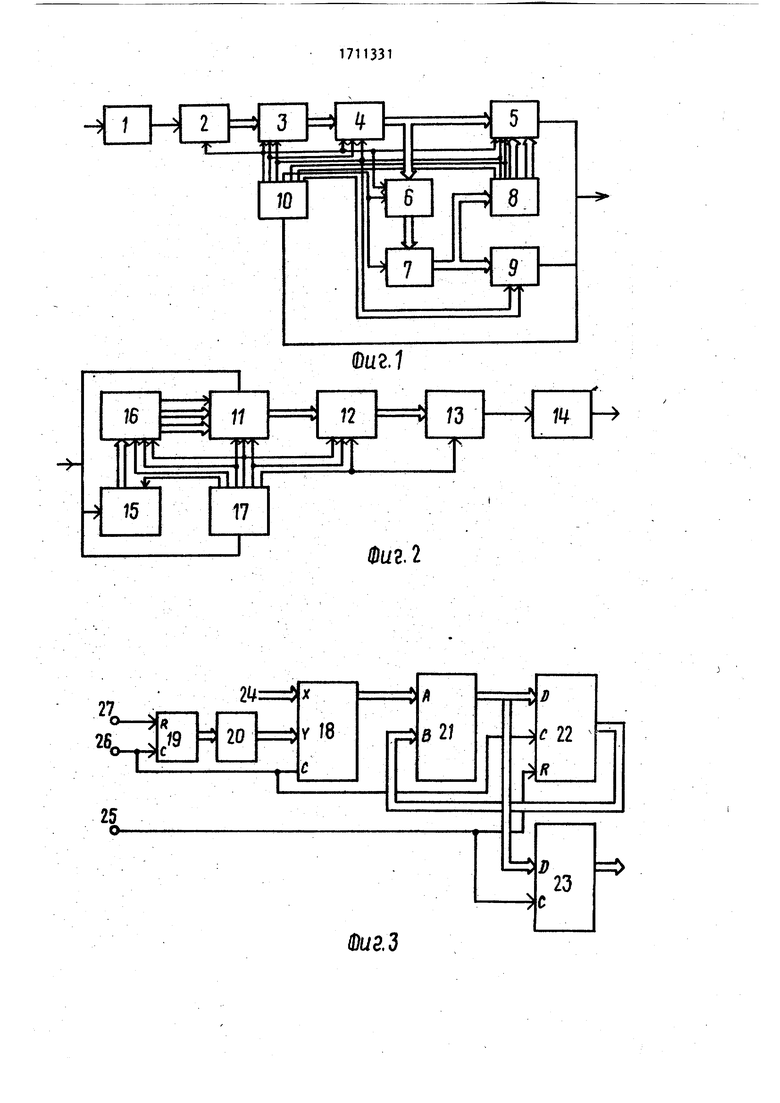

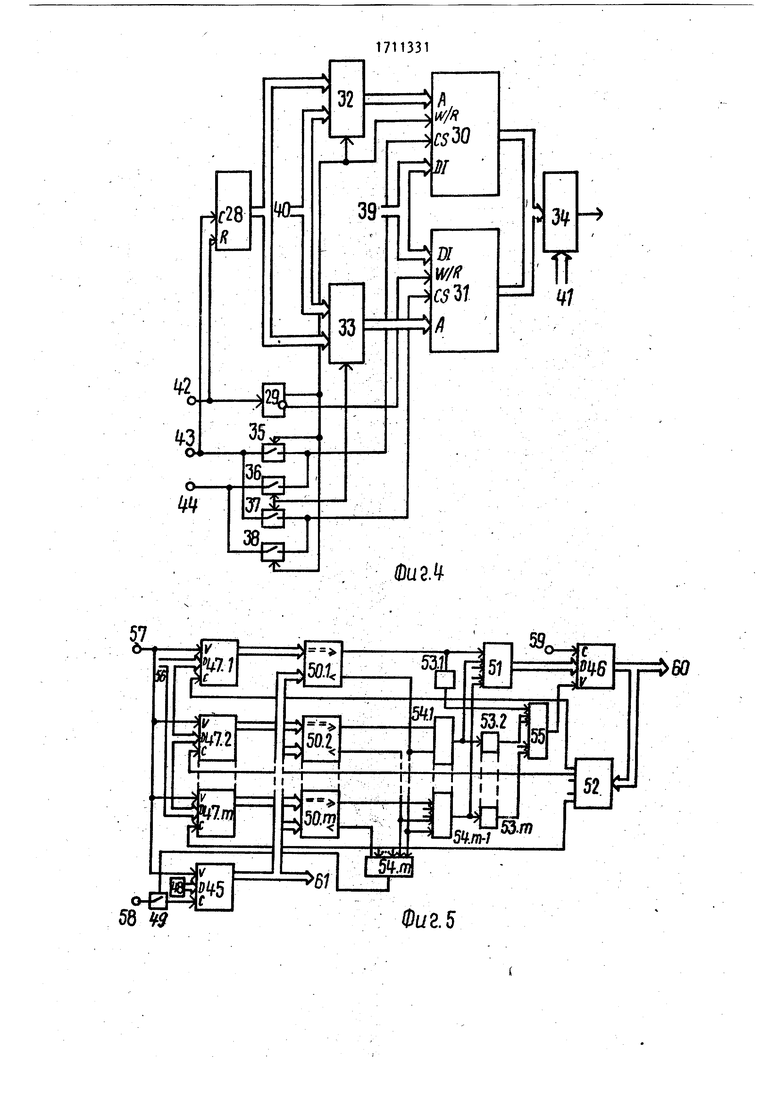

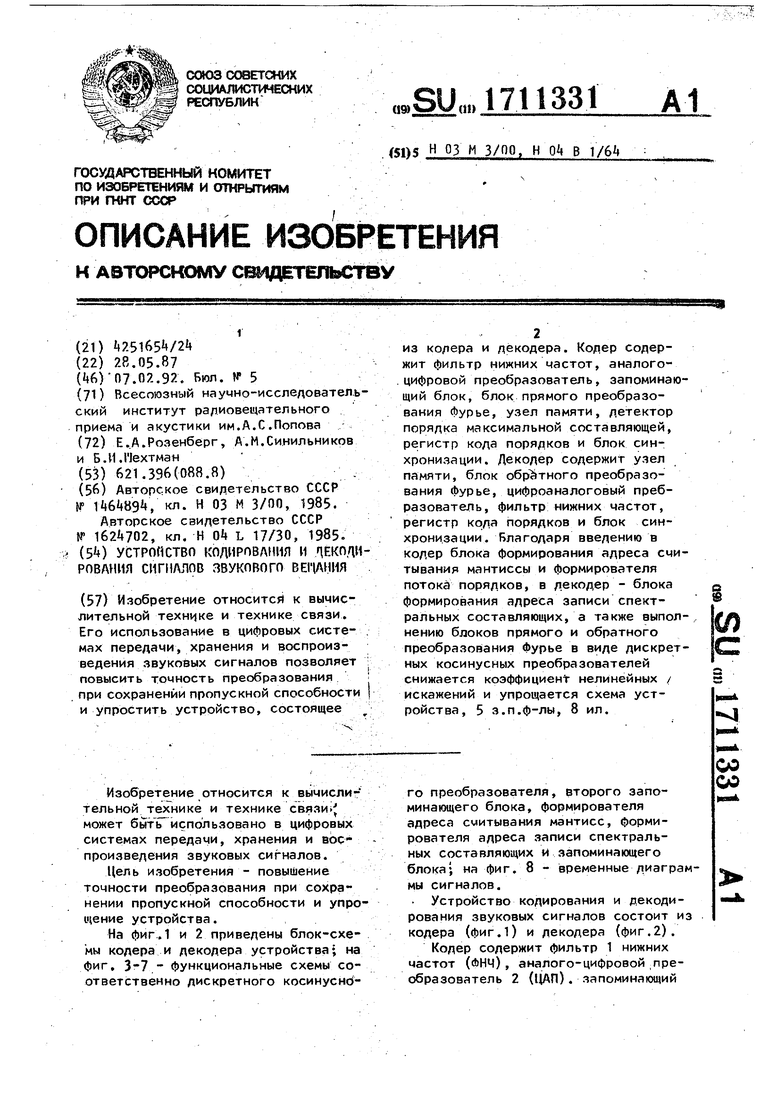

На фиг.. 1 и 2 приведены блок-схемы кодера и декодера устройства; на фиг. 3-7,- функциональные схемы соответственно дискретного косинуснбго преобразователя, второго запоминающего блока, формирователя адреса считывания мантисс, формирователя адреса записи спектральных составляющих и запоминающего блока1, на фиг. 8 - временные диаграммы сигналов.

Устройство кодирования и декодирования звуковых сигналов состоит из кодера (фиг.1) и декодера (фиг.2). Кодер содержит фильтр 1 нижних частот (НЧ), аналого-цифровой.преобразователь 2 (ЦАП). запоминающий

со оо

3

блок 3 блок Л прямого преобразования Фурье, узел 5 памяти, декодер 6 порядка максимальной составляющей регистр 7 кода порядков блок 8 формирования адреса считывания, формирователь 9 потока порядков и блок 10 синхронизации.

Декодер содержит узел 11 памяти, блок 1Ъ обратного преобразования Фурье, цифроаналоговый преобразователь 13 (ЦАП), ФНЧ И, регистр 15 кода порядка, блок 16 формирования адреса записи спектральных составляющих и блок 17 синхронизации.

Блок k прямого преобразования Фурье (фиг.З) выполнен как дискретный косинусный преобразователь и содержит перемножитель 18, счетчик 19 импульсов, блок 20 постоянной памяти, сумматор 21, первый и второй буферные регистры 22 и 23. На фиг.З обозначены информационные входы 2А, вход 25 синхронизации, тактовый вход 26 и управляющий вход 27.

Узел 5 памяти (фиг.А) содержит счетчик 28 импульсов триггер 29, первый и второй блоки 30 и 31 оперативной памяти, первый - третий мультиплексоры 32-31 и первый - четвертый ключи 35-38. На фиг. обозначены информационные входы 39 первые и вторые адресные входы 0 и И управляющий вход 2, тактовый вход Д3 записи и тактовый вход kb считывания.

Блок 8 формирования адреса считывания мантиссы (фиг.5) содержит первый и второй счет.чики 5 и 6 импульсов, группу 4 7 счетчиков импульсов, источник 48 постоянного кода, ключ 49, компараторы 50, шифратор дешифратор 52, формирователи 53 импульсов, элементы И 54 и элемент ИЛИ 55. На фиг.5 обозначены информационные входы 56, вход 57

I ZlX(n), при К

5

0

синхронизации, счетный вход 58, тактовый вход 59, первые и вторые выходы 60 и 61.

Формирователь 9 потока порядков реализуется на сдвиговом регистре.

Остальные блоки кодера выполнены как в известном устройстве.

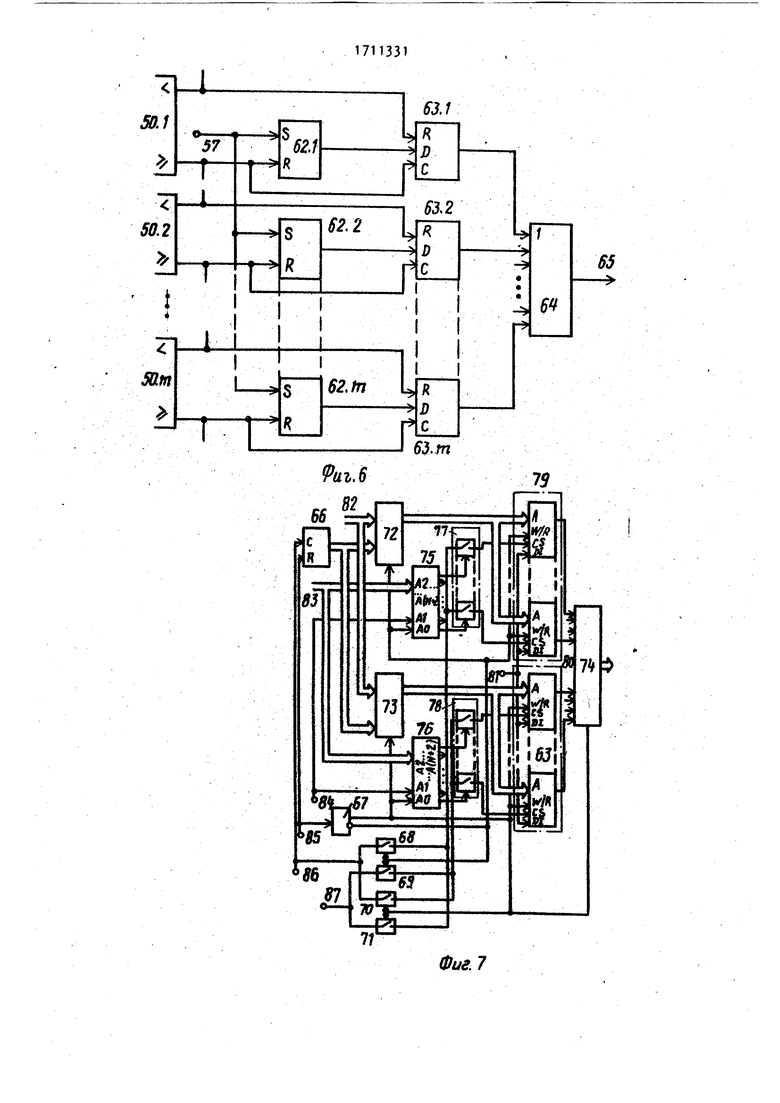

Блок 16 формирования адреса записи спектральных составляющих (фиг.5 и.6) содержит те же элементы 5-55, что и блок 8 кодера, а кроме того первую и вторую группы 62 и 63 триггеров и второй элемент ИЛИ 64, выход которого является третьим выходом 65 блока 16.

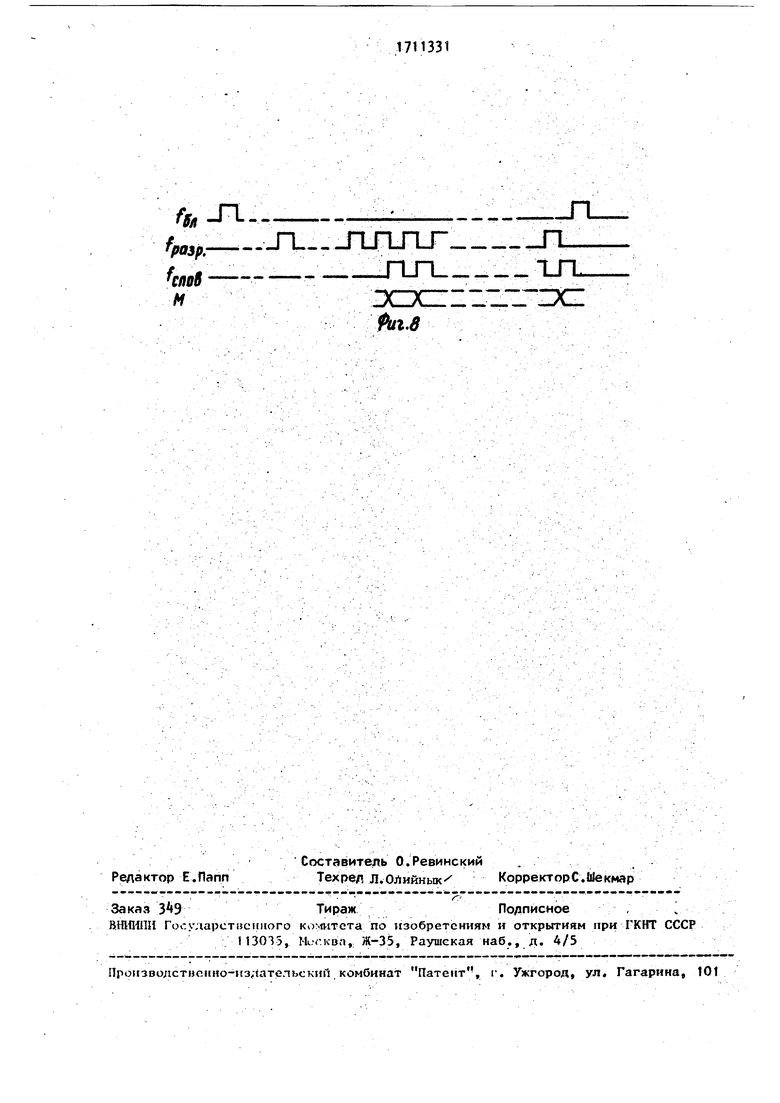

Узел 11 памяти содержит (фиг,7) счетчик 66 импульсов, триггер 67, первый -четвертый ключи 68-71, пер- вый - третий мультиплексоры 72-7, первый и второй дешифраторы 75 и 76, первую и вторую группы 77 и 78 ключей, первую и вторую группы 79 и 80 блоков оперативной памяти. На фиг.7 5 обозначены информационный вход 81, первые и вторые адресные входы 82 и 83, вход 84 смены режимов, управляющий вход 85, тактовый вход 86 считывания и тактовый вход 87 записи.

Блок 12 обратного преобразования Фурье выполнен как обратный дискретный косинусный преобразователь и реализуется аналогично блоку 4 кодера.

Остальные блоки декодера выполнены так же как в известном устройстве.

Кодер устройства работает следующим образом.

Аналоговый сигнал через ФНЧ 1 поступает на АЦП 2, в Кхотором осущест- 0 вляетея линейное ИКМ-преобразование. Далее сигнал с выхода АЦП 2 поступает на блок 3, в котором происходит запоминание блоков отсчетов ИКМ. В преобразователе 1 эти блоки преобра- 5 зуются в блоки спектральных составляющих в соответствии с выражением

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования сигналов звукового вещания | 1990 |

|

SU1774500A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Цифровой компандер | 1986 |

|

SU1427575A1 |

| Преобразователь кода спектра звукового сигнала | 1990 |

|

SU1800618A1 |

| Устройство для вычисления скользящего спектра | 1983 |

|

SU1095188A1 |

| Процессор быстрого преобразования Фурье | 1987 |

|

SU1425709A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

Изобретение относится) к вычислительной технике и технике связи. Его использование в цифровых системах передачи, хранения и воспроизведения звуковых сигналов позволяет . повысить точность преобразования j при сохранении пропускной способности j и упростить устройство, состоящее гиз колера и декодера. Кодер содержит фильтр нижних частот, аналого- .цифровой преобразователь, запоминающий блок, блок прямого преобразования Фурье, узел памяти, детектор порядка максимальной составляющей, регистр кода порядков и блок синхронизации. Декодер содержит узел памяти, блок обратного преобразования Фурье, цифроаналоговый преб- разователь, фильтр нижних частот, регистр кода порядков и блок синхронизации. Благодаря введению в кодер блока формирования адреса считывания мантиссы и формирователя потока порядков, в декодер - блока формирования адреса записи спектральных составляющих, а также выполнению блоков прямого и обратного преобразования Фурье в виде дискретных косинусных преобразователей снижается коэффициент нелинейных / искажений и упрощается схема устройства, 5 з.п.ф-лы, 8 ил. с

Ч(К)

де Х(п) Y(X)(K

ми

/v

,, ,п,«

отсчеты, входящие в обрабатываемый блок; 0,1,...,N-1) - коэффициенты /ЖП, которые представляют мгно55

Отли ского с что отр

(1)

1,2,...,N-1

венный спектр обрабатываемого., сигнала .

Отличие спектра ЛКП от классического спектра Фурье-(состоит в том, что отрезок сигнала раскладывается

по набору ортогональных гармонических сигналов вила cos( -НА,) с

К /v

(I Ч

безразмерными частотами f . ---К.fj

(у классического преобразования Фус 2frKv рье частоты f.u ---) и фазами

1Гк

и ™- в отличие от классическо ZN

кого преобразования Фурье,не зависящими от обрабатываемой последовательности отсчетов. При этом коэффициенты /ЖП -вещественные числа (коэффициенты Фурье - комплексные), а разрешающая способность по частоте у ДКП равна &f F/2N, F - частота дискретизации, и в два раза выше, чем у классического преобразования Фурье при одной и той же длине обрабатываемого блока. По этой причине повышается эффективность спектрального преобразования, так как спектральные составляющие снимаются чаще и, следовательно, спектр /1ПК ближе к естественному, а также упрощается аппаратурная реализация кодера и декодера, так как для вещественных составляющих в отличие от комплексных требуется только один канал обработки.

Работа преобразователя заключается в последовательном вычислении значений спектральных составляющих блока. При этом для каждой составляющей производится перемножение перемножителем 18 значений всех отсчетов блока ИКМ, поступающих на - входы 2k с блока 3 на соответствующие значения косинусов, записанных в блок 20 постоянной памяти и поступающих на другие входы перемножите- л,я 18. Результаты перемножения складываются в сумматоре 21, при этом в регистре 22 фиксируются промежуточные сложения, а в регистре 23 - значения каждой спектральной составляющей. Адресация блока 20 осуществляется счетчиком 19, на входы которого поступают синхросигналы с блока 10: на входы 26 - тактовая частота умножения и сложения, нэ вход 27 - частота смены блоков, а на вход 25 поступают синхросигналы с частотой дискретизации, которые фиксируют результат вфегистре 23 и обнуляют регистр промежуточного результата 22. Эти сигналы могут быть получены не с блока 10, а с

выхода соответствующего разряда счетчика 19;

Каждый блок из N спектральных составляющих разбивается на частотные группы, соответствующие критическим полосам слуха, и записываются в узел 5. В частотных группах спектральные составляющие представляются в формате кода с поблочно-плавающей запятой, при этом длина мант тисе в частотных группах переменна. Блоки спектральных составляющих, поступающие.с информационных входов

5 39 на два идентичных блока 30 и 31 оперативной памяти, записываются в них по очереди. Очередность работы узлов 30 и 31 определяется состоянием триггера 29, на счетный вход

0 которого (вход 2) поступает частот та смены блоков с третьего выхода

блока 10. С его же первого и пято- го выходов на входы 3 и М посту- пают тактовые частоты записи и

считывания, которые в соответствии с положением триггера 29 через ключи 35-38 поступают на соответствующие : входы обращения блоков 30 и 31. Адресные шины блоков 30 и 31 подклю0 чаются через мультиплексоры 32 и 33 к выходам счетчика 28 (адреса записи) или к первым адресным вхо- ,: дам 0 (считывания слоя) , подключенным к первым выходам блока 8. Уп5 равление этими мультиплексорами осуществляется также триггером 29. Таким образом, при записи адресные шины соответствующего блока 30 или 31 подключены к выходу счетчика 28, ;

0 изменяющего состояние с частотой записи. При этом осуществляется параллельная запись слов в этот блок 30 и 31 с выхода преобразователя 4. Другой блок 31(30) находится в режи5 ме считывания. К его адресным шинам подключены адресные выходы считывания слов блока 8 и считывание слов этого блока осуществляется с частотой считывания. Выбор из счи0 тываемого слова нужного разряда осуществляется мультиплексором 3, уп- равляемым по входам 1 с вторых адресных выходов (считывания разрядов) блока 8.

5 Таким образом, при считывании осуществляется формирование последовательного потока из матрицы блока спектральных составляющих. Скорость

т 171

этого потока (длина блока мантисс) определяется количеством импульсов частоты считывания f, -бит/с:

v.-jl a-KMf+q) (2)

где L - количество частотных групп

(обычно выбирают L 24)i К - разрядность порядка (при 16-разрядном коде спектральных составляющих Кпор 4), Q - число бит, выделенных для кодирования мантисс всех N спектральных составляющих блока. .-

Одновременно в детекторе о определяются значения порядков максимальных составляющих для каждой группы спектральных составляющих и аапо- минаются в регистре 7. Таким образом, по окончании цикла записи блока спектральных составляющих в блоке 5 на выходе регистра 7 зафиксированы значения порядков групп этого блока спектральных составляющих. Далее осуществляется запись следующего блока в узел 5 и его обработка в детекторе 6 и регистре 7 и последовательное, считывание из узла 5 потока мантисс в соответствии с адресными сигналами„ вырабатываемыми блоком 8, и потока порядков из формирователя 9. Адресные сигналы, выработанные в блоке 8, соответствуют зафиксированным в нем значениям порядков блока спектральных составляющих по окончании цикла записи данного блока. В формирователе 9 осуществляется параллельно-последовательное преобразование кода порядков блока спектральных составляющих.

Блок 8 формирует адреса считывания слов и разрядов для блока 5 таким образом, чтобы при считывании осуществлялось преобразование в коде плаваю- щей запятой и переменной ллйной ман- тиссы. Блок 8 формирования адреса считывания мантисс работает следующим образом.

При поступлении на вход 57 импуль- са (fgd, фиг.8) частоты смены блоков с третьего выхода блока 10 осущест-; вляется параллельная запис ь в вычитающие счетчики порядков групп спектральных составляющих и в вычитающий счетчик 45 адреса считывания разряда, при этом, в счетчики 47 со входов 56 осуществляется запись порядков с регистра.2, а в счетчик 45 - с источни8

ка 48 постоянного кода. Состояние счетчиков 47 сравнивается с состоянием счетчика 45 компараторами 50. При этом, так как на выходе счетчика 45 максимальное значение кода порядка (адрес старшего разряда блока 5), то уровень логической 1 появляется на большинстве (или на всех) выходах компараторов 50. В зависимости от этого элемент И 54.ro вырабатывает управляющий сигнал на элетронный ключ 49. В том случае, если в блоке спектральных составляющих нет групп с максимальным значением порядка, ключ 49 открыт и с входа 58 через него на тактовый вхо/ч счетчика 45 поступают импульсы (фиг.8) с шестого входа блока 10. Изменение состояния счетчика 45 происходит до тех пор, пока не наступит равенство хотя бы в одном из компараторов 50. Тогда изменится состояние элемента И 5.го и ключ 49 закроется, при это состояние счетчика 45 будет соответствовать максимальному значению порядка группы в считываемом блоке и, таким образом, будет установлен адрес первого из считываемых разрядов. Кроме того, при равенстве хотя бы в одном из компараторов 50 произой- дет параллельная запись в счетчик 46 адреса считывания слов. Такт записи вырабатывается узлом, состоящим из т-1 элемента И 5, формирователей 53 импульсов и элемента ИЛИ 55. Назначение узла - выработать такт записи при появлении логической 1м на выходе в одном из компараторов 50, а также в том случае, если эта 1м исчезает, но она есть в каком-либо из других компараторов 50. Код, записываемый в счетчик 46, определяется дешифратором 51. Этот дешифратор может -быть выполнен, например, на ПЗУ, в котором записаны нижние границы частотных групп ( адресов слов). Элементы И 54.1-54.(го-1) обеспечивают очередность установки адресов слов в тех случаях, когда уровень логической 1 появляется на выходах нескольких компараторов 50. Таким образом, еще до появления на входе 59 счетчика 46 Јл.п11(фиг.8)

. -СЛО 6

на его выходе 60, подключенном к входу 40 блока 5, уже установлен адрес считывания слова и первый импульс, который осуществляет считывание в блок 5, переводит счетчик

6 в состояние, соответствующее адресу следующего слова. Такой процесс продолжается до тех пор, пока дешифратор 52 не опознает одно из значений кодов (адресов слов) соответствующих верхним границам частотных групп. В этом случае перепад уровня на одном из его выходов переключит по счетному входу соответствующий счетчик kl, и, таким образом, эта группа подготовлена к считыванию следующих разрядов мантиссы. Переход же к этому процессу произойдет после того, ,как во всех компара

торах 50 логическая 1 окажется на выходах «с, через элемент И 5.т откроется ключ 9 и сигнал Јда« переведет счетчик А5 в состояние, соответствующее Следующему разряду.

Таким образом осуществляется управление считыванием потока мантисс М (фиг„8) из узла 5.Цифровой поток передается из кодера в декодер по линии связи.

Декодер устройства работает следующим образом.

Последовательный код порядков из цифрового потока поступает на регист 15, где преобразуется в параллельный код, который записывается в блок 16. Последний формирует адреса записи слов и разрядов и управляющий сигнал которые позволяют при записи потока мантисс в блок 11 осуществить npe-v образование в линейный код.

Узел 18 работает следующим образо

Цифровой поток, поступающий на информационный вход 81 двух идентичных групп 79 и 80 блоков оперативной памяти, записывается в них по очереди. Очередность работы групп 79 и 80 определяется состоянием триггера 67, на счетный вход которого поступает сигнал с входа 85 (фиг.8) с третьего входа блока 17. С его же второго и четвертого выходов поступают тактовые частотй записи и считывания на входы 86 и 87, которые в соответствии с положением триггера 67 через ключи 68-71 поступают на группы 77 и 78 ключей. Адресные шины бло г ков в группах 79 и 80 через мультиплексоры 12 и 13 подключаются к вы- ходам счетчика 66 (адреса считывания или к адресным входам 82 (записи сло подключенным к соответствующим выходам блока 16. Управление этими мультиплексорами 7.2 и 73 осуществляется

7П33110

также триггером 67. Таким образом, при считывании адресные шины соответствующего блока оперативной памяти подключены к выходу счетчика 66, изменяющего состояния с частотой считывания, соответствующие группы 77 и

10

15

20

25

30

35

р ,

м

5$ )

40

50

78 ключей при этом открыты, и, вследствие этого, осуществляется парал- лельное считывание слов с блока этой группы на входы преобразователя 12 , через мультиплексор 7 управляемый триггером 67. В этот интервал времени блоки другой группы находятся в режиме записи. К их адресным шинам подключены адресные выходы записи слов блока 16, а запись слов в блоки этой группы осуществляется с частотой записи (вход 87). Выбор нужных разрядов в этом случае определяется дешифраторами 75 и 76, управляющими группами 77 и 78 ключей. Эти дешифраторы 75 и 76 работают следующим образом: при считывании на всех выходах логические 1 независимо от сигналов на остальных входах, при записи сигнал логическая 1 появляется на одном из выходов, соответствующем адресу 83 разряда записи, поступающему с соответствующего выхода блока 16. При этом наличие сигнала на входе 81 управления приводит к появлению логической 1 на выходах дешифратора 75 И 76, управляющих всеми ключами более старших разрядов. Таким образом, при записи осуществляется одновременное преоб- ; разование кода с плавающей запятой и с переменной.длиной мантиссы в линейный код, так как в блоках групп 79. (80) оказывается записанной матрица блока спектральных составляющих.

Считываемые с узла 11 блоки спектральных составляющих обрабатываются 45 в ОДКП 12, в котором происходит преобразование их в блоках отсчетов ИКМ в соответствии с выражением

J(n) (K)cos tЈ2g1lK .

. ЈN

0,1,..,, N-1

n

(2)

X(n)

Y(K)

-восстановленная последовательность из N от. счетов;

-восстановленные спектральные составляющие, . представленные в квазилинейном коде.

11

С выхода преобразователя 12 ИКМ- сигнал поступает в ЦАП 13 и далее на ФНЧ 1, с выхода которого аналоговый (восстановленный) сигнал поступает на выход устройства.

В блоке 17 из цифрового потока, поступающего на его вход, выделяется последовательность символов цикловой синхронизации, осуществляется синхронизация декодера ,с кодером и вырабатываются последовательности синхронизирующих сигналов, необходимых для работы всех синхронизируемых блоков декодера.

Таким образом, в рассматриваемом устройстве осуществляется минимизация суммарной среднеквадратичной ошибки кодирования при условии, что всего на кодирование мантисс всех N спектральных составляющих блока выделено Q бит. Для этого в каждой частотной группе вычисляется значение порядка В(1), 1 - номер частотной группы, по которым формируется поток разрядов мантисс следующим образом. Сначала передаются старшие разряды мантисс частотных групп с максимальным значением порядка, затем передаются следующие по старшинству разряды мантисс этих частотных групп, а также тех групп, где значение порядка на единицу меньше максимального и т.д. Процесс формирования потока мантисс продолжается таким образом до тех пор, пока не сформируется последовательность из Q старших разрядов мантисс, причем величина Q определяется требуемой скоростью V передачи цифрового потока (выражение (2).

Как показала проверка, объективные параметры восстановленного в результате декодирования сигнала значительно лучше, Мем в извественом устройстве и приближаются к соответствующим параметрам исходного ИКН- . сигнала. Действительно, при обработке, например, моночастотного сигнала его энергия сосредоточена в нескольких спектральных составляющих. В соответствии с описанным методом кодирования эти спектральные составляющие будут переданы без сжатия.

Рассмотренное устройство при ско- рости цифрового потока 166 кБкг/с по воляет снизить коэффициент нелинейны искажений с 1 до 0,05%.

х

. -оз ых

1331 -л

Формула изобретения

JQ аналого-цифрового преобразователя, выходы которого подключены к информационным входам запоминающего блока, выходы которого соединены с информационными входами блока прямого пре15 образования Фурье, выходы которого подключены к информационным входам узла памяти и детектора порядка максимальной составляющей, выходы которого соединены с информационными

20 входами регистра кода порядков, блока синхронизации, первый выход которого подключен к тактовому входу записи узла памяти, к входам синхронизации аналого-цифрового преобразова25 теля, заломи на кчцего блока, блока прямого преобразования Фурье и детектора порядка максимальной составляющей, второй выход блока синхронизации соединен с тактовыми входами

30 запоминающего блока и блока прямого преобразования Фурье, третий выход блока синхронизации подключен к управляющим входам запоминающего блока, узла памяти и блока прямого преоб35 разования Фурье, четвертый выход блока синхронизации соединен с тактовыми входами детектора порядка максимальной составляющей и регистра кода порядков, пятый выход блока синхро40 низации подключен к тактовому входу считывания узла памяти, декодер, выполненный на регистре кода порядков, узле памяти, выходы которого подключены к информационным входам блока

45 обратного преобразования Фурье, выходы которого соединены с информационными входами цифроаналогового преобразователя, выход которого че- рез фильтр нижних частот подключен к

50 выходу устройства, блоке синхронизации, первый выход которого соединен с входами синхронизации блока обратного преобразования Фурье и цифроаналогового преобразователя,

се второй выход блока синхронизации подключен к тактовому входу блока обратного преобразования Фурье и тактовому входу считывания узла памяти, третий выход блока синхрони13

яации соединен с управляющими входами блока обратного преобразования Фурье и узла памяти, четвертый выход блока синхронизации подключен к тактовому входу записи узла памяти, отличающееся тем, что, с целью повышения точности преобразования при сохранении пропускной способности и упрощения устройства, в него введены: в кодер - блок формирования адреса счи- тывания мантисс и формирователь ...-,, потока порядка, входы синхронизации которых объединены и подключены к третьему входу блока синхронизации, тактовый вход блока формирования адреса считывания мантисс подключен к пятому выходу блока синхронизации, шестой и седьмой выходы которого соединены соответственно со счетным входом блока формирования адреса считывания мантисс и тактовым входом формирователя потока порядка, выходы регистра кода порядков подключены к информационным входам формирователя потока порядка и блока формирования адреса считывания мантисс, первые и вторые выходы которого соединены содноименными адресными входами узла памяти, выход которого объединен с выходом формирователя потока порядков и восьмым выходом блока синхронизации и является выходом кодера,, блоке прямого преобразования Фурье выполнен как дискретный косинусный преобразователь, в декодер введен блок формирования адреса записи спектральных составляющих, вход синхронизации и тактовый вход которого подключены соответственно к третьему и четвертому выходам блока синхронизй- ции, пятый и шестой выходы которого соединены соответственно со счетным входом блока формирования адреса записи спектральных составляющих и тактовым входом регистра кода порядков, вход которого объединен с информационным входом узла памяти и входом блока синхронизации и является входо декодера, выходы регистра кода порядков соединены с информационными входми блока формирования адреса записи спектральных составляющих, первые - третий выходы которого подключены -, соответственно к первым и вторым адресным входам и входу смены режимов узла памяти, блок обратного преобра

U ,

зования Фурье выполнен как обратный дискретный косинусный преобразовать

0

5

0

5

5

0

5

0

5

k. Устройство по п.1, о т ли - чающееся тем, что блок формирования адреса считывания мантиссы содержит первый и второй счетчики импульсов, ключ, дешифратор, шифратор j элемент ИЛИ, группу из m счетчиков импульсов (т - число кодов порядков), m-компараторов, m формирователей импульсов, m элементов И и источник постоянного кода, выходы которого соединены с информационными входами первого счетчика импульсов, вход разрешения записи которого объединен с входами разрешения записи . счетчиков импульсов группы и. является входом синхронизации блока, информационные входы счетчиков импульсов группы соответственно объединены и являются информационными входами блока, выходы 1-го счетчика импульсов группы (,го) соединены с первыми входами 1-го компаратора, выход Больше.или равно первого компаратора подключен к входу формирователя импульсов и первому входу шифратора, выход Меньше 1-го ком-, паратора соединен с i-ми входами (i-tn)-ro элементов И, выход Больше или равно j-ro компаратора (j 2,m) подключен к j-му входу (j-l)-ro элемента И, выход которого соединен с j-м входом шифратора и входом j-ro формирователя импульсов, выходы всех формирователей импульсов подключены к соответствующим входам элемента ИЛ выход которого соединен с входом разрешения записи второго счетчика импульсов, счетный вход которого яв

0

5

0

5

0

5

0

5

ляется тактовым входом блока, выход т-го элемента И подключен к управляющему входу ключа, информационный вход которого является счетным входом блока, выходы шифратора соединены с информационными входами второго счетчика импульсов, выходы которого подключены к входам дешифратора и являются первыми выходами блока, 1-й выход дешифратора (,m) соединен со счетным входом 1-го счетчика импульсов группы, выход ключа соединен со счетным входом первого счетчика импульсов, выходы которого подключены к соответствующим вторым входам компараторов и являются вторыми выходами блока.

10

15

рователеи импульсов подключены к соответствующим входам первого элемента ИЛИ, выход которого соединен с входом разрешения записи второго счетчика импульсов, счетный вход которого является тактовым входом блока, выход m-го элемента И подключен к управляющему входу ключа, информационный вход которого является счетным входом блока, выходы шиф ратора соединены с информационными входами второго счетчика, выходы которого подключены к- входам дешиф- ратора и являются первыми выходами / блока, i-й выход дешифратора (,га) соединен со счетным входом 1-го счетика импульсов группы, выход ключа - со счетным входом первого счетчика импульсов, выходы которого подключе- 20 ны к соответствующим вторым входам компараторов и являются вторыми выходами блока, выход ir-ro триггера . первой группы подключен к D-входу 1-го триггера второй группы, выход 25 которого соединен с входом второго элемента ИЛИ, выход которого является третьим выходом блока.

10

15

2025

7И33118

ния узла, информационные входы вто- рого и четвертого ключей объединены и являются тактовым входом записи узла, выходы счетчика импульсов соединены с вторыми информационными входами первого и второго мультиплексоров, выходы которых подключены к адресным входам блоков оперативной памяти одноименной группы, прямой выход триггера соединен с управляющими входами второго и третьего мультиплексоров, блоков оперативной памяти второй группы, третьего и четвертого ключей и входом нулевого разряда входов второго дешифратора , инверсный выход триггера подключен к управляющим входам первого мультиплексора, блоков оперативной памяти первой группы, первого и второго ключей и входу нулевогос разряда первого дешифратора, входы первого и последующих разрядов которого объединены с одноименными входами разрядов второго дешифратора и являются соответственно входом смены режимов и вторыми адресными входами узла, выходы первого, четвертого и второго, третьего ключей соответственно объединены и подключены к информационным входам ключей соответственно первой и второй групп информационные входы всех блоков оперативной памяти обеих групп объеди-. нены и являются информационным входом блока, i-й выход каждого дешиф- ратора (,т) соединен с управляющим входом 1-го ключа одноименной группы, выход которого подключен к входу синхронизации 1-го блока опе- ративной памяти одноименной группы, выход которого соединен с i-м входом одноименной группы информационных входом третьего мультиплексора, выходы крторого являются выходами блока.

ft/а З

58 #

Фиг. 7

гц -п.--- ; ---

...TU- TL . п :пt п.

f . А л :........ - .j...

| Авторское свидетельство СССР , кл- Н 03 М 3/00, 1985 | |||

| Авторское свилетельство СССР № , кл | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| ( УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ СИГНАЛОВ ЗВУКОВОГО ВЕЦАНИЯ | |||

Авторы

Даты

1992-02-07—Публикация

1987-05-28—Подача