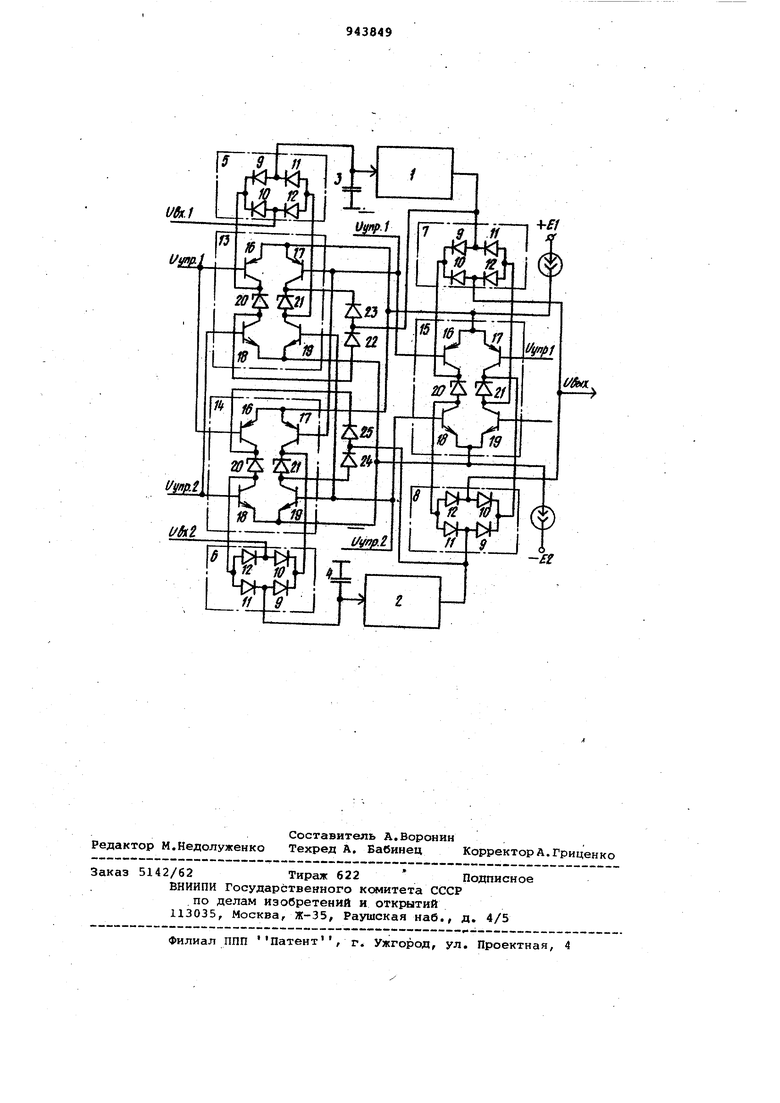

ной коммутаторы, каждый из которых выполнен на первом и втором транзисторах одного типа проводимос ти, третьем и четвертом транзисторах другого типа проводимости и двух стабилитронах, катоды которых подключены к коллекторам первого и второго транзисторов, а аноды к коллекторам третьего и четвертого транзисторов, ко второй диаго,нали первого ключа подключены катод (первого и анод второго стабилитронов входного коммутатора, к первым диагоналям третьего и четвертого ключей подключены выходы буферных усилителей и выход устройства, к второй диагонали третьего ключа под ключен катод первого и анод второго стабилитронов выходного коммутатора а анод первого и катод второго ста билитронов подключены к второй диа- гонали четвертого ключа, эмиттеры транзисторов коммутаторов соединены с шинами питания, базы транзисто ров подключены к шинам управления, введены дополнительный комму1атор и элементы с йелинейной характеристикой, например диоды, анод первого из которых соединен с анодом первого стабилитрона входного коммутатора, катод первого диода подключен к выходу первого буферного усилителя и аноду второго диода, катод которого соединен с катодом второго стабилитрона входного коммутатора, анод третьего диода соединен с анодом второго стабилитрона дополнительного коммутатора, катод третьего диода подключен к выходу второго буферного усилителя и к аноду четвертого диода, катод которого соединен с катодсял первого стабилит на дополнительного коммутатора, ано ды третьего и четвертого диодов вто рого ключа соединены с анодом перво го стабилитрона дополнительного ком мутатора, катоды первого и третьего диодов второго ключа соединены с катодом второго стабилитрона дополнительного коммутатора, базы транзисторов которого подключены к шина управления, а эмиттеры - к шинам пи тания. На чертеже представлена принципиальная схема аналогового запомина ющего устройства. Аналогов-ое запоминающее устройст во содержит первый и второй буфервые усилители 1 и 2, накопительные элементы, например конденсаторы 3 и 4, ключи 5-8, выполненные по мостовой схеме на диодах 9-12, входные и выходной коммутаторы 13-15, каждый из которых выполнен на перво и втором транзисторах 16 и 17 од-, ного типа проводимости, третьем и четвертом транзисторах 18 и 19 другого типа проводимости и двух стабилитронах 20 и 21, элементы с нелинейной характеристикой, например диоды 22-25. Аналоговое запоминающее устройство работает следующим образом. При подаче управляющих сигналов DnPi и .. открываются первый и четвертый транзисторы 16 и 19, входных коммутаторов 13 и 14 и второй и третий транзисторы 17 и 18 выходного коммутатора 15. 8результате обеспечивается открытое состояние первого и второго диодов 22 и 23 и закрытое - третьего и четвертого диодов 24 и 25, а также замкнутое состояние второго и третьего ключей 6 и 7 и разомкнутое первого и четвертого ключей 5 и 8. Следовательно, на конденсаторе 4 повторяется напряжение Ug , поступающее на второй вход устройства, а на выход устройства через буферный усилитель 1 и ключ 7 поступает напряжение с конденсатора 3, уровень которого соответствует значению сигнала на первом входе устройства Ug в момент подачи указанных управляющих сигналов. Напряжение с выхода буферного усилителя 1 подается также через диоды 22 и 23 на входной коммутатор 13 для фиксации уровней напряжений запирания диодов 9и 11 первого ключа 5. При подаче управляющих сигналов другой фазы, т.е. когда Uynp-i U,,npi и I открываются второй и третий транзисторы 17 и 18 входных коммутаторов 13 и 14 и первый и четвертый транзисторы 16 и 19 выходного коммутатора 15. В результате обеспечивается закрытое состояние диодов 22 и 23 и открытое - диодор 24 и 25, а также разомкнутое состояние второго и третьего ключей 6 и 7и замкнутое - первого и четвертого ключей 5 и 8. В этом случае на конденсаторе 3 повторяется напряжение Ugj , поступающее на первый вход устройства, а на выход устройства через буферный усилитель 2 и ключ 8 поступает напряжение с конденсатора 4, уровень которого соответствует значению сигнала на втором входе устройства в момент изменения фазы управляющих сигналов. I . . ,, Напряжение с выхода буферного усилителя 2 подается также через диоды 24 и 25 на входной коммутатор 14 для фиксации уровней напряжений запира1ния диодов 9 и 11 второго ключа 6. Из сказанного следует, что при. равенстве (с заданной точностью) напряжений на стабилитронах 20 и 21 и диодах 22 и 23, 24 и 25 запирающие напряжения на первом и третьем диодах 9 и 11 ключей 5 и 6 равны по величине И не зависят от текущих значений си налов Ugx и Upjjj, поступающих на входы аналогового запоминающего уст ройства. Следовательно, напряжения на конденсаторах 3 и 4 на этапе хра нения не изменяются при изменении напряжений на входах устройства, т точность работЁ устройства оказывае ся вьзше по сравнению с известным ус ройством. Таким образом, введение дополнительногЬ коммутатора и элементов с нелинейной характеристикой, например диодов, позволяет по сравнению с базовым устройством уменьшить на этапе хранения пролезание на вы ход устройства входных сигналов с десятков милливольт до долей милливольт. Это позволяет повысить точность аналогового запоминающего уст ройства и использовать его в аналог цифровых преобразователях при кодир вании быстро флюктуирующих сигналов. Формула изобретения Аналоговое запоминающее устройст во, содержащее первый и второй буферные усилители, входы которых сое динены соответственно с накопитель.ными элементами, например с одними из обкладок конденсаторов, другие обкладки которых подключены к шине нулевого потенциала, ключи, выполненные по мостовой диодной схеме, причем к первым диагоналям первого И второго ключей подключены соответственно вход первого буферного усилителя и первый вход устройства вход второго буферного усилителя и второй вход устройства, входной и выходной коммутаторы, каждый из которых вьтолнен на первом и втором транзисторах одного типа проводимос ти, третьем и четвертом транзистоpax другого типа проводимости и двух стабилитронах, катоды которых подключены к коллекторам первого и второго транзисторов , а аноды - к ;КОллекторам третьего и четвертого транзисторов, к второй диагонали первого ключа подключены катод первого и анод второго стабилитронов вгсрдного коммутатора, к первым диагоналям третьего и четвертого ключей подключены выходы буферных усилителей и выход устройства, к второй диагонали третьего ключа подключены катод первого и анод второго стабилитронов выходного коммутатора, а анод первого и катод второго стабилитронов подключены к второй диагонали четвертого ключа, эмиттеры транзисторов коммутаторов соединены с шинами питания, базы транзисторов подключены к шинам управления, о тличающееся тем, что, с целью повышения точности устройства, в него введены дополнительный коммутатор и элементы с нелинейной характеристикой, например диоды, анод первого из которых соединен с анодом первого стабилитрона входного коммутатора, катод первого диода подключен к выходу первого буферного усилителя и к аноду второго диода, катод которого соединен с катодом второго стабилитрона входного ксялмутатора, анод третьего диоДа соединен с анодом второго стабилитрона дополнительного коммутатора, катод третьего диода подключен к выходу второго буферного усилителя и к аноду четвертого диода, катод которого соединен с катодом первого стабилитрона дополнительного коммутатора, аноды третьего и четвертого дио.дов второго ключа соединены с анодом первого стабилитрона дополнительного коммутатора, катоды первого и . третьего диодов второго ключа соединены с катодом второго стабилитрона дополнительного коммутатора, базы Транзисторов которого подключены к шинам управления, а эмиттеры к шинам питания. Источники информации, принятые во внимание при экспертизе 1.Заявка ФРГ 264&161, кл. G 11 С 27/00, опублик. 1977. 2.Зарубежная радиоэлектроника, 1978, 10, с. 71. 3. Автометрия, 1975, 1, с. 115 (прототип).

3 ,ч b±

yfx.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU822295A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ТЕМПЕРАТУРЫ | 1992 |

|

RU2032209C1 |

| Среднеквадратичный детектор | 1990 |

|

SU1781640A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| СИСТЕМА ЗАЖИГАНИЯ С НАКОПЛЕНИЕМ ЭНЕРГИИ НА КОНДЕНСАТОРЕ | 1992 |

|

RU2020259C1 |

| МНОГОКАНАЛЬНЫЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ДАТЧИКОВ | 2022 |

|

RU2795214C1 |

| Устройство управления газоразрядной индикаторной панелью | 1989 |

|

SU1709388A1 |

| Устройство для включения и отключения электрического освещения | 1988 |

|

SU1767475A1 |

| Коммутатор аналоговых сигналов | 1981 |

|

SU978345A1 |

| УСТРОЙСТВО ПРОТИВОАВАРИЙНОЙ АВТОМАТИКИ | 2001 |

|

RU2221318C2 |

Авторы

Даты

1982-07-15—Публикация

1980-01-28—Подача