(5) УСТРОЙСТВО ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1978 |

|

SU718905A1 |

| Управляемый генератор | 1978 |

|

SU723762A1 |

| Преобразователь напряжения во временной интервал | 1979 |

|

SU892708A1 |

| Устройство задержки | 1980 |

|

SU894845A1 |

| Реле времени | 1981 |

|

SU984047A2 |

| Устройство задержки импульсов | 1979 |

|

SU856000A1 |

| КОММУТАЦИОННОЕ УСТРОЙСТВО | 1997 |

|

RU2175166C2 |

| Мультивибратор | 1981 |

|

SU1182634A1 |

| Мультивибратор | 1979 |

|

SU790122A1 |

| Устройство защиты полупроводниковых микросборок от тиристорного эффекта | 2017 |

|

RU2661282C1 |

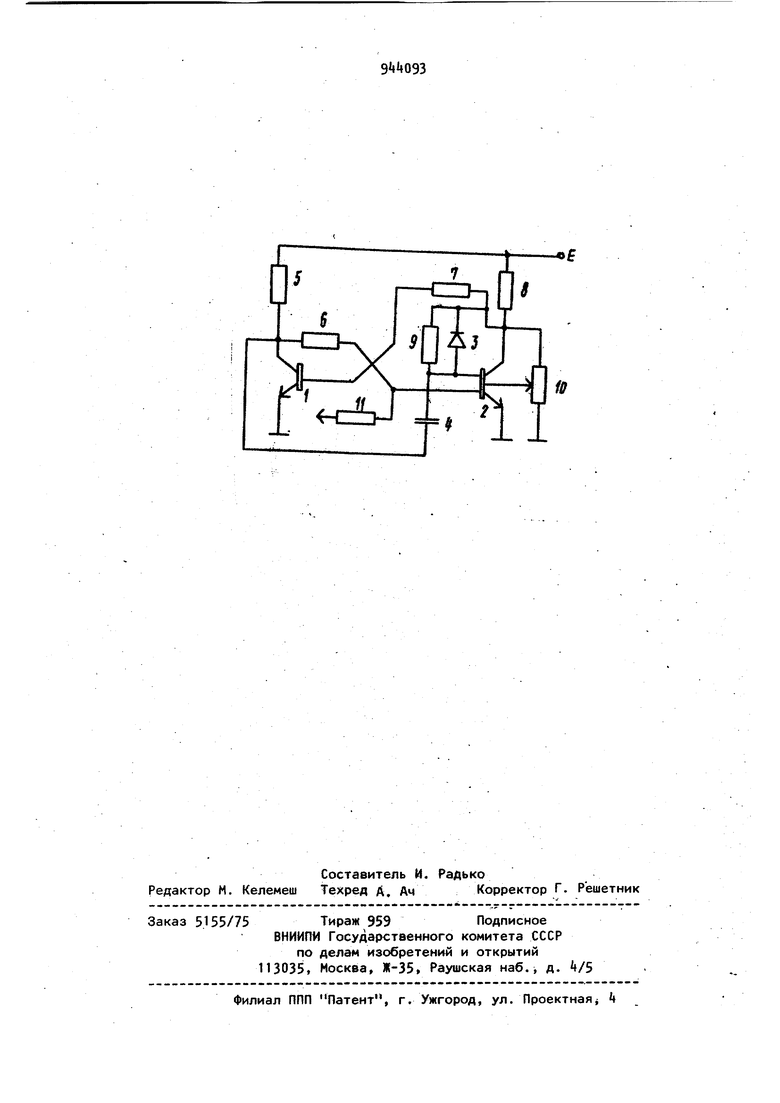

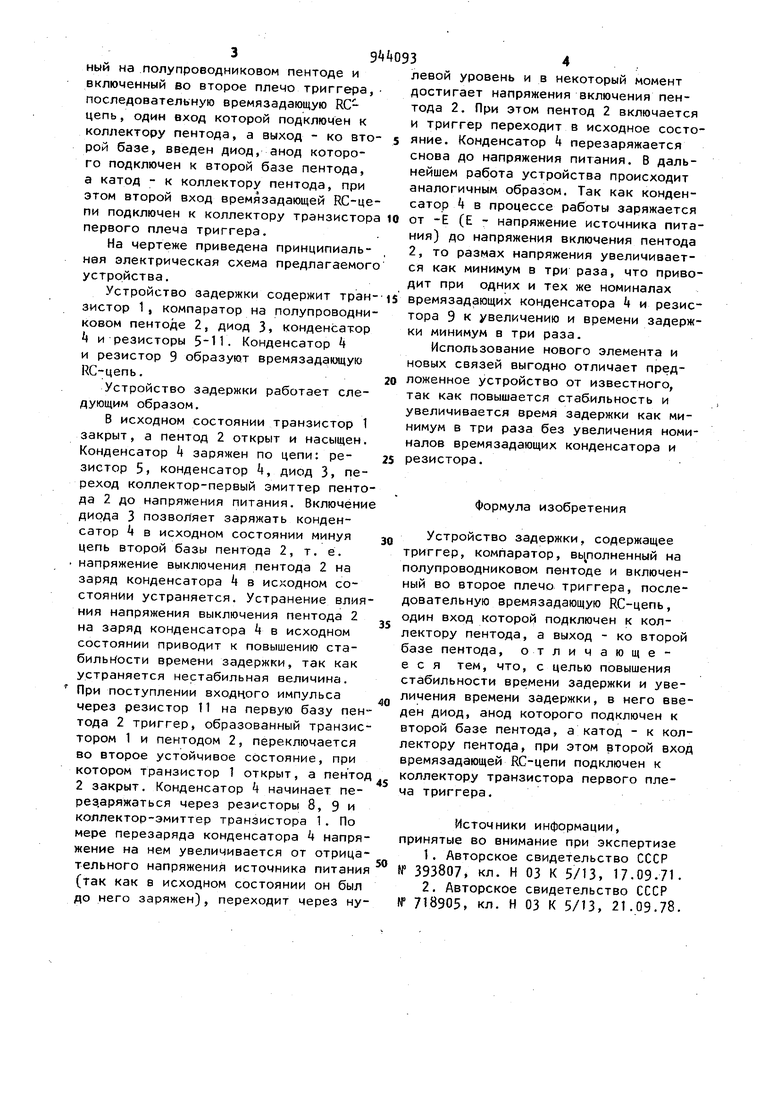

Изобретение относится к импульсной технике. Известно устройство задержки, со держащее транзисторный триггер с ра дельными входами, мостовую схему, состоящую из RC-цепи и цепи установки опорного напряжения, к диагонали которой подсоединен диодно-регенер тивный компаратор,мостовая схема подключена между коллектором и эмиттером выходного транзистора триггера D. Однако известное устройство имеет недостаточную выдержку времени. Известно также устройство задержки, содержащее триггер, компаратор, выполненный на полупроводниковом пен тоде и включенный во второе плечо триггера, последовательную времязадающую RC-цепь, один вход которой подключен к коллектору пентода, а выход - ко второй базе 23 Недостатком данного устройства является низкая стабильность времени задержки и малое время задержки. . Нестабильность устройства определяется тем, что конденсатор времязадающей КС-цепи в исходном состоянии разряжается до напряжения выключения пентода, величина.которого является ненормированной и существенно меняющейся при смене приборов и температуры, что и приводит к нестабильности времени задержки. В процессе работы конденсатор времязадающей RC-цепи заряжается от напряжения выключения и до напряжения включения пентода, т. е. разма напряжений мал, что не позволяет получать большое время задержки без увеличения номиналов времязадающих конденсатора и резистора. Цель изобретения является повышение стабильности времени задержки и увеличение времени задержки. Поставленная цель достигается тем, |что в устройство задержки, содержащее триггер, компаратор, выполненныи на полупроводниковом пентоде и включенный во второе плечо триггера, последовательную времязадающую RCцепь, один вход которой подключен к коллектору пентода, а выход - ко второй базе, введен диод, анод которого подключен к второй базе пентода, а катод - к коллектору пентода, при этом второй вход времязадающей RC-цепи подключен к коллектору транзистора первого плеча триггера. На чертеже приведена принципиальная электрическая схема предлагаемого устройства. Устройство задержки содержит транзистор 1, компаратор на полупроводниковом пентоде 2, диод 3 конденсатор и резисторы 5-11. Конденсатор и резистор 9 образуют времязадающую RC-цепь. Устройство задержки работает следующим образом. В исходном состоянии транзистор 1 закрыт, а пентод 2 открыт и насыщен. Конденсатор k заряжен по цепи: резистор 5, конденсатор 4, диод 3, переход коллектор-первый эмиттер пентода 2 до напряжения питания. Включение диода 3 позволяет заряжать конденсатор Ц в исходном состоянии минуя цепь второй базы пентода 2, т. е. напряжение выключения пентода 2 на заряд конденсатора в исходном состоянии устраняется. Устранение влия ния напряжения выключения пентода 2 на заряд конденсатора k в исходном состоянии приводит к повышению стабильности времени задержки, так как устраняется нестабильная величина. При поступлении входного импульса через резистор 11 на первую базу пен тода 2 триггер, образованный транзис тором 1 и пентодом 2, переключается во второе устойчивое состояние, при котором транзистор 1 открыт, а пентод 2 закрыт. Конденсатор t начинает перез,аряжаться через резисторы 8, 9 и коллектор-эмиттер транзистора 1. По мере перезаряда конденсатора 4 напря жение на нем увеличивается от отрица тельного напряжения источника питани (так как в исходном состоянии он был до него заряжен), переходит через ну левои уровень и в некоторый момент достигает напряжения включения пентода 2. При этом пентод 2 включается и триггер переходит в исходное состояние. Конденсатор k перезаряжается снова до напряжения питания. В дальнейшем работа устройства происходит аналогичным образом. Так как конденсатор j в процессе работы заряжается от -Е (Е - напряжение источника питания) до напряжения включения пентода 2, то размах напряжения увеличивается как минимум в три раза, что приводит при одних и тех же номиналах времязадающих конденсатора k и резистора 9 к увеличению и времени задержки минимум в три раза. Использование нового элемента и новых связей выгодно отличает предложенное устройство от известного, так как повышается стабильность и увеличивается время задержки как минимум в три раза без увеличения номиналов времязадающих конденсатора и резистора. Формула изобретения Устройство задержки, содержащее триггер, компаратор, вы полненный на полупроводниковом пентоде и включенный во второе плечо триггера, последовательную времязадающую RC-цепь, один вход которой подключен к коллектору пентода, а выход - ко второй базе пентода, отличающееся тем, что, с целью повышения стабильности времени задержки и увеличения времени задержки, в него введен диод, анод которого подключен к второй базе пентода, а катод - к коллектору пентода, при этом второй вход времязадающей RC-цепи подключен к коллектору транзистора первого плеча триггера. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР If 393807, кл. Н 03 К 5/13, 17.09.71. 2.Авторское свидетельство СССР f 718905, кл. Н 03 К 5/13, 21.09.78.

-o

-0-1

Авторы

Даты

1982-07-15—Публикация

1980-10-10—Подача