(5) АНАЛОГОВЫЙ УМНОЖИТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ ГАРМОНИЧЕСКОГО СИГНАЛА | 2015 |

|

RU2565424C1 |

| Аналоговое множительное устройство | 1979 |

|

SU860087A1 |

| Устройство для определения характеристик операционных усилителей | 1981 |

|

SU985797A1 |

| Квадратичный преобразователь | 1983 |

|

SU1144123A1 |

| Квадратичный преобразователь | 1980 |

|

SU989562A1 |

| Перемножитель аналоговых сигналов | 1985 |

|

SU1242992A1 |

| Измерительный преобразователь среднеквадратичных значений напряжений | 1985 |

|

SU1585766A1 |

| Аналоговое делительное устройство | 1980 |

|

SU898446A1 |

| ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2252452C1 |

| Вычислительное устройство | 1981 |

|

SU978159A1 |

1

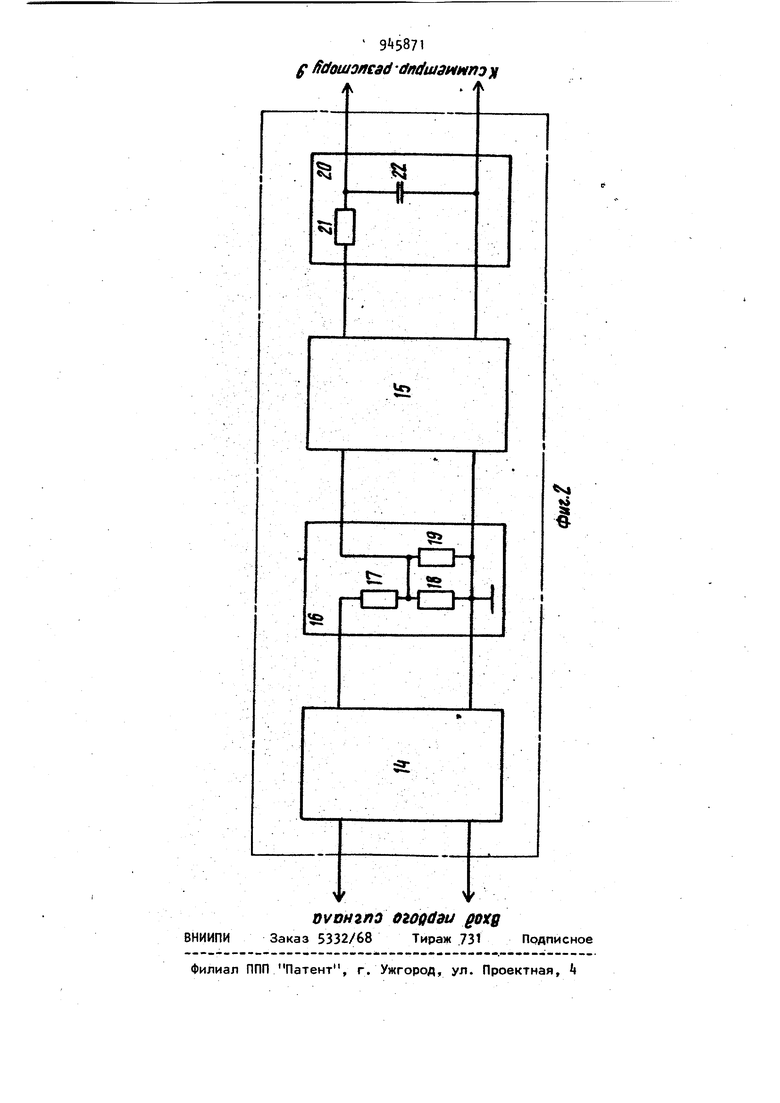

Изобретение относится к аналоговой вычислительной технике и может быть использовано в системах обработки сигналов, измерительных приборах и системах связи.

Известны аналоговые умножители, основанные на принципе управления коэффициентом передами управляемого аттенюатора, в состав которых входят элементы с регулируемым сопротивлением, например полевые транзисторы П.

Известные умножители характеризуются низкой точностью и узким частотным диапазоном входных сигналов.

Наиболее близким к изобретению является аналоговый умножитель, содержащий входной дифференциальный усилитель, инвертирующий вход которого подключен через первый и второй масштабные резисторы соответственно к источнику первого перемножаемого сигнала и источнику напряжения смещения, а неинеертирующий - через

третий масштабный резистор к шине нулевого потенциала, первый и второй управляемые резисторы, выполненные, например, на полевых транзисторах, масштабные резисторы, делитель напряжения и выходной дифференциальный усилитель f2 J.

Недостатками известного умножителя являются снижение его точности

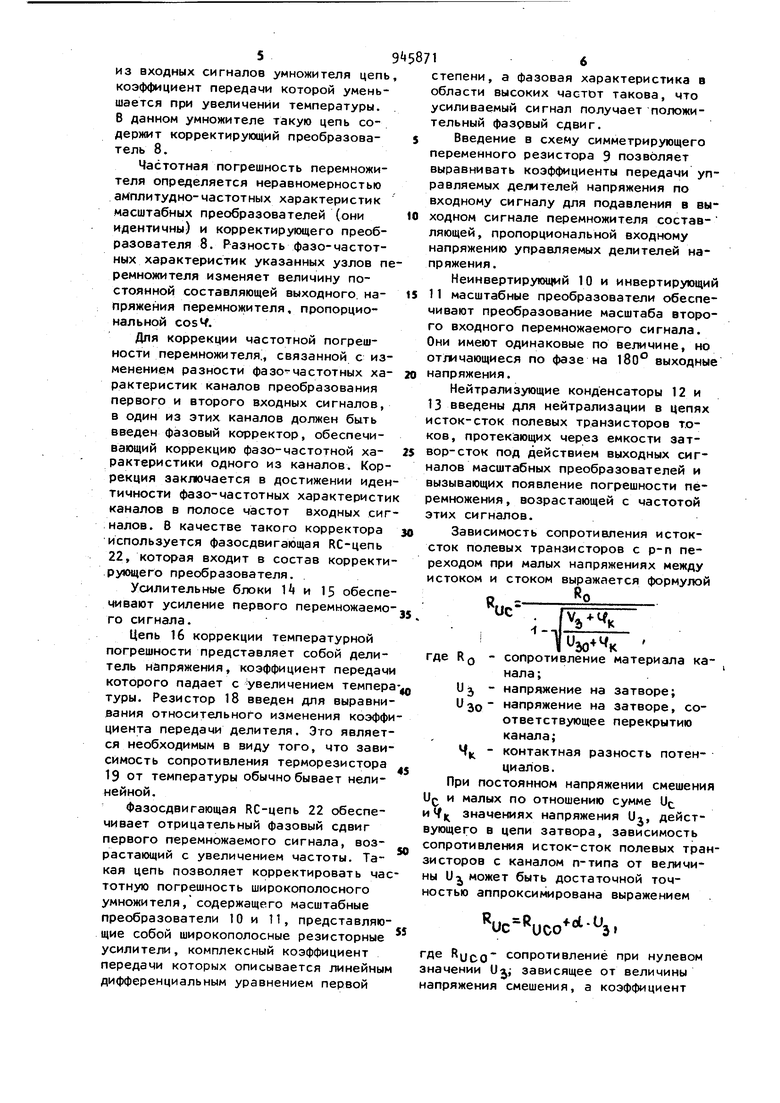

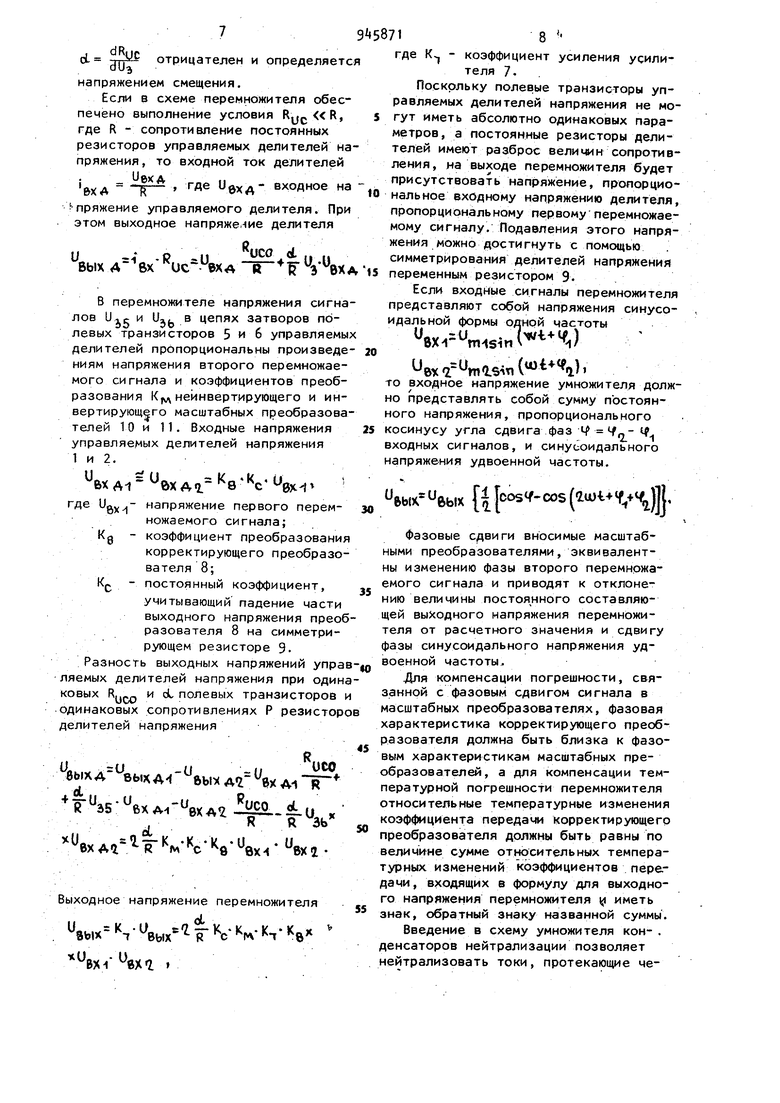

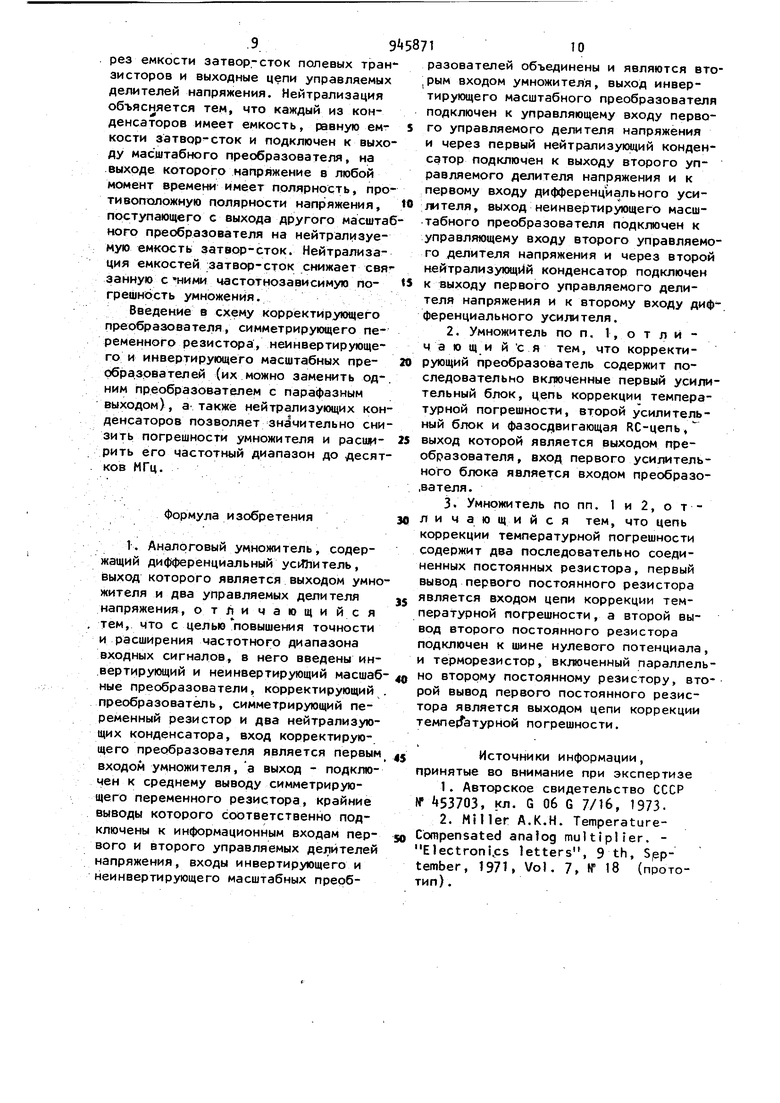

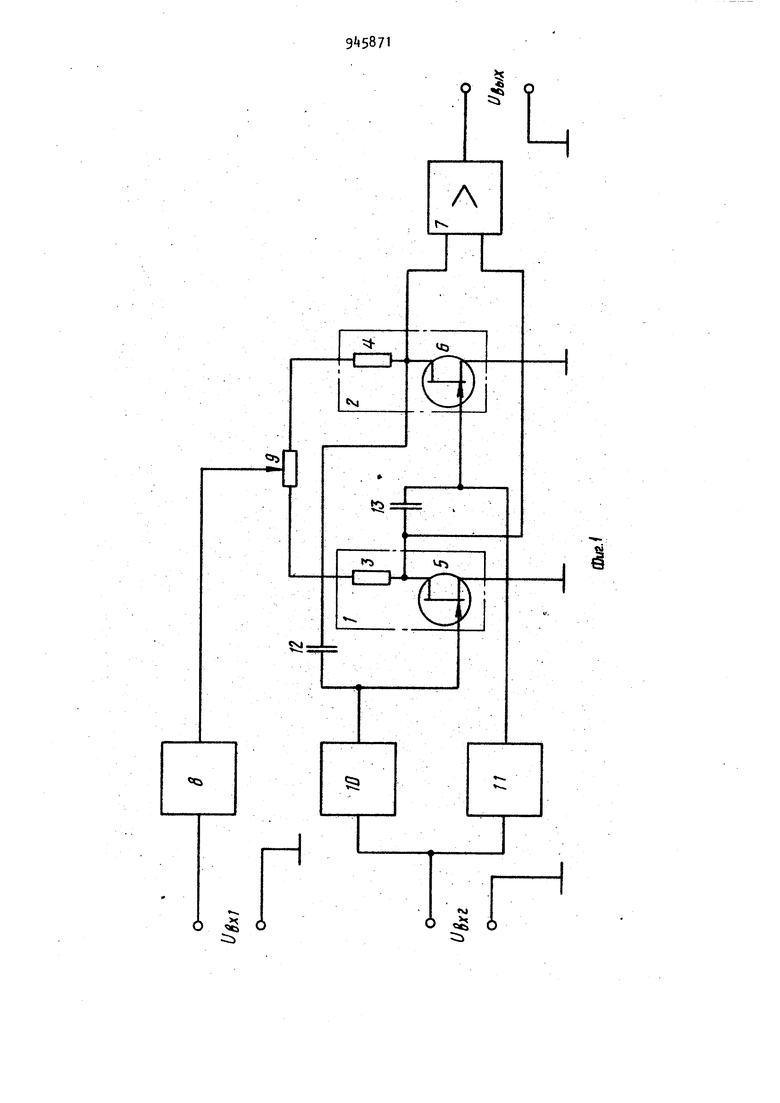

,Q при расширении спектров входных сигналов, невысокая температурная стабильность коэффициента преобразования и начального выходного уровня. Это связано е тем, что в нем применяют 5 ся дифференциальные усилители, вносящие значительные фазовые сдвиги высокочастотных составляющих спектров сигналов и обладающие дрейфом нуля, а также тем, что в области высоких частот сопротивления межэлектродных емкостей полевых транзисторов , уменьшаются,и через эти емкости протекают сравнительные большие токи. Так, например, через емкость затворсток полевого транзистора протекает ток, обусловленный подводимым к цепи затвора сигналом. Указанный ток протекает через участок исток-сток полевого транзистора и вызывает появление на этом участке напряжения, складывающегося с выходным сигналом управляемого аттенюатора. Это ведет к повышению погрешности умножения, увеличивающейся с ростом частоты сигнала, действующего в цепи затвора Целью изобретения является повышение точности и расширение частотного диапазона входных сигналов. Эта цель достигается тем, что в аналоговый умножитель, содержащий .дифференциальный усилитель, выход которого является выходом умножителя и два управляемых делителя напряжения, введены инвертирующий и неинвер тирующий масштабные преобразователи, корректирующий преобразователь, симметрирующий переменный резистор и два нейтрализующих конденсатора, вход корректирующего преобразователя является первым входом умножителя, а выход - подключен к среднему выводу сим метрирующего переменного резистора, крайние выводы которого соответственно подключены к информационным входам управляемых делителей напряжения, вхо ды инвертирующего и неинвертирующего масштабных преобразователей объединены и являются вторым входом умножителя, выход инвертирующего масштабного преобразователя подключен к управляющему входу первого управляемого делителя напряжения и через первый нейтрализующий конденсатор подключен к выходу второго управляемого делителя напряжения и к. первому входу дифферен циального усилителя, выход неинвертирующего масштабного преобразователя подключен к управляющему входу второго управляемого делителя напряжения и через второй нейтрализующий конденсатор подключен к выходу первого управляемого делителя напряжения и к второму входу дифференциального усилителя.. Корректирующий преобразователь содержит последовательно включенные пер вый усилительный блок, цепь коррекций температурной погрешности, второй усилительный блок и фазосдвигающую выход которой является Bbixoдом преобразователя, вход первого уси лительного блока является входом преобразователя. Цепь коррекции температурной погрешности содержит два последовательно соединенных постоянных резистора, первый вывод первого постоянного Резистора является входом цепи коррекции температурной погрешности, а второй вывод второго постоянного резистора подключен к щине нулевого потенциала, и терморезистор, включенный параллельно второму постоянному резистору, второй вывод первого постоянного резистора является выходом цепи коррекции температурной погрешности. На фиг, t приведена функциональная схема аналогового умножителя; на фиг. 2 - функциональная схема корректирующего преобразователя. Аналоговый умножитель содержит два управляемых делителя напряжения Iи 2, состоящих из постоянных резисторов 3 и и полевых транзисторов 5 и 6, дифференциальный усилитель 7 корректирующий преобразователь 8, симметрирующий переменный резистор 9, неинвертирующий 10 и инвертирующий IIмасштабные преобразователи и нейтрализующие конденсаторы 12 и 13. Корректирующий преобразователь 8 содержит два усилительных блока Н и 15 цепь коррекции температурной погрешности 16, выполненную на резисторах 17 и 18 и терморезисторе 19, фазосдви гающая fiC-цепь 20, вы полненную на резисторе 21 и конденсаторе 22. Аналоговый умножитель работает следующим образом. Управляемые делители напряжения 1 и 2 выполняют операции аналогового перемножения, формируя выходной сигнал , содержащий составляющую, пропорциональную произведению их входного и управляющего напряжений. Усилитель 7 служит для выделения и усиления разности выходных сигналов управляемых делителей напряжения, пропорциональной произведению входных сигналов умножителя. . Корректирующий преобразователь 8 обеспечивает коррекцию частотной и температурной погрешностей перемножителя и преобразование масштаба пер-, вого перемножаемого сигнала, поступакйцего через Него на входы управляемых делителей напряжения. Коррекции температурной погрешности умножителя можно достигнуть, введя в канал преобразования одного ИЗ входных сигналов умножителя цепь, коэффициент передачи которой уменьшается при увеличении температуры. В данном умножителе такую цепь содержит корректирующий преобразователь 8. Частотная погрешность перемножителя определяется неравномерностью амплитудно-частотных характеристик масштабных преобразователей (они идентичны) и корректирующего преобразователя 8. Разность фазо-частотных характеристик указанных узлов пе ремножителя изменяет величину постоянной составляющей выходного, напряжения перемножителя, пропорциональной cos Ч. Для коррекции частотной погрешности перемножителя., связанной с изменением разности фазо-частотных характеристик каналов преобразования первого и второго входных сигналов, в один из этих каналов должен быть введен фазовый корректор, обеспечивающий коррекцию фазо-частотной характеристики одного из каналов. Коррекция заключается в достижении иден тичности фа30-частотных характеристи каналов в полосе частот входных сиг налов. В качестве такого корректора используется фазосдвигающая RC-цепь 22, которая входит в состав корректи рующего преобразователя. Усилительные блоки 1 и 15 обеспе чивают усиление первого перемножаемо го сигнала. Цепь 16 коррекции температурной погрешности представляет собой делитель напряжения, коэффициент передач которого падает с -увеличением темпер туры. Резистор 18 введен для выравни вания относительного изменения коэфф циента передачи делителя. Это являет ся необходимым в виду того, что зави симость сопротивления терморезистора 19 от температуры обычно бывает нелинейной. Фазосдвигающая RC-цепь 22 обеспечивает отрицательный фазовый сдвиг первого перемножаемого сигнала, возрастающий с увеличением частоты. Такая цепь позволяет корректировать ча тотную погрешность широкополосного умножителя, содержащего масштабные преобразователи 10 и 11, представляю щие собой широкополосные резисторные усилители, комплексный коэффициент передачи которых описывается линейны дифференциальным уравнением первой степени, а фазовая характеристика в области высоких частот такова, что усиливаемый сигнал получает положительный фазовый сдвиг. Введение в схему симметрирующего переменного резистора 9 позволяет выравнивать коэффициенты передачи управляемых делителей напряжения по входному сигналу для подавления в выходном сигнале перемножителя составляющей, пропорциональной входному напряжению управляемых делителей напряжения. Неинвертирующий 10 и инвертирующий 11 масштабные преобразователи обеспечивают преобразование масштаба второго входного перемножаемого сигнала. Они имеют одинаковые по величине, но отличающиеся по фазе на 180 выходные напряжения. Нейтрализующие конденсаторы 12 и 13 введены для нейтрализации в цепях исток-сток полевых транзисторов токов, протекающих через емкости затвор-сток под действием выходных си|- налов масштабных преобразователей и вызывающих появление погрешности перемножения, возрастающей с частотой этих сигналов. Зависимость сопротивления истоксток полевых транзисторов с р-п переходом при малых напряжениях между истоком и стоком выражается формулой . fv , где RQ - сопротивление материала канала ; Uj - напряжение на затворе; и 3Q - напряжение на затворе, соответствующее перекрытию канала; Чц - контактная разность потенциалов. При постоянном напряжении смешения UQ и малых по отношению сумме DC. иЧц значениях напряжения Ua, действующего в цепи затвора, зависимость сопротивления исток-сток полевых транзисторов с каналом п-типа от величины иJ может быть достаточной точностью аппроксимирована выражением uc-Ruco t- эг где RUCO сопротивление при нулевом значении Uji зависящее от величины напряжения смешения, а коэффициент fi- S ЗЩ отрицателен и определяетс напряжением смещения. Если в схеме перемножителя обеспечено выполнение условия R.,j.«R, где R - сопротивление постоянных резисторов управляемых делителей на пряжения, то входной ток делителей бХА Т exA входное на ьпряжение управляемого делителя. При этом выходное напряжение делителя вых В перемножителе напряжения сигна лов и и, в цепях затворов полевых транзисторов 5 и 6 управляемы делителей пропорциональны произведе ниям напряжения второго перемножаемого сигнала и коэффициентов преобразования l,v нейнвертирующего и инвертирующего масштабных преобразова телей 10 и 11. Входные напряжения управляемых делителей напряжения 1 и 2. BXAl eXAl S где Ug напряжение первого перемножаемого сигнала; Kg - коэффициент преобразования корректирующего преобразователя 8; К - постоянный коэффициент, учитывающий падение части выходного напряжения преоб разователя 8 на симметрирующем резисторе 9. Разность выходных напряжений упра ляемых делителей напряжения при один ковых R.jf.Q и cL полевых транзисторов одинаковых сопротивлениях Р резистор делителей напряжения U и -и 1, 8ЫХА ВЫХА вЬ1ХА«г %А1Т Фъ5Лу..п, .К к ЗЬ / ехАа Лк- с- в вхч- вха. Выходное напряжение перемножителя . 8b.,x iFVVKV eX BxV 718 где К - коэффициент усиления усилителя 7. . Поскольку полевые транзисторы управляемых делителей напряжения не могут иметь абсолютно одинаковых параметров, а постоянные резисторы делителей имеют разброс вели« IH сопротивления, на выходе перемножителя будет присутствовать напряжение, пропорциональное входному напряжению делителя, пропорциональному первому перемножаемому сигналу. Подавления этого напряжения можно достигнуть с помощью симметрирования делителей напряжения переменным резистором 9. Если входные сигналы перемножителя представляют собой напряжения синусоидальной формы одной частоты вX. n-tsir,) () то входное напряжение умножителя должно представлять собой сумму постоянного напряжения, пропорционального косинусу угла сдвига фаз Ч - Чп-tf входных сигналов, и синусоидального напряжения удвоенной частоты. { oos f-cos(о.ч .+ч;), Фазовые сдвиги вносимые масштабными преобразователями, эквивалентны изменению фазы второго перемножаемого сигнала и приводят к отклонению величины постоя нного составляющей выходного напряжения перемножителя от расчетного значения и сдвигу фазы синусоидального напряжения удвоенной частоты.. Дпя компенсации погрешности, связанной с фазовым сдвигом сигнала в масштабных преобразователях, фазовая характеристика корректирующего преобразователя должна быть близка к фазовым характеристикам масштабных преобразователей, а для компенсации температурной погрешности перемножителя относительные температурные изменения коэффициента передачи корректирующего преобразователя должны быть равны по величине сумме относительных температурных изменений коэффициентов передачи, входящих в формулу для выходного напряжения перемножителя ((i иметь знак, обратный знаку названной суммы. Введение в схему умножителя кон- . денсаторов нейтрализации позволяет нейтрализовать токи, протекающие через емкости затвор-сток полевых тран зисторов и выходные цепи управляемых делителей напряжения. Нейтрализация объясняется тем, что каждый из конденсаторов имеет емкость, равную емкости затворусток и подключен к выхо ду масштабного преобразователя, на выходе которого напряжение в любой момент времени имеет полярность, про тивоположную полярности напряжения, поступающего с выхода другого масшта ного преобразователя на нейтрализуемую емкость затвор-сток. Нейтрализация емкостей затвор-сток снижает свя занную с НИМИ частотнозависимую погрешность умножения. Введение в схему корректирующего преобразователя, симметрирукяцего переменного резистора, неинаер тирующего и инвертирующего масштабных прербрадователей (их можно заменить одним преобразователем с парафазным выходом), а также нейтрализующих кон денсаторов позволяет значительно сни зить погрешности умножителя и расширить его частотный диапазон до десят ков МГц. Формула изобретения 1. Аналоговый умножитель, содержащий дифференциальный уо итель, выход которого является выходом умно жителя и два управляемых делителя напряжения, отличающийся тем, что с цельюповышения точности и расширения частотного диапазона входных сигналов, в него введены инвертирующий и неинвертирующий масшаб ные преобразователи, корректирующий преобразователь, симметрирующий переменный резистор и два нейтрализующих конденсатора, вход корректирующего преобразователя является первым входом умножителя, а выход - подключен к среднему выводу симметрирующего переменного резистора, крайние выводы которого соответственно подключены к информационным входам первого и второго управляемых делителей напряжения, входы инвертирующего и неинвертирующего масштабных преобразователей объединены и являются вторым входом умножителя, выход инвертирующего масштабного преобразователя подключен к управляющему входу первого управляемого делителя напряжения и через первый нейтрализующий конденсатор подключен к выходу второго управляемого делителя напряжения и к первому входу дифференциального усилителя, выход неинвертирующего масштабного преобразователя подключен к управляющему входу второго управляемого делителя напряжения и через второй нейтрализующий конденсатор подключен к выходу первого управляемого делителя напряжения и к второму входу дифференциального уси;мтеля. 2.Умножитель по п. 1, о т л И ч а ю щи и с я тем, что корректирующий преобразователь содержит последовательно включенные первый усилительный блок, цепь коррекции температурной погрешности, второй усилительный блок и фазосдвигающая RC-цепь, выход которой является выходом преобразователя, вход первого усилительного блока является входом преобразо.вателя. 3.Умножитель по пп. 1 и 2, о т л и ч а ю щ и и с я тем, что цепь коррекции температурной погрешности содержит два последовательно соединенных постоянных резистора, первый вывод первого постоянного резистора является входом цепи коррекции температурной погрешности, а второй вывод второго постоянного резистора подключен к шине нулевого потенциала, и терморезистор, включенный параллельно второму постоянному резистору, второй вывод первого постоянного резистора является выходом цепи коррекции темпе| атурной погрешности. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР If 53703, кл. G Об G 7/16, 1973. 2.Miller А.К.Н. TemperatureCompensated analog multiplier. Electronics letters, 9 th, Spptember, 1971, Vol. 7, № 18 (прототип). ff fou/3/ C3dcfftefta3HMn3)i

u

to

gjssyi

«V

dh

Авторы

Даты

1982-07-23—Публикация

1980-07-07—Подача