(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический преобразователь (его варианты) | 1982 |

|

SU1078442A1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

| Логарифмический аналого-цифровой преобразователь | 1985 |

|

SU1277146A1 |

| Логарифмический преобразователь | 1982 |

|

SU1043678A1 |

| Антилогарифмический преобразователь | 1979 |

|

SU822211A1 |

| Вычислитель статистических момен-TOB | 1978 |

|

SU807342A1 |

| Логарифмический преобразователь | 1982 |

|

SU1064283A1 |

| Логарифмический преобразователь | 1985 |

|

SU1316009A1 |

| Устройство для логарифмированияОТНОшЕНия дВуХ СигНАлОВ | 1979 |

|

SU822210A1 |

| Устройство для определения статистических моментов | 1978 |

|

SU723589A1 |

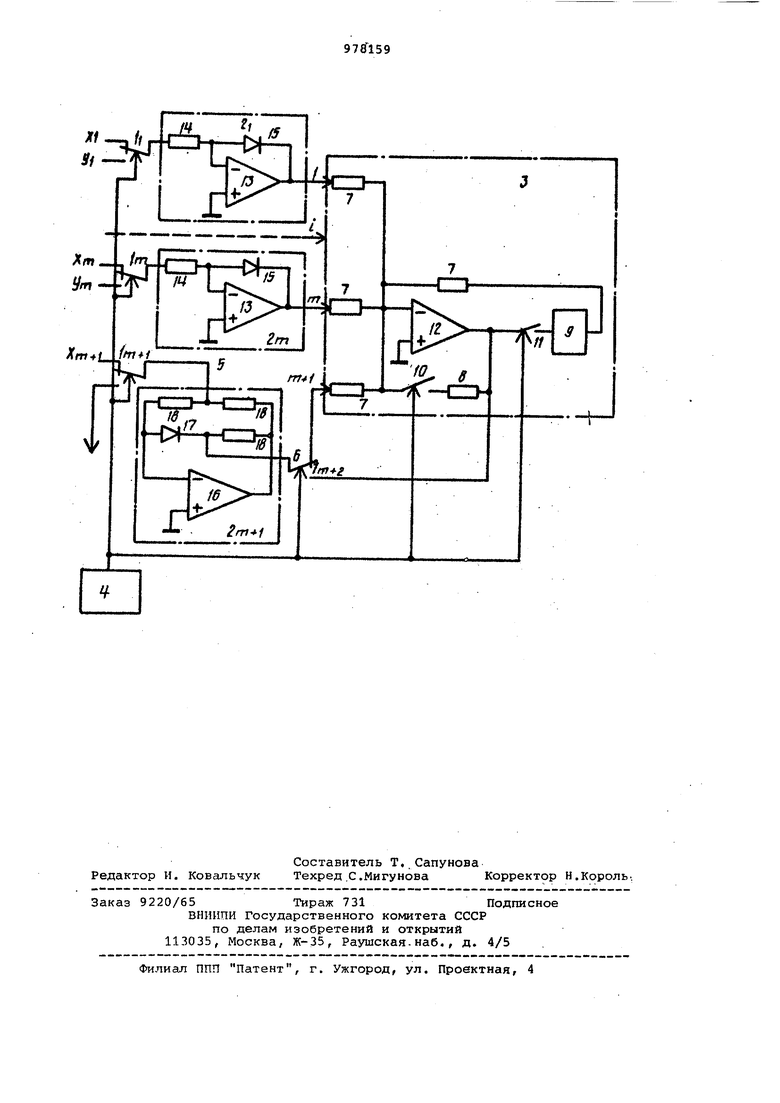

Изобретение относится к автомати ке и вычислительной технике и служит для вычисления выражений вида П(-) Х,, , где Хт, УГП Vff,+i - входные сигналы; показатель степени ().; количество входных сигналов, с помощью логарифмического алгоритмаZ antilogJZZf dog X - (2 Известно вычислительное устройство, содержащее коммутатор, логарифмический преобразователь, переключатель, масштабный делитель, йнтегрозапоминающий блок, блок сравне ния, источник опорного сигнала и ин тегратор 11. Недостаток устройства - малое быстродействие и низкая точность. Наиболее близким к предлагаемому по технической сущности является вычислительное устройство, содержащее коммутатор входных сигналов, m входов которого являются входами устройства, а выход соединен со входом-выходом обратимого логарифмического преобразователя, выходвход которого соединен со входом переключателя, m -f 1 выходы переклйчателя соединены с входами m + 1 усилителей выборки-хранения, а m . + 2 выход с выходом масштабно суммирующего блока, прияем выходы усили- . телей выборки-хранения соединешл с входами масштабно-суммирующего блока 2. Использование обратимого логарифмического преобразователе хотя и позволяет упростить устройство и уменьшить погрешность преобразования, но требует для т-входных сигналов m + 2 тактов в цикле работы устройства. Это ограничивает быстродействие устройства. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в вычислительное устройство, содержащее первый переключатель, первый и второй неподвижные контакты которого являются соответственно входом и выходом устройства, обратимый логарифмический преобра ователь, вход-выход которого подключен к неподвижному контакту первого переключателя, второй переключатель, масштабно-суммирующий блок и блок управления, подвижный контакт втор го переключателя подключен к выходу входу обратимого логарифмического преобразователя, а первый и второй неподвижные.контакты второго переключателя подключены соответственно к первому входу и к выходу масш табно-суммирующего блока, выход бло ка управления подключен к управляющим входам переключателей и к упра ляющему входу масштабно-суммирующе блока, введены m переключателей и логарифмических преобразователей, первые и вторые неподвижные контак.ты m переключателей являются соотве ственно первой и второй группами входов устройства, подвижные контак ты m переключателей подключены соответственно к входам m логарифмических преобразователей,выходы которых подключены к соответствующим входам масштабно-суммирующего блока, управляющие входы m переключателей подключены к выходу блока уп равления. Кроме того, масштабно-суммирующий блок содержит m + 2 масштабных резисторов,резистор обратной связи инвертирующий усилитель, два ключа и элемент памяти, первые выводы т+ + 2 масштабных резисторов объединены и подключены к входу инвертирующего усилителя и к-информационному входу первого ключа, выход которого через резистор обратной связи подключен к входу инвертирующего усилителя и к выходу второго ключа, который является выходом масштабно-суммирующего блока, информационный вход второго ключа подклю .чен к выходу элемента памяти, вход которого подключен ко второму выводу (т + 2)-го масштабного резистора, второй вывод (т + 1)-го масштабного резистора является первым входом масштабно-суммирующего блока, вторые выводы m масштабных резисторов являются соответствующими входами масштабно-суммирующего блока,, управляющие входы ключей объединены и являются управляющим входом масштабно-суммирующего блока. На чертеже приведена фунз циональ ная схема вычислительного устройства. Устройство содержит переключатели 1 - 1.,,логарифмические преобразователи 2 - 2f, обратимый логарифмический .преобразователь 2. масштаб но-cyм 1иpyющи и блок 3, блок управления, вход-выход 5 и выходвход 6 обратимого логарифмического преобразователя. Мааитабно-суммирующий блок 3 содержит масштабные резисторы 7, ре зистор 8 обратной связи, элемент 9 памяти, ключи 10 и 11 и инвертирующий усилитель 12. Каждый из логарифмических преобразователей содержит операционный усилитель 13, масштабный резистор 14 и логарифмирующий диод 15. Обратимый логарифмический преобразователь содержит операционный усилитель 16, логарифмирующий диод 17 и масштабные резисторы 18. Устройство работает следующим образом. Входные сигналы Х-, - Х. через переключатели - 1,41 в течение первого такта поступают на входы ло гарифмических преобраз-ователей 2, , функция преобразования которых описывается вьлражением Y + N, (3) где К - мультипликативная.,N - аддитивная погрешности логарифмического преобразователя. Результаты преобразования сигналов Xj - X,p,пo ступают в масштабно-сумлвдрующий блок с запоминанием, в котором они масштабируются в соответствии с показателями степени п Q. - п входных сигналов и суммируются с результатом преобразования обратимого логарифмического преобразователя , . +J/, + ... + п К„1од + N -f К „411од„Х + N,t. (4) Полученная сумма (4) запоминаете в масштабно-суммирующем блоке 3. Во второй такт работы устройства входные сигналы Y , - Y через переключатели , - 1 поступают в масштабно-суммирующий блок 3, где масштабируется в соответствии с показателями степени п - п и вычитаются из сформированной в первом также сумглы (4) -(n,,+ ..,r,. M,K,eoq; V l - m mf°Tc n,Nm .. Полученный сигнал Y с входа-выхода масштабно-суммирующего блока 3 поступает на вход-выход 6 обратимого логарифмического преобразователя 2., где потенциируется. Поскольку обратное преобразование обратимого логарифмического преобразователя 2 описывается выражением . V то, подставляя в (б) выражение (5), получает п,к, ЧпКщ / XT / Xm m+i Z () При условии равенства мультипликативных погрешностей К, К,,,,..., К выражение (7) переписывается следующим образом: Г1 -i Г1 - Как следует из последовательности преобразования сигналов, результаты логарифмирования входных сигналов Х ,. . . , Хт+1 вводятся в масштабносуммирующий блок с запоминанием в первый такт, во второй же такт осуществляется логарифмирование сигналов. Y., - Y, и потенциирование линейной комбинации логарифмов всех входных сигналов. Таким образом, сигналы Х - Х„+ преобразуются с прерыванием, т.е. операции логарифмирования сигналов и антилогарифмирования их линейной комбинации разнесены во времени, а для сигналов этот процесс происходит одновременно. Поэтому в течении второго такта осуществляется фактически непрерывное преобразование входных сигналов Y, - Уд,. Преимуществом предлагаемого устройства в сравнении с прототипом яв ляется не только сокращение числа рабочих тактов до двух независимо от количества входных сигналов, но и возможность работы с периодической коррекцией, когда длительность 2-го рабочего такта намного превыша ет длительность 1-го такта коррекции . Входные сигналы Х + этом случае могут задаваться как постоян ными (масштабными коэффициентами), так и изменяющимися с частотой, мно го меньшей частоты коммутации ключей в схеме устройства. При этом полностью компенсируются аддитивные и в основном мультипликативные ошибки логарифмических преобразователей. Наибольший положительный эффект достигается при применении в предлагаемом вычислительном устройстве логарифмических преобразователей, использующих логарифмические свойства приборов с р-п переходом, вольт-амперная характеристика кото рых описывается выражением и КЕпЗ- + N постоянная Больцмана, 1,38062-10- ,ЦжА i постоянная, равная единице заряда 1,60219-10- К; абсолютная температура К С + 273, 3(j - обратный ток насыщения пер хода, имеющий сильную зави симость от температуры и з висит от параметров индиви дуальных приборов одного т па. Зависимость от температуры тока Ufl (удвоение на каждые 10°С) и мул (0,33% Не типликативного члена каждый градус) приводит к суммарной погрешности около 8%С. Основная составляющая погрешности полупроводниковых логарифмических элементов обусловлена температурой нестабильностью аддитивного члена N (выражение 9). В известном устройстве, взятом в качестве прототипа, компенсация ад-, дитивного N и мультипликативного К членов осуществляется использованием одного логарифмического элемента для логарифмирования входных сигналов и антилогарифмирования их суммы. Это позволяет полностью исключить влияние температурной нестабильности логарифмического элемента,но приводит к снижению быстродействия. В других логарифмических вычислительных устройствах для компенсации аддитивной погрешности логарифмических элементов используют разность логарифмов двух входных сигналов , полученных идентичными логарифмическими усилителями, а мультипликативная ошибка компенсируется при потенцииропании линейной комбинации логарифмов входных сигналов, При этом необходиьфлм требованием для достижения полной компенссщии является идентичность параметров применяемых логарифмических элементов. Важным обстоятельством является то, что требования к идентичности применяемых элементов для компенсации различных составляющих погрешностей логарифмических элементов различны. Температурная нестабильность аддитивной погрешности N определяется в этом случае в основном неидентичностью-применяемых логарифмических элементов, например, для транзисторов разностью падений напряжений на переходах эмиттер - база. При этом даже лучшие пары интегральных транзисторов не обеспечивают полной идентичности. Так, например, разность падений напряжений на переходах эмиттер - база интегральной пары транзисторов К1НТ591 А равна 3 мВ, что приводит к погрешности логарифмирования, приведенной ко входу, порядка.10%. Компенсация разности падений напряжений на р-п переходах пары логарифмических элементов возможна, но это приводит к усложнению уст- . ройства и его настройки. При этом остается температурная чувствительность разности падений напряжений, которая составляет, например, для интегральной пары К1НТ591А величину В мкВ/С(10) 300°С

Такое значение температурной чувствительности приводит к погрешности логарифмирования, приведенной ко входу, равной 0,.

Лучшие зарубежные логарифмические устройства, в которых используется с целью компенсации аддитивной по грешности N разность логарифмов двух входных сигналов, имеют температурный коэффициент погрешности 0,02%. Таким образом, данный параметр не позволяет строить логарифми-i ческие вычислительные устройства, имеющие погрешность менее 0,1% в широком интервале температур. Следует также отметить, что транзисторы, выполненные в интегральном исполнении, хотя и обладают меньшим разбросом аддитивной погрешности N, но имеют большую погрешность несоответствия логарифму, принципиально неустранимую и дополнительно снижающую точность. Некоторые же дискретные элементы, например диоды АД 610, имеют погрешность несоответствия логарифму, что позволяет использовать их в широком диапазоне сигналов с большой точностью и к тому же обладают лучшими частотными свойствами в сравнении с интегральными парами транзисторов. Но выполнение равенства аддитивной погрешности дискретных логарифмических элементов практически трудно выполнимо как ло условию поддержания одинаковой -Температуры этих элементов (с точностью не хуже 0,005°С) так и по их временному дрейфу. В сравнении с аддитивной погрешностью N мультипликативная погрешность вносит в результат логарифмирования погрешность в 24 раза меньшую. Поскольку, как следует из выражения (9), мультипликативная погрешность К зависит только от температуры, то различие этого параметра для двух огарифмических элементов обусловлено неодинаковостью их температур. Причем требования по обеспечению одинаковой температуры логарифмических элементов для компенсаций с остаточной точностью мультипликативной погрешности К менее жесткие, ем для аддитивной погрешности N. Так, для достижения погрешности 0,033% достаточно поддержание разности температур 0,1° С, что сравнительно легко выполнимо. В предагаемом устройстве компенсация адитивной составляющей Ы осуществлятся также, как в прототипе, т.е. за счет использования одного логарифмического элемента для логарифирования двух входных сигналов, а омпенсация мультипликативной порешности К с достаточной точностью остигается за счет полдержаняя одинаковой температуры логарифмических

элементов, причем требования по точ ности в этом случае не являются жесткими. Это позволяет использовать в полной мере преимущества дискретных логарифмических элементов, а именно, быстродействие и ма,лую погрешность несоответствия логарифму и превзойти характеристики непрерывных вычислительных устройств по быстродействию (в пределах рабочего такта) с одновременным увеличением точности в широком интервале температур.

Представленный на чертеже вариант выполнения отдельных блоков устройства реализует выражение

V Чт

:ii)

с непрерывным преобразованием сигналов Y - Yff,, Логарифмические преобразователи 2 , - 2 вьтолнены на операционных усилителях с логарифмическими элементами в обратной связи . Обратимый логарифмический преобразователь 2 + -| выполнен по схеме обратимого функционального преобразователя. В качестве логарифмических элементов в логарифмических преобра.зователях применяются логарифмические диоды,

Масштабно-суммирующий блок рабо- . тает следующим образом.

Ключи 10 и 11 замкнуты соответственно в первый и второй такты, вследствие чего в первый такт в обратной связи инвертирующего усилителя подключается элемент 9 памяти, а во второй масштабный резистор 8. Положение ключей на чертеже соответствует первому такту работы устройства .

Устройство работает следующим образом.

В первый такт результаты логарифмирования сигналов Х - Х поступают на m + 1 входов масштабно-суммирующего блока 3, в котором они масштабируются с помощью масштабирующих резисторов, суммируются, и результат сутдашрования, соответствующий выражению (4 ), запоминается в элементе 9 памяти. Во второй такт происходит переключение переключателей 1 - 1гп+2 результате чего на вход устройства поступают сигналы Y,) - У, результаты логарифмирования которых поступают на т-входов масштабно-суммирующего блока 3, выход которого подключается к выходу-входу 6 обратимого логарифмического преобразователя 2, вход-выход 5 которого подключается к выходу Z устройства.

Таким образом, на вход масштабно-суммирующего блока 3 поступают результаты логарифмирования сигналов 5(Y - УТО и запомненный на элементе

памяти сигнал, ссютветствующий выражению (4), в результате чего на выходе масштабно-суммирующего блока 3 возникает сигнал, соответствующий выражению ( 5). Этот сигнал поступает на выход-вход 6 обрати ого логарифмического преобразователя 2,4 потенциируется и результат преобразования поступает на выход Z устройства.

Предлагаемый вариант устройства без существенных изменений принципиальной cxeNObi реализует также выражение вида

f Vv. f Ym ,m.. ,.„ Z - -(-7) . . . (-yi-J Х„+ (12

Л лЛ -«

с .непрерывным преобразованием сКгналов Y т Д этого достаточно поменять полярность включения диодов в обратимом логарифмическом преобразователе 2,к полярность си нала Х„+1 .

Следует добавить, что при изменении полярности входного сигнала и полярности включения диода в одном из логарифмических преобразователей знак степени этого сомножителя меняется на противоположный .

Таким образом, предложенный вариант устройства является универсальным, так как реализует все множите ль но- дели тельные и степенные опергцдии с незначительными переключения QI в принципиальной схеме.

Формула изобретения

0 вторые неподвижные контакты m переключателей являются соответственно первой н второй группами входов устройства, подвижные контакты m переключателей подключены соответственно к входам m логарифмических преобразователей, выходы которых подключены к соответствующим входам масштабно-суммирующего блока, управляющие входы m переключателей подключены к выходу блока управления.

выход которого через резистор обратной связи подключен к входу инвертирующего усилителя и к выходу второго ключа, который является выходом масштабно-суммирующего блока,

5 информационный вход второго ключа подключен к выходу элемента Пс1мяти, вход которого подключен к второму выводу m + 2-го масштабного резистора, второП вывод m + 1-го масштабного резистора является первым входом масштабно-суммирующего блока , вторые выводы m масштабных резисторов являются соответствующими входами машстабно-суммирующего блока,

5 Управляю11ие входы ключей объединены и являются управляющим входом масштабно-суммирующего блока.

Источники информации, принятые во внимание при экспертизе

0 1. Авторское свидетельство СССР , 467936, кл. G 06 G 7/24, 1972.

Авторы

Даты

1982-11-30—Публикация

1981-06-11—Подача