1

Изобретение относится к аналоговой вычислительной технике и может быть использовано в узлах формирования и преобразования сигналов, входящих в состав систем регулирования скорости электроприводов переменного и постоянного тока.

Известны множительные устройства, в которых для перемножения аналоговых сигналов используются полевые транзисторы, включенные на входе или в обвязке суммирующего операционного усилителя. Одним из пepeмнoжae влx сигналов осуществляется управление полевым транзистором, другой сигнал создает ток во входной цепи операционного усилителя 1.

Это множительное устройство не обеспечивает достаточную точность перемножения сигналов, так как зависимость сопротивления канала проводимости полевого транзистора от управляющего сигнала нелинейна, а предлагаемые в устройствах коррекции недостаточно зффективны.

Наиболее близким к предложенному является множительное устройство, содержащее источники первого и второго сомножителей, делитель напряжений, операционный усилитель с регу

лируемым коэффициентом усиления, вы- ход которого является выходом убтройства, два управляемых резистора, выполненные на полевых транзисторах, первые выводы управляемых резисторов объединены и подключены ко входу операционного усилителя, вторые выводы управляемых резисторов объединены и подключены ко входу делителя

10 напряжений и к источнику первого сомножителя, управляющий вход первого управляемого резистора подключен к выходу делителя напряжений, а управляющий вход второго управляемого ре15зистора подключен к выходу источника второго сомножителя 2 .

В данном множительном устройстве коррекция осуществляется за счет пропускания одного из перемножаемых

20 сигналов на вход операционного усилителя по двум каналам - основному и корректирующему (каналы проводимости полевых транзисторов). Этим же сигналом пропущенным через дели25тель, управляется транзистор корректирукядего канала. Вторым из перемножаемых сигнёшов осуществляется управление транзистором основного канала.

Если бы эависимостд сопротивления

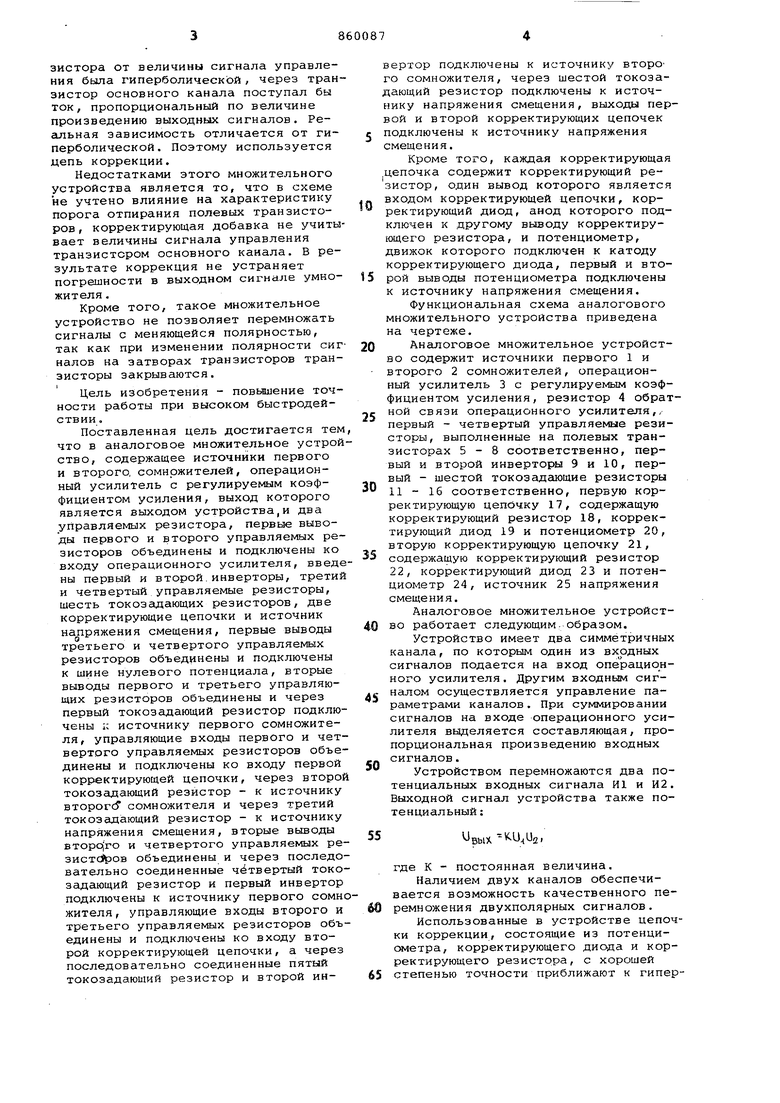

30 .канала проводимости полевого транзистора от величины сигнала управления была гиперболической, через тран зистор основного канала поступал бы ток, пропорциональный по величине произведению выходных сигналов. Регшьная зависимость отличается от гиперболической. Поэтому используется цепь коррекции. Недостатками этого множительного устройства является то, что в схеме не учтено влияние на характеристику порога отпирания полевых транзисторов , корректирующая добавка не учиты вает величины сигнала управления транзистором основного канала. В результате коррекция не устраняет погрешности в выходном сигнале умножителя. Кроме того, такое множительное устройство не позволяет перемножать сигналы с меняющейся полярностью, так как при изменении полярности сиг налов на затворах транзисторов транзисторы закрываются. Цель изобретения - повышение точности работы при высоком быстродействии. Поставленная цель достигается тем что в аналоговое множительное устрой ство, содержащее источники первого и второго, сомножителей, операционный усилитель с регулируемым коэффициентом усиления, выход которого является выходом устройства,и два управляемых резистора, первые выводы первого и второго управляемых ре зисторов объединены и подключены ко входу операционного усилителя, введ ны первый и второй.инверторы, трети и четвертый управляемые резисторы, шесть токозадающих резисторов, две корректирующие цепочки и источник напряжения смещения, первые выводы третьего и четвертого управляемых резисторов объединены и подключены к шине нулевого потенциала, вторые выводы первого и третьего управляющих резисторов объединены и через первый токозадающий резистор подклю чены ;с источнику первого сомножителя, управляющие входы первого и чет вертого управляемых резисторов объе динены и подключены ко входу первой корректирующей цепочки, через второ токозадающий резистор - к источнику второгсГ сомножителя и через третий токозещающий резистор - к источнику напряжения смещения, вторые выводы вторс го и четвертого управляемых ре зист( объединены и через последо вательно соединенные четвертый токо задающий резистор и первый инвертор подключены к источнику первого сомн жителя, управляющие входы второго и третьего управляемых резисторов объ единены и подключены ко входу второй корректирующей цепочки, а через последовательно соединенные пятый токозадающий резистор и второй инвертор подключены к источнику вторО го сомножителя, через шестой токозадающий резистор подключены к источнику напряжения смещения, выходы первой и второй корректирующих цепочек подключены к источнику напряжения смещения. Кроме того, каждая корректирующая цепочка содержит корректирующий резистор, один вывод которого является входом корректирующей цепочки, корректирующий диод, анод которого подключен к другому выводу корректирующего резистора, и потенциометр, движок которого подключен к катоду корректирующего диода, первый и второй выводы потенциометра подключены к источнику напряжения смещения. Функциональная схема аналогового множительного устройства приведена на чертеже. Аналоговое множительное устройство содержит источники первого 1 и второго 2 сомножителей, операционный усилитель 3 с регулируемым коэффициентом усиления, резистор 4 обратной связи операционного усилителя,/ первый - четвертый управляемые резисторы, выполненные на полевых транзисторах 5-8 соответственно, первый и второй инверторы 9 и 10, первый - шестой токозадгиощие резисторы 11 - 16 соответственно, первую корректирующую цепочку 17, содержащую корректирующий резистор 18, корректирующий диод 19 и потенциометр 20, вторую корректирующую цепочку 21, содержащую корректирующий резистор 22, корректирующий диод 23 и потенциометр 24, источник 25 напряжения смещения. Аналоговое множительное устройство работает следующим образом. Устройство имеет два симметричных канала, по которым один из входных сигналов подается на вход операционного усилителя. Другим входным сигналом осуществляется управление параметрами каналов. При суммировании сигналов на входе операционного усилителя выделяется составляющая, пропорциональная произведению входных сигналов. Устройством перемножаются два потенциальных входных сигнала И1 и И2. Выходной сигнал устройства также потенциальный : БЫХ-- ичи2, где К - постоянная величина. Наличием двух каналов обеспечивается возможность качественного перемножения двухполярных сигналов. Использованные в устройстве цепочки коррекции, состоящие из потенциометра, корректирующего диода и корректирующего резистора, с хорошей степенью точности приближают к гиперболической зависимости между сопротивлением цепей на входе операционного усилителя и входным сигналом аналогового множительного устройства, управляющими параметрами данных цепей. Входными цепями операционного ус лителя , являются цепь, состоящая из резистора 11 и управляемых резисторов 5 и 7, и цепь, состо5ццая из резистора 14 и управляемых резисторов 6 и 8. Все управляемые сопротивлени выполнены на полевых транзисторах с изолированным затвором. Во- входной цепи суммирующего опе рационного усилителя, состоящей из резисторов 11, 5 и 7, ток создается входным сигналом И1. Во входной цепи суммирующего операционного усилителя, состоящей из резисторов 14, б и 8, ток создается сигналом - И1, полученным инвертированием сигнала И1 инвертором 9. , На управляющие входы управляемых резисторов 5 и 8 подается сигнал . где Vfjff - постоянный сигнал смеще - (cM-fe.Mк - коэффициент (к - ( ) 12 На управляющие входы управляемых сопротивлений резисторов 6 и 8 подается сигнал U,np2-UcM-N 2 Сигнал - И2 формируется с помощь инвертора 10. Известно, что зависимость сопротивления проводящего канала полевог транзистора с изолированным затвором от величины сигнала управления близка к гиперболической канала где А - постоянная величина, соот ветствующая параметрам полевого транзистора; и - потенциал порога отпирани полевого транзистора. При управлении управляемыми рези сторами 5 и 8 таким сигналом + Kj И2, в котором U(, а К,- .-ип, сопротивление канал t- J проводимости транзисторов 5a 4M-UoVK,U2 При управлении управляемыми рези сторами 7 и 6 сигналом U)(-К. И сопротивление каналов проводимости транзисторов р -- Р г WcNv-UoV Oa На вход операционного усилителя поступает ток 1 через управляемый резистор 5 и ток i через управляемый резистор 6. Каждый из двух входных токов имеет составляющую, пропорциональную произведению И1И2, и составляющую, пропорциональную только И1. Суммарный входной ток усилителя г. 2 iR UcM-Uot Составляющие токов, пропорциональные только И1, взаимно компенсируются. Выходной сигнал усилителя S 4 2R4K,U,U выч- 2Числл-ио 2R.K Так как является погл исм-ио)+А стоянной величиной гггт- ----const-K, vUcM-UoltA то выходной сигнал устройства умноженияUB,,x--KU,U2 . Чтобы реальная зависимость между величиной сопротивления канала проводимости полевого транзистора и величиной сигнала управления не отличалась от гиперболической, в устройстве осуществляется ограничение разности потенциалов на электродах полевых транзисторов и используются цепи коррекции. Ограничение разности потенциалов на электродах транзисторов достигается включением резисторов 11 и 14 последовательно с каналами проводимости полевых транзисторов и резисторных делителей (11-13, 14-16) в цепях управления полевых транзисторов. Такое ограничение необходимо, поскольку зависимость между сопротивлениями полевых транзисторов и сигнапом управления близка к гиперболической только в узком диапазоне сигналов управления (и„.+ди) и при близких к нулю значениях разности потенциалов между стоком и истоком. Даже при ограничении разностей потенциалов на электродах полевого транзистора его реальная характеристика такова, что при больших отклонениях от рабочей точки (U) выходной сигнал усилителя 3 практически получается несколько большим, чем произведение . Для ликвидации,этого несоответствия и используются цепи коррекции (потенциометры 20 и 24, корректи рующие диоды 19 и 23, корректирующие резисторы 18 и 22), которые так воздействуют на величину сопротивлений полевых транзисторов, что выходной сигнсШ устройства снижается. Изобретение обеспечивает качественное перемножение двух анашоговых знакопеременных сигналов при высоком быстродействии. Формула изобретения 1. Аналоговое множительное устрой ство, содержащее источники первого и второго сомножителей, операционный усилитель с регулируемым коэффициентом усиления, выход которого является выходом устройства, и два управляемых резистора, первые выводы первого и второго управляемых резисторов объединены и подклю чены ко входу операционного усилите ля, о тличающееся тем, что с целью повышения точности работы при высоком быстродействии, в устройство введены первый и второй инверторы, третий и четвертый управля емые резисторы, шесть токозадающих резисторов, две корректирующие цепочки и источник напряжения смещени первые выводы третьего и четвертого управляемых резисторов объединены и подключены к шине нулевого потенциа ла, вторые выводы первого и третьег управляющих резисторов объединены и через первый токозгщающий резистор подключены к источнику первого сомно жителя, управляющие входы первого и четвертого управляемых резисторов о единены и подключены ко входу первой корректирующей цепочки, через второй токозадающий резистор - к источнику второго сомножителя и через третий токов ад ёцощий резистор - к источнику напряжения смещения, вторые выводы второго и четвертого управляемых резисторов объединены и через последовательно соединенные четвертый токозадающий резистор и первый инвертор подключены к источнику первого сомножителя, управляющие входы второго и третьего управляемых резисторов объединены и подключены ко входу второй корректирующей цепочки, а через последовательно соединенные пятый токозадающий резистор и второй инвертор подключены к источнику второго сомножителя, через шестой токозадающий резистор подключены к источнику напряжения смещения, выходы первой и второй корректирующих цепочек подключены к источнику напряжения смещения, 2, Устройство по п, 1, отличающееся тем, что каждая корректирующая цепочка содержит корректирующий резистор, один вывод которого является входом корректирующей цепочки, корректирующий atton, анод которого подключен к другоку выводу корректирующего резистора, и потенциометр, движок которого подключен к катоду корректирующего диода, первый и второй выводил потенциталетра подключены к источнику напряжения смещения, Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР 432526, кл, G Об G 7/16, 1972, 2,Авторское свидетельство СССР 430384, кл, G 06 G 7/163, 1973 (прототип) ,