(54) УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1982 |

|

SU1056250A2 |

| Устройство для сжатия информации | 1979 |

|

SU809297A1 |

| Устройство для сжатия информации | 1980 |

|

SU947897A2 |

| Устройство для сжатия информации | 1980 |

|

SU930333A1 |

| Мост для измерения омических сопротивлений электрических цепей,находящихся под напряжением | 1981 |

|

SU1004892A1 |

| Устройство для контроля работы транспортного средства | 1986 |

|

SU1345222A1 |

| Устройство для квантования случайного процесса | 1974 |

|

SU516188A1 |

| Устройство для измерения динамических характеристик аналого-цифровых преобразователей | 1978 |

|

SU738151A1 |

| Способ взвешивания движущихся объектов | 1990 |

|

SU1800269A1 |

| Устройство для сжатия и передачи информации | 1988 |

|

SU1515183A1 |

Изобретение относится к электроизмерительной и вычислительной технике и предназначено для преобразования стационарных эргодических случайных сигналов в цифровой код. Известно устройство аналого-цифрового преобразования, состоящее из аналого-цифрового преобразователя, первого и второго регистров, сумматора-вычитателя, блока сраанения и блока задатчика ошибки, причем на первый вход аналого-цифрового преобразователя подан входной сигнал, на второй вход подан сигнал «Пуск, выход его соединен с входом первого регистра, выход которого соединен с первым входом сумматора-вычитателя, второй вход последнего соединен с выходом второго регистра 1. Недостатком известного устройства является отсутствие возможности аналого-цифрового преобразования с заданной среднеквадратической погрешностью восстановления. Цель изобретения - оптимизация выбора интервала временной дискретизации, обеспечивающего заданную среднеквадратическую погрешность восстановления преобразуемого сигнала. Поставленная цель достигается тем, что в известное устройство аналого-цифрового преобразования, содержащее блок задания ошибок, блок сравнения, преобразователь аналог-код, первый вход которого соединен с входной шиной, второй - с шиной «Пуск, а выход - с входом первого регистра и первым входом второго регистра, выход которого соединен с выходной шиной и первым входом блока суммирования и вычитания, введены счетчик, регулируемый делитель частоты, два блока усреднения, умножитель, два квадратора, вход первого из которых соединен с выходом первого регистра и вторым входом блока суммирования и вычитания, а выход - с входом первого блока усреднения, выход которого соединен с первым входом умножителя, второй вход которого соединен с блоком задания ошибки, а выход - с первым входом блока сравнения, при этом вход второго квадратора соединен с выходом блока суммирования и вычитания, а выход - с входом второго блока усреднения, выход которого соединен со вторым входом блока сравнения, выход которого соединен с первым входом регулируемого делителя частоты, второй вход - через счетчик с шиной «Пуск, а выход - со вторым входом второго регистра.

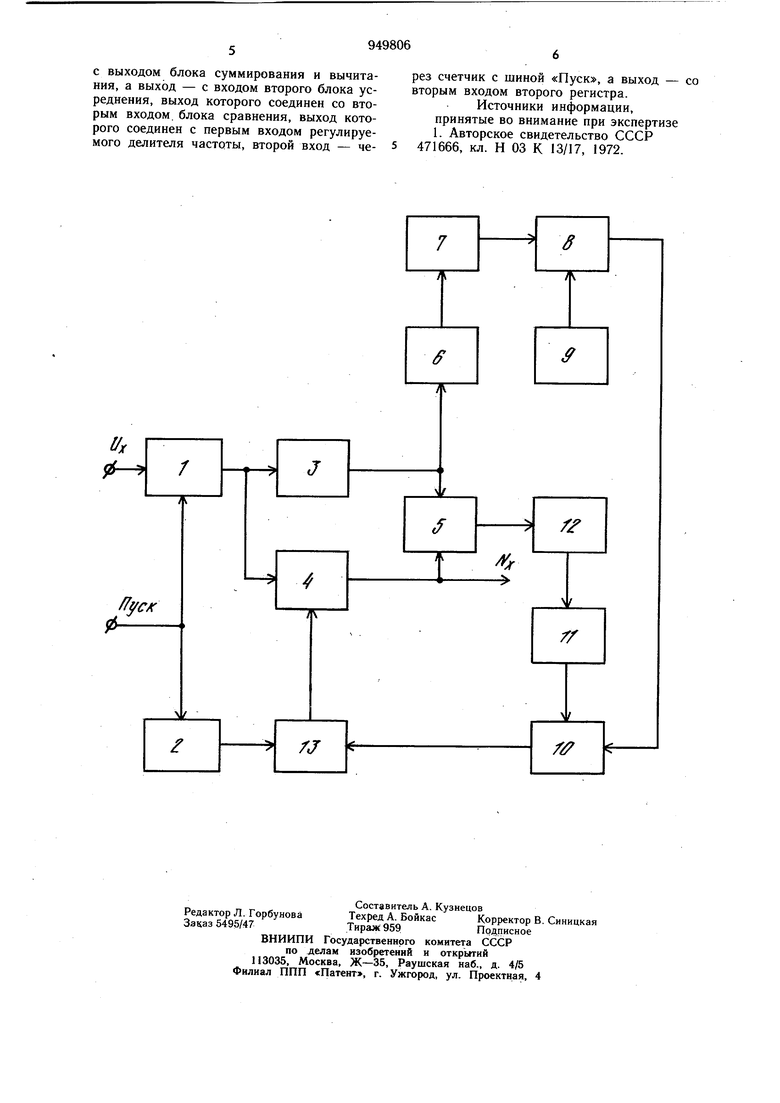

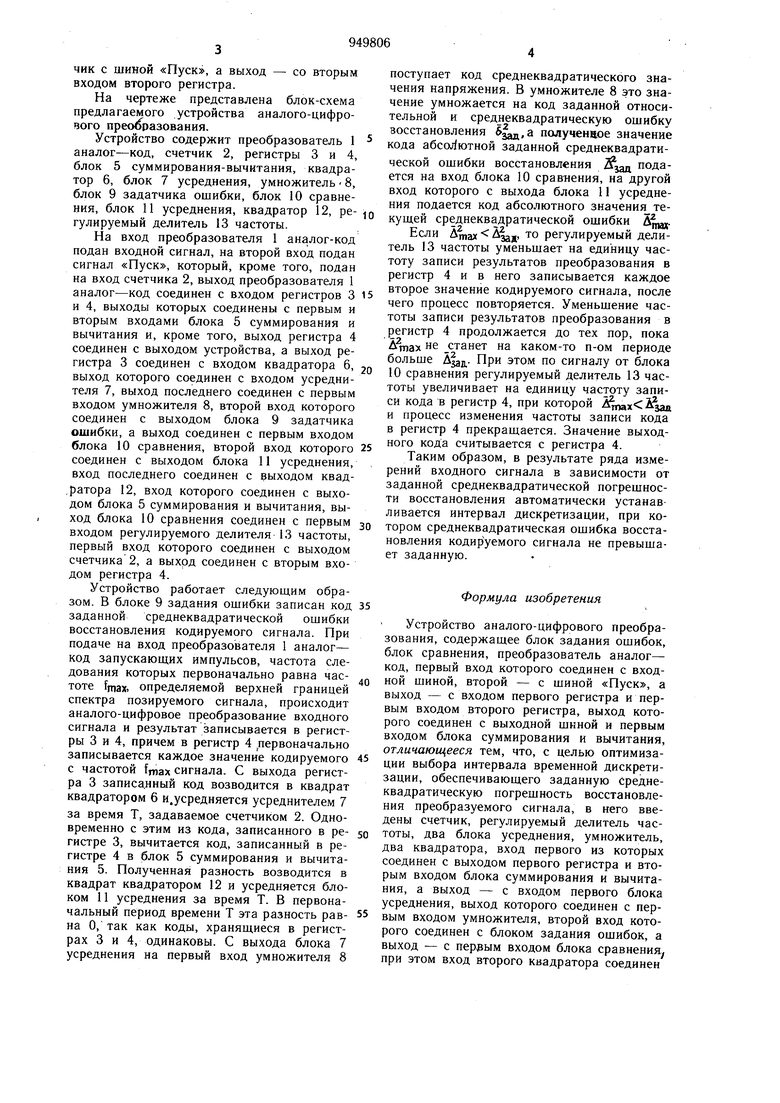

На чертеже представлена блок-схема предлагаемого устройства аналого-цифрового преобразования.

Устройство содержит преобразователь 1 аналог-код, счетчик 2, регистры 3 и 4, блок 5 суммирования-вычитания, квадратор 6, блок 7 усреднения, умножитель 8, блок 9 задатчика ошибки, блок 10 сравнения, блок 11 усреднения, квадратор 12, регулируемый делитель 13 частоты.

На вход преобразователя 1 аналог-код подан входной сигнал, на второй вход подан сигнал «Пуск, который, кроме того, подан на вход счетчика 2, выход преобразователя 1 аналог-код соединен с входом регистров 3 и 4, выходы которых соединены с первым и вторым входами блока 5 суммирования и вычитания и, кроме того, выход регистра 4 соединен с выходом устройства, а выход регистра 3 соединен с входом квадратора б, выход которого соединен с входом усреднителя 7, выход последнего соединен с первым входом умножителя 8, второй вход которого соединен с выходом блока 9 задатчика ошибки, а выход соединен с первым входом блока 10 сравнения, второй вход которого соединен с выходом блока 11 усреднения, вход последнего соединен с выходом квад.ратора 12, вход которого соединен с выходом блока 5 суммирования и вычитания, выход блока 10 сравнения соединен с первым входом регулируемого делителя 13 частоты, первый вход которого соединен с выходом счетчика 2, а выход соединен с вторым входом регистра 4.

Устройство работает следующим образом. В блоке 9 задания ошибки записан код заданной среднеквадратической ошибки восстановления кодируемого сигнала. При подаче на вход преобразователя 1 аналог- код запускаюш,их импульсов, частота следования которых первоначально равна частоте fjtiax. определяемой верхней границей спектра позируемого сигнала, происходит аналого-цифровое преобразование входного сигнала и результат записывается в регистры 3 и 4, причем в регистр 4 первоначально записывается каждое значение кодируемого с частотой fmax сигнала. С выхода регистра 3 записанный код возводится в квадрат квадратором 6 и.усредняется усреднителем 7 за время Т, задаваемое счетчиком 2. Одновременно с этим из кода, записанного в регистре 3, вычитается код, записанный в регистре 4 в блок 5 суммирования и вычитания 5. Полученная разность возводится в квадрат квадратором 12 и усредняется блоком 11 усреднения за время Т. В первоначальный период времени Т эта разность равна О, так как коды, хранящиеся в регистрах 3 и 4, одинаковы. С выхода блока 7 усреднения на первый вход умножителя 8

поступает код среднеквадратического значения напряжения. В умножителе 8 это значение умножается на код заданной относительной и среднеквадратическую ошибку восстановления ,а полученаое значение кода абсолютной заданной среднеквадратической ошибки восстановления подается на вход блока 10 сравнения, на другой вход которого с выхода блока 11 усреднения подается код абсолютного значения текущей среднеквадратической ошибки А Если Дтах Дзая регулируемый делитель 13 частоты уменьшает на единицу частоту записи результатов преобразования в регистр 4 и в него записывается каждое второе значение кодируемого сигнала, после чего процесс повторяется. Уменьшение частоты записи результатов преобразования в регистр 4 продолжается до тех пор, пока 6 станет на каком-то п-ом периоде больше При этом по сигналу от блока 10 сравнения регулируемый делитель 13 частоты увеличивает на единицу частоту записи кода в регистр 4, при которой и процесс изменения частоты записи кода в регистр 4 прекращается. Значение выходного кода считывается с регистра 4.

Таким образом, в результате ряда измерений входного сигнала в зависимости от заданной среднеквадратической погрешности восстановления автоматически устанавливается интервал дискретизации, при котором среднеквадратическая ощибка восстановления кодируемого сигнала не превышает заданную.

Формула изобретения

Устройство аналого-цифрового преобразования, содержащее блок задания ошибок, блок сравнения, преобразователь аналог- код, первый вход которого соединен с входной шиной, второй - с шиной «Пуск, а выход - с входом первого регистра и первым входом второго регистра, выход которого соединен с выходной шиной и первым входом блока суммирования и вычитания, отличающееся тем, что, с целью оптимизации выбора интервала временной дискретизации, обеспечивающего заданную Среднеквадратическую погрешность восстановления преобразуемого сигнала, в него введены счетчик, регулируемый делитель частоты, два блока усреднения, умножитель, два квадратора, вход первого из которых соединен с выходом первого регистра и вторым входом блока суммирования и вычитания, а выход - с входом первого блока усреднения, выход которого соединен с первым входом умножителя, второй вход которого соединен с блоком задания ошибок, а выход - с перзым входом блока сравнения при этом вход второго квадратора соединен

с выходом блока суммирования и вычитания, а выход - с входом второго блока усреднения, выход которого соединен со вторым входом, блока сравнения, выход которого соединен с первым входом регулируемого делителя частоты, второй вход -

рез счетчик с шиной «Пуск, а выход - со вторым входом второго регистра. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 471666, кл. Н 03 К 13/17, 1972.

Авторы

Даты

1982-08-07—Публикация

1980-04-21—Подача