Изобретение относится к устройствам связи и может быть использовано для фор1-1ирования потока безызбыточных при передаче телеметрических данных о цифровых изображениях.

Цель изобретения - повышение информативности устройства.

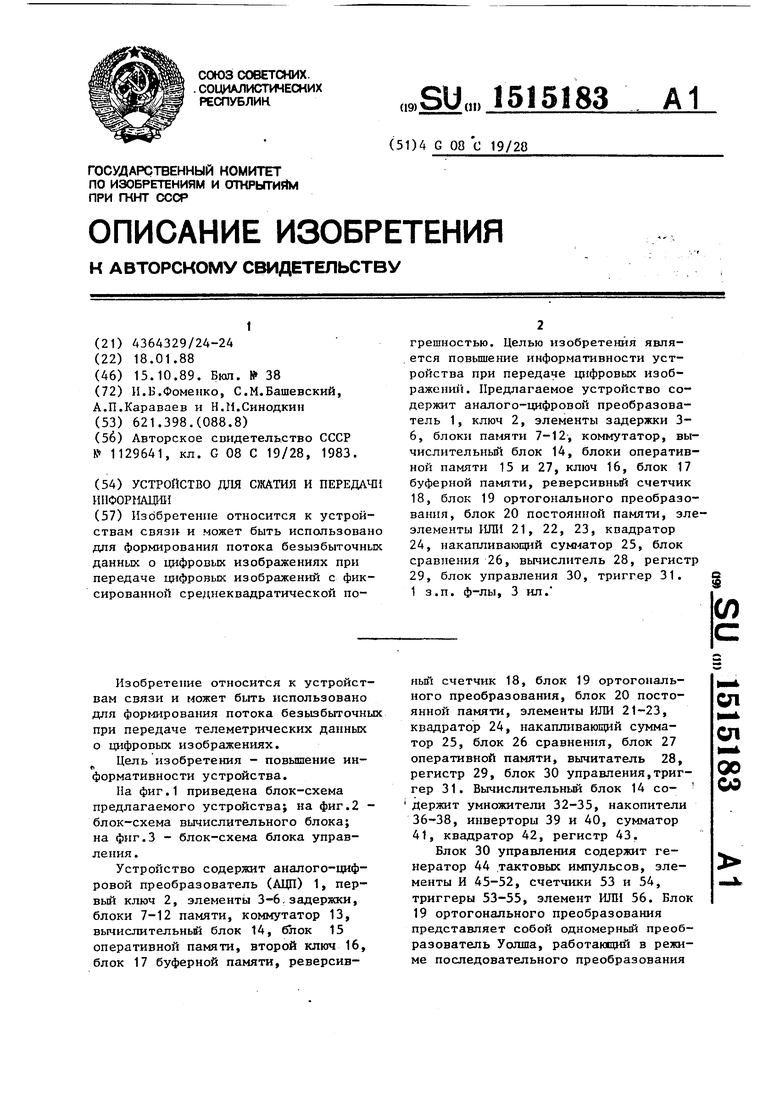

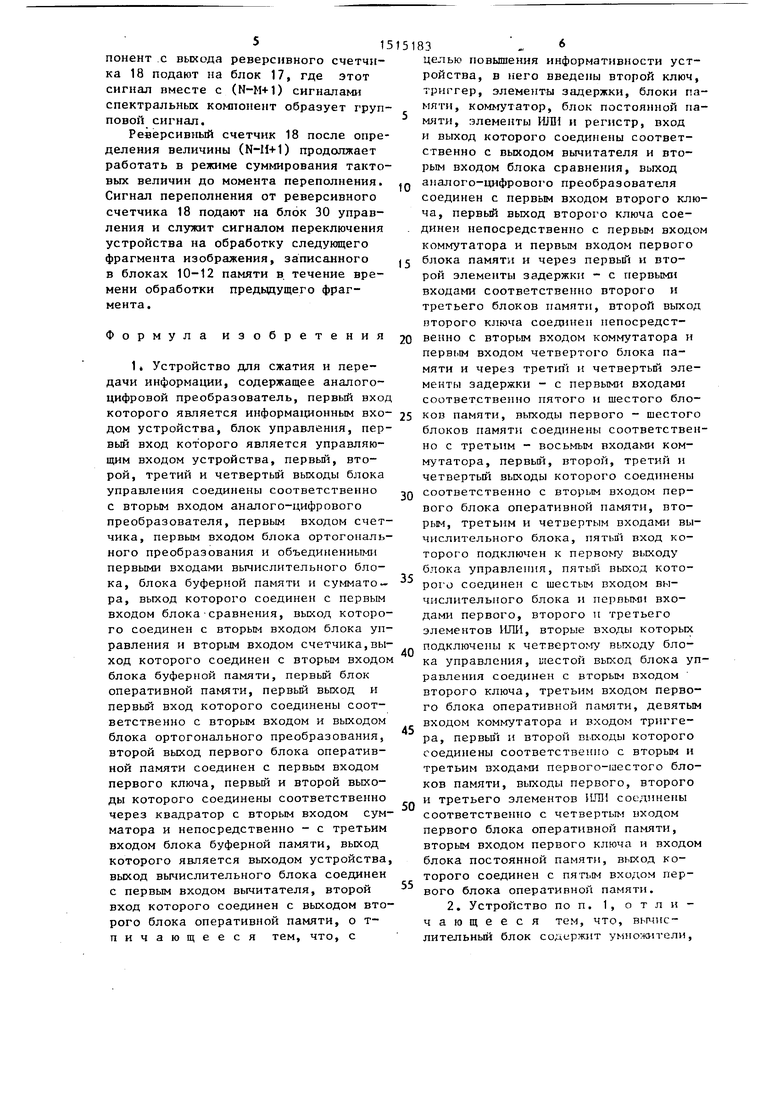

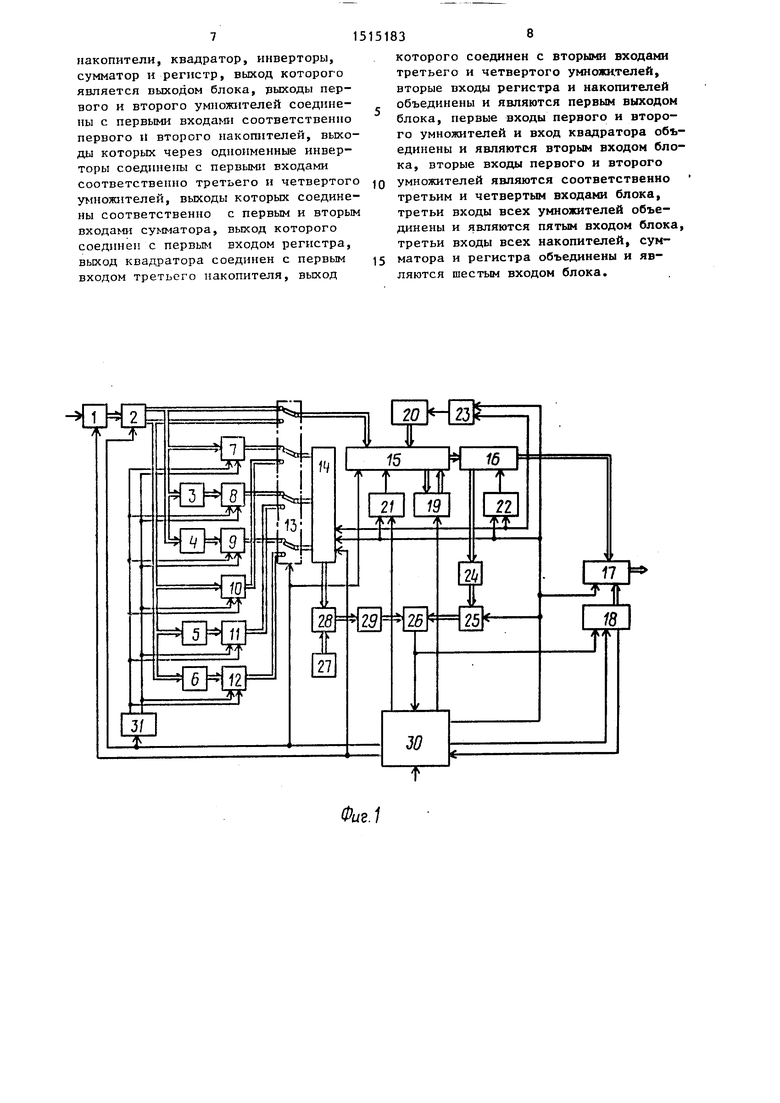

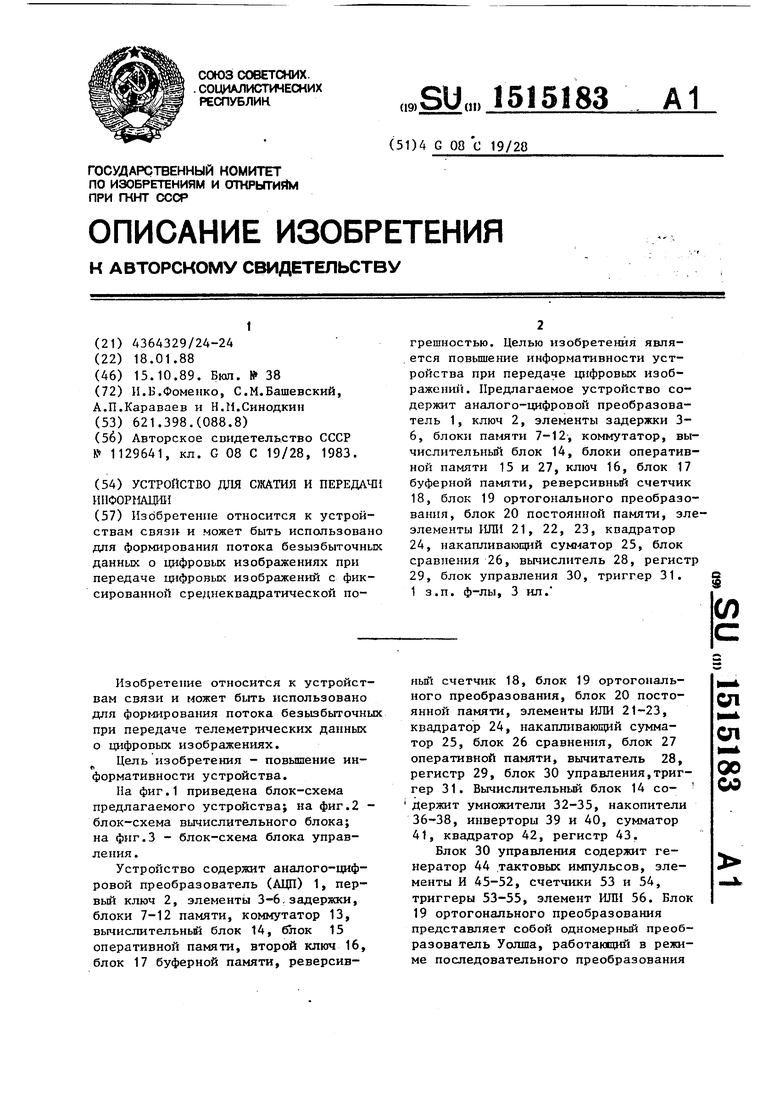

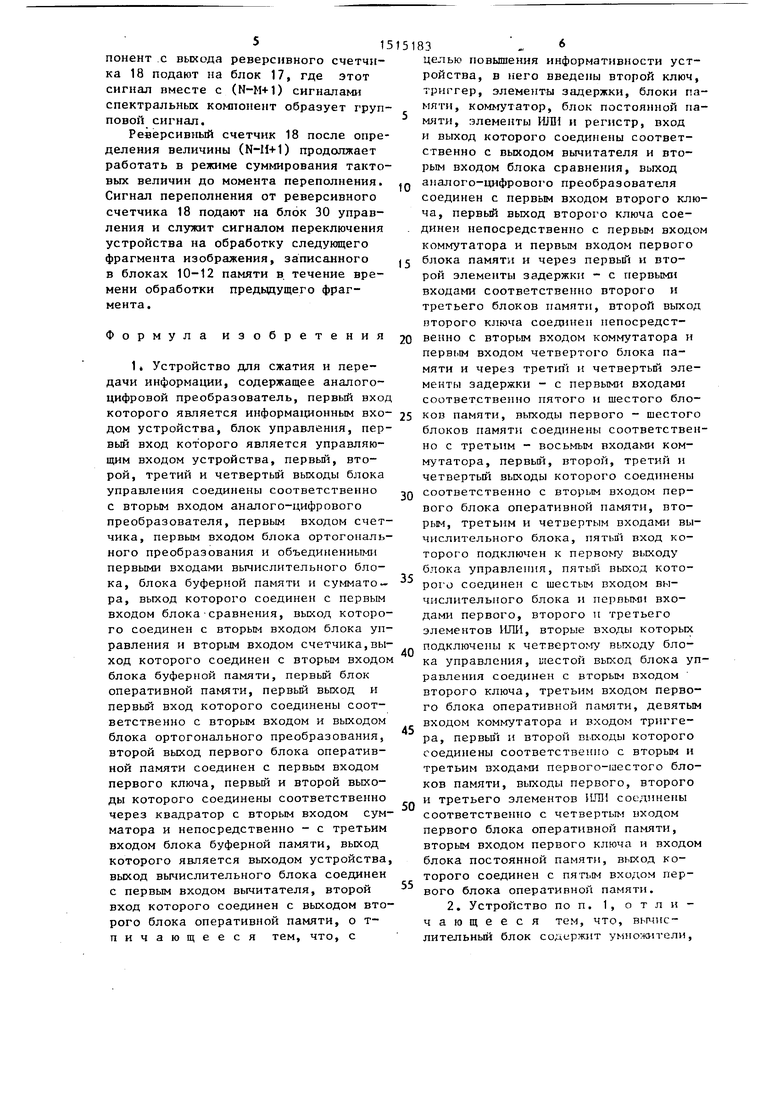

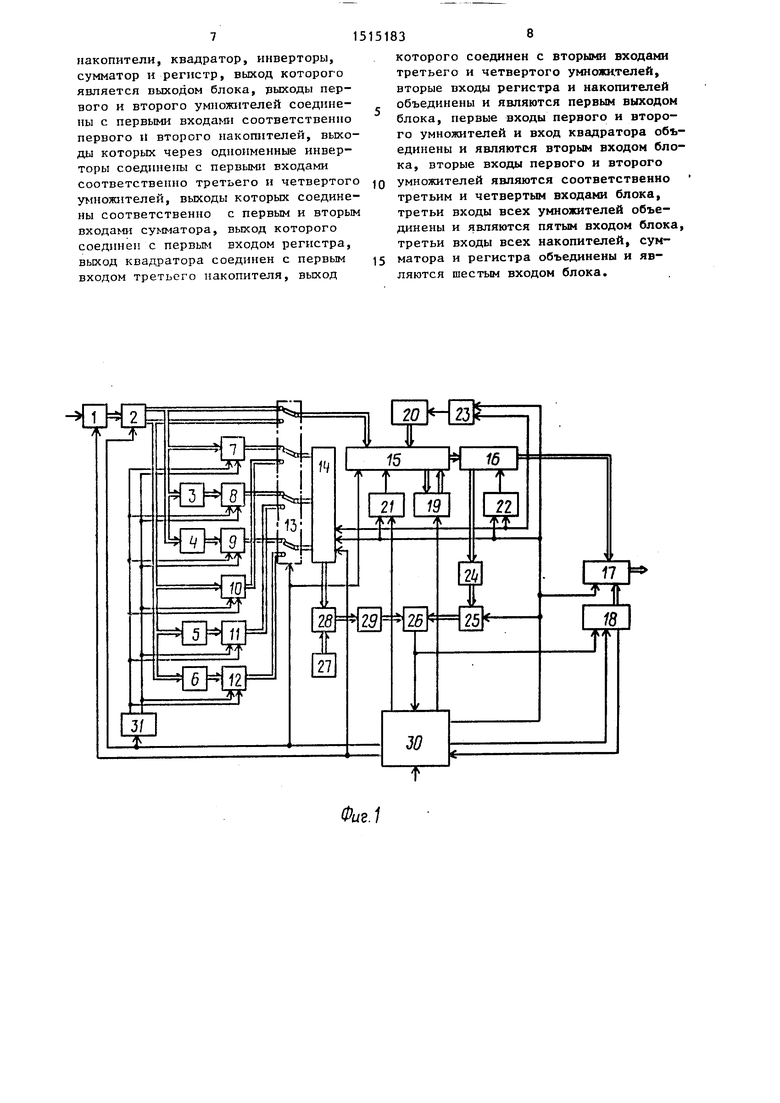

На фиг.1 приведена блок-схема предлагаемого устройства; на фиг.2 - блок-схема вычислительного блока; на фиг.З - блок-схема блока управления.

Устройство содержит аналого-цифровой преобразователь (АЦП) 1, пер вьй ключ 2, элементы 3-6,задержки, блоки 7-12 памяти, комьтутатор 13, вычислительный блок 14, блок 15 оперативной памяти, второй ключ 16, блок 17 буферной памяти, реверсивный счетчик 18, блок 19 ортогонального преобразования, блок 20 постоянной памяти, элементы ИЛИ 21-23, квадратор 24, накапливающий сумматор 25, блок 26 сравнения, блок 27 оперативной памяти, вычитатель 28, регистр 29, блок 30 управления,триггер 31. Вычислительный блок 14 со- Держит умножители 32-35, накопители 36-38, инверторы 39 и 40, сумматор 41, квадратор 42, регистр 43.

Блок 30 управления содержит генератор 44 тактовых импульсов, элементы И 45-52, счетчики 53 и 54, триггеры 53-55, элемент ИЛИ 56. Блок 19 ортогонального преобразования представляет собой одномерный преобразователь Уолша, работающий в режиме последовательного преобразования

СП СП

сх со

строк фрагмента в построчные спектры Уолша.

Устройство-работает следующим образом.

Перед началом работы сигналом Сброс от блока 30 управления производят установку нулевых начальных условий в блоках 15, 17, 20. и 27 памяти, вычислительном блоке 14, накапливающем сумматоре 25. Затем на вход АЦП 1 подают выборки первого фрагмента изображения. На выходе АЦП 1 с частотой тактирующих импульсов с первого выхода блока 30 управления получакгг Njf-Nj p - битовых отсчетов первого фрагмента в виде параллельного кода. Шаг дискретизации выбирают, исходя из максимальной ожидаемой частоты в спектре сигнала. Через ключ 2 отсчеты подают на блок

7памяти непосредственно, на блоки

8и 9 памяти через элементы 3 и 4 задержки. В этих блоках 7-9 записывают

матрицу N ,f ГЦ отсчетов первого фраг-25 . ошибки преобразования мента. По сигналу считывания с шестого выхода блока 30 записанные отсчеты подают на второй, третий и четвертый входы вычислительного блока 14,

,

Этот сигнал 6 подают где запоминают. В блок 30 Дят сравнение сигнала ошибки преобразования лом , равным теку образования Ср изводят до тех пор, по полняться условие

где по отсчетам фрагментавычисляют

ошибки дискретизации 6,,. и6 по коС X :з

ординатам х и у

где

координатам х и у;

R (л) , Ry(4) -первые отсчеты нормированных автокорреляционных функций сигнала по координатам хну при значении аргумента, равном шагу дискретизации л. По значениям сигналов 6„ и определяют сигнал квадрата общей текущей ошибки дискретизации

.

которьй запоминают на регистре 43.

Отсчеты фрагмента, прошедшие через коммутатор 13, подают на блок 15 где запоминают. .По команде с шестого выхода блока 30 управления отсчеты из блока 15 передают в блок 19 ортогонального преобразования, где определяют N ( N д сигналов ортогональ- ньсх спектральных компонент С jj , которые запоминают в блоке 15. Из блока 15 через ключ 16 сигналы ортогональных спектральных компонент подают либо в квадратор 24, либо в блок 17 буферной памяти.

Сигналы спектральных компонент получают на выходе блока 15 после одномерного зигзагообразного упорядочения по номерам, вьщанным блоком 20 в блок 15 по командам от блока 30 управления. В накапливающем сумматоре 25 формируют Сигнал, пропорциональный сумме квадратов сигналов ортогональных спектральных компонент, причем суммирование начинают с наи- большего номера и ведут в направлении меньших номеров. На вычитатель 28 подают сигнал квадрата общей текущей ошибки дискретизации б от вычислительного блока 14 и сигнал квадрата допустимой ошибки восстановления от блока 17 на выходе вычитате- ля 28 - сигнал квадрата допустимой

5 . ошибки преобразования

5

,

Этот сигнал 6 подают на регис тр 29, где запоминают. В блоке 26 произво- 0 Дят сравнение сигнала допустимой ошибки преобразования 6, с сигналом , равным текущей ошибке преобразования Сравнение производят до тех пор, пока не будет выполняться условие

ic, .6

(N«W)

где М - количество шагов сравнения.

С выхода блока 26 сравнения при 0 выполнении условия () получают сигнал, поступающий на блок 30 управления, где вырабатьшают сигнал переключения выхода ключа 16 на блок 17. В блок 17 записьшают из блока 15 сиг- Нсшы начальных спектральных компонент.

Реверсивный счетчик 18 определяет наибольший номер (N-M+1) сигнала спектральной компоненты, которым можно ограничить ряд сигналов существенных спектральньк компонент, начиная от C(j . Реверсивный счетчик 18 начинает работать одновременно с началом операции сравнения () и вьща- ет результат (N-M+1) при выполнении условия () по команде сигнала с выхода блока 26 сравнения. Сигнал о количестве (N-M-V1) передаваемых в канал Связи сигналов спектральных ком5

0

5,

понент с выхода реверсивного счетчика 18 подают на блок 17, где этот сигнал вместе с (N-M+I) сигналами спектральных компонент образует групповой сигнал.

Реверсивный счетчик 18 после определения величины (N-11+1) продолжает работать в режиме суммирования тактовых величин до момента переполнения. Сигнал переполнения от реверсивного счетчика 18 подают на блок 30 управления и служит сигналом переключения устройства на обработку следующего фрагмента изображения, записанного в блоках 10-12 памяти в. течение времени обработки предьщущего фрагмента.

Формула изобретения

1« Устройство для сжатия и передачи информации, содержащее аналого- цифровой преобразователь, первый вход которого является информа1р1онным входом устройства, блок управления, первый вход которого является управляющим входом устройства, первьй, второй, третий и четвертый выходы блока управления соединены соответственно с вторым входом аналого-цифрового преобразователя, первым входом счетчика, первым входом блока ортогонального преобразования и объединенными первыми входами вычислительного блока, блока буферной памяти и сумматора, выход которого соединен с первым входом блока-сравнения, выход которого соединен с вторым входом блока управления и вторым входом счетчика,выход которого соединен с вторым входом блока буферной памяти, первый блок оперативной памяти, первый выход и первый вход которого соединены соответственно с вторым входом и выходом блока ортогонального преобразования, второй выход первого блока оперативной памяти соединен с первым входом первого ключа, первый и второй выходы которого соединены соответственно через квадратор с вторым входом сумматора и непосредственно - с третьим входом блока буферной памяти, выход которого является выходом устройства выход вычислительного блока соединен с первым входом вычитателя, второй вход которого соединен с выходом второго блока оперативной памяти, о т- пичающееся тем, что, с

5183 6

повышения информативности устройства, в него введены второй ключ, триггер, элементы задержки, блоки памяти, коммутатор, блок постоянной памяти, элементы ИЛИ и регистр, вход и выход которого соединены соответственно с выходом вычитателя и вторым входом блока сравнения, выход

Q аналого-цифрового преобразователя

соединен с первым входом второго ключа, первьй выход второго ключа соединен непосредственно с первым входом коммутатора и первым входом первого

5 блока памяти и через первьп и второй элементы задержки - с первыми входами соответственно второго и третьего блоков памяти, второй выход второго ключа соединен непосредст0 венно с вторым входом коммутатора и первым входом четвертого блока памяти и через третш и четвертый элементы задержки - с первыми входами соответственно пятого и шестого бло5 КОБ памяти, выходы первого - шестого блоков памяти соединены соответственно с третьим - восьмым входами коммутатора, первый, второй, третий и четвертый выходы которого соединены

Q соответственно с вторым входом первого блока оперативной памяти, вторым, третьим и четвертым входами вычислительного блока, пятьп вход которого подключен к пepвo гy выходу блока управления, пятый выход которого соединен с шестым входом вычислительного блока и перяыми входами первого, второго и третьего элементов ИЛИ, вторые входы которых подключены к 4eTBepTONry выходу блока управления, кюстой выход блока управления соединен с вторым входом второго ключа, третьим входом первого блока оперативной памяти, девятым входом коммутатора и входом триггера, первьш и второй выходы которого соединены соответственно с вторым и третьим входами первого-шестого блоков памяти, выходы первого, второго и третьего элементов ИЛИ соединены

5

0

5

0

5

соответственно с четвертым входом первого блока оперативной памяти, вторым входом первого ключа и входом блока постоянной памяти, выход которого соединен с пяп.м входом первого блока оперативной памяти.

2, Устройство по п. 1, отличающееся тем, что, вычислительный блок содержит умножители.

накопители, квадратор, инверторы, сумматор и регистр, вькод которого является выходом блока, рыходы первого и второго умножителей соединены с первыми входами соответственно первого It второго накопителей, выходы которых через одноименные инверторы соединены с первыми входами соответственно третьего и четвертого умножителей, выходы которых соединены соответственно с первым и вторым входами сумматора, выход которого соединен с первьв входом регистра, выход квадратора соединен с первым входом третьего накопителя, выход

которого соединен с вторыми 3 oR&tm третьего и четвертого умножнтелей, вторые входы регистра и накопителей объединены и являются первым выходом блока, первые входы первого и второго умножителей и вход квадратора объединены и являются вторым входом блока, вторые входы первого и второго умножителей являются соответственно третьим и четвертым входами блока, третьи входы всех умножителей объединены и являются пятым входом блока, третьи входы всех накопителей, сумматора и регистра объединены и являются шестым входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи телеметрической информации | 1983 |

|

SU1129641A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1126993A1 |

| Устройство для кодирования сигналов звукового вещания | 1990 |

|

SU1774500A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Устройство для контроля работы транспортного средства | 1986 |

|

SU1345222A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1997 |

|

RU2115135C1 |

| Устройство для вычисления спектра сигналов | 1988 |

|

SU1649566A1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Цифровой анализатор спектра речевого сигнала | 1982 |

|

SU1126969A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

Изобретение относится к устройствам связи и может быть использовано для формирования потока безызбыточных данных о цифровых изображениях при передаче цифровых изображений с фиксированной среднеквадратической погрешностью. Целью изобретения является повышение информативности устройства при передаче цифровых изображений. Предлагаемое устройство содержит аналого-цифровой преобразователь 1, ключ 2, элементы задержки 3-6, блоки памяти 7-12, коммутатор, вычислительный блок 14, блоки оперативной памяти 15 и 27, ключ 16, блок 17 буферной памяти, реверсивный счетчик 18, блок 19 ортогонального преобразования, блок 20 постоянной памяти, элементы ИЛИ 21, 22, 23, квадратор 24, накапливающий сумматор 25, блок сравнения 26, вычислитель 28, регистр 29, блок управления 30, триггер 31. 1 з.п. ф-лы, 3 ил.

вых.В

4-5

-

Вы(.1

вьи.5

Авторы

Даты

1989-10-15—Публикация

1988-01-18—Подача