(54) ПРЕОБРАЗОВАТЕЛЬ ФАЗОВОГО СДВИГА ВО ВРЕМЕННОЙ ИНТЕРВАЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь фазового сдвига во временной интервал | 1978 |

|

SU783704A2 |

| Преобразователь фазового сдвига во временной интервал | 1983 |

|

SU1088113A1 |

| Преобразователь фазового сдвига во временной интервал | 1976 |

|

SU678666A1 |

| Преобразователь фазового сдвига в временной интервал | 1984 |

|

SU1239628A1 |

| ШИРОКОДИАПАЗОННЫЙ ВОЛОКОННО-ОПТИЧЕСКИЙ ИЗМЕРИТЕЛЬ УГЛОВОЙ СКОРОСТИ | 2002 |

|

RU2227272C2 |

| Преобразователь фазового сдвига во временной интервал | 1984 |

|

SU1239627A2 |

| Синхронно-синфазный электромагнитный вибропривод | 1980 |

|

SU964885A1 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1285392A1 |

| Фазометр | 1980 |

|

SU890266A2 |

1

Изобретение относится к электроизмерениям и может быть использовано при измерении фазовых сдвигов.

Известен преобразователь фазового сдвига во временной интервал, содержащий два триггера, источник опорного напряжения, два интегратора, три ключа, инвертор, детектор нуля, дополнительный триггер и два формирователя коротких импульсов, выход одного из которых подключен к первому входу первого триггера, второй вход которого соединен с выходом второго формирователя коротких импульсов и со счетным входом второго триггера, причем выход источника опорного напряжения подключен к потенциальным входам первого и второго ключей, управляющие входы которых соединены соответственно с выходом первого триггера и с прямым выходом второго триггера, инверсный выход которого подключен к первым входам третьего ключа и дополнительного триггера, выход первого ключа через первый интегратор и детектор нуля соединен с вторым входом дополнительного триггера, выход второго ключа через второй интегратор и инвертор подключен к второму входу

третьего ключа, выход -которого связан с входом первого интегратора 1.

Недостатком известного устройства является невысокая точность работы.

Известен также преобразователь фазового сдвига во временной интервал, содержащий источник опорного напряжения, три триггера, три интегратора, четыре ключа, инвертор, детектор нуля, задатчик времени и два формирователя коротких импульсов.

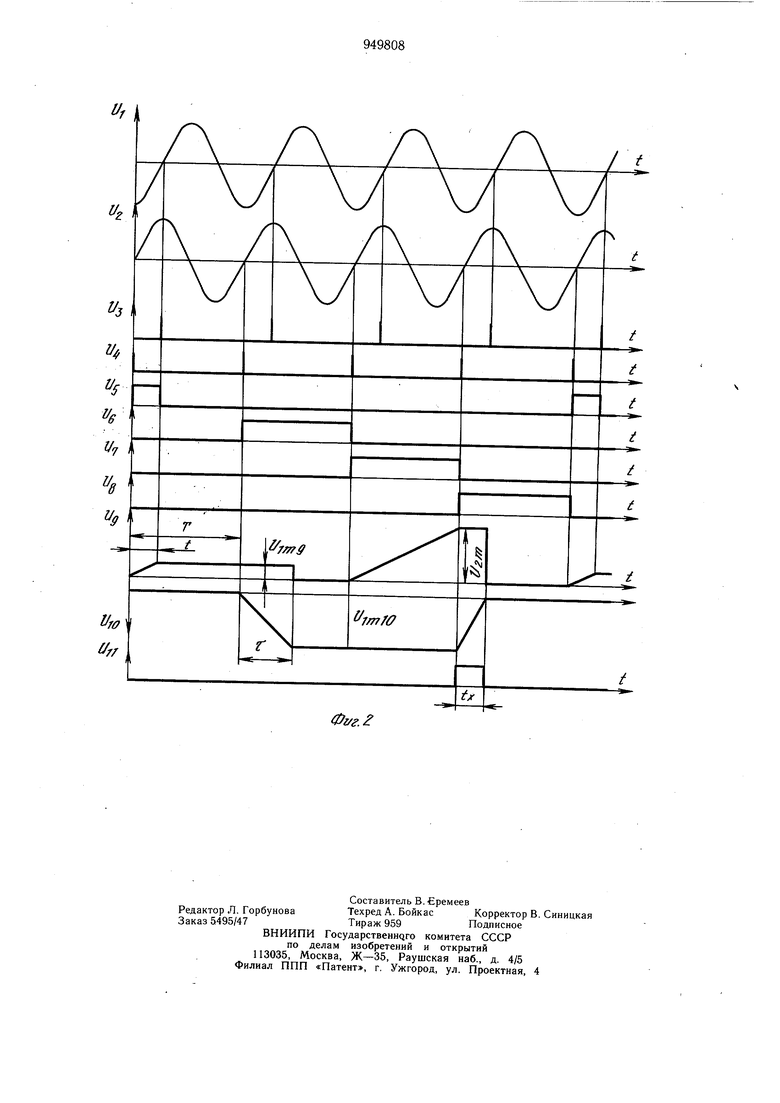

,0 Выход одного из формирователей подключен к первому входу первого триггера, второй вход которого соединен с выходом второго формирователя и счетным входом второго триггера. Выход источника опорного напряжения подключен к потенциальным входам первого и второго ключей, управляющие входы которых соединены соответственно с выходом первого триггера и прямым выходом второго триггера. Инверсный выход второго триггера подключен к входу задатчи20 ка времени. Выход первого ключа через первый интегратор соединен с потенциальным входом третьего ключа, а выход второго ключа через второй интегратор и инвертор - с потенциальным входом четвертого ключа, выход которого соединен с выходом третьего ключа и через третий интегратор и детектор нуля с первым входом третьего триггера. Один из выходов задатчиков времени подключен к -управляющему входу третьего ключа, а второй выход - к управляющему входу четвертого ключа и второму входу третьего триггера 2. Однако данный преобразователь характеризуется недостаточной точностью работы в широком диапазоне дестабилизирующих факторов, обусловленной наличием в информационном и опорных каналах двух независимых интеграторов с разными температурами и временными уходами (по описанию - первый и второй интеграторы). Цель изобретения - повыщение точноети устройства. Для достижения указанной цели в преобразователь сдвига во временной интервал дополнительно введены элемент И, два элемента ИЛИ и распределитель импульсов, вход которого соединен с вторым входом первого триггера, первый выход распределителя импульсов соединен с одним из входов элемента И, другой вход которого подключен к выходу первого триггера, второй выход распределителя импульсов соединен с входом задатчика времени, третий выход распределителя импульсов подключен к одному из входов первого элемента ИЛИ, другой вход которого соединен с выходом элемента И, четвертый выход распределителя импульсов соединен с вторым входом второго триггера, первый вход последнего подключен к одному из входов второго элемента ИЛИ, другой вход которого соединен с вторым выходом задатчика времени, а выход - с управляющим входом четвертого ключа, потенциальный вход которого соединен с входом первого интегратора, а выход последнего подключен к выходу четвертого ключа и входу инвертора, причем выход первого элемента ИЛИ подключен к управляющему входу первого . На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временная диаграмма его работы. . Преобразователь содержит первый и второй формирователи 1 и 2 коротких импульсов, выходы которых соединены с входами первого триггера 3. Выход формирователя 2 подключен к входу распределителя 4 импульсов. Выход триггера 3 и первый выход распределителя 4 соединены с входами элемента И 5, выход которого и третий выход распределителя 4 подключены к входам первого элемента ИЛИ 6. Выход элемента ИЛИ 6 соединен с управляющим входом первого ключа 7, выход которого через последовательно соединенные первый интегратор 8, второй ключ 9, второй интегратор 10 и детектор 11 нуля подключен к первому входу второго триггера 12. Выход интегратора 8 через последовательно соединенные инвертор 13 и третий ключ 14 подключен к входу интегратора 10. Второй вход триггера 12 соединен с управляющим входом ключа 14 и четвертым выходом распределителя 4. Потенциальный вход ключа 7 подключен к выходу источника 15 опорного напряжения. Второй выход распределителя 4 подключен к входу задатчика 16 времени, первый выход которого соединен с управляющим входом ключа 9, а второй выход - с одним из входов второго элемента ИЛИ17, другой вход которого подключен к первому входу триггера 12. Выход элемента ИЛИ 17 соединен с управляющим входом четвертого ключа 18, включенного параллельно интегратору 8. Устройство работает следующим образом. В исходном состоянии на вход формирователя 1 поступает напряжение Ut, а на вход формирователя 2 - напряжение Uz, относительно которого измеряется фазовый сдвиг напряжения Ut. В момент перехода напряжений Ui и Uz через нулевой уровень от отрицательного значения к положительному на выходах формирователей 1 и 2 образуются короткие импульсы, которые, поступая на входы триггера 3, формируют на его выходе временной интервал t, причем ч , где Т - период колебаний напряжений Ui и Uj с фазовым сдвигом ср. Выходные импульсы триггера 3 длительностью t поступают на один из входов элемента И 5, на другой вход которого подается сигнал с первого выхода распределителя 4 импульсов. Распределитель импульсов вырабатывает на своих выходах четыре сдвинутых на время Т (период напряжения Ui) сигнала. По первому периоду напряжения Uz на выходе элемента И 5 появляется сигнал Us длительностью t, который, проходя через элемент ИЛИ 6, открывает ключ 7 и заряжает интегратор 8 от источника 15 до величины Uni,g Т, - постоянная времени интегратора 8. С началом второго периода напряжения Us распределитель 4 вырабатывает сигнал и , запускающий задатчик 16 времени, который открывает ключ 9 на время т. В течение этого времени происходит заряд интегратора 10 до напряжения Um,9 . -и„ .. где t -постоянная времени интегратора 10. По окончании времени задатчик 16 вырабатывает сигнал обнуления интеграто g проходящий через элемент 17 и открывающий ключ 18. В следующий период напряжения Vz (по третьему состоянию распределителя 4) сигнал Ur длительностью Т через элемент ИЛИ 6 открывает ключ 7, заряжая интегратор. 8 до напряжения Um29 on т, По началу четвертого периода напряжения U2 вырабатывается сигнал Us, открывающий ключ 14 и формирующий иа выходе триггера 12 начало временного интервала tx(Uii). Инвертированное напряжение Uni29 через ключ 14 начинает разряжать интегратор 10 до нуля. При этом - Um,io 129 t-T T-tK , откуда t .oя т„rI ™; v s;rг;v;я мент ИЛиТГи ключ 18. На выходе триггеоЛ2 Формируется временной интервал. Изобретени е позволяет повысить точнзооретение шс5ьи,; и Т lOVyWi-V. Д -- ность измерений фазовых сдвигов при длительных непрерывных измерениях за счет исключения из окончательного результата погрешностей, вызванных температурными и временными уходами интегратора. Формула изобретения Преобразователь фазового сдвига ви ь сПреобразователь фазового сдвига во вре::orii rs-itr;i-rU-лл Til ттга ii.-r/MJLIUU Г ПОПратора, инвертор, детектор нуля, два триггера, задатчик времени и два формирователя коротких импульсов, выход одного из которых подключен к первому входу первого триггера, второй вход которого соединен с выходом второго формирователя коротких импульсов, выход источника опорного напряжения подключен к потенциальному входу первого ключа, выход последнего через

f/f

f

4ZW. / первый интегратор соединен с потенциальным входом второго ключа, выходы Biopoj го и третьего ключей соединены через второй интегратор и детектор нуля с первым входом второго триггера, а потенциальный вход третьего ключа подключен к выходу инвертора, первый выход задатчика времени соединен с управляющим входом второго ключа, а управляющий вход третьего ключа - с вторым входом второго триггера, отличающийся тем, что, с целью повыщения точности, в него введены элемент И, два элемента ИЛИ и распределитель импульсов, вход которого соединен с вторым входом первого триггера, первый выход распределителя импульсов соединен с одним из .Гя/й рг:™™ „ -ГГ/д Г™ ре Т™Т распределителя импульсов подключен к одному из входов первого элемента ИЛИ, другой вход которого соединен с выходом элемента И, четвертый выход распределителя импульсов соединен с вторым входом второго триггера, первый вход последнего подключен к одному из входов второго элемента ИЛИ, другой вход которого соединен с вторым выходом задатчика времени, а выход - с управляющим входом четвертого ключа, потенциальный вход которого соединен с входом первого интегратора, а выход последнего подключен к выходу четвертого г равляющему входу первого ключа. Источники информации, принятые во внимание пр;-; экспертизе 1Авторское свидетельство СССР № 678666, кл. Н 03 К 13/20, 1977. 2Авторское свидетельство СССР № 783704, кл. Н 03 К 13/20, 1978 (прототип) .

и,

Г ,

LL

и

3

и

% 6

щ в

I/O

f t t

i

/ i

Vro

r

//

7m/ff

Фг/г.

Авторы

Даты

1982-08-07—Публикация

1979-12-27—Подача