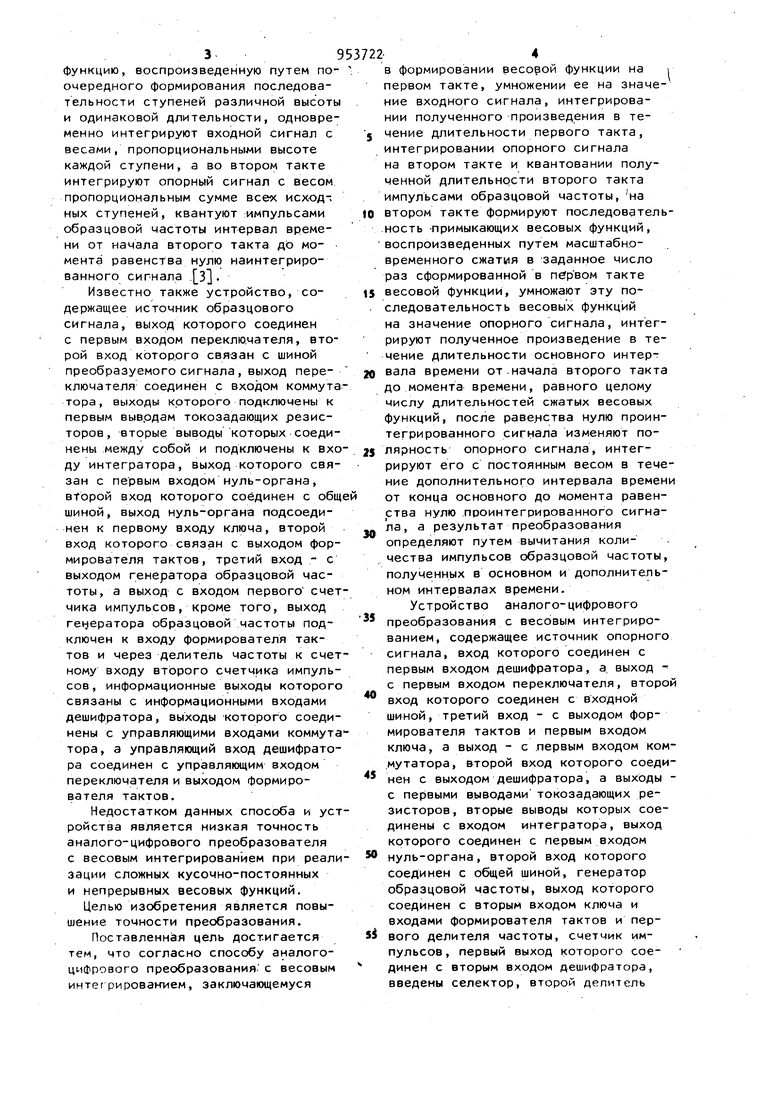

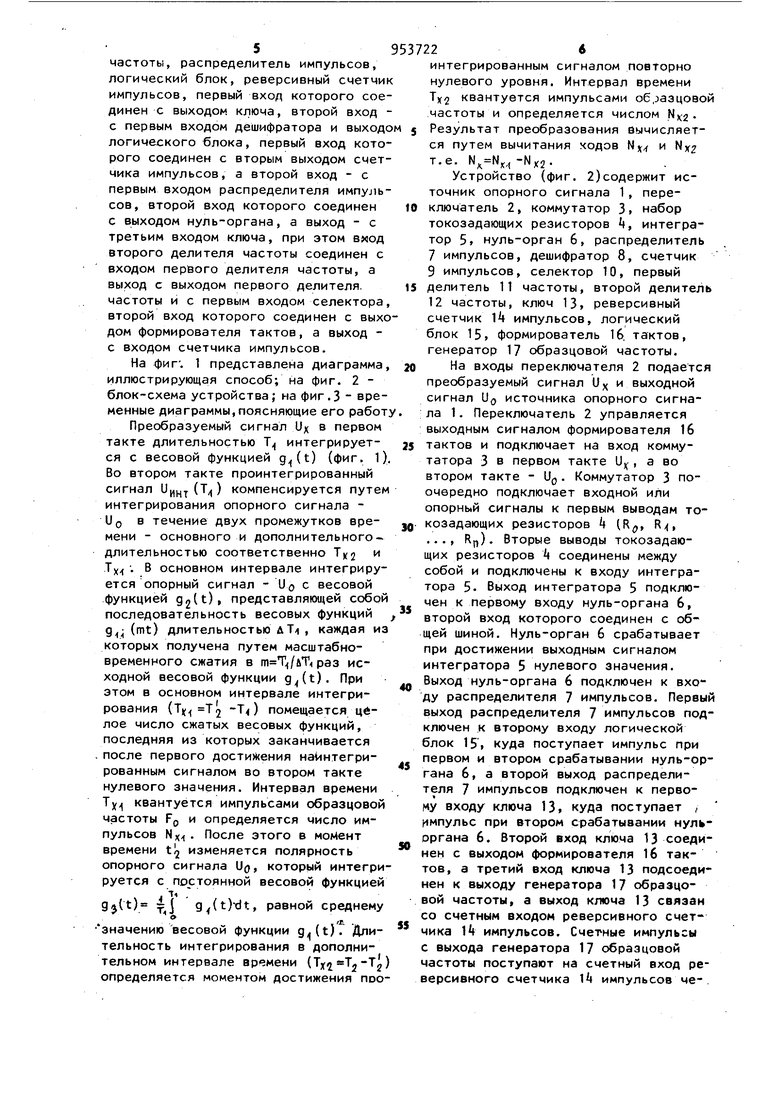

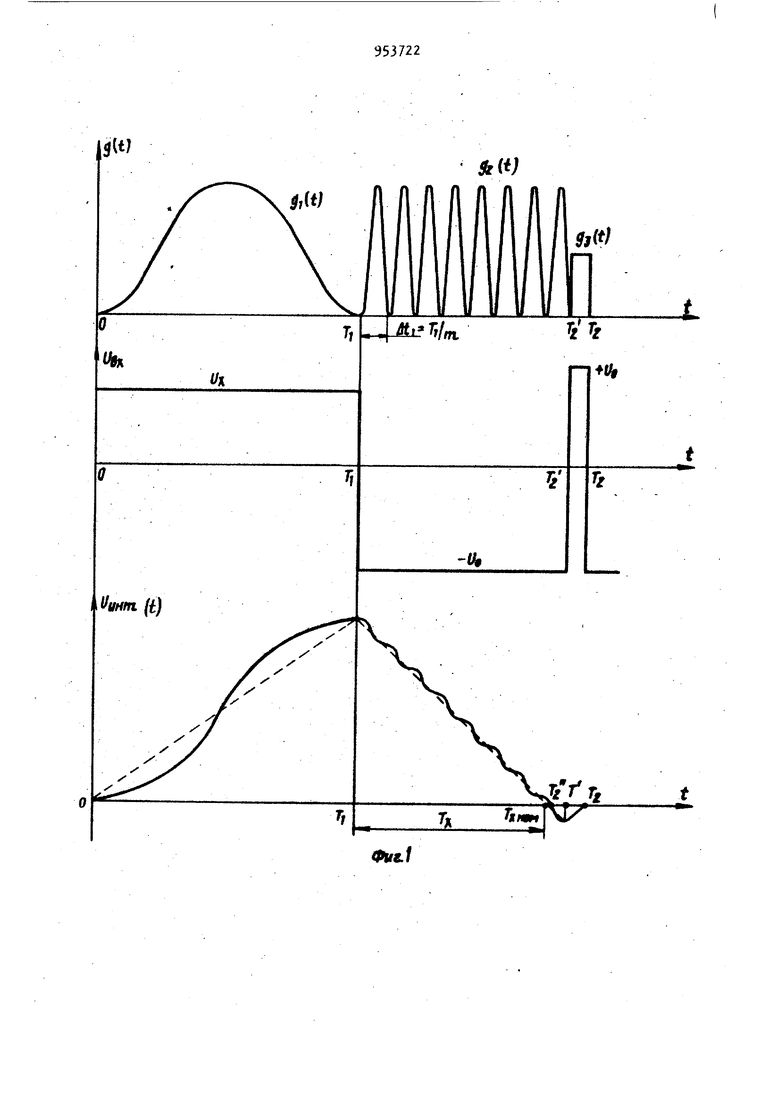

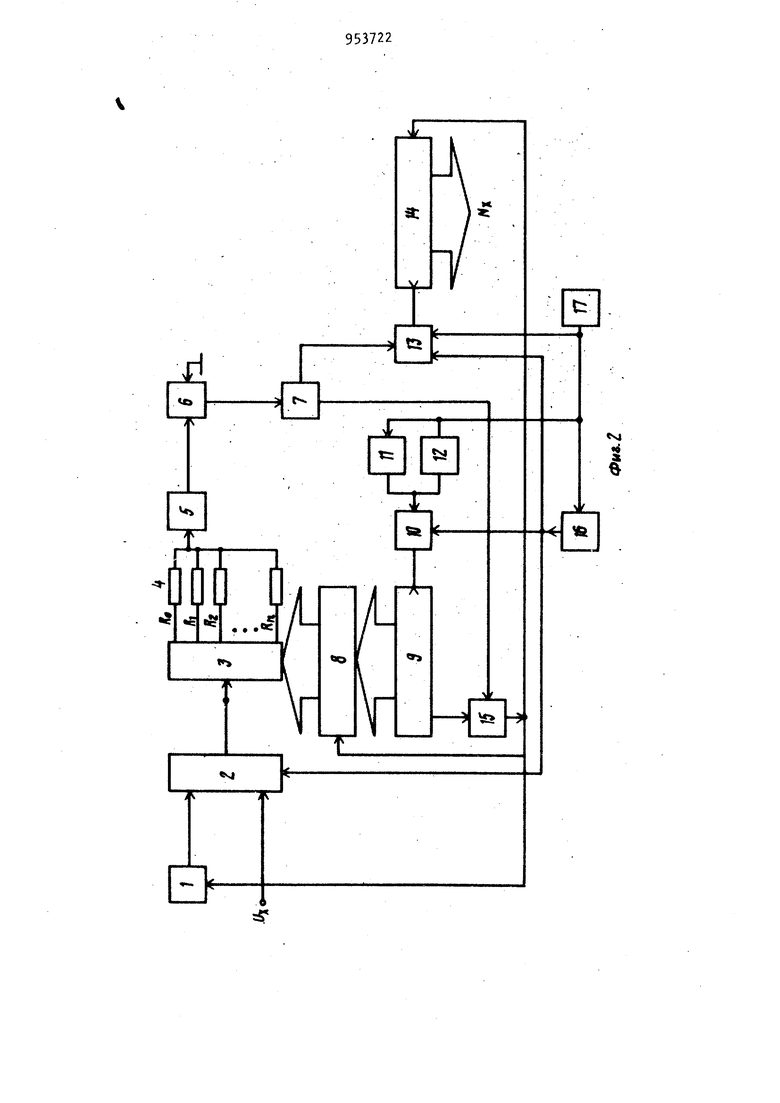

функцию, воспроизведенную путем поочередного формирования последова тельности ступеней различной высоты и одинаковой длительности, одновременно интегрируют входной сигнал с весами, пропорциональными высоте каждой ступени, а во втором такте интегрируют опорный сигнал с весом пропорциональным сумме исход-, ных ступеней, квантуют ;импульсами образцовой частоты интервал времени от начала второго такта до момента равенства нулю наинтегрированного сигнала .З. Известно также устройство, содержащее источник образцового сигнала, выход которого соединен с первым входом переклю.чателя, второй вход котор.ого связан с шиной преобразуемого сигнала , выход переключателя соединен с входом коммута тора, выходы которого подключены к первым выводам токозадаю.щих резисторов, вторые выводы которых соединены между собой и подключены к вхо ду интегратора, выход которого связан с первым входом нуль-органа, второй вход которого соединен с общ шиной, выход нуль-органа подсоединен к первому входу ключа, второй вход которого связан с выходом формирователя тактов, третий вход - с выходом генератора образцовой частоты, а выход с входом первого счет чика импульсов, кроме того, выход генератора образцовой частоты подключен к входу формирователя тактов и через делитель частоты к счет ному входу второго счетчика импульсов, информационные выходы которого связаны с информационными входами дешифратора, выходы которого соединены с управляющими входами коммута тора, а управляющий вход дешифратора соединен с управляющим входом переключателя и выходом формирователя тактов. Недостатком данных способа и уст ройства является низкая точность аналого-цифрового преобразователя с весовым интегрированием при реали зации сложных кусочно-постоянных и непрерывных весовых функций. Целью изобретения является повышение точности преобразования. Поставленная цель достигается тем, что согласно способу аналогоцифрового преобразования с весовым интегрированием, заключающемуся В формировании весовой функции на первом такте, умножении ее на значение входного сигнала, интегрировании полученного произведения в течение длительности первого такта, интегриров.ании опорного сигнала на втором такте и квантовании полученной длительности второго такта импульсами образцовой частоты, на втором такте формируют последовательность Примыкающих весовых функций, воспроизведенных путем масштабновременного сжатия в заданное число раз сформированной в первом такте весовой функции, умножают эту последовательность весовых функций на значение опорного сигнала, интегрируют полученное произведение в течение длительности основного интерт вала времени от.начала второго такта до момента времени, равного целому числу длительностей сжатых весовых функций, после раве.нства нулю проинтегрированного сигнала изменяют полярность опорного сигнала, интегрируют его с постоянным весом в течение дополнительного интервала времени от конца основного до момента равенства нулю .проинтегрированного сигнала, а результат преобразования определяют путем вычитания количества импульсов образцовой частоты, полученных в основном и дополнительном интервалах времени. Устройство аналого-цифрового преобразования с весовым интегрированием, содержащее источник опорного сигнала, вход которого соединен с первым входом дешифратора, а, выход с первым входом переключателя, второй вход которого соединен с входной шиной, третий вход - с выходом формирователя тактов и первым входом ключа, а выход - с .первым входом коммутатора, второй вход которого соединен с выходом дешифратора, а выходы с первыми выводами токозадающих резисторов, вторые выводы которых соединены с входом интегратора, выход которого соединен с первым входом нуль-органа, второй вход которого соединен с общей шиной, генератор образцовой частоты, выход которого соединен с вторым входом ключа и входами формирователя тактов и первого делителя частоты, счетчик импульсов , первый выход которого соединен с вторым входом дешифратора, введены селектор, второй делитель частоты, распределитель импульсов, логический блок, реверсивный счетчик импульсов, первый вход которого соединен с выходом ключа, второй вход с первым входом дешифратора и выходо логического €лока, первый вход которого соединен с вторым выходом счетчика импульсов, а второй вход - с первым входом распределителя импульсов, второй вход которого соединен с выходом нуль-органа, а выход - с третьим входом ключа, при этом вход второго делителя частоты соединен с входом первого делителя частоты, а выход с выходом первого делителя. частоты и с первым входом селектора второй вход которого соединен с выхо дом формирователя тактов, а выход с входом счетчика импульсов. На фиг , 1 представлена диаграмма иллюстрирующая способ; на фиг. 2 блок-схема устройства; на фиг.З временные диаграммы,поясняющие его работ Преобразуемый сигнал Ux в первом такте длительностью Т интегрируется с весовой функцией g(t) (фиг. 1) Во втором такте проинтегрированный сигнал (Т) компенсируется путем интегрирования опорного сигнала 11(5 в течение двух промежутков времени - основного и дополнительногодлительностью соответственно TXJ и В основном интервале интегрируется опорный сигнал - UQ с весовой функцией g2(t), представляющей собой последовательность весовых функций д (mt) длительностью дТ, каждая из которых получена путем масштабновременного сжатия в (/uT раз исходной весовой функции g(t). При этом в основном интервале интегрирования ( -Т) помещается цблое число сжатых весовых функций, последняя из которых заканчивается после первого достижения найнтегрированным сигналом во втором такте нулевого значения. Интервал времени Ту квантуется импульсами образцовой частоты FO и определяется число импульсов NX.( . После этого в момент времени t/j изменяется полярность опорного сигнала DO, который интегри руется с постоянной весовой функцией gj(t) :pj )-dt, равной среднему значению весовой функции g(t). Длительность интегрирования в дополнительном интервале времени (Т; определяется моментом достижения поо интегрированным сигналом повторно нулевого уровня. Интеррал времени Т)(2 квантуется импульсами о6,;азцовой частоты и определяется числом . Результат преобразования вычисляется путем вычитания кодов Мц и NX т.е. ,,,. Устройство (фиг. 2)содержит источник опорного сигнала 1, переключатель 2, коммутатор 3f набор токозадающих резисторов t, интегратор 5. нуль-орган 6, распределитель 7 импульсов, дешифратор 8, счетчик 9 импульсов, селектор 10, первый делитель 11 частоты, второй делитель 12 частоты, ключ 13, реверсивный счетчик 14 импульсов, логический блок 15, формирователь 16. тактов, генератор 17 образцовой частоты. На входы переключателя 2 подается преобразуемый сигнал Ux и выходной сигнал U(j источника опорного сигнала 1. Переключатель 2 управляется выходным сигналом формирователя 16 тактов и подключает на вход коммутатора 3 в первом такте U,, а во втором такте - UQ. Коммутатор 3 поочередно подключает входной или опорный сигналы к первым выводам токозадающих резисторов 4 (R, R, ..., Rf)). Вторые выводы токозадающих резисторов k соединены между собой и подключены к входу интегратора 5. Выход интегратора 5 подключен к первому входу нуль-органа 6, второй вход которого соединен с общей шиной. Нуль-орган 6 срабатывает при достижении выходным сигналом интегратора 5 нулевого значения. Выход нуль-органа 6 подключен к входу распределителя 7 импульсов. Первый выход распределителя 7 импульсов подключен к второму входу логической блок 15, куда поступает импульс при первом и втором срабатывании нуль-органа 6, а второй выход распределителя 7 импульсов подключен к первоi y входу ключа 13, куда поступает , импульс при втором срабатывании нуль органа 6. Второй вход ключа 13 соединен с выходом формирователя 1б тактов, а третий вход ключа 13 подсоединен к выходу генератора 17 образцовой частоты, а выход ключа 13 связан со счетным входом реверсивного счетчика 1 импульсов. Счетные импульсы с выхода генератора 17 образцовой частоты поступают на счетный вход реверсивного счетчика 14 импульсов через.ключ 13 в течение интервала времени, начало, которого определяется

.импульсом формирователя 1б тактов, а конец - вторым срабатыванием нульоргана 6. Выход генератора 17 образцовой частоты подключен также к входу формирователя 16 тактов и к входа первого 11 и второго 12 делителей частоты. Выходы делителей частоты . 11 и 12 подключены ;К входам селектора 10, управляющий вход которого подключен к выходу формирователя 16

.тактрв. Выход селектора 10 подключен :к счетному входу счетчика 9 импульсов, информационные выходы которого подключены к входам дешифратора 8, который управляет своими выходами работой коммутатора 2. В зависимости от того, какой делитель 11 или 12 частоты включен, изменяется скорость форйирования весовых функций. Выход переполнения счетчика импульсов 9 соединен с первым входом логического блока 15, сигнал на выходе которого появляется после первого срабатывания нуль-органа 6 и очередного переполнения счетчика 9 импульсов. Выход логического блока 15 подключен к управляющим входам источника опорного сигнала 1, дешифраторэ 8 и реверсивного счетчика 1 импульсов. При этом на выходе источника опорного сигнала 1 изменяется полярность сигнала, реверсивный счетчик импульсов 1 переводится в риежим вычитания, а дешифратор 8 формирует сигнал на подключение коммутатором 3 к входу интегратора 5 токрзадающего резистора RQ. В .исходное состояние логический блок 15 приводится импульсом второго срабатывания нуль-органа.

Устройство работает следующим образом.

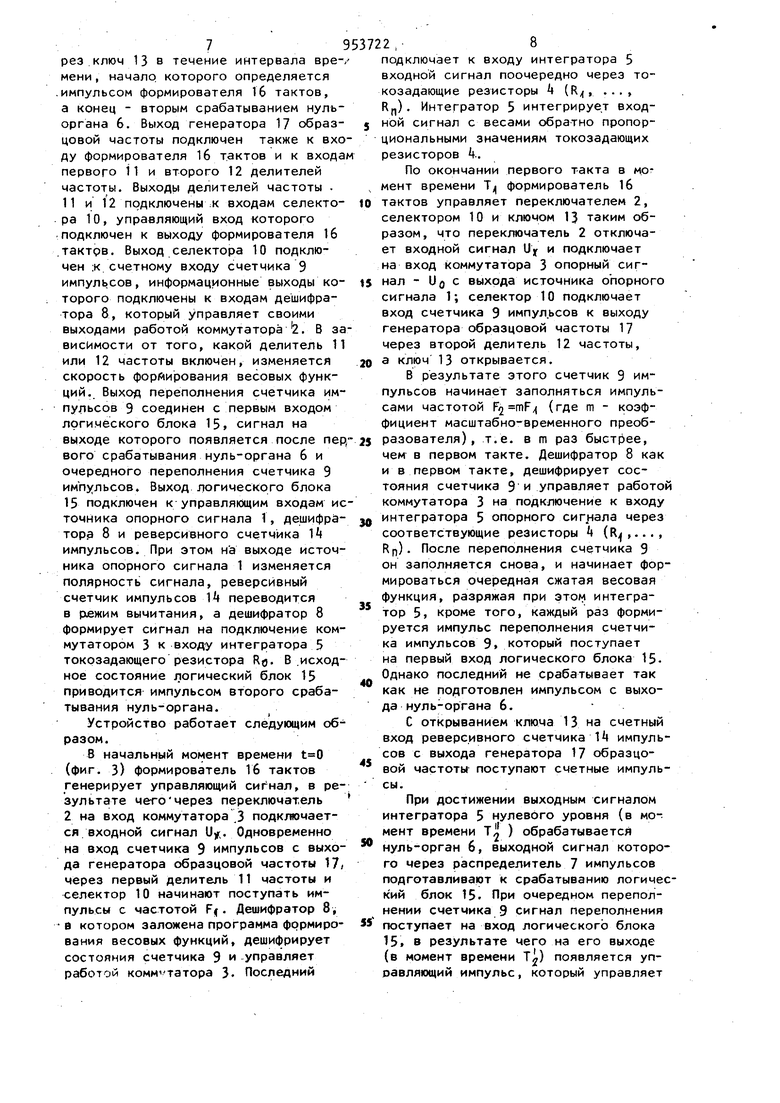

В начальный момент времени (фиг. 3) формирователь 16 тактов генерирует управляющий сигнал, в результате чегочерез переключатель 2 на вход коммутатора 3 подключается входной сигнал . Одновременно на вход счетчика 9 импульсов с выхода генератора образцовой частоты 17/ через первый делитель 11 частоты и селектор 10 начинают поступать импульсы с частотой Ff. Дешифратор 8,

а котором заложена программа формирования весовых функций, дешифрирует состояния счетчика 9 и управляет работой коммутатора 3. Последний

подключает к входу интегратора 5 входной сигнал поочередно через токозадающие резисторы t (R,(,

). Интегратор 5 интегрирует входR/ной сигнал с весами обратно пропорциональными значениям токозадающих резисторов t-.

По окончании первого такта в момент времени Т формирователь 16 тактов управляет переключателем 2, селектором 10 и ключом 13 таким образом, что переключатель 2 отключает входной сигнал Uy и подключает на вход коммутатора 3 опорный сигнал - DO с выхода источника опорного сигнала 1; селектор 10 подключает вход счетчика 9 импул.ьсов к выходу генератора образцовой частоты 17 через второй делитель 12 частоты,

0 а ключ 13 открывается.

В результате этого счетчик 9 импульсов начинает заполняться импульсами частотой (где m - коэффициент масштабно-временного преобразователя), т.е. в m раз быстрее, чем в первом такте. Дешифратор 8 как и в первом такте, дешифрирует состояния счетчика 9 и управляет работой коммутатора 3 на подключение к входу

интегратора 5 опорного сиг.нала через соответствующие резисторы (R,..., Rp). После переполнения счетчика 9 он заполняется снова, и начинает формироваться очередная сжатая весовая функция, разряжая при этом интегратор 5, кроме того, каждый раз формируется импульс переполнения счетчика импульсов 9 который поступает на первый вход логического блока 15Однако последний не срабатывает так как не подготовлен импульсом с выхода нуль-органа 6.

С открыванием ключа 13 на счетный вход реверсивного счетчика 1 импульсов с выхода генератора 17 образцовой частоты поступают счетные импульсы.

При достижении выходным сигналом интегратора 5 нулевого уровня (в момент времени TJ| ) обрабатывается нуль-орган 6, выходной сигнал которого через распределитель 7 импульсов подготавливают к срабатыванию логический блок 15. При очередном переполнении счетчика 9 сигнал переполнения

поступает на вход логического блока 15i в результате чего на его выходе (в момент времени Тр появляется управляющий импульс, который управляет источником опорного сигнала, дешифра тором 8 и реверсивным счетчиком Tt и пульсов. Вследствие этого изменяется полярность опорного сигнала, дешифратор 8 управляет коммутатором 3 таким образом, что опорный сигнал подключается на вход интегратора 5 через резистор .Г 1/R, а реверсивный счетчик 14 наминает работ. тать в режиме вычитания, в котором к .этому моменту накопилось число Nxf Начиная с момента времени Рл , ин . тегратор 5 начинает перезаряжаться. При достижении выходным сигналом интегратора 5 во второй раз нулевого уровня (в момент времени Tj) срабатывает нуль-орган 6, выходной сигнал которого через распределитель импуль сов 7 закрывает ключ 13 и отключает логический блок 15В течение интервала времени Т2-Т2 в реверсивный счетчик импульсов И прошло на вычитание N импульсов, в результате чего состояние счетчика Т равно N4. которое пропорционально пресэбразуемому сигналу. На этом заканчивается второй такт работы устройства. При очередном срабатывании формирователя 16 тактов устройство продолжает работать в той же последовательности как описано. Способ и устройство обеспечивают повышение точности аналого-цифрового преобразования при реализации как континуальных, так и многоступенчатых весовых функций за счет выбора коэффициента масштабно-временного преобразования. ( В первом такте интегрирования дли тельностью формируется весовая функция g(t), и выходной сигнал интегратора 5 к моменту Т равен т , u«Ht(T,bJ u4,(tMuu J ,{im ,),, о - о J. т гдeG|ДT,) J6,t)dt - площадь ве7 . о совой функции g(t) . Во втором такте интегрирования : 1}юрмируется последовательность весовых функций вида д}(t)g(m«t), и к моменту времени Т. Т выходной сигнал интегратора равен т.(и)Й ,,,(Т,).1. ( « (, где К j- целое число сжатых весовых функций, которые поместились в интервал времени Tjj -Т , или путем замены переменных t-T -ill t/ .. % :. ииит1 5 нт1г-,)-, ,адт,). к моменту времени Тл , когда закончилось интегрирование опорного сигнала DO с весовой функцией g,{t)« %, лмм T ), где G4 ном СТ) - номинальная площадь весовой функции g|(t), выходной сигнал интегратора равен нулю ,|ь. )-UHHtCn;)ju,ai. Тз А1т,,оЛт,),Оном(г)-о, е. II Ji ,, - Ч т, олт. I Если действительная весовая функция gAt) отклоняется от номинальной 9/1 ° возникает погрешность ,(T).-Gnew (Т-и), и тогда :.ч- --01-м ,4ном-Л) или . Таким образом, разность интервалов времени {Tj-T2)-{Tj-Tj)Тх, а значит и разность кодов Nx -Nxji соответствующих этим интервалам, пропорциональны преобразуемому сигналу U, 11. но при этом преобразование осуществляется с погрешностью 8jt fixTIT --% обусловленной отклонением G.(Jj ) от G - Ьыбрав необходимое значение коэффици ента с масштабно-.временного прробразования m в заданное число раз умень шается погрешность из-.за неточности формирования весовой функции, не ухудшая при этом другие параметры преобразования. Формула изобретения 1. Способ аналого-цифрового преоб разования с весовым интегрированием заключающийся в формировании весовой функции на первом такте, умножении ее на значение входного сигнала, интегрировании полученного произведения в течение длительности первого такта, интегрировании опорного сигнала на втором такте и квантовании полученной длительности второго такта импульсами образцовой частоты, отличающийся тем, что, с целью повышения точности преобразования, на втором такте формируют последовательность примыкающих весовых функций, воспроизведенных путем масштабно-временного сжатия в заданное число раз сформированной на первом такте весовой функции, умножает эту последовательность весовых функций на значение опорного сигнала, интегрируют полученное произведение в течение основного интервала времени от начала второго такта до момента времени, равного Целому числу длительностей сжатых весовых функций, после равенства нулю проинтегрированного сигнала изменяют полярность опорного сигнала, интегри руют его с постоянным весом в течение дополнительного интервала времени от конца основного до момента равенства нулю проинтегрированного сигнала, а результат преобразования определяют путем вычитания количест ва импульсов образцовой частоты, полученных в основном и дополнительном интервалах времени. 2 2. Устройство аналого-цифрового преобразования с весовым интегрированием, содержащее источник опорного сигнала, вход которого соединен с первым входом дешифратора, а выход с первым входом переключателя, второй вход которого соединен с входной шиной, третий вход -с выходом формирователя тактов и первым входом ключа, а выход - с первым входом коммутатора, второй вход которого соединен с выходом дешифратора, а выход - с первыми выводами токозадающих резисторов, вторые выводы которых соединены с входом интегратора, выход которого соединен с первым входом нуль-органа, второй вход которого соединен с общей шиной, генератор образцовой частоты, выход которого соединен с вторым входом ключа и входами формирователя тактов и первого делителя частоты, счетчик импульсов, первый выход которого соединен с вторым входом дешифратора, отличающееся тем, что, с целью повышения точности преобразования, в него введены селектор, второй делитель частоты, распределитель импульсов, логический блок, реверсивный счетчик импульсов, первый вход которого соединен с выходом ключа, второй вход - с первым входом дешифратора и выходом логического блока, первый вход которого соединен с вторым выходом счетчика импульсов, а второй вход - с первым входом распределителя импульсов, второй вход которого соединен с выходом нуль-органа, а выход - с третьим входом ключа, при этом вход второго делителя частоты соединен с входом первого делителя частоты, а выход с выходом первого делителя частоты и с первым входом селектора, второй вход которого соединен с выходом формирователя тактов, а выход - с входом счетчика импульсов., Источники информации, принятые во внимание при экспертизе 1. Измерение контроля автоматизации, 1980, № 3-, с. 17-22. : 2. Приборы и системы управления 1979, N 2, с. 20-22. 3. Тезисы докладов областного семинара. Пенза, ПДНТП, , с. 5253 (прототип).

u;

5fc(;

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой вольтметр | 1985 |

|

SU1273825A1 |

| Цифровой измеритель параметров | 1977 |

|

SU702317A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Устройство для измерения температуры | 1987 |

|

SU1490504A1 |

| Цифровой измеритель -параметров | 1978 |

|

SU788036A1 |

| Интегрирующий аналого-цифровой преобразователь | 1987 |

|

SU1495996A2 |

| Устройство для измерения веса | 1984 |

|

SU1244496A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДЫ ГАРМОНИЧЕСКОГО НАПРЯЖЕНИЯ | 1991 |

|

RU2032182C1 |

| Цифровой измеритель температуры | 1985 |

|

SU1303849A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1560987A1 |

анп (i)

Авторы

Даты

1982-08-23—Публикация

1981-01-04—Подача