Изобретение относится к электроизмерительной технике, может быть использовано при проектировании поме- хозащищенных приборов и измерительных информационных систем и является усовершенствованием устройства по авт. св. № 782152.

Цель изобретения - повышение помехозащищенности за счет подавления второй и третьей гармоник сигнала помехи.

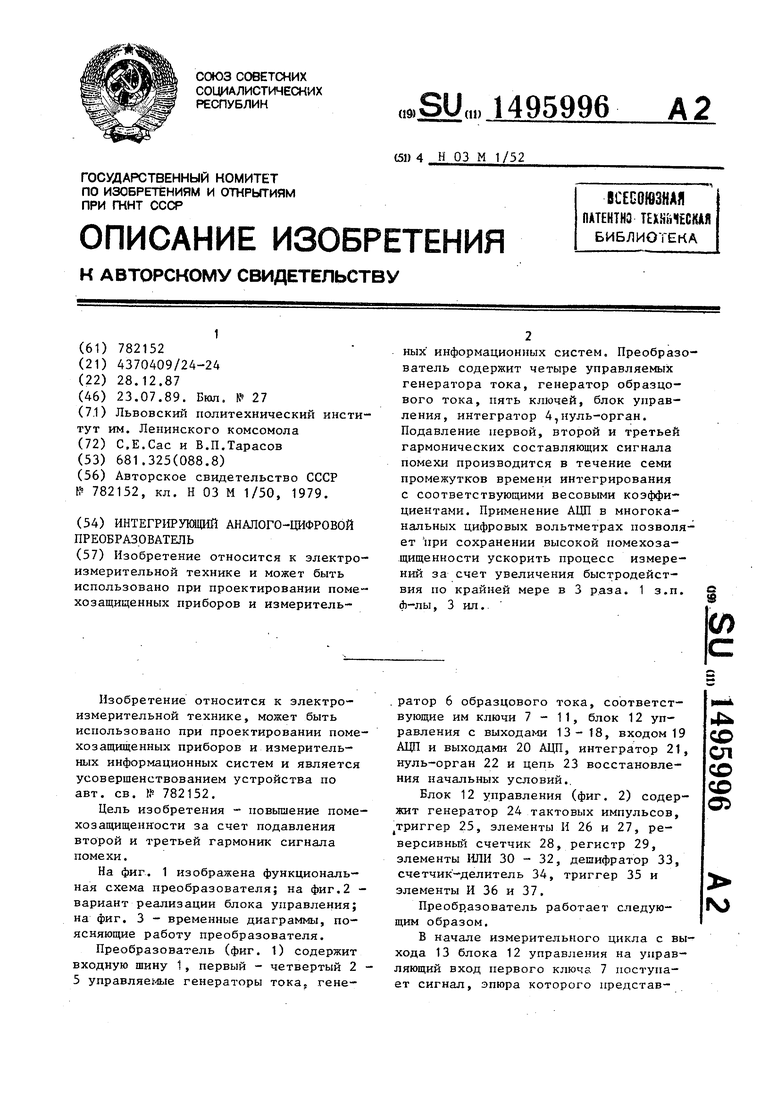

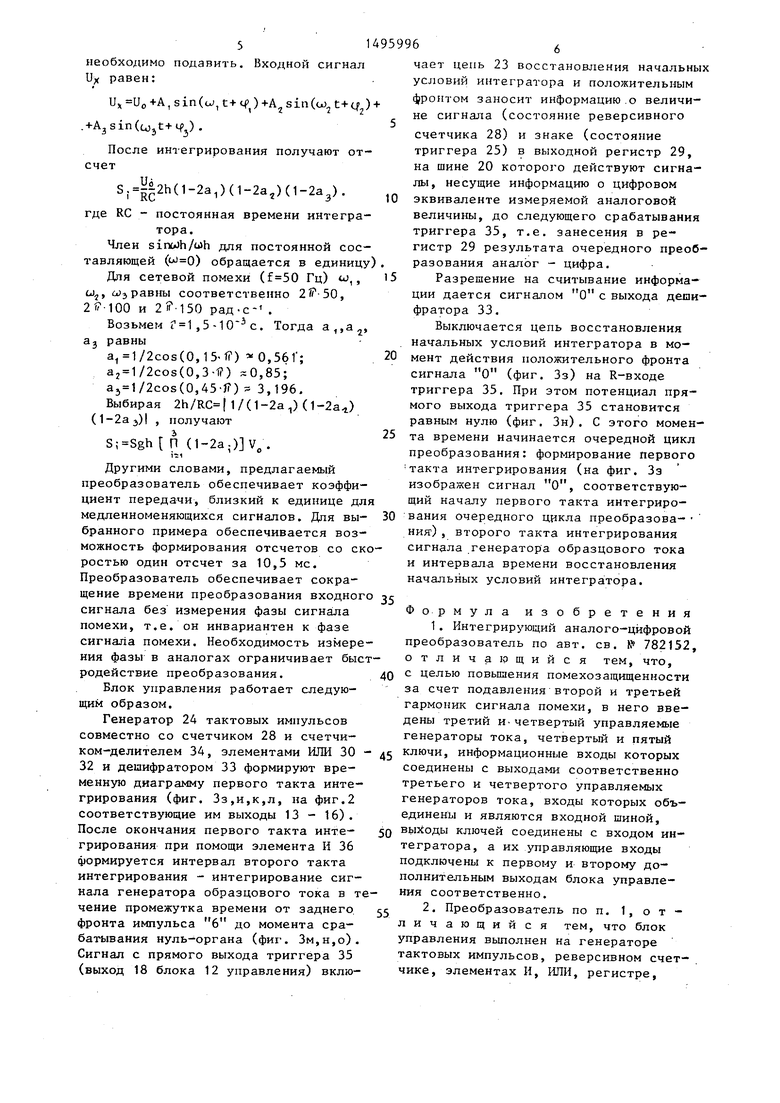

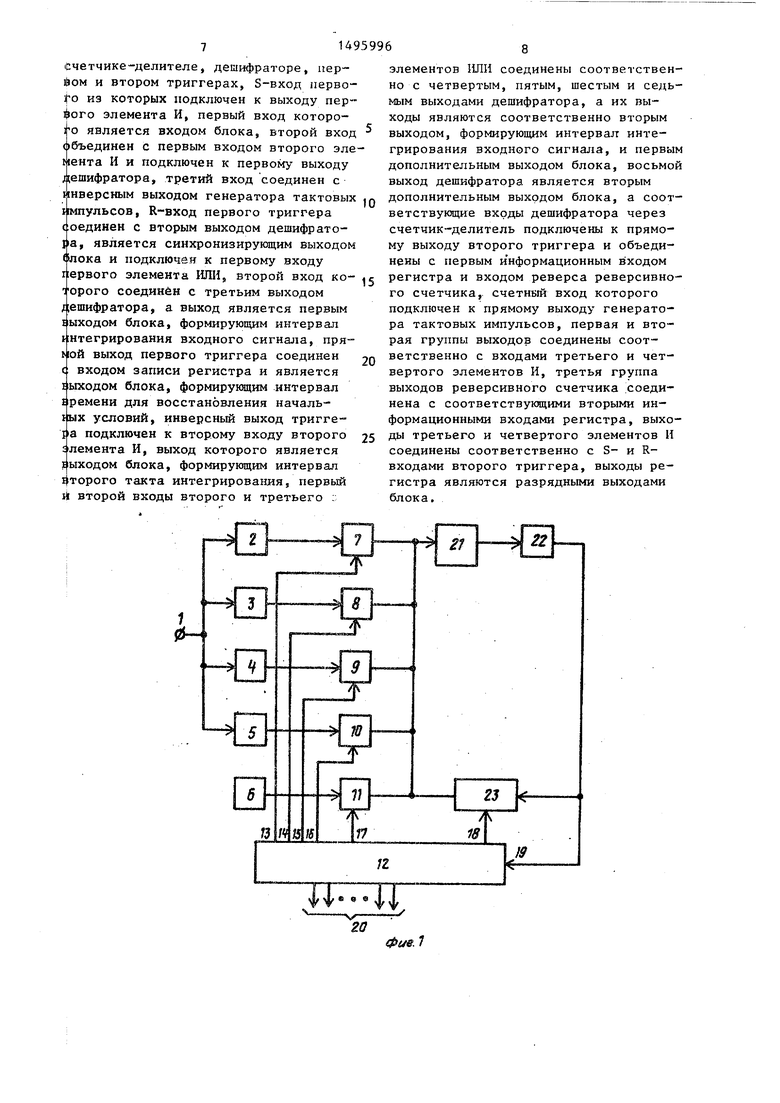

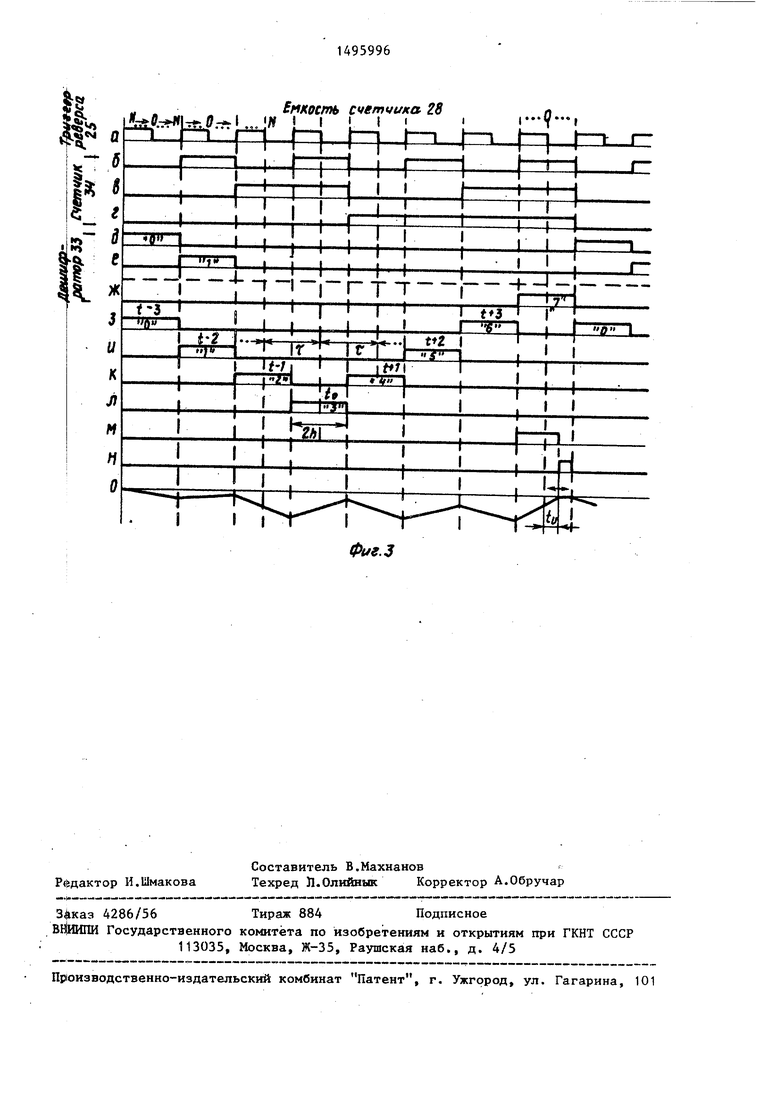

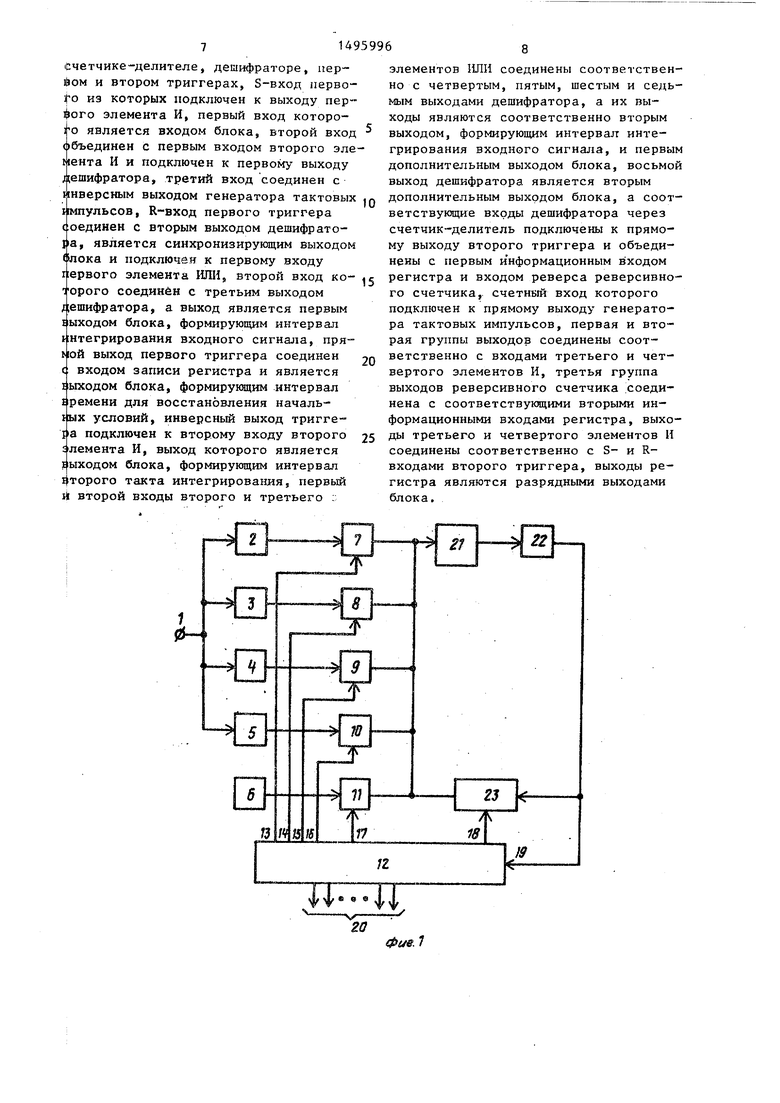

На фиг. 1 изображена функциональная схема преобразователя; на фиг.2 - вариант реализации блока управления; на фиг. 3 - временные диаграммы, поясняющие работу преобразователя.

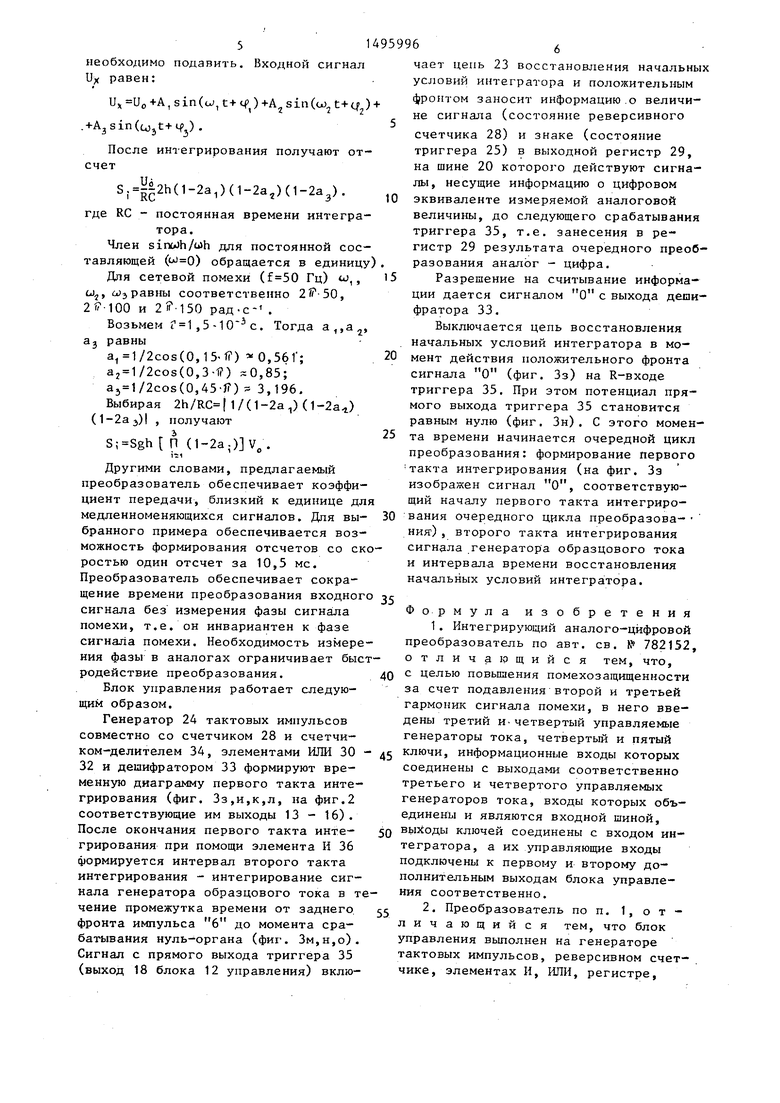

Преобразователь (фиг. 1) содержит входную шину 1, первый - четвертый 2 - 5 управляе1Л,1е генераторы тока, генератор 6 образцового тока, соответствующие им ключи 7-11, блок 12 управления с выходами 13- 18, входом 19 АЦП и выходами 20 АЦП, интегратор 21, нуль-орган 22 и цепь 23 восстановления начальных условий..

Блок 12 управления (фиг. 2) содержит генератор 24 тактовых импульсов, триггер 25, элементы И 26 и 27, реверсивный счетчик 28, регистр 29, элементы ИЛИ 30 - 32, дешифратор 33, счетчик -делитель 34, триггер 35 и элементы И 36 и 37.

Преобразователь работает следующим образом.

В начале измерительного цикла с выхода 13 блока 12 управления на управляющий вход первого ключа 7 поступает сигнал, эпюра которого представ4 СО СП

СО

со

05

го

:,1495996

J-ч

лена на фиг. Зз (импульсы О и 6). Получают

При этом на время действия положительных импульсов О и 6 на управляющем входе ключа 7 подключается выход первого управляемого генератора 2 тока на вход интегратора 21, который интегрирует входной сигнал в тчение промежутков времени О и 6 (t-3, t+3) с весом К -aj-а ,

Аналогичным образом с помощью ключей 8 - 10 и управляемых генераторов 3 5 тока на интервалах времени 1 и 5 (t-2, t+2) осуществляется интегрирование с весом j+a а ) на интервалах времени 2 и 4 (t-1 , t-bl) - с весом К ( +3а,), на интервале времени 3 (to). - с весом (

К моменту окончания седьмого ин- тервала парциального интегрирования 6 (t+3) на выходе интегратора значение сформированного сигнала пропорционально среднему значению входного сигнала за полное время интегрирова- НИН, из которого исключены гармонические составляющие сигнала с частотами со, , u),j,, причем коэффициенты а,, а,, 3 интервал времени t (фиг. Зи).связаны соотношением

Tcos

По управляющему сигналу, действующему на выходе 17 узла 12, ключ 11 подключает образцовый генератор 6 тока на вход интегратора 21. Момент перехода выходного сигнала интегратора через нуль (фиг. Зо) в интервале времени 7 (фиг. Зж) фиксируется нуль-органом 22, по сигналу которого включается цепь 23 восстановления начальных условий интегратора и снимается отсчет, пропорциональный интервалу времени t (фиг. Зо).

Покажем, что в снятом отсчете от-

сутствуют составляющие трех гармоник

сигнала помехи.

При интегрировании гармонического сигнала частоты u)j по интервалу 2h

с центром t д- с имеют

1о--г-ь

I(to- ,h) 5 sin(w t+M i)dt

to-C-Ь

2hSi2 i- sin(uj,t, + tfj) cos w.-r -COS(w; t4-4 )sin Wf «J .

вычисляют cyMNry .,I(,h)+I(t,h)-a,-l().

S,2hSiffl sin(.,t..c,1- -2a;cosw; tj .

Полагая a- 1/2co.siVj , имеют . Параметр D принципиально может быть выбран сколь угодно малым. Применяя эту процедуру к отсчетам сигнала, который содержит компоненту частотой cij,- , получают новый ряд преобразованных отсчетов, в которых отсутствует составляющая частоты ы. .

Применяя к новому ряду отсчетов такую же процедуру со значением коэффициента а ., получают следующий набор отсчетов, в которых отсутствует составляющая частоты cOj.

Аналогично можно подавить и другие гармонические составляющие сигнала помехи.

Для трех гармоник о , ы и uj получают следующую систему уравнений для вычисления из исходного

ряда отсчетов

ы

последующих преп 12) , (3) Ь ; , о )

образованных S v , i- ; ,

где S ( - отсчеты, в которых подавлена составляющая частоты w,; S - отсчеты с подавленными составляющими частоты W, и U), ; S - отсчеты с подавленными составляющими частоты и;„ Wj , О),:

S; -а, S(,.5 Si iSj, ;

-а -а ; - -г)- i 3,jb j., ,

q(l) . я с(2

ь, - . +ь i j .

После вычислений получают:

,,.з -(,а .,+ ,,)S f(,)S. + +l.+2(,a,)(.,+ ,,)S +(a, j)S j,-a . .

Из последнего равенства следует: если провести семь последовательных парциальных интегрирований с параметрами 2h и полученные результаты просуммировать с весами, выраженными через а, а и а, то результирующий отсчет S. , не содержит первой, второй и третьей гармоник сигнала помехи.

. Пример. Измеряемый сигнал равен сумме постоянной составляющей U(js подлежащей измерению, и гармонической помехи, три гармоники которой

необходимо подавить. Входной сигнал DX равен:

и Uo+А, S in(cj, t+tf)+А. Sin(ы.; t-f tfp .+A3sin(tOjt+4 ),

После интегрирования получают отсчет

Uo

S.2h(1-2ai)(1-2a,)(1-2ap.

где RC - постоянная времени интегратора.

Член sinuJh/uh для постоянной составляющей () обращается в единицу

Для сетевой помехи ( Гц) uj,, ы, шз равны соответственно , и 2й -150 рад-с- .

Возьмем ,5-10 с. Тогда а,а, aj равны

a 1/2cos(0,15-ff) «0,561 ;

aj 1/2cos(0,3-1) 0,85;

аэ 1/2соБ(0,45-Я) 3,196.

Выбирая 2h/RC |1/(1-2а,)(1-2а) (1-2аз)1 , получают

П (1-2а;)У„.

i-ii

Другими словами, предлагаемый преобразователь обеспечивает коэффициент передачи, близкий к единице дл медленноменяющихся сигналов. Для вы- бранного примера обеспечивается возможность фор1-1ирования отсчетов со скростью один отсчет за 10,5 мс. Преобразователь обеспечивает сокращение времени преобразования входног сигнала без измерения фазы сигнала помехи, т.е. он инвариантен к фазе сигнала помехи. Необходимость измерения фазы в аналогах ограничивает бысродействие преобразования.

Блок управления работает следующим образом.

Генератор 24 тактовых импульсов совместно со счетчиком 28 и счетчиком-делителем 34, элементами ИЛИ 30 32 и дешифратором 33 формируют временную диаграмму первого такта интегрирования (фиг. Зз,и,к,л, на фиг.2 соответствующие им выходы 13 - 16). После окончания первого такта интегрирования при помощи элемента Н 36 формируется интервал второго такта интегрирования - интегрирование сигнала генератора образцового тока в тчение промежутка времени от заднего фронта импульса 6 до момента сра- баттзшания нуль-органа (фиг. 3м,н,о). Сигнал с прямого выхода триггера 35 (выход 18 блока 12 управления) вклю

10

14959966

чает цепь 23 восстановления начальны условий интегратора и положительным фронтом заносит информацию.о величине сигнала (состояние реверсивного

счетчика 28) и знаке (состояние триггера 25) в выходной регистр 29, на шине 20 которого действуют сигналы, несущие информацию о цифровом эквиваленте измеряемой аналоговой

величины, до следующего срабатывания триггера 35, т.е. занесения в регистр 29 результата очередного преобразования аналог - цифра.

Разрешение на считывание информации дается сигналом выхода дешифратора 33.

Выключается цепь восстановления начальных условий интегратора в момент действия положительного фронта сигнала О (фиг. Зз) на R-входе триггера 35. При этом потенциал прямого выхода триггера 35 становится равным нулю (фиг. Зн). С этого момента времени начинается очередной цикл преобразования: формирование первого такта интегрирования (на фиг. Зз изображен сигнал О, соответствующий началу первого такта интегрирования очередного цикла преобразова- ния), второго такта интегрирования сигнала генератора образцового тока и интервала времени восстановления начальных условий интегратора.

30 40

55

Ф

ормула изобретения 1. Интегрирующий аналого-цифровой преобразователь по авт. св. № 782152 отличающийся тем, что, с целью повышения помехозащищенности за счет подавления второй и третьей гармоник сигнала помехи, в него введены третий и-четвертый управляемые генераторы тока, четвертый и пятый

д5 ключи, информационные входы которых соединены с выходами соответственно третьего и четвертого управляемых генераторов тока, входы которых объединены и являются входной шиной,

50 выходы ключей соединены с входом интегратора, а их управляющие входы подключены к первому и второму дополнительным выходам блока управления соответственно.

2. Преобразователь по п. 1, о т - личающийся тем, что блок управления выполнен на генераторе тактовых импульсов, реверсивном счетчике, элементах И, ИЛИ, регистре,

счетчике-делителе, дешифраторе, пер- йом и втором триггерах, S-вход иерво- to из которых подключен к выходу первого элемента И, первый вход котороэлементов 11ПН соединены соответствен но с четвертым, пятым, шестым и седь мым выходами дешифратора, а их выходы являются соответственно вторым

о является входом блока, второй вход выходом, формирующим интервал инте(Ьбъединен с первым входом второго элемента И и подключен к первому выходу дешифратора, третий вход соединен с инверсным выходом генератора тактовых 1 мпульсов, R-вход первого триггера (оединен с вторым выходом дешифрато- Га, является синхронизирующим выходом Олока и подключен к первому входу

10

грирования входного сигнала, и первы дополнительным выходом блока, восьмо выход дешифратора является вторым дополнительным выходом блока, а соот ветствующие входы дешифратора через счетчик-делитель подключены к прямому выходу второго триггера и объединены с первым и нформационным входом

элементов 11ПН соединены соответственно с четвертым, пятым, шестым и седьмым выходами дешифратора, а их выходы являются соответственно вторым

выходом, формирующим интервал инте

грирования входного сигнала, и первым дополнительным выходом блока, восьмой выход дешифратора является вторым дополнительным выходом блока, а соответствующие входы дешифратора через счетчик-делитель подключены к прямому выходу второго триггера и объединены с первым и нформационным входом

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2354955C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА | 2004 |

|

RU2263300C1 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| Способ аналого-цифрового преоб-РАзОВАНия и уСТРОйСТВО для ЕгООСущЕСТВлЕНия | 1979 |

|

SU839050A1 |

| Нелинейный преобразователь | 1988 |

|

SU1674172A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1246376A1 |

| Низкочастотный измеритель частоты и фазы | 1990 |

|

SU1829013A1 |

| Устройство для измерения температуры | 1987 |

|

SU1490504A1 |

| ЦИФРОВОЙ НИЗКОЧАСТОТНЫЙ ФАЗОМЕТР-ЧАСТОТОМЕР МГНОВЕННОГО ЗНАЧЕНИЯ | 1990 |

|

RU2024027C1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

Изобретение относится к электроизмерительной технике и может быть использовано при проектировании помехозащищенных приборов и измерительных информационных систем. Преобразователь содержит четыре управляемых генератора тока, генератор образцового тока, пять ключей, блок управления, интегратор и нуль-орган. Подавление первой, второй и третьей гармонических составляющих сигнала помехи производится в течение семи промежутков времени интегрирования с соответствующими весовыми коэффициентами. Применение АЦП в многоканальных цифровых вольтметрах позволяет при сохранении высокой помехозащищенности ускорить процесс измерений за счет увеличения быстродействия по крайней мере в 3 раза. 1 з.п. ф-лы. 3 ил.

гервого элемента ИЛИ, второй вход ко- .с регистра и входом реверса реверсивногорого соединён с третьим выходом лешифратора, а выход является первым Iыходом блока, формирующим интервал интегрирования входного сигнала, прямой выход первого триггера соединен с входом записи регистра и является Iыходом блока, формирунлцим интервал J рамени для восстановления началь- 1ЫХ условий, инверсный выход триггера подключен к второму входу второго элемента И, выход которого является I ыходом блока, формирующим интервал второго такта интегрирования, первый lit второй входы второго и третьего ;

20

25

го счетчика, счетный вход которого подключен к прямому выходу генератора тактовых импульсов, первая и вторая группы выходов соединены соответственно с входами третьего и четвертого элементов И, третья группа выходов реверсивного счетчика соединена с соответствукяцими вторыми информационными входами регистра, выходы третьего и четвертого элементов И соединены соответственно с S- и R- входами второго триггера, выходы регистра являются разрядными выходами блока.

t4 ФФ

0

5

го счетчика, счетный вход которого подключен к прямому выходу генератора тактовых импульсов, первая и вторая группы выходов соединены соответственно с входами третьего и четвертого элементов И, третья группа выходов реверсивного счетчика соединена с соответствукяцими вторыми информационными входами регистра, выходы третьего и четвертого элементов И соединены соответственно с S- и R- входами второго триггера, выходы регистра являются разрядными выходами блока.

20

Фие. 1

Vi

Jl

л «4

s:

Фи9.3

| Интегрирующий аналого-цифровой преобразователь | 1979 |

|

SU782152A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-23—Публикация

1987-12-28—Подача