Изобретение относится к вычислите/1ьной технике, а именно к устройствам вывода цифровой информации для визуального считывания.

Известен счетчик импульсовс блокировкой индикации неэнача1аих старших разрядов/ состоящий из газоразрядных индикаторных ламп, N блоков передачи информации, дешифратора двоично-десятичного кода в десятичный , генератора цифр и переключателя положения запятой Ц.

Недостатком этого устройства являе,тся ограниченная область применения, обусловленная использованием в хеме блокировки цепей переноса нереверсивного де;сятичного счетчика.

Известно также устройство гашения незначащих разрядов для динамической индикации, состоящее из переключателя положения запятой, блоков передачи информации, N газоразрядных индикаторных ламп, генераторов цифр, генератора нуля, дешифратора, распределителя импульсов на N+1 выход, элемента объединения на N выходов, элемента запрета, N элементов совпадения и N-1 триггеров 2 .

Недостатками данного устройства являются ограниченные функциональные возможности, определяемые условием гашения незначащих нулей только старших разрядов и сложностью устройства.

Цель изобретения - упрощение устройства.

Поставленная цель достигается

10 тем, что устройство для индикации, содержащее распределитель импульсов, соединенный с первыми входами блоков памяти, с управлякяцими электродами индикаторов, входами блока уп15равления, первый элемент ИЛИ, входы которого соединены с выходами блоков памяти, а выходы - с входами дешифраторов, выходы первого дешифратора соединены с информационными

20 электродами индикаторов, содержит два элемента И, второй третий и четвертый элементы ИЛИ и два триггера, причем выход второго дешифратора соединен с вторыми входами элемен25тов И и второго и третьего элементов ИЛИ, первые входы элементов и соединены с соответствующими выходами распределителя импульсов, первые входы второго и третьего элементов ИЛИ соединены с выходами

блока управления, выходы первого элемента И и второго элемента ИЛИ соединены с входами первого триггера, а выходы второго элемента И и третьего элемента ИЛИ соединены с входами второго триггера, выходы триггеров соединены с входами четвертого элемента ИЛИ, выход которого соединен с стробирующим входом второго дешифратора.

А также тем, что в устройство для индикации, содержащеераспределитель импульсов, соединенный с первыми входами блоков памяти, с управляющими электродами индикаторов, первый элемент ИЛИ, входы которого соединены с выходами блоков памяти, а выходы - с входами дешифраторов, выходы первого дешифратора соединены с информационными электродами индикаторов, введены элемент И, второй элемент ИЛИ и триггер, выход второго деиж1фратора.соединен с первыми входами элемента И и второго элеме.нта ИЛИ, выходы которых соединены с входами триггера, выход которого соединен с стробирующим входом первого дешифратора, причем вторые входы элемента И и второго элемента ИЛИ соединены с соответствующими .выходами распределителя импульсов.

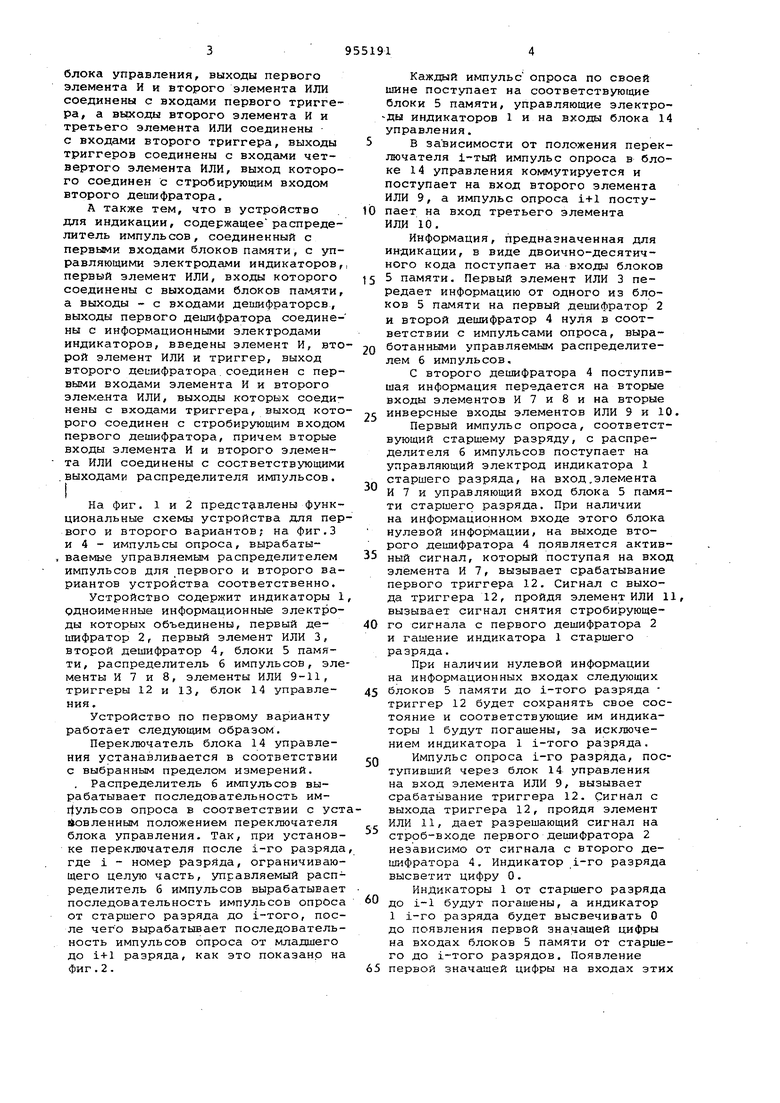

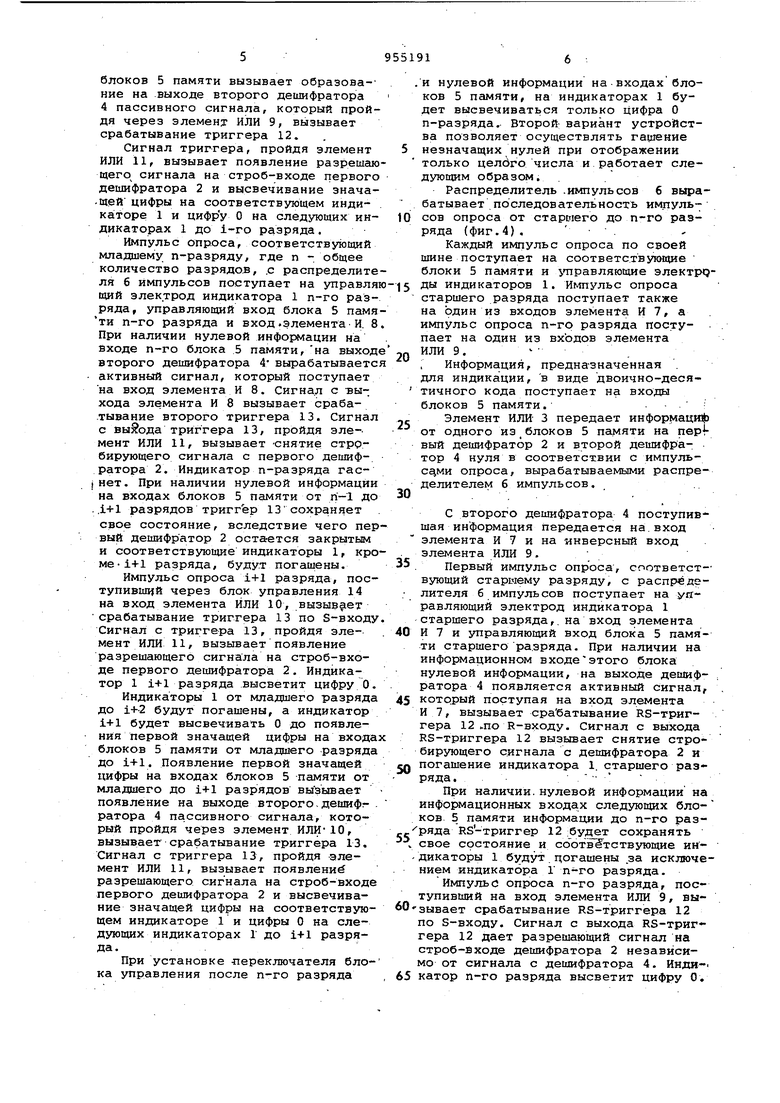

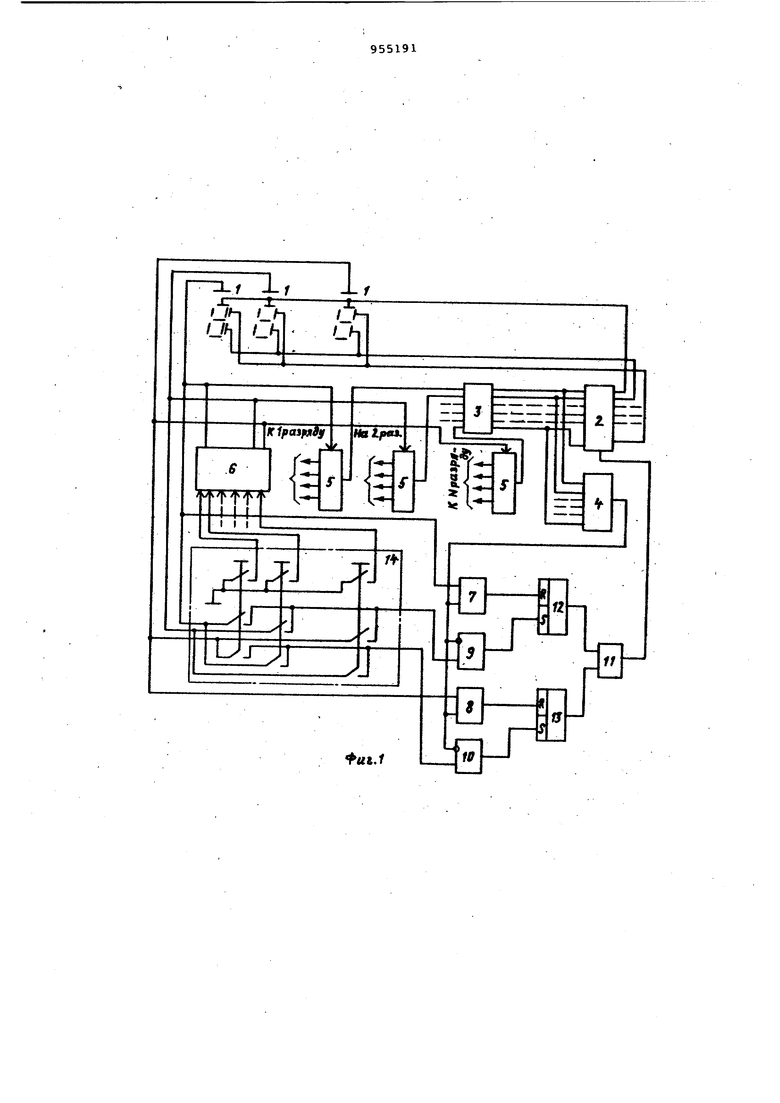

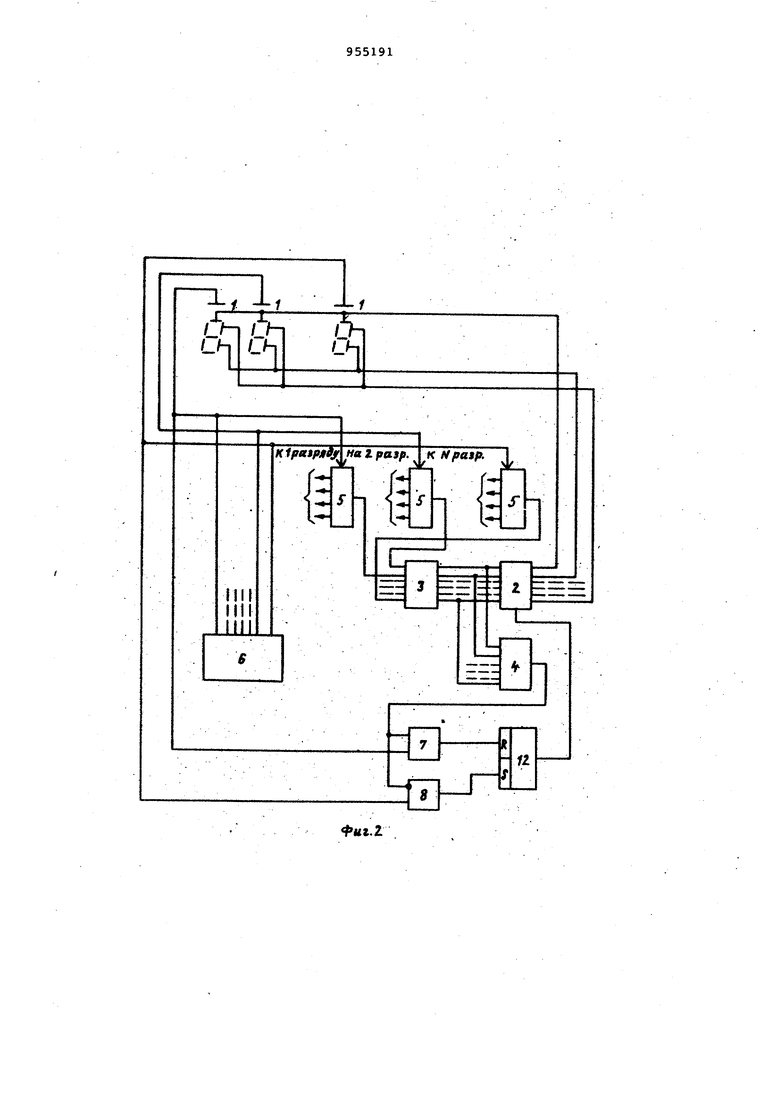

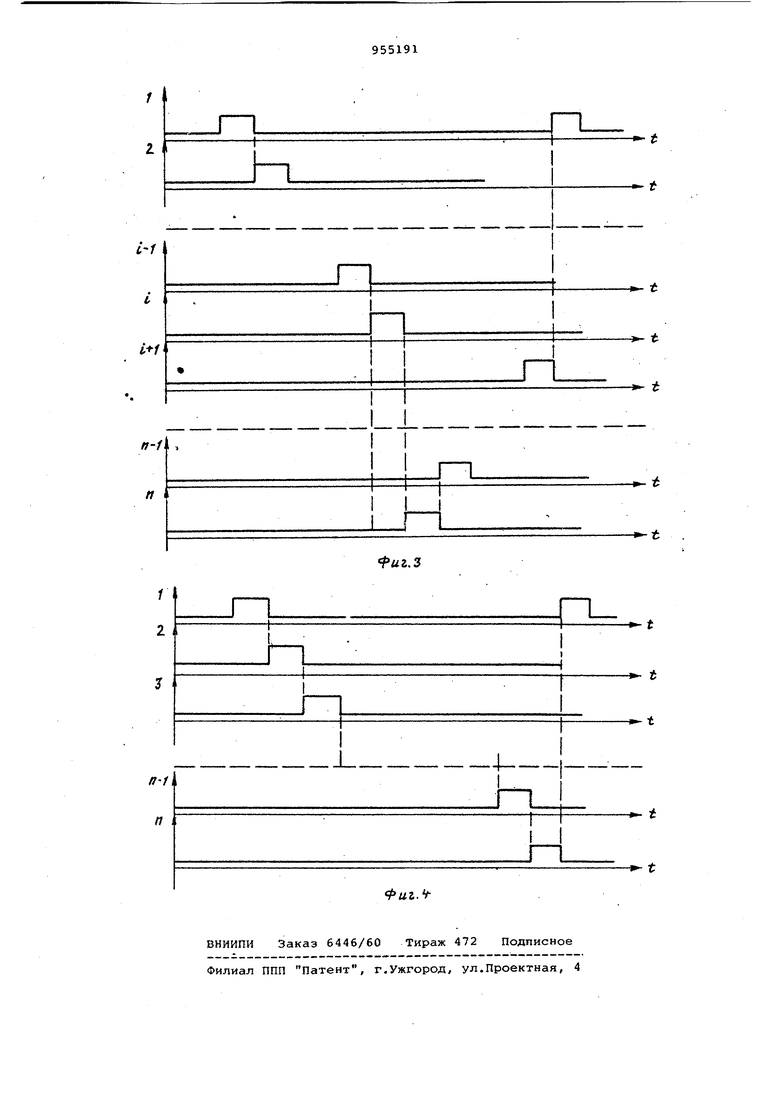

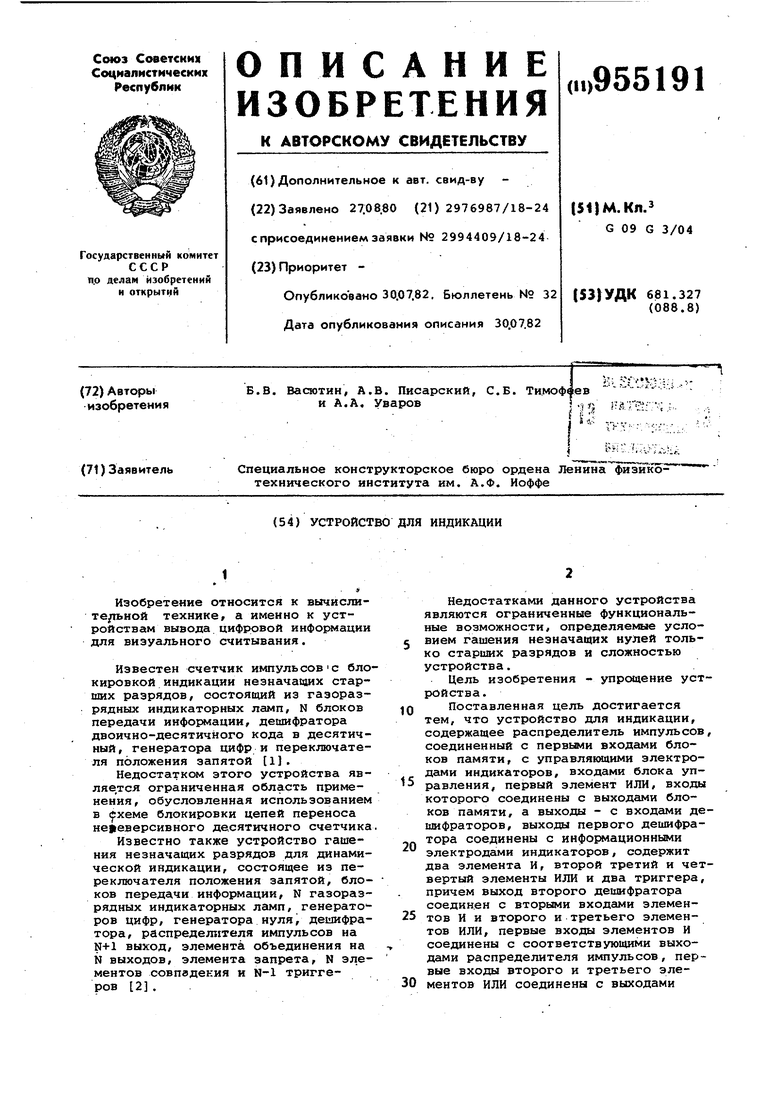

На фиг. 1 и 2 представлены функциональные схемы устройства для первого и второго вариантов; на фиг.З и 4 - импульсы опроса, вырабатываемые управляемым распределителем импульсов для первого и второго вариантов устройства соответственно.

Устройство содержит индикаторы 1 одноименные информационные электроды которых объединены, первый дешифратор 2, первый элемент ИЛИ 3, второй дешифратор 4, блоки 5 памяти, распределитель 6 импульсов, элементы И 7 и 8, элементы ИЛИ 9-11, триггеры 12 и 13, блок 14 управления ,

Устройство по первому варианту работает следующим образом.

Переключатель блока 14 управления устанавливается в соответствии с выбранным пределом измерений.

, Распределитель б импульсов вырабатывает последовательность имг|ульсов опроса в соответствии с устйовленным положением переключателя блока управления. Так, при установке переключателя после i-ro разряда где i - номер раэряда, ограничивающего целую часть, управляемый распределитель б импульсов вырабатывает последовательность импульсов опроса от старшего разряда до i-того, после чего вырабатывает последовательность импульсов опроса от младшего до i+1 разряда, как это показано на фиг.2.

Каждый импульс опроса по своей шине поступает на соответствующие блоки 5 памяти, управляющие электро ды индикаторов 1 и на входы блока 14 управления.

В зависимости от положения переключателя 1-тый импульс опроса в блоке 1 4 управления коммутируется и поступает на вход второго элемента ИЛИ 9, а импульс опроса i+1 поступает на вход третьего элемента ИЛИ 10.

Информация, предназначенная для индикации, в виде двоично-десятичного кода поступает на входы блоков 5 памяти. Первый элемент ИЛИ 3 передает информацию от одного из блоков 5 памяти на первый дешифратор 2 и второй дешифратор 4 нуля в соответствии с импульсами опроса, выработанными управляемым распределителем 6 импульсов.

С второго дешифратора 4 поступившая информация передается на вторые входы элементов И 7 и 8 и на вторые инверсные входы элементов ИЛИ 9 и 10

Первый импульс опроса, соответствующий старшему разряду, с распределителя б импульсов поступает на управляющий электрод индикатора 1 старшего разряда, на вход,элемента И 7 и управляющий вход блока 5 памяти старшего разряда. При наличии на информационном входе этого блока нулевой информации, на выходе второго дешифратора 4 появляется активный сигнал, который поступая на вход элемента И 7, вызывает срабатывание первого триггера 12. Сигнал с выхода триггера 12, пройдя элемент ИЛИ 1 вызывает сигнал снятия стробирующего сигнала с первого дешифратора 2 и гашение индикатора 1 старшего разряда.

При наличии нулевой информации на информационных входах следующих блоков 5 памяти до i-того разряда триггер 12 будет сохранять свое состояние и соответствующие им индикаторы 1 будут погашены, за исключением индикатора 1 i-того разряда.

Импульс опроса i-ro разряда, поступивший через блок 14 управления на вход элемента ИЛИ 9, вызывает срабатывание триггера 12. Сигнал с выхода триггера 12, пройдя элемент ИЛИ 11, дает разрешающий сигнал на строб-входе первого дешифратора 2 независимо от сигнала с второго дешифратора 4. Индикатор i-ro разряда высветит цифру О.

Индикаторы 1 от старшего разряда до i-1 будут погашены, а индикатор 1 i-ro разряда будет высвечивать О до появления первой значащей цифры на входах блоков 5 памяти от старшего до разрядов. Появление первой значащей цифры на входах этих

блоков 5 памяти вызывает образование на выходе второго дешифратора 4 пассивного сигнала, который пройдя через элемент ИЛИ 9, вызывает срабатывание триггера 12.

Сигнал триггера, пройдя элемент ИЛИ 11, вызывает появление разрешающего сигнала на строб-входе первого дешифратора 2 и высвечивание знача щей цифры на соответствующем индика:торе 1 и цифру О на следующих индикаторах 1 до 1-го разряда.

Импульс опроса, соответствующий младшему п-разряду, где п -. общее количество разрядов, .с распределителя б импульсов поступает на управляющий электрод индикатора 1 п-го разряда, управляющий вход блока 5 памяти п-го разряда и вход .элемента И. 8. При наличии нулевой информации на входе п-го блока 5 памяти, на выходе второго дешифратора 4 вырабатывается активный сигнал, который поступает на вход элемента И 8. Сигна.л с выхода элемента И 8 вызывает срабатывание второго триггера 13. Сигнал с вывода триггера 13, пройдя эле-мент ИЛИ 11, вызывает снятие стррбирующего сигнала с первого дешиф-. ратора 2. Индикатор п-разряда гасНет. При наличии нулевой информации на входах блоков 5 памяти от п-1 до .i+1 разрядов триггер 13сохраняет свое состояние, вследствие чего первый дешифратор 2 оста-ется закрытым и соответствующие индикаторы 1, кроме- 1+1 разряда, будут погашены.

Импульс опроса 1+1 разряда, поступивший через блок управления 14 на вход элемента ИЛИ 10, вызывает срабатывание триггера 13 по S-входу. Сигнал с триггера 13, пройдя элемент ИЛИ 11, вызывает появление разрешающего сигнала на строб-входе первого дешифратора 2. Индикатор 1 1+1 разряда высветит цифру 0.

Индикаторы 1 от младшего разряда до 1+-2 будут погашены, а индикатор 1+1 будет высвечивать О до появления первой значащей цифры на входах блоков 5 памяти от младшего разряда до 1+1. Появление первой значащей цифры на входах блоков 5 памяти от младшего до 1+1 разрядов вызывает появление на выходе второго.дешифг- . ратора 4 пассивного сигнала, который пройдя через элемент ИЛИ10, вызывает срабатывание триггера 13, Сигнал с триггера 13, пройдя элемент ИЛИ 11, вызывает появлений разрешающего сигнала на строб-входе первого дешифратора 2 и высвечивание значащей цифры на соответствующем индикаторе 1 и цифры О на следующих индикаторах Г до 1+1 разряда. ..

При установке -переключателя блока управления после п-го разряда

.и нулевой информации на-входах блоков 5 памяти, на индикаторах 1 будет высвечиваться только цифра О п-разряда. Второй вариант устройства позволяет осуществлять гашение незначащих нулей при отображении только целого числа и работает следующим образом.

Распределитель .импульсов б вырабатывает последовательность импульсов опроса от старшего до п-го разряда (фиг.4) . .

Каждый импульс опроса по своей шине поступает на соответствующие блоки 5 памяти и шравляющие электр }5 ДЫ индикаторов 1. Импульс опроса

старшего разряда поступает также на один из входов элемента И 7, а импульс опроса п-гр разряда поступает на один из входов элемента ИЛИ 9.

0

Информация, предназначенная . для индикации, в виде двоично-деся тичного кода поступает на входы блоков 5 памяти.- Элемент ИЛИ 3 передает информациф от одного из блоков 5 памяти на nepf вый дешифратор 2 и второй дешифратор 4 нуля в соответствии с импульс ми опроса, вырабатываемыми распределителем 6 импульсов,

0

С второго деишфратора 4 поступившая информация передается на.вход элемента И 7 и на инверсный вход

. элемента ИЛИ 9.

5. Первый импульс опроса, соответствующий старшему разряду, с распрнёделителя 6 импульсов поступает на управляющий электрод индикатора 1 старшего разряда,, на вход элемента

0 И 7 и управляющий вход блока 5 памяти старшего ра.зряда. При наличии на информационном входеэтого блока нулевой информации, на выходе дешифратора 4 появляется активный сигнал,

5 который поступая на вход элемента И 7, вызывает срабатывание RS-триггера R-входу. Сигнал с выхода RS-триггера 12 вызывает снятие стробирующего сигнала с дешифратора 2 и

0 погашение индикатора 1. старшего разряда.

При наличии.нулевой информации на инфОЕ 1ационных входах следующих блоков 5 памяти информации до п-го разряда RS-триггер 12 :будет сохранять

Ч свое состояние и соотв тствующие ин-дика торы 1 будут , цогашены .за исключением индикатора Г п-го разряда.

Импульс опроса п-го разряда, поступивший на вход элемента ИЛИ 9, вы0зывает срабатывание RS-триггера 12 по S-входу. Сигнал с выхода RS-триггера 12 дает разрешающий сигнал на строб-Входе дешифратора 2 независимо от сигнала с дешифратора 4. Инди-i

5 катор п-го разряда высветит цифру О,

Индикаторы 1 от старшего разряда о п-го будут погашены, а индикатор 1 п-го разряда будет высвечивать цифру О до появления первой значащей цифры на. входах блоков 5 памяти от таршего до п-го разряда. Появление первой значащей цифры на входах этих блоков 5 памяти вызывает образование на выходе дешифратора 4 пассивного сигнала, который пройдя элемент ЛИ 8, вызывает срабатывание RS-триггера 12 по S-входу. Сигнал с RS-триггера 12 дает разрешающий сигнал на строб-входе дешифратора 2. Значащая цифра высветится на соответствующем индикаторе 1, а на последующих индикаторах высветятся О или значащие цифры.

Предлагаемое устройство- позволяет Sмeньшить утомляемость операторов при контроле технологических процессов, когда допущенные оператором ошибки могут привести к значительным последствиям.

Гашение незначащих нулей старших и младших разрядов, кроме тех, которые входят в состав отображаемого числа, снижает утомляемость зрения оператора, а высвечивание нулей слева и справа от установленной запятой придает уверенность оператору, что прибор включен и установка функ ционируат.

В предлагаемом техническом решении сокращено оборудование устройства, что значительно упростило его изготовление.

По сравнению с прототипом в устройстве сокращено количество триггеров, иск1почены логические элементы на четыре входа, исключены генераторы цифр, что значительно упростило схемное решение.

Формула изобретения

1. Устройство для индикации, содержащее распределитель импульсов, соединенный с первыми входами блоков памяти, с управляющими эле.ктродаМи индикаторов, входами блока управления, первый элемент ИЛИ, входы которого соединены с выходгши блоков памяти, а выходы - с входами

дешифраторов, выходы первого дешифратора соединены с информационными электродами индикаторов, отличающееся тем, что, с целью упрощения устройства, оно содержит

два элемента И, второй,третий и. четвертый элементы ИЛИ и два триг,- гера, причем выход второго дешифратора соединен с вторыми входами элементов И и второго и третьего элементов ИЛИ, первые входы элементов И соединены с соответствующими выходами распределителя импульсов, первые входы второго н третьего элементов ИЛИ соединены с выходами

5 блока управления, выходы первого элемента И и второго элемента ИЛИ .соединены с входами первого триггера, а выходы второго элемента И и третьего элемента ИЛИ соединены с входами второго триггера, выходы

триггеров соединены с входами четвертого элемента ИЛИ, выход которого соединен со стробирующим входом второго дешифратора.

2. Устройство для индикации.

содержащее распределитель импульсов, соединенный с первыми входами блоков памяти, с управляющими электродами индикаторов, первый элемент ИЛИ, входы которого соединены с выходами

0 блоков памяти, а выходы - с входами дешифраторов, выходы первого дешифратора соединены с информационными электродами индикаторов, о т л ич ающе ее я тем, что, с целью

5 упрощения устройства, оно содержит элемент И, второй элемент ИЛИ и триггер, выход второго дешифратора соединен с первыми входами элемента И и второго элемента ИЛИ, выходы .

0 которых соединены с входами триггера, выход которого.соединен со стробирующим входом первого дешифратора, причем вторые входы элемента И и второго элемента ИЛИ соединены с соот5 вётствующими выходами распределителя импульсов.

Источники информации, принятые во внимание при экспертизе

1.Патент США 3632998, кл. 238-920, опублик. 1971.

2.Авторское свидетельство СССР 571803, кл. G 06 F 3/04, 1977 (прототип).

If

5T15r сьГ

Ul C Lh

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1983 |

|

SU1149306A1 |

| Устройство для индикации | 1985 |

|

SU1310886A1 |

| УСТРОЙСТВО для ЦИФРОВОЙ ИНДИКАЦИИ | 1973 |

|

SU370603A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для индикации | 1978 |

|

SU744664A1 |

| Устройство для цифровой индикации | 1981 |

|

SU1045226A1 |

| Устройство для индикации | 1979 |

|

SU851453A1 |

| Устройство для индикации | 1982 |

|

SU1163349A1 |

| Устройство для отображения информации | 1981 |

|

SU987670A1 |

| Устройство для проверки электрического монтажа | 1986 |

|

SU1336035A1 |

KifMfxSy

S Г/ ГМ

I I I

S

- -Lt:ji

31

HatfMO,

ГгЧ

I

V

Й

;7

IT

Л, i

ill I

Mil

ill

J1

i

Ь

- t

- t

n

t

«г.З

cu

L.

..

Авторы

Даты

1982-08-30—Публикация

1980-08-27—Подача