Изобретение относится к вычислитель- 1ной технике и может быть использовано в цифровых вычислительных машинах для деления чисел в форме с плавающей запятой.

Цель изобретения - расширение функциональных возможностей устройства за счет деления ненормализованных исходных операндов и повышение достоверности вычисляемых результатов.

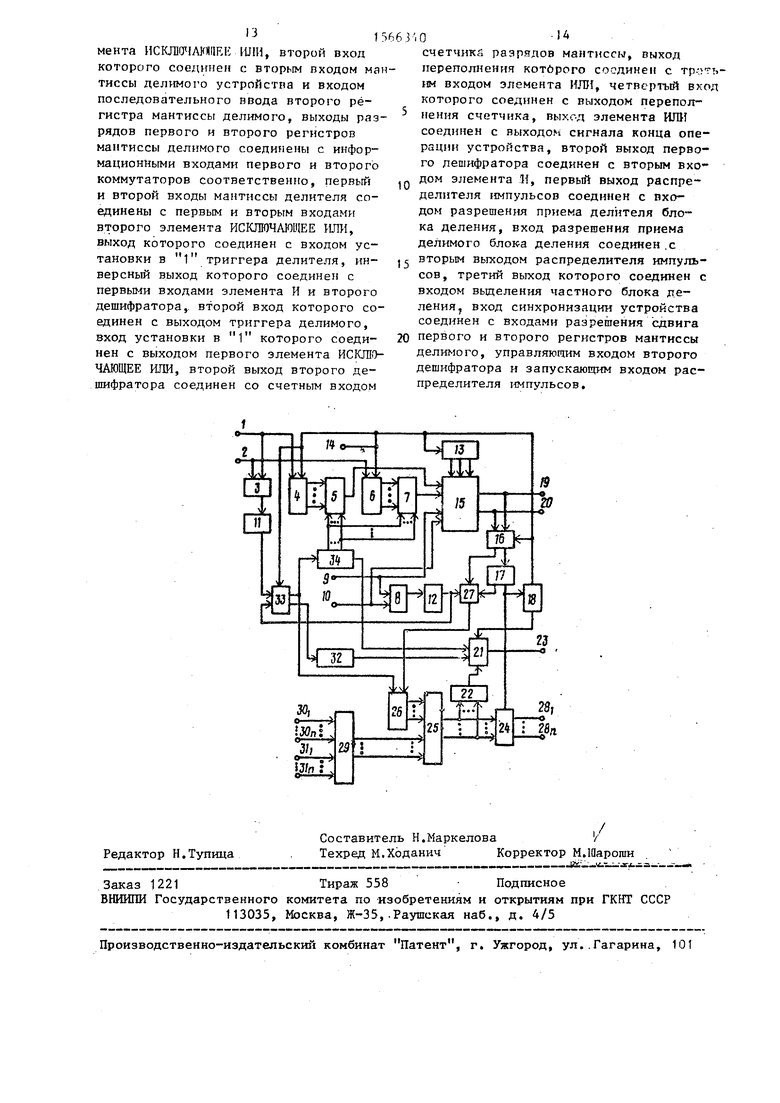

На чертеже представлена структурная схема устройства для деления чисел в форме с плавающей запятой.

Устройство содержит входы 1 и 2 мантиссы делимого, элемент ИСКЛЮЧАЮ- ИЛИ 3, первый регистр 4 мантиссы делимого, первый комм гатор 5, второй регистр Ь мантиссы лепимого, второй коммутатор 7, - ЧРМГНТ ИСКЛЮЧАЮЩЕЕ ИЛИ 8, РХОДЫ ° и 10 мантиссы

елителя, триггер 11 делимого, тригер 12 делителя, распределитель 13 мпульсов, вход 14 синхронизации, лок 15 деления, первый дешифратор 16, риггер 17, регистр 18 управления, ходы 19 и 20 мантиссы частного, элеент ИЛИ 21, блок 22 сравнения, выход 23 сигнала конца операции, регистр 24 орядка частного, сумматор 25 норма- изации, счетчик 26 нормализации, элемент И 27, выходы 28-28ппорядка частного, сумматор 29 порядков, вхоы 30-ЗО и порядков делимого и делителя соответственно, счетчик ,, 32 разрядов мантиссы, второй дешифратор 33 и счетчик 34.

Регистры 4,6.и 18 выполнены сдвига- Лщими, разрядность которых равна га 1 (m-разрядность мантисс) . -

Блок 15 деления можно построить, например, с помощью регистров делимого и делителя, блока суммирования, регистра частного, триггера, дешифратора и элемента ИЛИ. Этот извест- 25 ный блок предназначен для деления последовательно поступающих, начиная со старших разрядов, мантисс операндов, представленных в избыточной двоичной системе.счисления с цифрами 1,0 и -1. В каждом цикле вычислений (где ,2,3...) такой блок при последовательном поступлении на его входы разрядов мантисс операндов с весом формирует на своих выходах разряды мантиссы частного с весом 35 , т.е. разряды мантиссы частного вычисляются с запаздыванием на три цикла. При этом обеспечивается совмещение во времени процессов поразрядного ввода мантисс операндов и их обработки.

Цифры избыточной двоичной системы, с помощью которых представляются раз ряды мантисс исходных операндов и частного, изображены кодом канонической двоичной системы. Так, цифре -1 соответствует наличие сигнала логической единицы на входах 1 или 9 или на выходе 19.. Цифре 1 соответствует 50 наличие сигнала логической единицы на входах 2 или 10 или на выходе 20. Цифре 0 соответствует либо отсутствие сигнала логической единицы на входах 1 и 2 или 9 и 10, а также на выходах 55 19 и 20, либо наличие такого сигнала на каждом входе и выходе перечисленных пар. Другими словами, цифра О

30

,

5 5

50 55

0

может быть представлена двоичным кодом 00 либо 11 .

Дешифратор 16 служит для распознавания первого значащего разряда мантиссы частного.

Блок 22 сравнения представляет собой стандартную схему сравнения чисел, рыполняющую сравнение вычисляемого значения порядка частного с величиной минимального порядка, при котором формируемое частное можно считать равным нулю. Величина такого минимального порядка заранее известна и равна -2Ь 1 (где п -1 - разрядность порядка без учета знакового разряда). Для представления порядков операндов и частного используется каноническая двоичная система счисления. Значения порядков представляются со знаком с помощью дополнительного кода.

В качестве сумматоров 25 и 29 могут быть использованы стандартные п - разрядные двоичные сумматоры комбинационного типа. Оба сумматора служат для выполнения операции вычитания с учетом знаков слагаемых. Сумматор 29 вычисляет разность порядков делимого и делителя. Для этого у сумматора 29 все п входов второго слагаемого, подключенных к входам 31.,- 31 „порядка делителя, являются инвертирующими, а на вход переноса младшего разряда этого сумматора подается сигнал логической единицы. Сумматор 25 определяет разность между числом на выходе сумматора 29 и содержимым счетчика 26. Для этого все п входов первого слагаемого сумматора 25 также являются инвертирующими (они подключены к выходам счетчика 26).

Счетчик 26 нормализации - это стандартный п - разрядный реверсивный двоичный счетчик, исходное состояние которого -4 в обратном коде.

Счетчики 32 и 34 представляют собой обычные двоичные суммирующие счетчики, коэффициенты счета которых соответственно равны m + 1.

Устройство работает следующим образом.

Перед выполнением операции деления счетчика 32 и 34, все триггеры и регистры устройства устанавливаются в нулевое состояние, а блок 15 и счетчик 26 - в исходное (цепи установки не показаны). Установка очередных 1-х разрядов мантисс операндов на входах 1,2 и 9,10 устройства в каждом

515

i-м цикле вычислений происходит под действием синхронизирующих сигна- лоп с входа 14, а именно по спадающему фронту этих сигналов. Кроме того, синхронизирующие сигналы своими спа- даклцими фронтами выполняют как сдвиги на один разряд в регистрах 4,6 и 18, так и запуски распределителя 13. При обработке нормализованных и не рав- ньгх нулю операндов с появлением синхронизирующих сигналов с входа 14 на выходы 1,2 и 9,10 поразрядно поступают соответственно коды разрядов мантисс делимого и делителя, начиная со старших разрядов. Одновременно с поступлением на входы 1,2 и 9,10 первых старших разрядов (с несом ) мантисс операндов их порядки подаются на входы 30,- 31,- 31. Сумматор 29 вычисляет разность поступивших порядков с учетом их знаков. Полученная разность с вькодов сумматора 29 выдается на входы второго слагаемого сумматора 25 для последующих преобразований в соответствии со значениями разрядов мантиссы частного, которые в каждом i-м цикле вычислений формирует на своих выходах блок 1 Последний производит вычисления в каждом i-м цикле под управлением трех сигналов от распределителя 13, который в свою очередь, под действием каждого i-rc синхронизирующего сигнала на своем запускающем входе вырабатывает следующие друг за другом и неперекрывающиеся во времени три необходимых блока 15 управляющих сигнала.

При поступлении на входы 1,2 и 9,10 двоичных кодов первых старших знача- щих разрядов мантисс операндов элементами 3 и 8 на своих выходах вырабатываются сигналы логических единиц, которые устанавливают в единичное состояние триггеры 11 и 12. Дешифратор 33 анализирует состояния триггеров 11 и 12 по синхронизирующим сигналам с входа 14 устройства. Причем на первом выходе дешифратора 33 сигнал логической единицы возникает тогда, когда в единичном состоянии находится триггер 11. Появление сигнала логической единицы на втором выходе дешифратора 33 происходит в том случае, когда триггер 11 находится в нулевом состоянии, а состояние триггера 12 при этом может быть произвольным.

Если оба триггера 11 и 12 находятся в единичном состоянии, то формирова

5

0

3

Q 5 о

Q ,-

5

0

5

4 0«

нне сигналов логически едишш на выходах дешифратора 33 HI, происходит. Для случая нирмализсг лнных мантисс состояние счетчика 34 остается нулевым после прихода червых старших разрядов мантисс операндов и не изменяется п процессе вычислений. Коммутаторы 5 и 7, имея на своих управляющих входах нулевой двоичный код, к споим вькодам через свои первые информационные входы подключают выходы первых разрядов регистров 4 и 6, С выходов коммутаторов- 5 и 7 двоичные коды разрядов мантиссы делимого, задержанные с помощью регистров 4 и 6 на один цикл вычислений по отношению к цвоич- ным кодам разрядов мантиссы п.-штеля, подаются на входы депимо1о хтока 15. Задержка разрядов мантиссы делимого необходима для правильного функционирования блока 15, поскольку для него необходимо, чтобы делимое было меньше делителя.

Таким образом, по каждому i-му си (иронизирующему сигналу двоичный код с входоь 1 и 2 запоминается в регистрах 4 и 6 и в следующем цикле с выходов первых разрядов этих регистров через коммутаторы 5 и 7 поступает на входы делимого блока 15. Последний на основгшш поступающих разрядов мантисс операндов формирует на своих выходах разряды мантиссы частного с запаздыванием на три цикла вычислений. По каждому i-му синхронизирующему сигналу через выходы 19 и 20 выдсзются из устройства коды разрядов мантиссы частного, которое при этом анализируются1 дешифратором 16. Причем, если анализируемой цифрой мантиссы частного является 0, то дешифратор 16 на своем втором выходе по синхронизирующему сигналу с входа 14 формирует сигнал логической единицы. Этот сигнал поступает на первый вход элемента И 27, на втором и третьем входах которого в настоящее время, т.е. после прихода первого старшего значащего разряда мантиссы делителя и до появления первого значащего разряда мантиссы частного на выходах блока 15, установлены разрешающие потенциалы логических единиц. Поэтому сигнал логической единицы с второго выхода дешифратора 16 через элемент И 27 поступает на суммирующий вход счетчика 26 и увеличивает его содержимое на единицу. При помпщи сумматора 25 определяется разность между числом (уменьшаемое) на выходе сумматора 29 и содержимом (вычитаемое) счетчика 26. Таким образом, по каждому разряду вычисляемой блоком 15 мантиссы частного, начиная с первого старшего разряда, равного нулю, осуществляется меньшение разности порядков на ej иницу до появления пер- вого значащего разряда.

При получении первого значащего разряда мантиссы частного, равного 1 или -1, дешифратор 16 по синхронизирующему сигналу выдает сигнал логи- ческой единицы на своем первом выходе устанавливая таким образом триггер 17 в единичное состояние. При этом появившийся логический нуль на нулевом выходе триггера 17 блокирует прохожде ние возможных последующих сигналов логической единицы через элемент 27 с второго выхода дешифратора 16 на суммирующий вход счетчика 26.

Сигнал логической единицы с единич ного выхода триггера 17 устанавливает в состояние единицы первый младший разряд регистра 18 управления, а также- производит запись в регистр 24 значения откорректированного на суммато- ре 25 порядка частног . Вследствие этого на выходах 28-28пустанавливает- ся порядок еще вычисляемой, но уже нормализованной мантиссы частного. Под действием последующих синхронизирующих сигначов в регистре 18 про исходит сдвиг логической единицы от младших разрядов этого регистра к старшим. Это позволяет вести отсчет

числа выдаваемых разрядов нормализованной мантиссы частного. Вычисления разрядов мантиссы частного устройством прекращается, когда единица в регистре 18 появляется в его старшем (т +1) м разряде. При этом через выходы 19 и 20 выдано m разрядов нормализованной мантиссы частного. Признак окончания операции деления формируется с помощью сигнала логической единицы на выходе 23 устройства по сигналу логической единицы на первом входе элемента ИЛИ 21.

Если же в процессе одновременного вычисления мантиссы частного, ее нормализации и соответствующей корректировки порядка частного его значе- ние на выходах сумматора 25 становится равным значению минимально допустимого порядка, то блок 22 срав

,Q

,-

25

35

40

45

50

нения определяет это и на его выходе устанавливается сигнал логической единицы. Этот сигнал попадает на второй вход элемента ИЛИ 21 и, пройдя через этот элемент, появляется на выходе 23 сигнала конца опт рации устройства, свидетельствуя о Том, что очгфация закончена.

Предлагаемое устройство позволяет также выполнять операцию деления ненормализованных операндов и обраба- .ывать ситуации, когда одна либо обе мантиссы исходных операндов равны нч лю. Такие случаи могут возникать, например, при использовании предлагаемого устройства в контуре управления системой, работающей в реальном времени. В этих условиях работы на входы устройства, как правило, поступают ненормализованные либо даже нулевые операнды, формирующиеся в преобразователях поразрядного уравновешивания, которые работают синхронно.

Работа устройства для ситуации нулевых мантисс выглядит следующим образом; Если на входы 1,2 и 9,10 устройства начинают поступать разряды мантисс, равные нулю, то по каждому i - му синхронизирующему сигналу с входа 14 депгифратор 33 на своем втором вьЬсоде выдает сигнал логической единицы, который увеличивает каждый раз содержимое счетчика 32 на единицу. Производя отсчет (м + 1)-го сигнала, счетчик 32 формирует на своем выходе сигнала переполнения логическую единицу. Такой сигнал, пройдя через элемент ИЛИ 21, появляется на выходе 23 устройства, сигнализируя об окончании операции. В этом случае, если мантисса делителя не равна нулю, то после появления на входах 9 и 10 первого значащего разряда элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 8 будет выдана логическая единица на вход установки в единичное состояние триггера 12, который при этом изменит свое состояние на единичное. Однако дешифратор 33 после этого будет продолжать формирование сигналов логических единиц на своем втором выходе по синхронизирующим сигналам. В результате этого будет получен сигнал переполнения счетчика 32,который приведет к выработке элементом ИЛИ 21 сигнала конца операции на выходе 23 ус- стройства.

915

Сигнал конца операции может быть получен раньше, если на выходах сумматора 25 в процессе ввода мантисс операндов образуется число, равное значению минимально допустимого по- рядка, что обнаруживается блоком 22, который при сложившейся ситуации на своем выходе устанавливает сигнал логической единицы, вызывающей ление аналогичного сигнала на выходе 23. Такая ситуация может возникнуть, поскольку после установки в единичное состояние триггера 12 на суммирующий вход счетчика 26 начинают про- ходить сигналы логических единиц через элемент И 27 от второго выхода дешифратора 16, увеличивая содержимое счетчика 26. При этом значение числа на выходах сумматора 25 уменьшает- ся.

Если мантисса делителя равна нулю, а мантисса делимого ненулевая, то с приходом первого значащего разряда мантиссы делимого на выходы 1 и 2 устройства происходит установка в единичное состояние триггера 11 логической единицей с выхода элемента 3 Теперь счетные сигналы логических единиц начинают поступать на счетный вход счетчика 34 и вычитающий вход счетчика 26 от первого выхода дешифратора 33. Отсчитав m + 1 счетных сигналов, счетчик 34 формирует сигнал переполнения на одноименном выходе в виде логической единицы, которая, пройдя через элемент ИЛИ 21, возчи- кает на выходе 23 устройства.

При делении ненулевых ненормализованных мантисс исходных операндов ус- тройство работает следующим образом.

При одновременном появлении первых значащих разрядов мантисс делимого и делителя работа устройства аналогична делению нормализованных мантисс. Если первым значащий разряд в процессе поразрядного ввода возникает на входах 1 и 2 разрядов мантиссы делимого устройства, то это определяет элемент 3, на своем выходе форми- руя логическую единицу.

Этот сигнал устанавливает триггер 11 в единичное состояние. После этого и до момента появления на выходах 9 и 10 первого значащего разряда мантиссы делителя по каждому синхронизирующему сигналу с входа 14 дешифратором 33 на его первом выходе вырабатывается сигнал логической единицы.

. Q ,5 20

5 -JQ

JQ

0

5

5

,010

Указанный сигнал поступает па тычитающий вход счетчика 26, уменьпшч его содержимое на единицу, i на счетный вход счетчика 34, увеличивая его содержимое на единицу Уменьшение содержимого счетчик1- 26 приводит к росту значения числа на выходе сумматора 25, где происходит формирование порядка вычисляемого частного. Таким образом достигается совмепеннр во времени процесса поразрядного чво- да ненормализованных мантисс и процесса коррекции порядка частного по нулевым разрядам мантиссы делителя до прихода на входы 9,10 первого значащего разряда мантиссы дегштеля.

Двоичные коды разрядов манпк-сы делимого с входов 1 и 2 последовательно разряд за разрядом по каждому синхронизирующему сигналу вводятся в сдвигающие регистры 4 и 6. До момента поступления первого значащего разряда мантиссы.делителя на входы 9 и 10 с помощью счетчика 34 и коммутаторов 5 и 7 осуществляется слежение за движением кодов разрядов делимого в регистрах 4 и 6. С приходом первого значащего разряда мантиссы делителя на входы 9 и 10 триггера 12 по сигналу логической единицы с выхода элемента 8 переходит в единичное ос- тояние, после чего дешифратор 33 лре- кращает форм фовать на своем первом выходе сигналы логических единиц. Содержимое счетчика 34 задает информа- ционный вход коммутаторов л и 7, обеспечивая таким образом поступление разрядов мантиссы делимого на входы делимого блока 15 с задержкой на одьн цикл по отношению к разрядам мантиссы делителя, которые подаются на входы делителя блока 15.Такая задержка необходима для правильной работы блока 15, поскольку при этом достигается условие превышения мантиссы делителя над мантиссой делимого. Дальнейший процесс вычисления частного аналогичен работе устройства при делении нормализованных операндов.

В том случае, когда первый значащий разряд поступает на входы 9 i 10 разрядов мантиссы делителя устройства, происходит установка в единичное состояние триггера 12 сигналом логической единицы с выхода элемента Я. После этого на суммирующий вход счетчика 26 по каждому синхронизирующему сигналу начинают поступать сигн.1И15

лы логических единиц с второго выхода дешифратора 16 через элемент И 27, на третий вход которого подан разрешающий сигнал логической единицы с выхода триггера 12. Такая коррекция порядка вычисляемого частного происходит до тех пор, пока на выходах блока 15 не появится двоичный код первого значащего разряда мантиссы частного. При получении первого значащего разряда мантиссы частного, равного 1 или -1, дешифратор 16 по синхронизирующему сигналу выдает сигнал логической единицы на своем пер- вом выходе, устанавливая триггер 17 в единичное состояние.Порядок частного с выходов сумматора 25 запоминается в регистре 24 по сигналу логической единицы с единичного выхо- да триггера 17. Далее, как и при обработке нормализованных мантисс исходных операндов, осуществляется вычисление и поразрядная выдача через выходы 19 и 2(1 остальных разрядов мантиссы частного.

При делении устройством как нормализованных, так и ненормализованных исходных операндов, для представления мантисс которых используется избыточная двоичная система счисления с цифрами 1,0 и -1 (цифры системы счисления меньше ее основания), мантисса частного также представляется в избыточной двоичной системе. Поэтому знаком мантиссы частного является знак первого старшего значащего разряда, так как он обладает набольшим весом Т и в отличие от други разрядов мантиссы частного сохраняет ее знак.

Предлагаемое устройство позволяет выполнять операцию деления в тех случаях, когда исходные операнды нормализованы, исходные операнды ненор- мализованы, один либо оба исходных операнда равны нулю.

Формула изобретения

Устройство для деления чисел в форме с плавающей запятой, содержащее блок деления, сумматор порядков, первый дешифратор, триггер, регистр управления, элемент ИЛИ, счетчик нормализации, сумматор нормализации, блок сравнения, регистр порядка частного и первый регистр мантиссы дели

г 0 5

0 о

5

5

0

.

О12

мого, причем входы порядков делимого и делителя устройства соединены с первой и второй группами входов сумматора порядков соответственно, выходы счетчика нормализации соединены с первыми информационными входами сумматора нормализации, выходы которого соединены с информационными входами блока сравнения и регистра порядка частного, выходы которого являются выходами порядка частного yci- ройства, первый и второй входы мантиссы делителя устройства соединены с первым и вторым входами делителя соответственно блока деления, выходы которого соединены с выходами мантиссы частного устройства и входами первого дешифратора, первый выход которого соединен с входом установки я 1 триггера, прямой выход которого соединен с входом разрешения записи регистра порядка частного и входом установки в Г1 младшего разряда регистра управления, выход старшего разряда которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом блока сравнения, выходы сумматора порядков соединены с вторыми информационными входами сумматора нормализации, вход синхронизации устройства соединен с управляющим входом первого дешифратора и входом разрешения сдвига регистра управления, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет деления ненормализованных исходных операндов и повышения достоверности вычисляемых результатов, в него введены два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй регистр мантиссы делимого, два коммутатора, распределитель импульсов, второй дешифратор, триггеры делимого и делителя, счетчик разрядов мантиссы, счетчик и элемент И, выход которого соединен с суммирующим входом счетчика нормализации, вычитающий вход которого соединен с первым входом второго дешифратора и счетным входом счетчика, информационные выходы ко- . торого соединены с управляющими входами первого и второго коммутаторов, выходы которых соединены с первым и вторым входами делимого блока деления, первый вход мантиссы делимого устройства соединен с входом последовательного ввода первого регистра мантиссы делимого и первым входом первого эле

131S

мента ИСКЛЮЧАМИКК ИЛИ, второй вход которого соединен с вторым входом мантиссы делимого устройства и входом последовательного ппода второго регистра мантиссы делимого, выходы раз- рядов первого и второго регистров мантиссы делимого соединены г информационными входами первого и второго коммутаторов соответственно, первый и второй входы мантиссы делителя соединены с первым и вторым входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом установки в 1 триггера делителя, инверсный выход которого соединен с первыми входами элемента И и второго дешифратора, второй вход которого соединен с выходом триггера делимого, вход установки в 1 которого соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй выход второго дешифратора соединен со счетным входом

0

5

.О14

счетчики разрядов мантиссы, выход переполнения котброго соединен с тр гъ- iw входом элемента ИЛИ, четвертый вход которого соединен с выходом переполнения счетчика, выход элемента ИЛИ соединен с выходом сигнала конца операции устройства, второй выход первого дешифратора соединен с вторым входом элемента И, первый выход распределителя импульсов соединен с входом разрешения приема делителя блока деления, вход разрешения приема делимого блока деления соединен с вторым выходом распределителя импульсов, третий выход которого соединен с входом выделения частного блока деления, вход синхронизации устройства соединен с входами разрешения сдвига первого и второго регистров мантиссы делимого, управляющим входом второго дешифратора и запускающим входом распределителя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СТРАНИЧНЫЙ ДЕЛИТЕЛЬ С ПЛАВАЮЩЕЙ ТОЧКОЙ | 1998 |

|

RU2130639C1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления | 1976 |

|

SU590738A1 |

| Устройство для деления с плавающей запятой | 1979 |

|

SU860063A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и системах управления, в которых применяется поразрядная передача операндов. Цель изобретения - расширение функциональных возможностей устройства за счет деления ненормализованных исходных операндов и повышения достоверности вычисляемых результатов. Устройство выполняет операцию деления как с нормализованными, так и с ненормализованными числами в форме с плавающей запятой, мантиссы которых формируются вне устройства, например в преобразователях поразрядного уравновешивания, и поступают последовательно старшими разрядами вперед на входы устройства, чем обеспечивается достижение поставленной цели. Изобретение также позволяет совмещать во времени процессы поразрядного ввода и вычисления частного, вследствие чего значительно экономится время на получение результата операции деления чисел. Устройство содержит блок деления, сумматор порядков, два дешифратора, триггер, регистр управления, элемент ИЛИ, счетчик нормализации, сумматор нормализации, блок сравнения, регистр порядка частного, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, два регистра мантиссы делимого, два коммутатора, распределитель импульсов, триггер делимого, триггер делителя, счетчик разрядов мантиссы, счетчик и элемент И , которые соединены между собой соответствующим образом. 1 ил.

&ц

| Авторское свидетельство СССР Г,- 662938, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-23—Публикация

1988-07-29—Подача