Устройство относится к систеяам обработки случайных процессов и может быть использовано в системах диагностики технического состояния подвижных динамических объектов.

Известно устройство для цифровой фильтрации Г} .

Недостатками известного устройства являются низкое быстродействие и большое количество оборудования.

Известно также устройство для цифровой фильтрации, содержащее -входной регистр, (2п+2) блока умножения, блок формирования эталонного сигнала, первый накапливающий сумматор, два блока памяти, сумматор, п квадраторов, второй накапливающий сумматор и усилитель 2 .

Однако устройство обеспечивает недостаточное быстродействие, т.е. сходимость весовых коэффициентов к оптимальным значениям даже для устройства, реализующего метод самонастройки Ньютона-Рафсона, невелика. Особенно это заметно при обработке высокочастотных сигналов, когда значительно возрастает ошибка запаздывания в сложений за изменением весовых коэффициентов.

Цель изобретения - повышение оыстродействия.

Поставленная цель достигается тем, что в устройство для адаптивной цифровой фильтрации, содержащее m квадраторов, первый регистр, (2т+2) умножителей, блок формирования эталонного сигнала,, первый и второй накапливаклцие сумматоры,

10 два блока памяти, сумматор, усилитель, причем выход k-ro (,m) квадратора соединен с первым входом сумматора, выход которого подключен к первому входу (2т+1)-го умножите15ля, выход которого .соединен с первым входом k-ro (,2m) умножителя, выходы первого влока памяти под- ; ключены к первому входы k-ro (,m) умножителя, выход которого

20 соединен с k-м входом первого накапливающего сумматора, выход которого соединен с вторым входом сумматора и является выходом устройства, выхол второго блока памяти соединен с

25 первым входом (2т+2)-го умножителя, выход k-ro квадратора подключен к k-.iy входу второго накапливакяцего сумматора, выход которого соединен с входом усилителя, выход которого

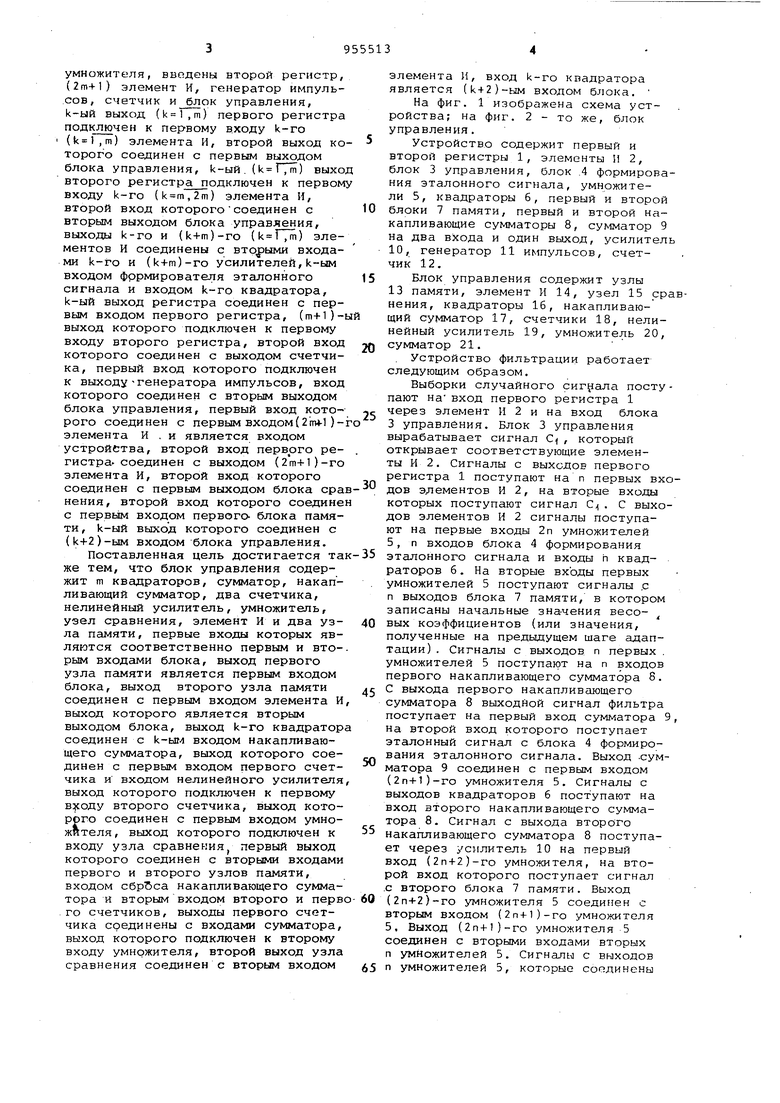

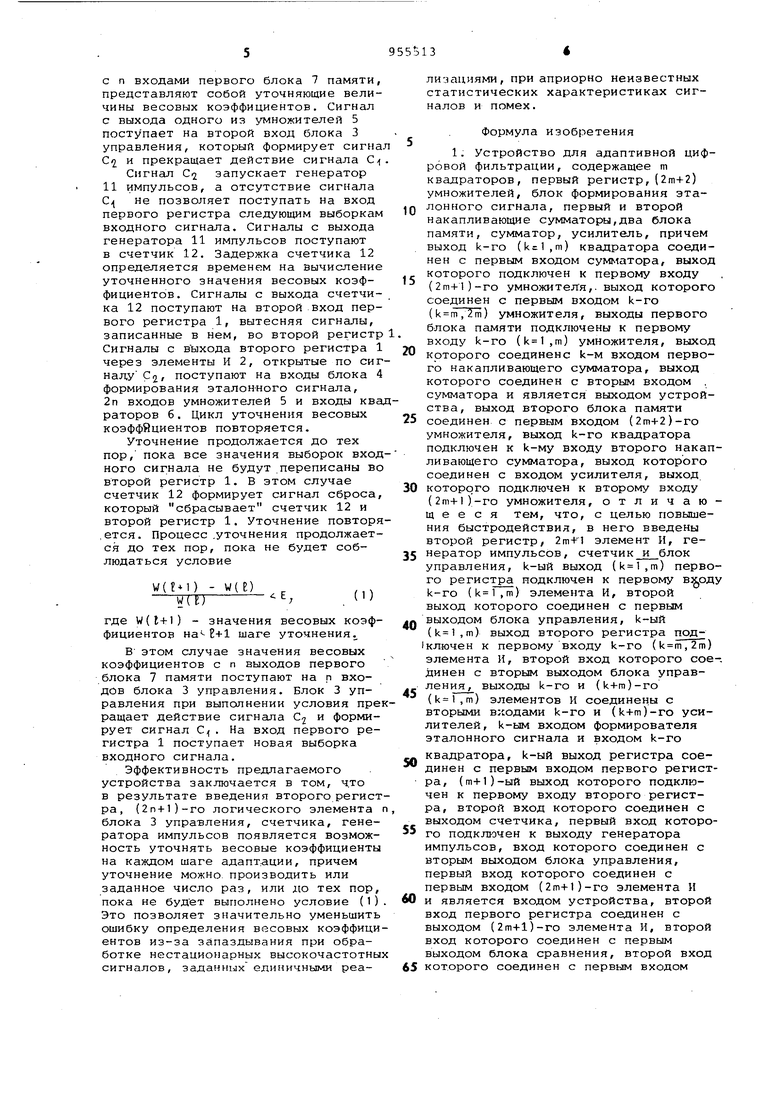

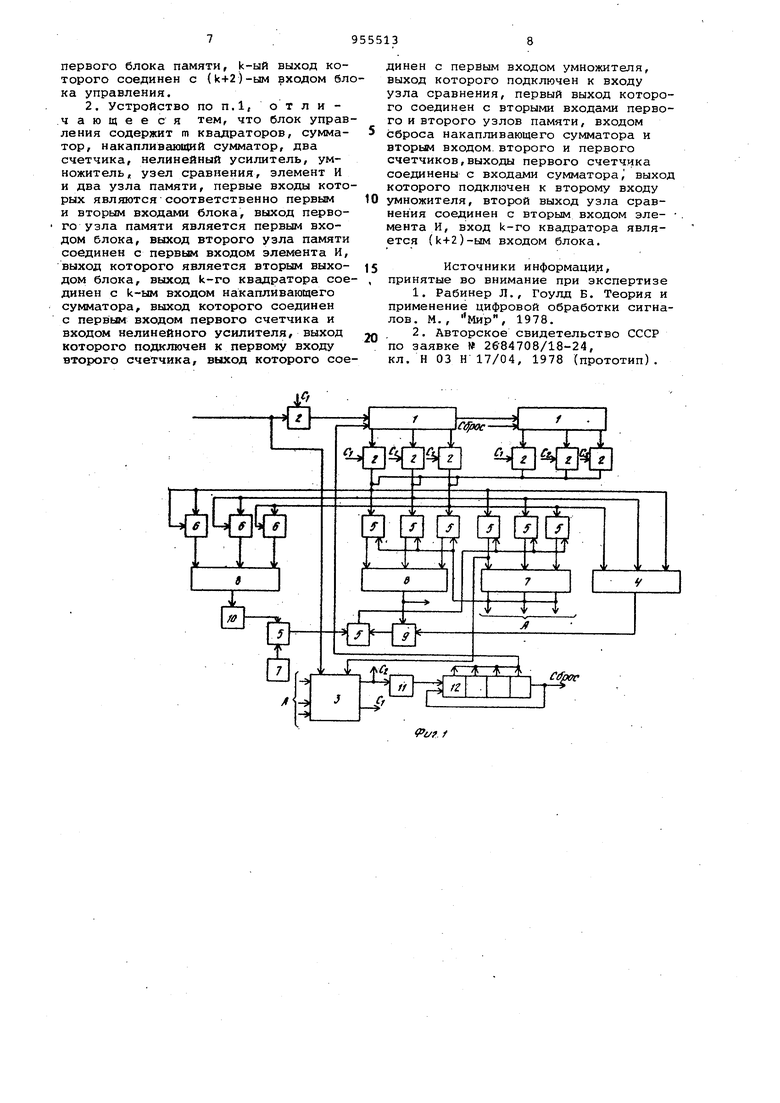

30 подк.лючен к второму входу {2т4-1)-го умножителя, введены второй регистр, (2m-fl) элемент И, генератор импульсов, счетчик управления, k-ый выход (,m) первого регистра подключен к первому в.ходу k-ro (,m) элемента И, второй выход ко торого соединен с первым выходом блока управления, k-ый. ( ,т) выхо второго регистра подключен к первом входу k-ro (,2m) элемента Н, второй вход которого соединен с вторым выходом блока управления, выходы k-ro и (k+m)-ro (k 1 ,m) элементов И соединены с вторыми входами k-ro и (k+m)-ro усилителей,k-ым входом фррмирователя эталонного сигнала и входом k-ro квадратора, k-ый выход регистра соединен с первым входом первого регистра, (т+1)выход которого подключен к первому входу второго регистра, второй вход которого соединен с выходом счетчика, первый вход которого подключен к выходуГенератора импульсов, вход которого соединен с вторым выходом блока управления, первый вход которого соединен с первым входом( )элемента И . и является входом устройства, второй вход первого регистра- соединен с выходом (2т-И)-го элемента И, второй вход которого соединен с первым выходом блока сра нения, второй вход которого соедине с первЕлм входом первого- блока памяти , k-ый выход которого соединен с (k+2)-biM входом блока управления. Поставленная цель достигается та же тем, что блок управления содержит m квадраторов, сумматор, накапливающий сумматор, два счетчика, нелинейный усилитель, умножитель, узел сравнения, элемент И и два узла памяти, первые входы которых являются соответственно первым и вторым входами блока, выход первого узла памяти является первым входом блока, выход второго узла памяти соединен с первым входом элемента И выход которого является вторым выходом блока, выход k-ro квадратор соединен с k-ым входом накапливающего сумматора, ВЕЛХОД которого соединен с первым входом первого счетчика и входом нелинейного усилителя выход которого подключен к первому ВХОДУ второго счетчика, выход которого соединен с первым входом умножителя , выход которого подключен к входу узла сравненияJ первый выход которого соединен с вторыми входами первого и второго узлов памяти, входом сбрСса накапливающего сумматора и вторым входом второго и перв го счетчиков, выходы первого счетчика соединены с входами сумматора, выход которого подключен к второму входу умножителя, второй выход узла сравнения соединен с вторым входом элемента И, вход k-ro квадратора является (k42)-biM входом блока. На фиг. 1 изображена схема устройства; на фиг. 2 - то же, блок управления. Устройство содержит первый и второй регистры 1, элементы 1 2, блок 3 управления, блок .4 формирования эталонного сигнала, умножители 5, квадраторы б, первый и второй блоки 7 памяти, первый и второй накапливающие сумматоры 8, сумматор 9 на два входа и один выход, усилитель 10, генератор 11 импульсов, счетчик 12. Блок управления содержит узлы 13 памяти, элемент И 14, узел 15 сравнения, квадраторы 16, накапливающий сумматор 17, счетчики 18, нелинейный усилитель 19, умножитель 20, сумматор 21, , Устройство фильтрации работает следующим обр а 3 ом. Выборки случайного сигнала посту пают на вход первого регистра 1 через элемент Н 2 и на вход блока 3 управления. Блок 3 управления вырабатывает сигнал С( , который открывает соответствующие элементы И 2. Сигналы с выходов первого регистра 1 поступают на п первых входов элементов И 2, на вторые входы которых поступают сигнал С. С выходов элементов И 2 сигналы поступают на первые входы 2п умножителей 5, п входов блока 4 формирования эталонного сигнала и входы h квадраторов б. На вторые входы первых умножителей 5 поступают сигналы .с п выходов блока 7 памяти, в котором записаны начальные значения весовых коэффициентов (или значения, полученные на предыдущем шаге адаптации) . Сигналы с выходов п первых . умножителей 5 поступают на п входов первого накапливающего сумматора 8. С выхода первого накапливающего сумматора 8 выходной сигнал фильтра поступает на первый вход сумматора 9, на второй вход которого поступает эталонный сигнал с блока 4 формирования эталонного сигнала. Выход -сумматора 9 соединен с первым входом (2п+1)-го умножителя 5. Сигналы с выходов квадраторов б поступают на вход второго накапливающего сумматора 8. Сигнал с выхода второго накапливающего сумматора В поступает через усилитель 10 на первый вход (2п+2)-го умножителя, на второй вход которого поступает сигнал .с второго блока 7 памяти. Выход (2п+2)-го умножителя 5 соединен с вторым входом (2п+1)-го умножителя 5. Выход (2п+)-го умножителя 5 соединен с вторыми входами вторых п умножителей 5. Сигналы с выходов п умножителей 5, которые соединены с n входами первого блока 7 памяти представляют собой уточняющие величины весовых коэффициентов. Сигнал с выхода одного из умножителей 5 поступает на второй вход блока 3 управления, который формирует сигна С и прекращает действие сигнала С Сигнал С запускает генератор 11 импульсов, а отсутствие сигнала С не позволяет поступать на вход первого регистра следующим выборкам входного сигнала. Сигналы с выхода генератора 11 импульсов поступают в счетчик 12, Задержка счетчика 12 определяется временем на вычисление уточненного значения весовых коэффициентов. Сигналы с выхода счетчика 12 поступают на второй вход первого регистра 1, вытесняя сигналы, записанные в нем, во второй регистр Сигналы с выхода второго регистра 1 через элементы И 2, открытые по сиг HanyCrj, поступают на входы блока 4 формирования эталон-ного сигнала, 2п входов умножителей 5 и входы ква раторов 6. Цикл уточнения весовых коэффЯциентов повторяется. Уточнение продолжается до тех пор, пока все значения выборок вход ного сигнала не будут переписаны во второй регистр 1. В этом случае счетчик 12 формирует сигнал сброса который сбрасывает счетчик 12 и второй регистр 1. Уточнение повторя ,ется. Процесс .уточнения продолжается до тех пор, пока не будет соблюдаться условие W(b1) - W(E) WTEl где W(l+1) - значения весовых коэффициентов на Е+1 шаге уточнения. В этом случае значения весовых коэффициентов с п выходов первого блока 7 памяти поступают на п входов блока 3 управления. Блок 3 управления при выполнении условия пре ращает действие сигнала С и формирует сигнал Сц . На вход первого регистра 1 поступает новая выборка входного сигнала. Эффективность предлагаемого устройства заключается в том, ч.то в результате введения второго регист ра, (2п+1)-го логического элемента блока 3 управления, счетчика, генератора импульсов появляется возможность уточнять весовые коэффициенты на каждом шаге адаптдции, причем уточнение можно производить или заданное число раз, или до тех пор, пока не будет выполнено условие (1 ) Это позволяет значительно уменьшить ошибку определения весовых коэффици ентов из-за запаздывания при обработке нестационарных высокочастотны сигналов, заданных единичными реализациями, при априорно неизвестных статистических характеристиках сигналов и помех. Формула изобретения 1. Устройство для адаптивной цифровой фильтрации, содержащее m квадраторов, первый регистр,(2т+2) умножителей, блок формирования эталонного сигнала, первый и второй накапливающие сумматоры,два блока памяти, сумматор, усилитель, причем выход k-ro (,m) квадратора соединен с первым входом сумматора, выход которого подключен к первому входу (2т+1)-го умножителя,. выход которого соединен с первым входом k-ro (k m, 21т|) умножителя, выходы первого блока памяти подключены к первому входу k-ro (,m) умножителя, выход которого соединено k-м входом первого накапливающего сумматора, выход которого соединен с вторым входом . сумматора и является выходом устройства, выход второго блока памяти соединен с первым входом (2т+2)-го умножителя, выход k-ro квадратора подключен к k-му входу второго накапливающего сумматора, выход которого соединен с входом усилителя, выход которого подключен к второму входу (2п1+1)-го умножителя, отличающееся тем, что, с целью повышения быстродействия, в него введены второй регистр/ 2m+I элемент И, генератор импульсов, счетчик и блок управления, k-ый выход ,m) первого регистра подключен к первому в:,оду k-ro (,m) элемента И, второй выход которого соединен с первым выходом блока управления, k-ый (,ni) выход второго регистра подключен к первому входу k-ro (,2m) элемента И, второй вход которого сое-. динен с вторым выходом блока управления, выходы k-ro и (k+m)-ro (k),m) элементов И соединены с вторыми входами k-ro и (k+m)-ro усилителей, k-ым входом формирователя эталонного сигнала и входом k-ro квадратора, k-ый выход регистра соединен с первым входом первого регистра, (т+1)-ый выход которого подключен к первому входу второго регистра, второй вход которого соединен с выходом счетчика, первый вход которого подключен к выходу генератора импульсов, вход которого соединен с вторым выходом блока управления, первый вход; которого соединен с первым входом (2т+1)-го элемента И и является входом устройства, второй вход первого регистра соединен с выходом (2т+1)-го элемента И, второй вход которого соединен с первым выходом блока сравнения, второй вход которого соединен с первым входом

первого блока памяти, k-ый выход которого соединен с {k+2)-uM входом блока управления.

2. Устройство ПОП.1, отли.чающееся тем, что блок управления содержит m квадраторов, сумматор, накапливающий сумматор, два счетчика, нелинейный усилитель, умножитель, узел сравнения, элемент И и два узла памяти, первые входы которых являются соответственно первым и вторым входами блока, выход первого узла памяти является первым входом блока, выход второго узла памяти соединен с первым входом элемента И, выход которого является вторым выходом блока, выход k-ro квадратора соединен с k-ым входом накапливающего сумматора, выход которого соединен с первым входом первого счетчика и входом нелинейного усилителя, выход которого подключен к первому входу второго счетчика, выход которого соединен с первым входом умножителя, выход которого подключен к входу узла сравнения, первый выход которого соединен с вторыми входами первого и второго узлов памяти, входом

сброса накапливающего сумматора и вторым входом, второго и первого счетчиков,выходы первого счетчика соединены с входами сумматора, выход которого подключен к второму входу

умножителя, второй выход узла сравнения соединен с вторым входом эле- мента И, вход k-ro квадратора является )-ым входом блока.

Источники информации, принятые во внимание при экспертизе

1.Рабинер Л., Гоулд Б. Теория и применение цифровой обработки сигналов, М. , МИР, 1978.

2.Авторское свидетельство СССР по заявке 26-84708/18-24,

кл. Н 03 Н 17/04, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой фильтрации | 1983 |

|

SU1113884A2 |

| Устройство для цифровой фильтрации | 1981 |

|

SU957416A1 |

| Устройство для решения систем алгебраических уравнений | 1983 |

|

SU1226427A1 |

| Устройство для решения систем алгебраических уравнений | 1984 |

|

SU1203552A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Анализатор спектра | 1989 |

|

SU1651226A1 |

| Адаптивная диагностическая система | 1987 |

|

SU1441350A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Адаптивный измеритель параметров сигнала | 1981 |

|

SU970251A1 |

| Устройство для автоматического регулирования частоты и перетоков мощности энергообъединения | 1982 |

|

SU1070641A1 |

Авторы

Даты

1982-08-30—Публикация

1980-04-14—Подача