-ч

7.1

ш

i

-1

j j

т

ж;

f АВ Н,

../

j

- --ij-f

тп

А

Li

-

MtW

5j

л

.

Л

гJS

6j

Фие.1

w

Hj

fj

:

5//

lOj

г

&tf

i

р

Ш

ПН

Сд

00

9) 1 4

Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах передачи информации.

Цель изобретения - повышение помехоустойчивости устройства и точность декодирования.

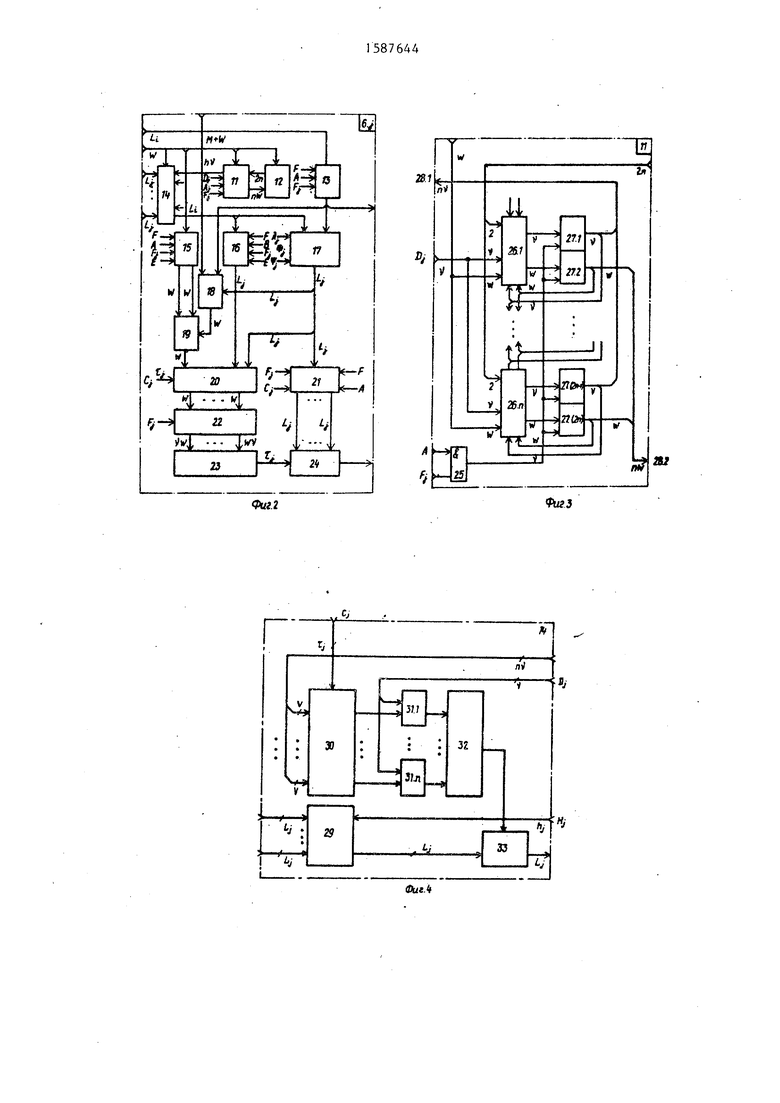

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - блок-схема декодера внешнего кода; фиг. 3-10 - соответственно блок , о чередности стираний, блок ввода сти- , блок декод1фования, блок вы15876444

памяти, блок 22 суммирования, блок 23 выбора номера минимального числа и мультиплексор 24.

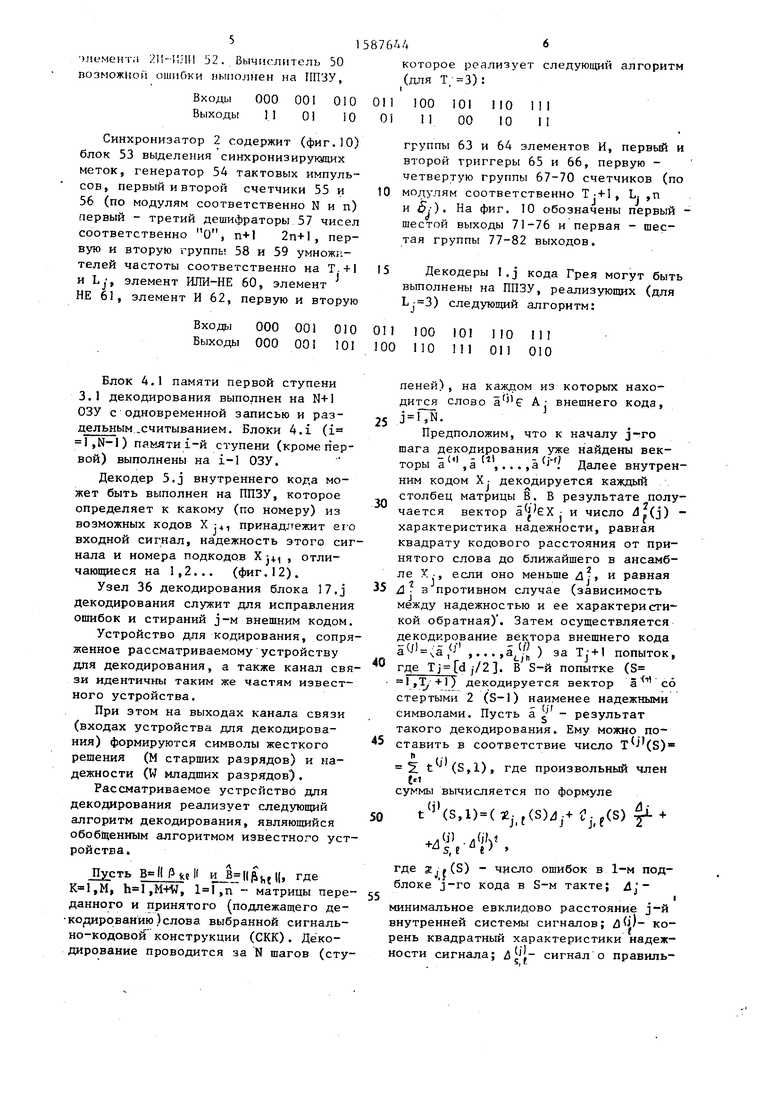

Блок 11 очередности стираний содержит (фиг.З) элемент И 25, коммутаторы 26 и буферные регистры 27. На фиг.З обозначены выходы 28.

Блок 12 анализа стираний представляет собой набор элементов сравнения, каждый из которых имеет выходы Боль10

ше или равно и Меньше.

Блок 13 памяти жестких символов, а также блок 15 памяти надежностей.

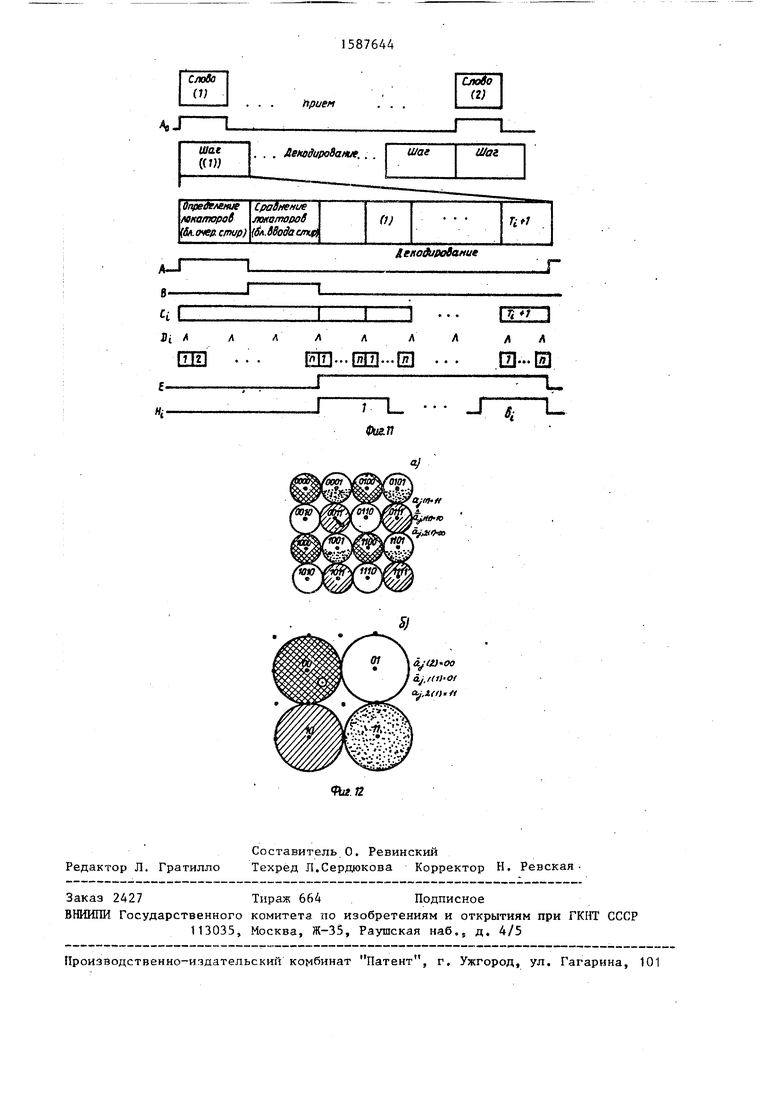

числения параметров декодирования, на-, блок 16 памяти стираний и блок 21 опе- к апливающего сумматора, блок выбора HJoMepa минимального числа, компара- ilopa и синхронизатора соответственно; на фиг. 11 - временная диаграмма Йаботы устройства; на фиг.12 - про- (JTpaHCTBO сигналов внутреннего деко-j |ирования иа первом (а) и втором (б) njarax (Р - принятый сигнал; NJ- надежность) .

20

30

ративной памяти выполнены на оперативных запоминающих устройствах (ОЗУ).

Блок 14 ввода стираний содержит (фиг.4) первый и второй коммутаторы 29 и 30, элементы 31 равнозначности, элемент ИЛИ 32 и элемент 33 неравнозначности.

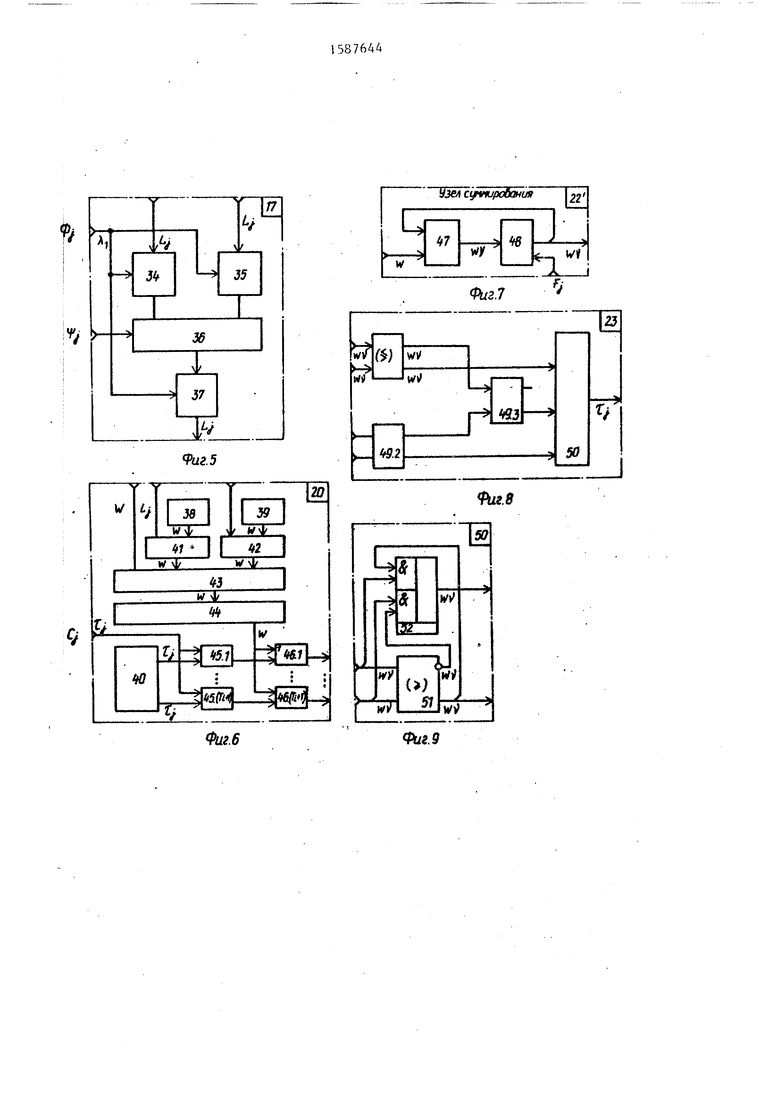

Блок 15 декодирования содержит (фиг.5) первый и второй мультиплексоры 34 и 35, узел 36 декодирования и демультиплексор 37.

Блок 18 контроля выполнен на программируемом постоянном запоми , нающем ycTpoJicTae (ПИЗУ) и реализует следующий алгоритм для комплексных чисел а,Ь,с;

; Г U f(a,c) 5 (a-,b);. 1о, если J)(а,с) (а,Ь) . . где р(а,Ь) - расстояние-на комплексной плоскости между числами а и Ь.

Блок 20 вычисления параметров декодирования содержит (фиг.6) первый - третий источники 38-40 постоянLj - разрядность симво- Q ного кода, первый и второй перемножители 41 и 42, сумматор 43, квадратор 44, элементы 45 равнозначности и элементы ИЛИ 46.

Источники 38 и 39 генерируют постоянные коды чисел соответственно Л-/2 и i3 ( 4 j минимальное евклидово расстояние j-й внутренней системт т сигналов),- источник 40 генерирует коды чисел l,2,,..,Tj+l.

Блок 22 суммирования состоит из однотипных накапливаю1цих сумматоров, каждый из которых содержит Сфиг.7} cy мaтop 47 и буферный регистр 48.

Блок 23 выбора номера минимально35

25

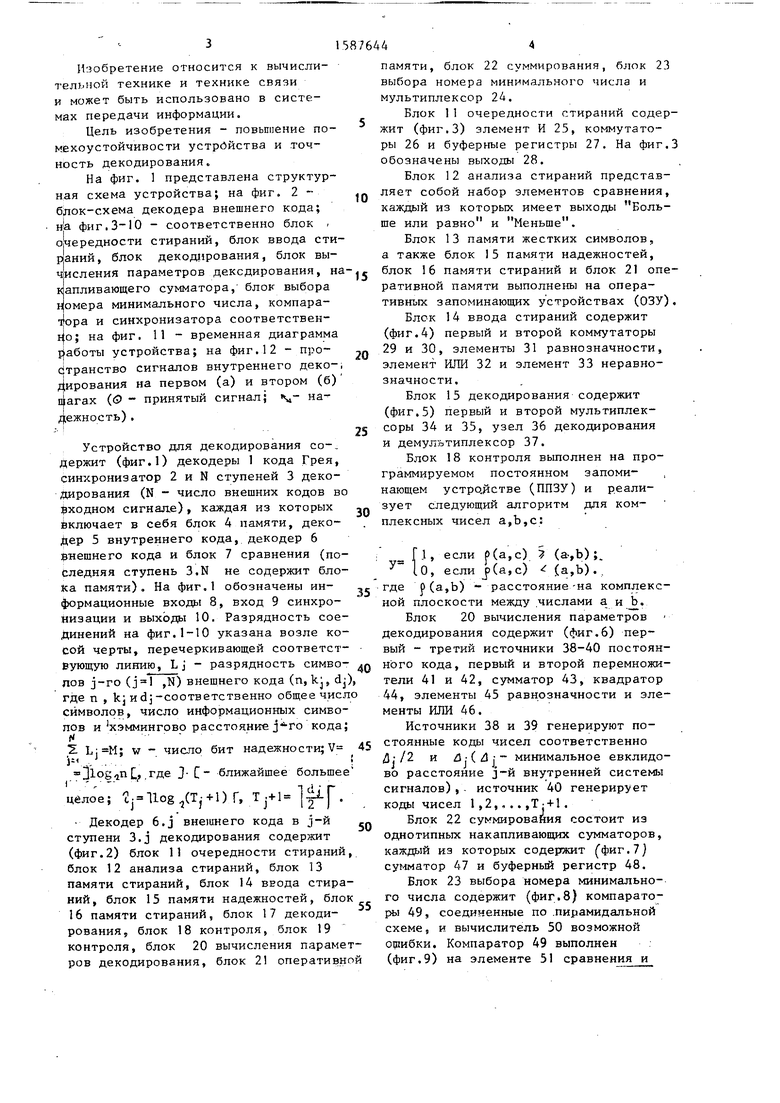

Устройство для декодирования со- держит (фиг.1) декодеры 1 кода Грея, синхронизатор 2 и N ступеней 3 декодирования (N - число внещних кодов во йходном сигнал.е), каждая из которых включает в себя блок 4 памяти, декодер 5 внутреннего кода, декодер 6 Внешнего кода и блок 7 сравнения (последняя ступень 3.N не содержит блока памяти). На фиг.1 обозначены информационные входы 8, вход 9 синхронизации и выходы 10. Разрядность соединений на фиг.1-10 указана возле косой черты, перечеркивающей соответствующую линию,

лов j-ro ( ,N) внешнего кода (п, kj, dj), где п , k; и dj-соответственно общее число символов, число информационных символов и хэммингово расстояние кода;

W - число бит надежности; V 45

il f

V......

1log/,nL, ,где J- C ближайшее большее

, f . . . f

целое; Cj llog .,(1,-+1) Г, Т j+l i- .

Декодер 6.j внешнего кода в j-й ступени 3.J декодирования содержит (фиг.2) блок 11 очередности стираний, блок 12 анализа стираний, блок 13 памяти стираний, блок 14 ввода стира50

НИИ, блок 15 памяти надежностей, блок го числа содержит (фиг.З) компарато16 памяти стираний, блок 17 декодирования, блок 18 контроля, блок 19 контроля, блок 20 вычисления параметров декодирования, блок 2 оперативной

ры 49, соединенные по .пирамидальной схеме, и вычислитель 50 возможной ощибки. Компаратор 49 выполнен (фиг.9) на элементе 51 сравнения и

ше или равно и Меньше.

Блок 13 памяти жестких символов, а также блок 15 памяти надежностей.

го числа содержит (фиг.З) компараторы 49, соединенные по .пирамидальной схеме, и вычислитель 50 возможной ощибки. Компаратор 49 выполнен (фиг.9) на элементе 51 сравнения и

элемент.- 2 -i;jIII 32. Вычислитель 50 ВОЗМОЖНО ошибки ныполнен на ППЗУ,

Входы 000 001 010 Выходы II 01 10

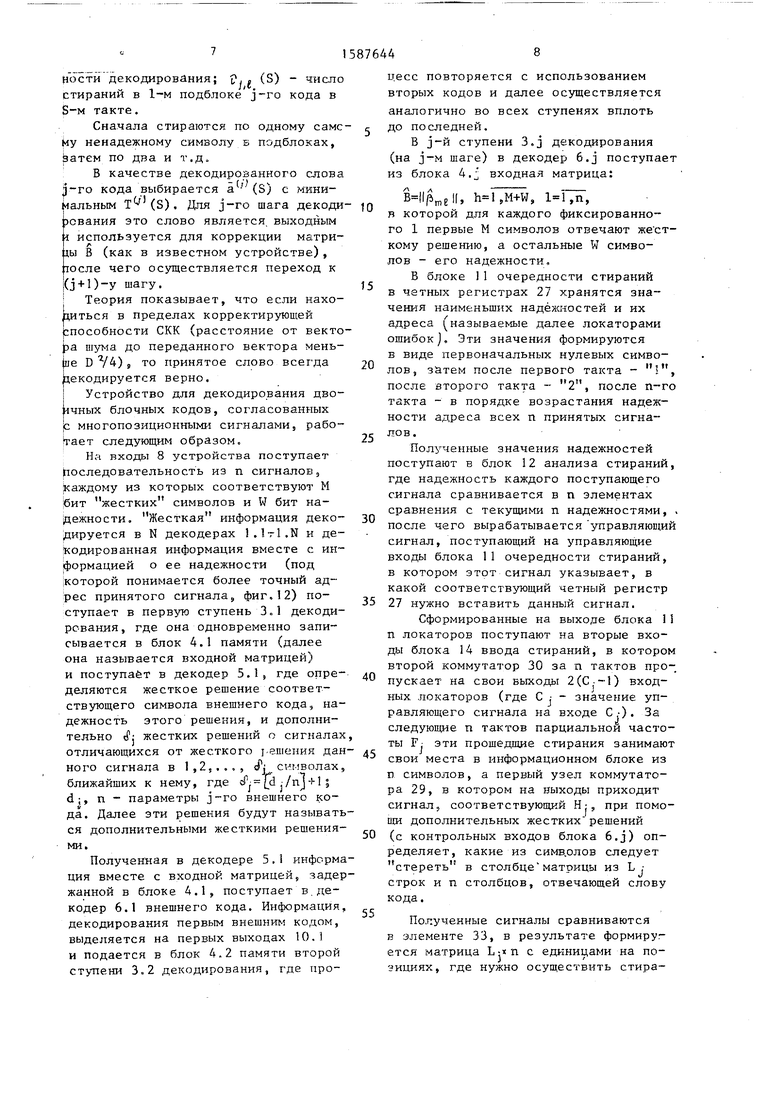

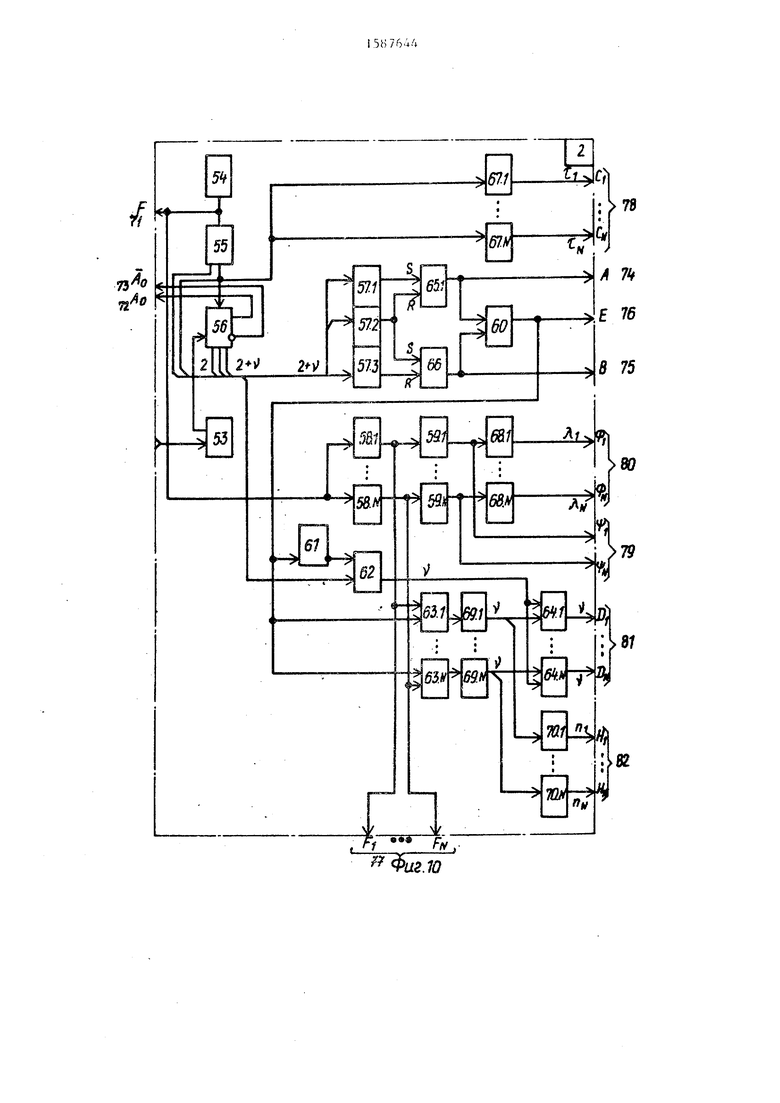

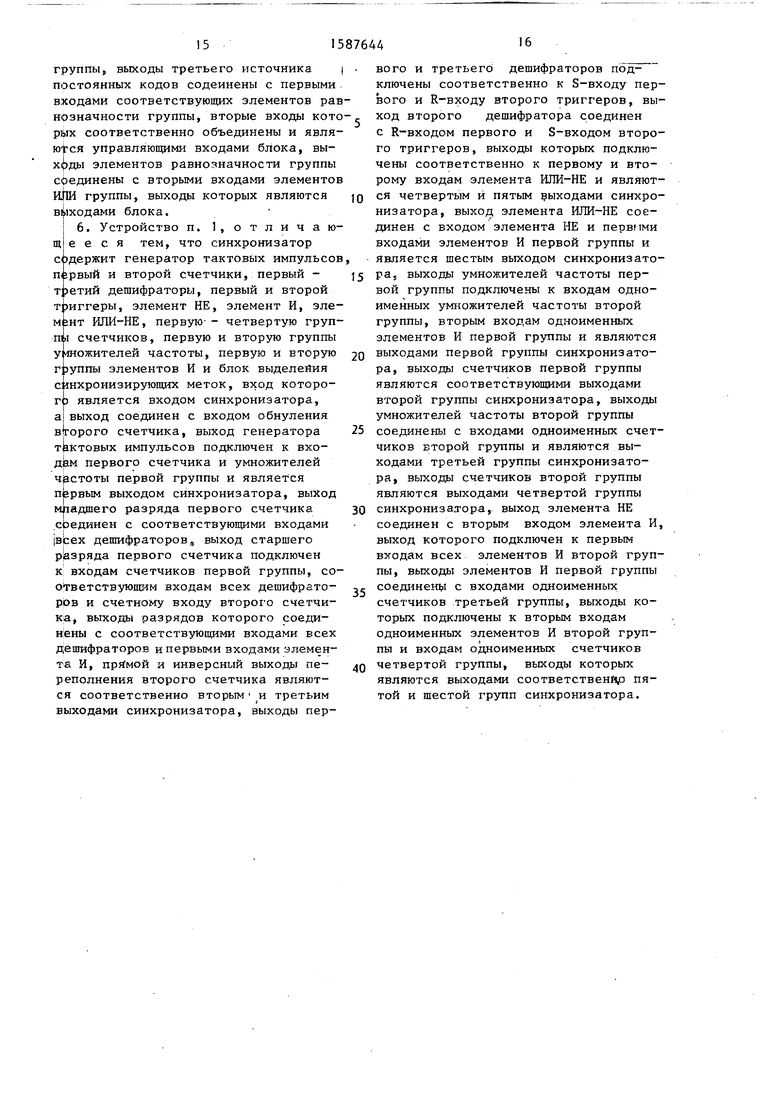

Синхронизатор 2 содержит (фиг.10) блок 53 выделения синхронизирукзщих меток, генератор 54 тактовых импульсов, первый и второй счетчики 55 и 56 (по модулям соответственно N и п) первый - третий дешифраторы 57 чисел соответственно О, п+1 2п+1, первую и вторую группы 58 и 59 умножителей частоты соответственно на T.+l и Ly, элемент ИЛИ-НЕ 60, элемент НЕ 61, элемент И 62, первую и вторую

Входы 000 001 010 Выходы 000 001 101

Блок 4.1 памяти первой ступени 3.1 декодирования выполнен на N+1 ОЗУ с одновременной записью и раз- дельным .считыванием. Блоки 4.1 ( 1,N-1) памяти i-й ступени (кроме первой) выполнены на i-1 ОЗУ.

Декодер 5.J внутреннего кода может быть выполнен на ППЗУ, которое определяет к какому (по номеру) из возможных кодов X -41 принадлежит его входной сигнал, надежность этого сигнала и номера подкодов X j., , отличающиеся на 1,2.., (фиг.12).

Узел 36 декодирования блока 17.J декодирования служит для исправления ошибок и стираний j-м внешним кодом.

Устройство для кодирования, сопряженное рассматриваемому устройству для декодирования, а также канал связи идентичны таким же частям известного устройства.

При этом на выходах канала связи (входах устройства для декодирования) формируются символы жесткого решения (М старших разрядов) и надежности (W младших разрядов) ,

Рассматриваемое устройство для декодирования реализует следующий алгоритм декодирования, являющийся обобщенным алгоритмом известного устройства

B ji P fcjl . 1),{|(, где 1,М, ,M+W, ,п - матрицы переанного и принятого (подлежащего де- о рованию) слова выбранной сигналь- о-кодавой конструкции (СКК). Декоирование проводится за N шагов (сту15876Л4

которое реализует следующий алгоритм (для ):

100

11

101 00

по 111 10 1 I

группы 63 и 64 элементов И, первый и второй триггеры 65 и 66, первую - четвертую группы 67-70 счетчиков (по модулям соответственно Т + , L, ,п

и ej) На фиг. 10 обозначены первый - шестой выходы 71-76 и первая - шестая группы 77-82 выходов.

Декодеры I.j кода Грея могут быть вьтолнены на ППЗУ, реализующих (для

Lj-3) следующий алгоритм:

100 110

101 111

10

01

I 1 I 010

пеней), на каждом из которых нахо- ди гся слово А; внешнего кода,

J NПредположим, что к началу j-ro

шага декодирования уже найдены векторы а , i ,. .. , Далее внутренним кодом Xj декодируется каждый столбец матрицы В. В результате получается вектор и число 4(j) - характеристика надежности, равная квадрату кодового расстояния от принятого слова до ближайшего в ансамбле Х-, если оно меньше л и равная . 3 противном случае (зависимость между надежностью и ее характеристикой обратная). Затем осуществляется декодирование вектора внешнего кода

ча/-| a jl ) за Tj + 1 попыток,

где ,723. В S-й попытке (S 1 +1) декодируется вектор а со стертыми 2 (S-1) наименее надежными символами. Пусть а - результат такого декодирования. Ему можно поставить в соответствие число (S) п ...

2 t (S,l), где произвольный член t l

суммы вычисляется по формуле

(s,i)(«. .(s)j.+ i: (s) ji- + ji t j ji t /

+A

(J) .дО Кг s, e e

55

где Zj{(S) - число ошибок в 1-м подблоке j-ro кода в S-M такте; Л, минимальное евклидово расстояние j-и внутренней системы сигналов; дО)- корень квадратный характеристики надежности сигнала; сигнал о правильности декодирования; р, . (S) - число стираний в 1-м подблоке j-ro кода в S-M такте.

Сначала стираются по одному самс My ненадежному символу Б подблоках, эатем по два и т.д

В качестве декодированного слова j-ro кода выбирается а (S) с мини- Йальным Т (S), /Для j-ro шага декоди эования это слово является, выходньсм л используется для коррекции матри- ды в (как в известном устройстве), лосле чего осуществляется переход к |(j + l)-y шагу.

I Теория показывает, что если находиться в пределах корректирующей Способности СКК (расстояние от векто JDa шума до переданного вектора мень- jue D V4) 5 то принятое слово всег да Декодируется верно.

I Устройство для декодирования двоичных блочных кодов, согласованных многопозиционными сигналами, рабо- rt aer следующим образом.

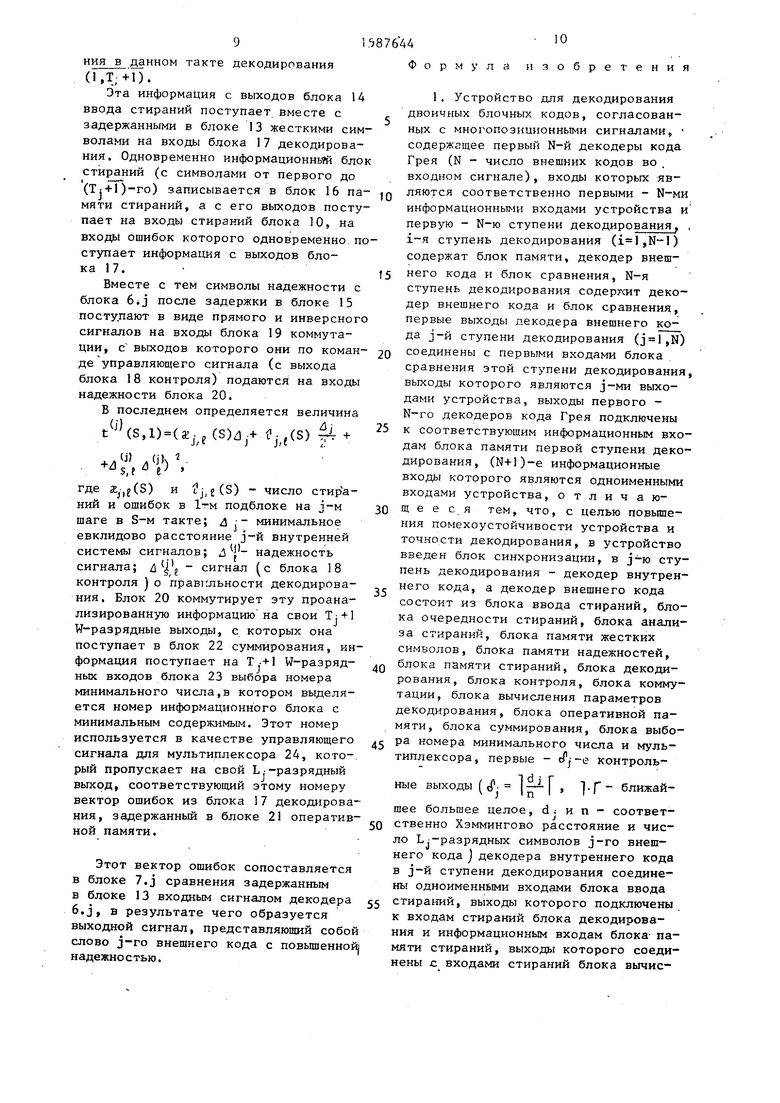

На входы 8 устройства поступает последовательность из п сигналов, каждому из которых соответствуют М Ьит жестких символов и W бит надежности. Жесткая информация деко- дируется в N декодерах l.l-rl.N и декодированная информация вместе с информацией о ее надежности (под |которой понимается более точный адрес принятого сигнала, фиг,12) по- ступает в первую ступень 3.1 декодирования, где она одновременно записывается в блок 4.1 памяти (далее она называется входной матрицей) и поступает в декодер 5.1, где опре- деляются жесткое решение соответствующего символа внешнего кода, надежность этого решения, и дополнительно rf: жестких решений о сигналах отличающихся от жесткого т.ешения дан ного сигнала в 1,2,..., / ; символах, ближайших к нему, где j/nj + l ; dj, n - параметры j-ro внешнего кода. Далее эти решения будут называться дополнительными жесткими решения- ми.

Полученная в декодере 5,1 информация вместе с входной матрицей, задержанной в блоке 4.1, поступает в. декодер 6.1 внешнего кода. Информация, декодирования первым внешним кодом, выделяется на первых выходах 10.1 и подается в блок 4.2 памяти второй ступени 3.2 декодирования, где процесс повторяется с использованием вторых кодов и далее осуществляется аналогично во всех ступенях вплоть до последней.

В j-й ступени 3.J декодирования (на J-M шаге) в декодер 6.J поступает из блока 4.J входная матрица:

(, ,M+W, ,n, в которой для каждого фиксированного 1 первые М символов отвечают же ст кому решению, а остальные W символов - его надежности,

В блоке 11 очередности стираний в четных регистрах 27 хранятся значения наименьших надёжноетей и их адреса (называемые далее локаторами ошибок. Эти значения формируются в виде первоначальных нулевых символов, затем после первого такта - . после второго такта - 2, после п-г такта - в порядке возрастания надежности адреса всех п принятых сигналов.

Полученные значения надежностей поступают в блок 12 анализа стираний где надежность каждого поступающего сигнала сравнивается в п элементах сравнения с текущими п надежностями, после чего вырабатывается управляющи сигнал, поступающий на управляющие входы блока 11 очередности стираний, в котором этот сигнал указывает, в какой соответствующий четный регистр 27 нужно вставить данный сигнал.

Сформированные на выходе блока 1 п локаторов поступают на вторые входы блока 14 ввода стираний, в которо второй коммутатор 30 за п тактов про пускает на свои выходы 2(С.-1) входных локаторов (где С .- - значение управляющего сигнала на входе С-). За следующие п тактов парциальной частоты F: эти прошедшие стирания занимаю свои места в информационном блоке из ю, символов, а первый узел коммутатора 29, в котором на ныходы приходит сигнал, соответствующий Н:, при помощи дополнительных жестких решений (с контрольных входов блока 6.J) определяет, какие из симв.олов следует стереть в столбце матрицы из L ; строк и п столбцов, отвечающей слову кода.

Полученные сигналы сравниваются в элементе 33, в результате формируг ется матрица L-«n с единиц,ами на позициях, где нужно осуществить стирания в данном такте декодирования (1,Т;+1).

Эта информация с выходов блока 1А ввода стираний поступает вместе с задержанными в блоке 13 жесткими символами на входы блока 17 декодирования. Одновременно информационнь й блок стираний (с символами от первого до (Tj+l)-ro) записывается в блок 16 памяти стираний, а с его выходов поступает на входы стираний блока 10, на входы ошибок которого одновременно поступает информация с выходов блока 17.

Вместе с тем символы надежности с блока 6ij после задержки в блоке 15 поступают в виде прямого и инверсного сигналов на входы блока 19 коммутации, с выходов которого они по команде управляющего сигнала (с выхода блока 18 контроля) подаются на входы надежности блока 20.

В последнем определяется величина

,l) (., (S)j C.,(S) 4i +

..).

где y,f(S) и t)j,e(S) - число стираний и ошибок в 1-м подблоке на j-м шаге в S-M такте; 4 ; минимальное евклидово расстояние j-й внутренней системы сигналов;

Форм

У л

изобретени

20

25

Л Ч - надежность сигнала; л j - сигнал (с блока 18 контроля о правильности декодирования. Блок 20 коммутирует эту проанализированную информацию на свои Т: + 1 W-разрядные выходы, с которых она поступает в блок 22 суммирования, информация поступает на Т-+1 W-разряд- ных входов блока 23 выбора номера минимального числа,в котором выделяется номер информационного блока с минимальным содержимым. Этот номер используется в качестве управляющего сигнала для мультиплексора 24, кото-, рый пропускает на свой L--разрядный выход, соответствующий этому номеру вектор ошибок из блока 17 декодирования, задержанный в блоке 2 оперативной памяти.

Этот вектор ошибок сопоставляется в блоке 7.J сравнения задержанным

1. Устройство для декодирования двоичных блочных кодов, согласованных с многопозишюнными сигналами, содержащее первый N-й декодеры кода Грея (N - число внешних кодов во входном сигнале), входы которых яв- IQ ляются соответственно первыми - N-м информационными входами устройства первую - N-ю ступени декодирования, i-я ступень декодирования (,) содержат блок памяти, декодер внеш- 15 него кода и блок сравнения, N-я

ступень декодирования содергшт декодер внешнего кода и блок сравнения, первые выходы декодера внешнего кода j-й ступени декодирования (,N) соединены с первыми входами блока сравнения этой ступени декодирования выходы которого являются j-ми выходами устройства, выходы первого - N-ro декодеров кода Грея подключены к соответствующим информационным вхо дам блока памяти первой ступени деко дирования, (N+)-e информационные входы которого являются одноименными входами устройства, отличаю- 30 Щ е е с я тем, что, с целью повышения помехоустойчивости устройства и точности декодирования, в устройство введен блок синхронизации, в j-ю сту пень декодирования - декодер внутрен него кода, а декодер внешнего кода состоит из блока ввода стираний, блока очередности стираний, блока анализа стираний, блока памяти жестких символов, блока памяти надежностей, Q блока памяти стираний, блока декодирования, блока контроля, блока коммутации, блока вычисления параметров декодирования, блока оперативной памяти, блока суммирования, блока выбо- 45 Ра номера минимального числа и мультиплексора, первые - fj-e контрольные выходы (JJ1. li , 1. j- - ближайшее большее целое, d; и п - соответ- 50 ственно Хзммингово расстояние и число Ь -разрядных символов j-ro внешнего кода ) декодера внутреннего кода в j-й ступени декодирования соединены одноименными входами блока ввода

35

.«i v- rt/44ji ii-jc;n.n, ол( UJlUKa ВБОДо.

в блоке 13 входным сигналом декодера 55 стиравдй, выходы которого подключены.

6.J, в результате чего образуется выходной сигнал, представляющий собой слово j-ro внешнего кода с повьШ1енной) надежностью.

к входам стираний блока декодирования и информационным входам блока- памяти стираний, выходы которого соединены с входами стираний блока вычис

орм

У л

10

изобретения

20

25

1. Устройство для декодирования двоичных блочных кодов, согласованных с многопозишюнными сигналами, содержащее первый N-й декодеры кода Грея (N - число внешних кодов во входном сигнале), входы которых яв- IQ ляются соответственно первыми - N-ми информационными входами устройства и первую - N-ю ступени декодирования, , i-я ступень декодирования (,) содержат блок памяти, декодер внеш- 15 него кода и блок сравнения, N-я

ступень декодирования содергшт декодер внешнего кода и блок сравнения, первые выходы декодера внешнего кода j-й ступени декодирования (,N) соединены с первыми входами блока сравнения этой ступени декодирования, выходы которого являются j-ми выходами устройства, выходы первого - N-ro декодеров кода Грея подключены к соответствующим информационным входам блока памяти первой ступени декодирования, (N+)-e информационные входы которого являются одноименными входами устройства, отличаю- 30 Щ е е с я тем, что, с целью повышения помехоустойчивости устройства и точности декодирования, в устройство введен блок синхронизации, в j-ю ступень декодирования - декодер внутреннего кода, а декодер внешнего кода состоит из блока ввода стираний, блока очередности стираний, блока анализа стираний, блока памяти жестких символов, блока памяти надежностей, Q блока памяти стираний, блока декодирования, блока контроля, блока коммутации, блока вычисления параметров декодирования, блока оперативной памяти, блока суммирования, блока выбо- 5 Ра номера минимального числа и мультиплексора, первые - fj-e контрольные выходы (JJ1. li , 1. j- - ближайшее большее целое, d; и п - соответ- 0 ственно Хзммингово расстояние и число Ь -разрядных символов j-ro внешнего кода ) декодера внутреннего кода в j-й ступени декодирования соединены одноименными входами блока ввода

35

.«i v- rt/44ji ii-jc;n.n, ол( UJlUKa ВБОДо.

5 стиравдй, выходы которого подключены.

стиравдй, выходы которого подключены.

к входам стираний блока декодирования и информационным входам блока- памяти стираний, выходы которого соединены с входами стираний блока вычисления параметров декодирования, выходы которого подключены к соответствующим информационным входам блока суммирования, выходы которого соеди- йены с соответствую1Цими входами бло-г ка выбора номера.минимального числа, Выходы которого подключены к управляющим входам мультиплексора, выходы жестких решений декодера внутрен- него кода в j-й ступени декодирова- ия соединены в декодере внешнего ода с информационными входами блока амяти жестких символов, выходы которого подключены к первым информацион- ым входам блока контроля и входам Ьшибок блока декодирования и являют- |ся первыми выходами декодера вн€;шне- 1го кода j-й ступени декодирования, Ьыходы надежностей декодера внутрен- tiero кода которой подключены к ин- Й)ормационным входам блока памяти 1надежносгей, первым информационным |входам блока очередности стираний и первым входам блока анализа сти- раний, выходы которого соединены с управляющими входами блока очередности стираний, первые и вторые выходы которого подключены соответ-. ственно к перзым управляющим входам блока ввода стираний и вторым вхо- ;лам блока анализа стираний, выходы блока памяти надежностей соединены с соответствующими информационными входами блока коммутации, выход которого подключены к входам надежностей блока вычисле.ния параметров, декодирования, выходы блока дeкoд ; poвa нйя соединены с информационными входами блока оперативной памяти, вхо- дами ошибок блока вычисления параметров декодирования и управляющими входами блока контроля, вьDcoд.I которого подключены к управляющим входам блока коммутации, выходы блока оператив ной памяти соединены с соответствующими информационными входами- мультиплексора, выходы которого подключен к вторьп) входам блока сравнения j-й ступени декодирования, входы декоде- pa внутреннего кода первой ступени декодирования объединены с соответствующими информационными входами блока памяти первой ступени декодирования, первые - (N+l)-e выходы кото- рого подключены к одноименным информационным входам декодеров внутреннего кода (1+1)-й ступени декодировани и вторым информационным входам блока

5 Q 5 0 О 45 Q

5

контроля в декодере внешнего кода j-й ступени декодирования, управляющие входы декодера внутреннего кода и информационные входы блока памяти второй ступени декодирования объединены и подключены к выходам блока сравнения первой ступени декодирова- . ния, первые - i-e выходы блока памяти и выходы блока сравнения i-й ступени декодирования соединены соответственно с первыми - (1+1)-ми управляющими входами декодера внутреннего кода и с первыми - (1+1)-ми информационными входами блока памяти (1+1)-й ступени декодирования, вход синхронизатора является входом синхронизации устройства, первый выход синхронизатора соединен с тактовым входом записи блока памяти первой ступени декодирования, тактовыми входами блоков памяти второй - (Н-1)-й ступеней декодирования и тактовыми входами записи блока памяти жестких символов, блока памяти надежностей, блока памяти стираний и блока оперативной памяти в декодере внешнего кода j-й ступени декодирования, второй и третий выходы синхронизатора подключены к входам управления соответственно записью и считыванием блока памяти первой ступени декодирования, четвертый выход синхронизатора соединен с входами управления блоков памяти второй - (Ы-1)-й. ступеней декодирования и входами управления записью блока очередности стираний, блока памяти жестких -символов, .блока памяти надежностей и блока оперативной памяти в декодере внешнего кода j-й ступени декодирования, пятый выход синхронизатора подключен к входам управления записью блока памяти стираний в декодере внешнего кода j-й ступени декодирования, шестой выход синхронизатора соединен с входами управления считыванием блока памяти надеж- ностей и блока памяти стираний, в декодере внешнего кода j-й ступени декодирования, j-й выход первой группы выходов синхронизатора подключен к j-му тактовому входу считывания блока памяти первой ступени декодирования, тактовому входу блока очередности стираний и тактовым вхо-- дам считывания блока памяти жестких , символов, блока памяти надежностей, блока памяти стираний, блока суммирования и блока оперативной памяти в

декодере внешнего кода j-й ступени декодирования, j-e выходы второй группы выходов синхронизатора соединены с управляющими входами блока вычисления параметров декодирования вторыми управляющими входами блока ввода стираний и входами управления считыванием блока оперативной памяти в декодере внешнего кода j-й ступени декодирования, j-й выход третьей и j-e выходы четвертой групп выходов синхронизатора подключены соответственно к тактовому и управляющим входам блока декодирования в декодере внешнего кода i-й ступени декодирования, j-e выходы пятой группы выходов синхронизатора соединены с третьими управляющими входами блока ввода стираний и вторыми информационными входами блока очередности стираний в декодере внешнего кода j-й ступени декодирования, j-e выходы шестой группы выходов синхронизатора подключены к четвертым управляющим входам блока ввода стираний в дек одере внешнего кода j-й ступени декодирования.

2. Устройство по п. , о т л и - чающееся тем,.что блок очередности стираний содержит первый - п-й коммутаторы, первый - (2п)-й буферные регистры и элемент И, первый и второй входы которого являются входом управления записью и тактовым входом блока, выход элемента И подключен к тактовым входам всех буферных регистров, первые и вторые информационные входы всех коммутаторов соответственно объедине1 ы и являются одноименными входами блока, управляющие входы всех коммутаторов являют- - ся управляющими входами блока, пер- вые и вторые выходы т-го коммутатора (,п) соединены с-информацирн- |ными входами соответственно (2т-1)-го и (2т)-го буферных регистров , вько- ды которьпс подключены соответственно к третьим и четвертым информационным входам т-го- и пятым и шестым информационным входам (т+1)-го коммутаторов и являются соответствующими первыми и вторыми выходами блока.

3. Устройство по п. 1, о т л и- ч а юще ее я тем, что блок ввода. стираний содержит первый -п-й элементы равнозначности, элемент ИЛИ, элемент нёравно.значности и первый и второй коммутаторы, информационные вхо10

t5

20

25

30

5

0

5

0

5

ды которых являются соответственно контрольными и первыми управляющими входами блока, управляющие входы второго коммутатора являются вторьми управляющими входами блока, выходы второго коммутатора соед гнены с первыми входами соответствующих элемен- тов равнозначности,.вторые входы которых соответственно объединены и являются третьими управляющими входами блока, управляющие входы первого коммутатора являются четвертыми управляющими входами блока, выходы элементов равнозначности соединены с соответствующими входами элемента ИЛИ, выходы которого и выходы первого коммутатора подключены к первым и вторым входам элемента неравнознач-- ности, выходы которого являются выходами блока.

4, Устройство по п. 1, о т ji и - чающееся тем, что блок декодирования содержит узел декодирования, демультиплексор и первый и второй мультиплексоры, информационные входы которых являются входами соответственно стираний и ошибок блока, управляющие входы мультиплексоров и демультуплексора соответственно объединены и являются управляющими входами блока, управляющий вход узла декодирования является тактовым входом блока, выходы мультиплексоров подключены к соответствующим информационным входам узла декодирования, выходы которого соединены с информационными входами демультиплексора, выходь которого являются выходами блока.

5. Устройство по п. 1, отличающееся тем, что блок вычисления параметров декодирования содержит первый - третий источники nor стоянных кодов, группу элементов рав нозначности, группу элементов ИЛИ, сумматор, квадратор и первый и второй перемножители, первые входы которых являются входами соответственно стираний и ошибок блока, вьпсоды первого и второго источников постоянных кодов соединены с вторыми входами одноименных перемножителей, выходы которых подключены к первым и вторым входам сумматора, третьи входы которого являются входами надежности блока, выходы сумматора соединены с входами квадратора, выходы которого подключены к первым входам элементов ИЛИ

группы, выходы третьего источника ( постоянных кодов содеинены с первыми . входами соответствующих элементов равнозначности группы, вторые входы которых соответственно объединены и явля- ra jrcH управляющими входами блока, вы- Х||)ды элементов равнозначности группы соединены с вторыми входами элементов

ИЛИ группы, выходы которых являются

в 1ходами блока. i 6. Устройство п. 1,отличак Щ

е е с я тем, что синхронизатор )держит генератор тактовь1х импульсов.

П(;рвый и второй счетчики, первый - Т1)етий дешифраторы, первый и второй Т1зиггеры, элемент НЕ, элемент И, эле MI2HT ИЛИ-НЕ, первую-- четвертую группы счетчиков, первую и вторую группы у шожителей частоты, первую и вторую группы элементов И и блок выделейия синхронизирующих меток, вход которого является входом синхронизатора, а| выход соединен с входом обнуления BJroporo счетчика, выход генератора тактовых импульсов подключен к вхо- д)ам первого счетчика и умножителей ч|астоты первой группы и является первым выходом синхронизатора, выход м тадшего разряда первого счетчика фединен с соответствующими входами |вЬех дешифраторов, выход старшего разряда первого счетчика подключен к входам счетчиков первой группы, со о ветствующим входам всех дешифрато- ров и счетному входу второго счетчика, выходы разрядов которого соединены с соответствующими входами всех дешифраторов и первыми входами элемента И, примой и инверсный выходД) пе- реполнения второго счетчика являются соответственно вторым и третьим выходами синхронизатора, выходы первого и третьего дешифраторов подключены соответственно к S-входу первого и R-входу второго триггеров, выход второго дешифратора соединен с R-входом первого и S-входом второго триггеров, выходы которых подключены соответственно к первому и второму входам элемента ШТИ-НЕ и являются четвертым и пятым выходами синхронизатора, выход элемента ИЛИ-НЕ соединен с входом элемента НЕ и первгми входами элементов И первой группы и является шестым выходом синхронизатора, выходы умножителей частоты первой группы подключены к входам одноименных умножителей частоты второй группы, вторым входам одноименных элементов И первой группы и являются выходами первой группы синхронизатора, выходы счетчиков первой группы являются соответствующими выходами второй группы синхронизатора, выходы умножителей частоты второй группы соединены с входами одноименных счетчиков второй группы и являются выходами третьей группы синхронизатора, выходы счетчиков второй группы являются выходами четвертой группы синхронизатора, выход элемента НЕ соединен с вторым входом элемента И, выход которого подключен к первым входам всех элементов И второй группы, выходы элементов И первой группы соединеЩр с входами одноименных сче1 чиков третьей группы, выходы которых подключены к вторым входам одноименных элементов И второй группы и входам одноименных счетчиков четвертой группы, выходы которых являются выходами соответственйр пятой и шестой групп синхронизатора.

.2

fia5

.6

Фиг.9

иг.Ю

прием

cJ

Слово

(г)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Кодек двоичных блочных кодов | 1986 |

|

SU1408532A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Кодек блочных кодов | 1984 |

|

SU1270899A1 |

| Кодек блочных кодов | 1986 |

|

SU1401613A1 |

| Декодер мажоритарных блоковых кодов | 1986 |

|

SU1349011A1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Кодек блочной сигнально-кодовой конструкции | 1989 |

|

SU1711337A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Кодек блочных кодов | 1987 |

|

SU1473088A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи информации позволяет повысить помехоустойчивость устройства и точность декодирования. Устройство для декодирования содержит декодеры 1 кода Грея и ступени 3 декодирования, содержащие блоки 4 памяти, декодеры 5 внутреннего кода и блоки 7 сравнения. Благодаря введению в каждую ступень 3 декодирования декодера 6 внешнего кода со специфическим выполнением, а также синхронизатора, в устройстве осуществляется последовательное декодирование вложенных кодов, причем декодированное слово предыдущего кода используется при декодировании последующего кода. 5 з.п. ф-лы, 12 ил.

ииае ((П)

. . . АемдироВанм.. .

OnpeafMHue

мяаторов

6л.оче1.с1гыр)

Сравнение jmamoDoS (6л.Кодаапл

Ct L

Hi л

ллл

ШГ....Тп

«iJ

ЛеноЛлюбамие

Г л У)

т... Гл1

«Г L.

Фиг.П

Л йУ-О

a.j,fiti-ot

| Зарубежная радиоэлектроника, 1985, № 7, с | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 1491310, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кодек двоичных блочных кодов | 1986 |

|

SU1408532A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-08-23—Публикация

1987-12-07—Подача