1

Изобретение относится к вычислительной технике и может быть использовано в аналого-цифровых преобразователях.

Известен аналоговый запоминающий элемент, содержащий биполярный транзистор, выход которого подключен к конденса- 5 тору и затвору полевого транзистора, выход последнего соединен с базой биполярного транзистора и резистором. В известном элементе конденсатор заряжается входным сигналом через биполярный транзистор. Заряд ,Q происходит до тех пор,пока напряжение с выхода полевого транзистора не закроет переход эмиттер-база биполярного транзистора. Таким образом, напряжение на выходе полевого транзистора устанавливается равным входному за вычетом напряжения на 5 участке эмиттер-база биполярного транзистора 1.

Недостатком, такого устройства является низкая точность запоминания вследствие остаточного напряжения между эмиттером и 2о базой биполярного транзистора и погрещности, вызванной «пролезанием входного сигнала через собственную емкость биполярного транзистора на выход устройства. Кроме того, устройство не имеет возможности

запоминать входные сигналы произвольной полярности.

Наиболее близким к предлагаемому по технической сущности является аналоговое запоминающее устройство, содержащее ячейку памяти, выход которой соединен с первым входом сумматора, усилитель, вход которого соединен с выходом сумматора, три ключа, нагрузочный элемент, пассивный элемент 2.

Недостатком устройства является невысокая точность как в связи с остаточным напряжением на ключах, так и за счет погрещности, вызванной «пролезанием входного сигнала на выход устройства через элементы сумматора.

Цель изобретения - повыщение точности устройства.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее ячейки памяти, каждая из которых состоит из ключа, выход которого соединен с накопительным элементом, например с одной из обкладок конденсатора, истокового повторителя напряжения, информационный вход которого соединен с выходом ключа, другая обкладка конденсатора соединена с щиной нулевого потенциала, пёрвый вход ключа соединен с выходом истокового повторителя напряжения, сумматор, выход которого соединен с первым входом операционного усилителя, введены пассивный элемент и делитель напряжения, первый вход которого соединен с первым выводом пассивного элемента, второй вывод пассивного элемента соединен с вторым входом ключа каждой ячейки памяти и является входом устройства, выход истокового повторителя напряжения каждой ячейки памяти соединен с соответствующим входом сумматора, второй и третий входы делителя напряжения соединены соответственно с выходом операционного усилителя и с шиной нулевого потенциала, выход делителя напряжения соединен с вторым входом операционного усилителя, выход которого является выходом устройства.

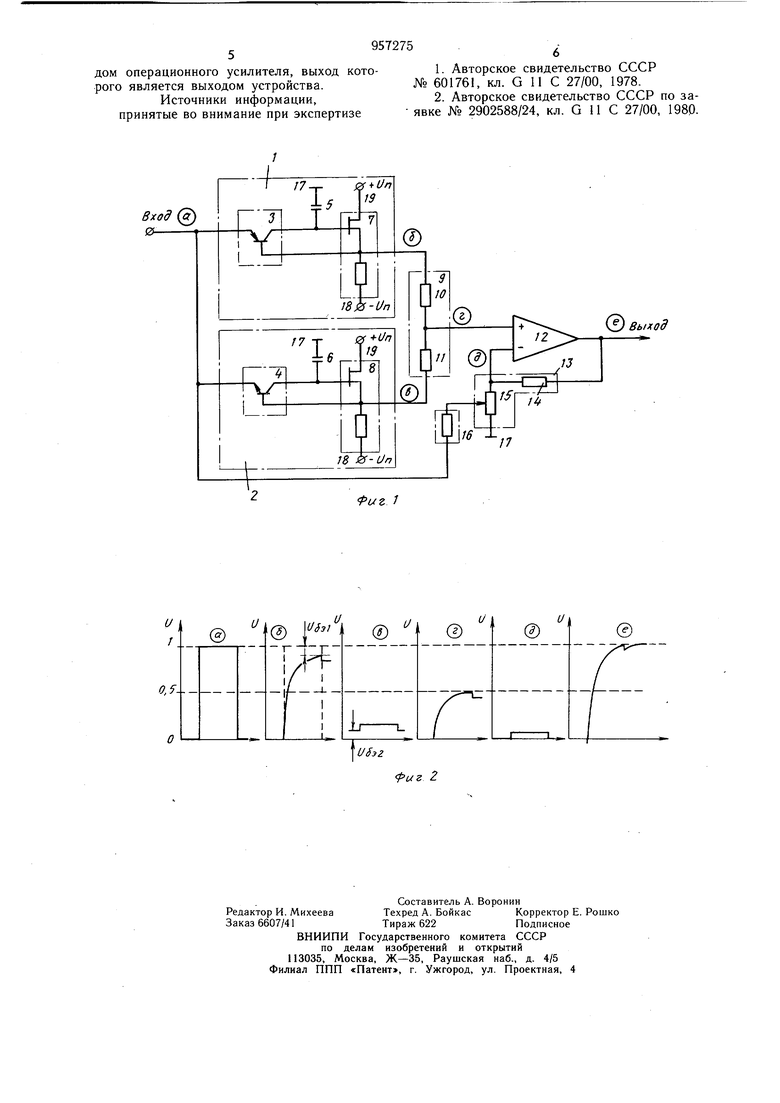

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 временные диаграммы, поясняющие его работу.

Устройство содержит ячейки 1 и 2 памяти, ключи 3 и 4, накопительные элементы, например конденсаторы 5 и 6, истоковые повторители 7 и 8 напряжения, сумматор 9, выполненный на резисторах 10 и 11, операционный усилитель 12, делитель 13 напряжения, состоящий из резистора 14 и потенциометра 15, пассивный элемент, например резистор 16, шину 17 нулевого потенциала и шины 18 и 19 питания.

Устройство работает следующим обраЗОИ.

При отсутствии входного сигнала ячейки 1 и 2 памяти производят отслеживание нулевого входного потенциала с погрешностью, равной падению напряжения на эмиттерно-базовых переходах биполярных транзисторов ключей 3 и 4.

Напряжение на выходе ячейки 1 памяти несколько меньше нуля, а на выходе ячейки 2 памяти несколько больше нуля. Напряжения с выходов ячеек 1 и 2 памяти поступают на резисторы 10 и 11 сумматоров, причем величины сопротивлений резисторов выбраны одинаковыми. В точке суммирования напряжения с выходов обеих ячеек памяти компенсируются. Причем в случае применения биполярных транзисторов одного типа, например кремниевых 2Т363А (р-п-р) и 2Т368А (п-р-п), в точке суммирования происходит полная компенсация погрешностей. Нулевой потенциал с выхода сумматора 9 подается через операционный усилитель 12 на выход устройства.

При поступлении на вход устройства импульса, например, положительной полярности происходит заряд конденсатора 5 первой ячейки 1 памяти, а биполярный транзистор ключа 4 второй ячейки 2 памяти закрыт этим входным импульсом, и конденсатор б не заряжается. Таким образом, после прекращения действия входного импульса с

выхода ячейки 1 памяти снимается напряжение, равное входному сигналу, а с выхода ячейки 2 памяти - кулевой потенциал. В суммирующей точке - точке соединения резисторов 10 и 11 -выходное напряжение понижается в два раза и одновременно происходит компенсация погрешностей эмиттернобазовых переходов. С сумматора 9 напряжение поступает на операционный усилитель 12 с коэффициентом усиления, равным двум, где восстанавливается до прежнего значения и поступает на выход устройства.

По окончании действия входного импульса на выходах ячеек 1 и 2 памяти появляется отрицательный перепад напряжения за счет наличия собственной емкости биполярных транзисторов ключей 3 и 4 (фиг. 26, в). Для компенсации этого перепада на инверсный вход операционного усилителя 12 через резисторы 15 и 16 подается часть входного сигнала (фиг. 2д), по величине равного отрицательному перепаду на прямом входе усилителя 12. Операционный усилитель 12 производит вычитание двух отрицательных перепадов, действующих по окончании входного импульса, компенсируя тем самым погрешность «пролезания входного сигнала (фиг. 2е). При отрицательной полярности входного сигнала устройство работает аналогично.

Таким образом, предлагаемое устройство позволяет снизить погрещность запоминания и одновременно позволяет запоминать сигналы произвольной полярности.

Формула изобретения

Аналоговое запоминающее устройство, содержащее ячейки памяти, каждая из которых состоит из ключа, выход которого соединен с накопительным элементом, например с одной из обкладок конденсатора, истокового повторителя напряжения, информационный вход которого соединен с выходом ключа, другая обкладка конденсатора соединена с шиной нулевого потенциала, первый вход ключа соединен с выходом истокового повторителя напряжения, сумматор, выход которого соединен с первым входом операционного усилителя, отличающееся тем, что, с целью повыщения точности устройства, в него введены пассивный элемент и делитель напряжения, первый вход которого соединен с первым выводом пассивного элемента, второй вывод пассивного элемента соединен с вторым входом ключа каждой ячейки памяти и является входом устройства, выход истокового повторителя напряжения каждой ячейки памяти соединен с соответствующим входом сумматора, второй и третий входы делителя напряжения соединены соответственно с выходом операционного усилителя и с шиной нулевого потенциала, выход делителя напряжения соединен с вторым вхог957275

j6

дом операционного усилнтеля, выход кото-1. Авторское свидетельство СССР

рого является выходом устройства.№ 601761, кл. G 11 С 27/00, 1978.

Источники информации,2. Авторское свидетельство СССР по запринятые во внимание при экспертизе явке № 2902588/24, кл. G 11 С 27/00, 1980.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1981 |

|

SU970474A1 |

| Аналоговое запоминающее устройство | 1990 |

|

SU1734123A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868840A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU734812A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU773734A1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1261013A1 |

| Аналоговое запоминающее устройство | 1974 |

|

SU510752A1 |

| Устройство выборки и хранения информации | 1976 |

|

SU746729A1 |

| Пиковый детектор | 1976 |

|

SU592011A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU680058A1 |

Авторы

Даты

1982-09-07—Публикация

1981-03-24—Подача