держащее в каждом разряде регистрирующий триггер, подготовительный вход которого подключен к выходу первого элемента ИЛИ, а выход, соединен с входами первого элемента ИЛИ, первого, второго и третьего элементов И, другой вход первого элемента И связан с нулевым выходом фиксирующего триггера, а выход с вторым входом первого элемента ИЛИ последующего разряда, вход установки фиксирующего триггера подсоединен к выходу третьего элемента Иу и дополнительный регистрирующийГ триггер, выход которого соединен с его -подготовительным входом и вторым входом первого элемента ИЛИ первого разряда, вход установки подключен к шине тактовых импульсов, а счетные вхо,цы всех регистрирующих триггеров подсоединены к входной шине, введены первый и второй управляющие триггеры, четвертый элемент И входы которого подключены к выходам управляющих триггеров, пятый элемент И, выход которого соединен с входом второго управляющего триггера, один вход соединен с выходом первого управляющего триггера, а другой вход связан с входной шиной, последовательно соединенные второй элемент ИЛИ, входы которого подключены к единичным выходам фиксирующих триггеров каждого разряда, элемент НЕ и шестой элемент И, выход которого подключен к вторым входам третьих элементов И каждого разряда, а второй вход связан с шиной тактовых импульсов и с входами установки управляющи триггеров, а также седьмой элемент И, выход которого подключен к входам- установки регистрирующих триггеров каждого разряда, один вход связан с шиной тактовых импульсов, а другой вход соединен с выходами второго элемента ИЛИ и счетным входом первого управляющего триггера, при этом выходы вторых элементов И каждого разряда подключены к счетному входу фиксирующего триггера, второй вход второго элемента И первого разряда подключен к выходу дополнительного регистрирующего триггера, а второй вход второго элемента И каждого последующего разряда подключен к выходу регистрирующего триггера предыдущего разряда.

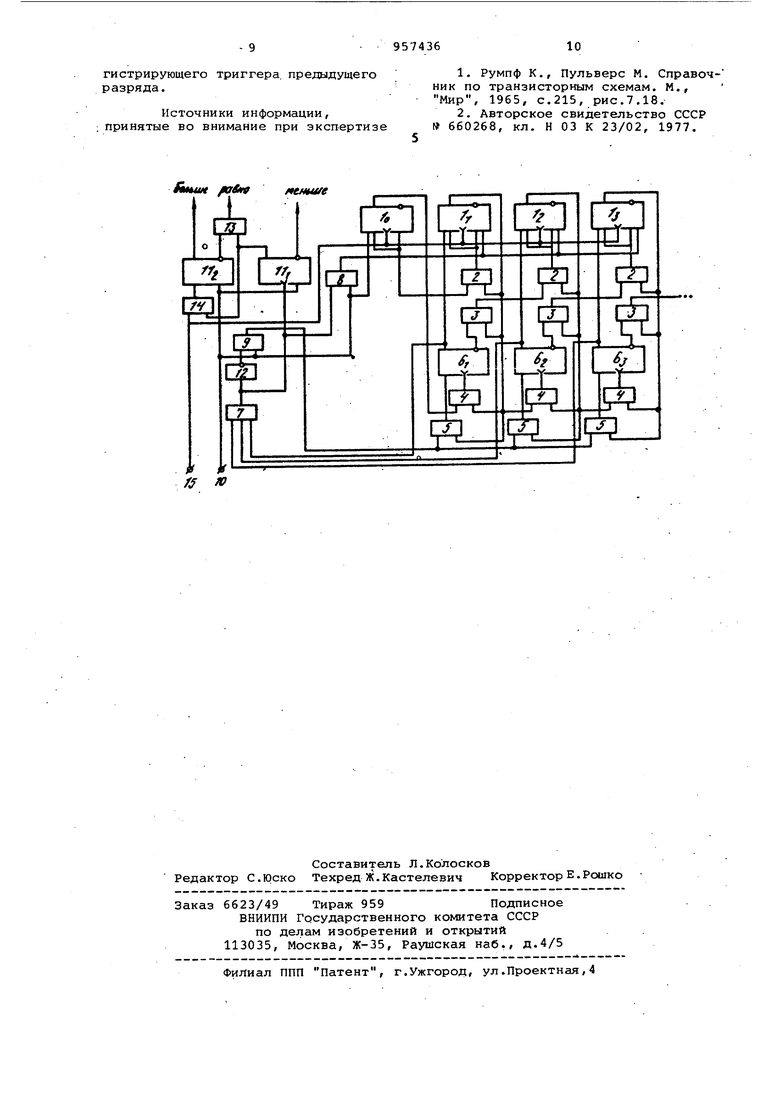

На чертеже показана схема счетного устройства.

Устройство содержит дополнительный ре151Стрирующий триггер 1 , регистрирующие триггеры 1 - 1-j в каждом разряде, первый элемент ИЛИ 2, первы элемент И 3, второй элемент И 4, третий элемент И 5, фиксирующие триггеры 6 - второй элемент ИЛИ 7, седьмой элемент И 8, шестой элемент И 9, шину 10 тактовых импульсов.

первый и второй управляющие триггеры 11 и 11, элемент НЕ 12, четвертый элемент И 13, пятый элемент И 14 входную шину 15. .

Единичный выход регистрирующих триггеров 1-,- Ij, начиная с первого разряда, подключен к первому входу первого элемента ИЛИ 2, к первым входам первого 3, второго 4 и третьего 5 элементов И и ко второму входу второго элементаИ 4 следующего разряда, выход вторых элементов И 4 соединен со счетным входом соответствующих фиксирующих триггеров , единичный выход которых подключен к единичным входам.соответствующих регистрирующих триггеров -,-, и к входу второго элемента ИЛИ 7, нулевой выход фиксирующих триггеров б - бз соединен со вторым входом первого элемента И 3, выход которого соединен со вторым входом первого элемента ИЛИ 2, начиная со 2-го разряда, в последнем разряде эта связь прерывается, второй вход элемента ИЛИ 2 первого разряда подключен к подготовительному входу и выходу дополнительного регистрирующего триггера 1 и к второму входу элемента И 4 первого разряда, выход элемента ИЛИ 2 подключен к подготовительному входу соответствующих регистрирующих триггеров 1 1 - 13, нулевая шина которых подсоединена к выходу седьмого элемента И 8, первый вход элемента И 8 соединен с единичным входом дополнительного регистрирующего триггера 1р, с первым входом шестого элемента И9, шиной 10 тактовых импульсов и с установкой нуля триггеров 11 и 11, а второй вход элемента И 8 - к выходу второго элемента ИЛИ 7 и к входу элемента НЕ 12, выход которого подключе к второму входу шестого элемента И 9 выход элемента И 9 соединен со вторыми входами третьего элемента И 5, выход элемента И 5 соединен с единичным входом фиксирующих т&иггеров 6 63, второй вход седьмого элемента И 8 подключен к счетному входу первого управляющего триггера 11-), с нулевого выхода которого получаем сигнал Меньше, а единичный выход триггера 11-1 подсоединен к первым входам четвертого 13 и пятого 14 элементов .И, второй вход пятого элемента И 14 подключен к входной шине 15 и к счетным входам регистрирующих триггеров IQ - Ij/ а выход к единичному входу второго управляющего триггера llii, где с единичного выхода снимается сигнал Больше, а нулевой выход соединен с вторым входом четвертого элемента И 13, с выхода которого поступает сигнал Равно.

В начальном состоянии все триггеры находятся в состоянии О, кроме регистрирующего триггера IQ, который находится в состоянии 1. Регистрирующие триггеры Ig - 1 вместе с первыми элементгиии ИЛИ 2 работают в режиме регистра сдвига единицы, в котором единица движется от триггера IQ направо в триггеры 1, lij и т.д. Единица перемещается на столько разрядов, сколько импульсов оказывается в первой серии входного сигнала X (1}. После подачи входного сигнала подается тактовый импульс на тактовый вход схемы, кото рый устанавливает регистрирующий триггер IQ в положение 1 и, пройдя через элемент 8 (в начальном состоянии все фиксирующие триггеры 6 63 находятся в состоянии О и на выходе элемента НЕ 12 установлен высокий потенциал, что дает разрешение на элемент И 8), поступает на вход элементов И 5, вторые входы которых сое динены с единичными выходами соответ ствующих триггеров 1 - 1з/ импульс проходит на установку единицы того фиксирующего триггера, соответствующий триггер которого находится в - состоянии 1, и записывает в нем единицу. Единичный выход фиксирующего триггера подтверждает единичное состояние соответствующего регистрирующего триггера через вход Установка единицы . Этот же тактовый импульс подается на вход установ ки нуля триггеров 11/i и 11 г но их состояние не изменяется, так как они находятся в нулевомсостоянии. Сигнал на выходе находится на шине Мен ше. При поступлении следующего вход ного сигнала возможны следующие три случая. 1.Количество импульсов в очередной серии Х(2) меньше количества импульсов в первой (предыдущей) серии X(1J, т.е. х(2) х(1) ,x(i) x(i-1) 2.Количества импульсов во второй серии Х(2) равноколичеству импульсов в первой серии ), т.е. Х(2) х(1Ь 3.Количество импульсов во второй серии (2) больше количества импульсов в первой серии Х(1), т.е. х(2) 7Х(1), xCi) x(i-1) Устройство работает следующим образом. В первом случае (Х(2)Х(1) вторая серия импульсов начинает продвижение с регистрирующего триггера 1 и в конце серии единица устанавливается в разряде левее того разряда, в котором записана единица в предыдущем такте тактовым импульсом. Эта единица фиксируется соответствующим фиксирующим триггером и во время поступления очередного входного сигнала не продвигается, несмотря на то, что высокий потенциал с единичного выхода данного регистрирующего триггера подготавливает собственный счетный вход. Счетный вход следующего триггера не подготавливается по той причине, что.на инверсном выходе соответствующего Триггера сигНсша нет и первый элемент И 3 этого же разряда закрыт. ПодаваегЫй тактовый импульс устанавливает триггер IQ в положение единицы и, пройдя через элемент И 8, все регистрирующие триггера, кроме триггера, фиксирующий триггер которого находится в положении единицы, устанавливает в положение нуль. Не изменяется состояние фиксирующих триггеров, так как в одном из разрядов находится единица, на выходе элемента ИЛИ 7 имеется сигнал, а на выходе элемента НЕ 12 отсутствует, что в свою очередь запирает элемент И 9. Не изменяется также состояние триггеров 11, и 11. Сигнал будет на инверсном выходе триггера 11-,, так что состояние схемы после заканчивания второго такта, в случае, если Х(2) Х(1), совпадает с состоянием до начала второго такта. В случае, когда количество импульсов в последующей серии равно количеству импульсов в предыдущей серии, т.е. Х(1) Х(2), до поступления прследнего импульса на вход схемы, схема работает также, как-и в прелыг -дущем случае, при Х(1) Х(2). Перед поступлением последнего им пульса единица текущего отсчета оказывается в предыдущем регистрирующем триггере, где находится единица предыдущего отсчета. При этом единичное плечо предыдущего разряда подготавливает свой счетный вход, а также через элемент И 4 подает высокий потенциал на счетный вход фиксирующего триггера последующего разряда, так как второй вход элемента И 4 подго- товлен высоким потенциалом с единичного выхода своего же регистрирующего триггера. При поступлении последнего импульса из серии последовательных импульсов предыдущий регистрирующий триггер перебрасывается в положение нуль, падает высокий потенциал на его. единичном выходе, закрывается упомянутый элемент И 4, перебрасывает триггер фиксации в положение нуль, в этот момент все триггеры фиксации оказываются в положении нуль падает высокий потенциал на выходе . элемента ИЛИ 7. Задний фронт импульса перебрасывает со счетного входа триггер 11 в положение единицы, открывается элемент И 13 и появляется сигнал на шине Равно, появляется сигнал на выходе элемента НЕ 12 и получает разрешение элемент И 5.

Во время поступления тактового импульса, в конце серии импульсов этот тактовый импульс проходит через элемент Н 9, фиксирует единицу в том же триггере фиксации, в котором была она до начала такта, и устанавливает триггер 11,, в положение .нуль, регистрирующий триггер IQ в положение единица и подготавливает схему к работе для следующего такта. В этом случае после подачи тактового импульса схема возвращается к тому же состоянию, в котором он была в предыдущем такте, т.е. до подачи тактов последней серии, только лишь с той разницей, что на выходной шине Равно появляется импульс длительностью, равной времени между по.ступлением последнего импульса из серии тактового импульса.

В третьем случае, т.е. когда Х(1) Х(2), во время поступления импульсов последней серии выполняются условия сначала первого случая, а потом второго, после чего только в одном регистрирующем разряде записывается единица и именно в том, в котором она была зафиксирована до подачи последней серии импульсов. .

Первый триггер управления находится в положении единица и высокий потенциал с единичного разряда данного триггера дает разрешение элементу И 14, к этому времени все фиксирующие триггеры находятся в положении нуль. На выходе элемента ИЛИ 7 сигнала нет появляется сигнал на выходе: э лемента НЕ 12, что дает разрешение элементу И 9. .

Очередной импульс проходит через элемент И 14, устанавливает, триггер HT. тоже в положение единица. Сигнал исчезает на выходе Равно и появля ется На выходе Больше, тот же импульс передвигает единицу в следующий регистрирующий триггер. После этого каждый поступающий импульс только передвигает единицу в следующий триггер, т.е. совокупность регистрирующих триггеров и элементов ИЛИ 2 работают как регистр сдвига еди ницы.

После окончания подачи серии импульсов подается тактовый импульс, который устанавливает триггер управ ления в положение Нуль, пройдя через элемент И 9, на вход элементов И« 5, фиксирует идиницу в том фиксирующем триггере, в соответствующем регистрирующем триггере которого имеется единица во время подачи последнего импульса из серии импульсов отсчета, этим схема подготовлена к работе в следующем такте. В это случ;ае сигнал на шине Больше будет существовать после нарушения условия равенства количества импульсов, записанных в предыдущем и в текущем такTax, до подачи последнего тактового , иг пульса.

Разрядность выбирается из условия максимального размаха обрабатываемого процесса.

Формула изобретения

Счетное устройство, содержащее в каждом разряде регистрирующий триггер, подготовительный вход которого подключен к выходу первого элемента ИЛИ, а выход соединен с входами первого элемента ИЛИ, первого , второго и третьего элементов И, другой вход первого элемента И связан с нулевым выходом фиксирующего триггера, а выход - с вторым входом первого элемента ИЛИ последующего разряда, вход установки фиксирукицего триггера подсоединен к выходу третьего элемента И, и дополнительный регистрирующий триггер, выход которого соединен с его подготовительным вхо дом и вторым входом первого элемента ИЛИ первого разряда, вход установки подключен к шине тактовых импульсов, ;а счетные входы всех реги-стрирукицих Триггеров подсоединены к входной шине, отличающееся тем, что, с целью расширения его функциональных возможностей за счет сравнения пода-, ваемых кодов и вывода экстремального значения, в него введены первый и второй управляющие триггеры, четвертый элемент И, входы которого подключены к выходам управляющих триггеров, пятыйэлемент И, выход которого соединен.с входом второго управляющего триггера, один вход соединен с выходом первого управляющего триггера, а другой вход связан с входной шиной, последовательно соединенные второй элемент ИЛИ, входы которого подключены к единичным выходам фиксирующих триггеров каждого разряда, элемент НЕ и шестой элемент И, выход которого подключен к вторым входам третьего элемента И каждого разряда, а второй вход CBsr зан с шиной тактовых импульсов и с

0 входами установки управляющих триггеров, а также седьмой элемент И, выход которого подключен к входам установки регистрирующих триггеров каждого разряда, один sxcsa связан с

5 шиной тактовых импульсов, а другой вход соединен с выходом второго элемента ИЛИ и счетным входом-первого управляющего триггера, при этом выходы вторых элементов И каждого разряда подклйэчены к счетному входу фиксирующего триггера, второй вход второго элемента И первого разряда подключён к выходу дополнительного регистрирующего триггера, а второй вход второго элемента И каждого последующего разряда подключен к выходу регистрирующего триггера, предыдущего разряда.

Источники информации, ; принятые во внимание при экспертизе

1.Румпф К,, Пульверс М. Справочник по транзисторным схемам. М., Мир, 1965, с.215, рис.7.18.

2.Авторское свидетельство СССР № 660268, кл. Н 03 К 23/02, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик | 1977 |

|

SU660268A1 |

| Устройство для сжатия последователь-НОСТи СигНАлОВ | 1979 |

|

SU842911A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| УСТРОЙСТВО для ИНТЕГРИРОВАНИЯ ФУНКЦИЙ в ДВОИЧНО-ДЕСЯТИЧНОМ ЦИКЛИЧЕСКОМ КОДЕ | 1967 |

|

SU203321A1 |

| Устройство для преобразования частоты следования импульсов в код | 1983 |

|

SU1182676A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| Устройство для импульсного регулирования мощности переменного тока | 1984 |

|

SU1244763A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

Авторы

Даты

1982-09-07—Публикация

1980-12-30—Подача