АЗОИМПУЛЬСНЫЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| Фазо-импульсный сумматор | 1977 |

|

SU651343A1 |

| К-значный фазоимпульсатор сумматор | 1977 |

|

SU657435A1 |

| Последовательный сумматор | 1983 |

|

SU1149248A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1295381A1 |

| Устройство для сложения чисел | 1976 |

|

SU634274A1 |

| Десятичный сумматор | 1973 |

|

SU491947A1 |

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

| Устройство для суммирования последовательных кодов | 1984 |

|

SU1254472A1 |

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

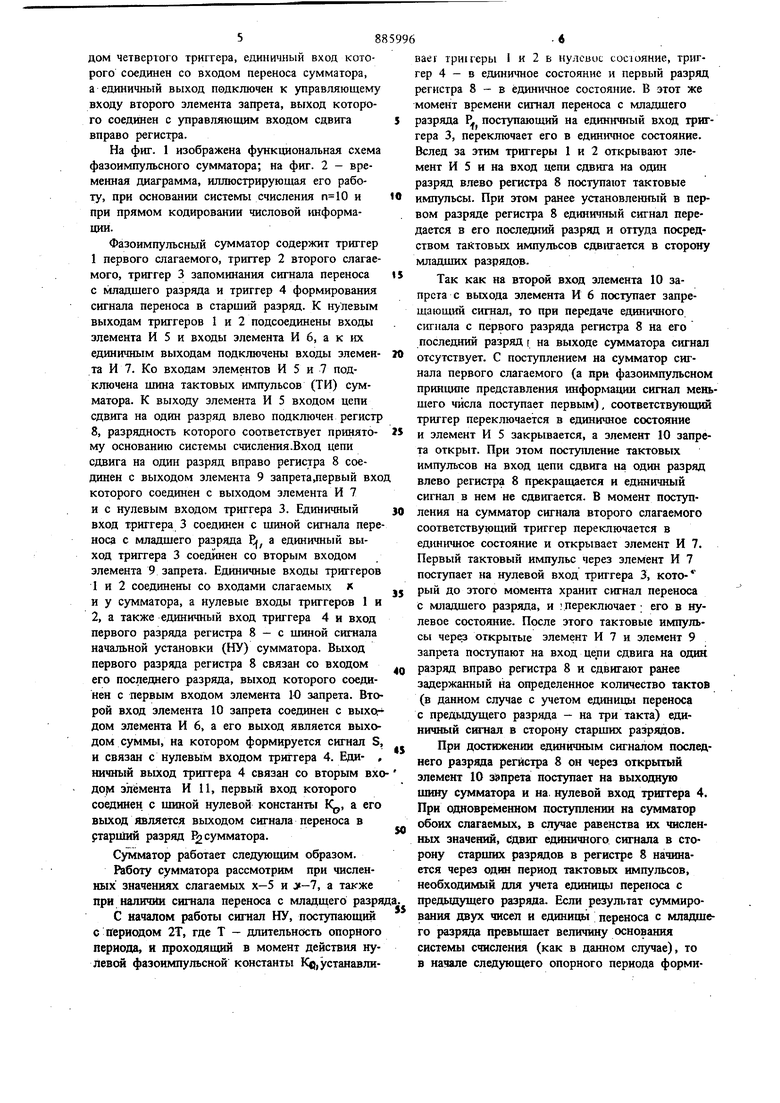

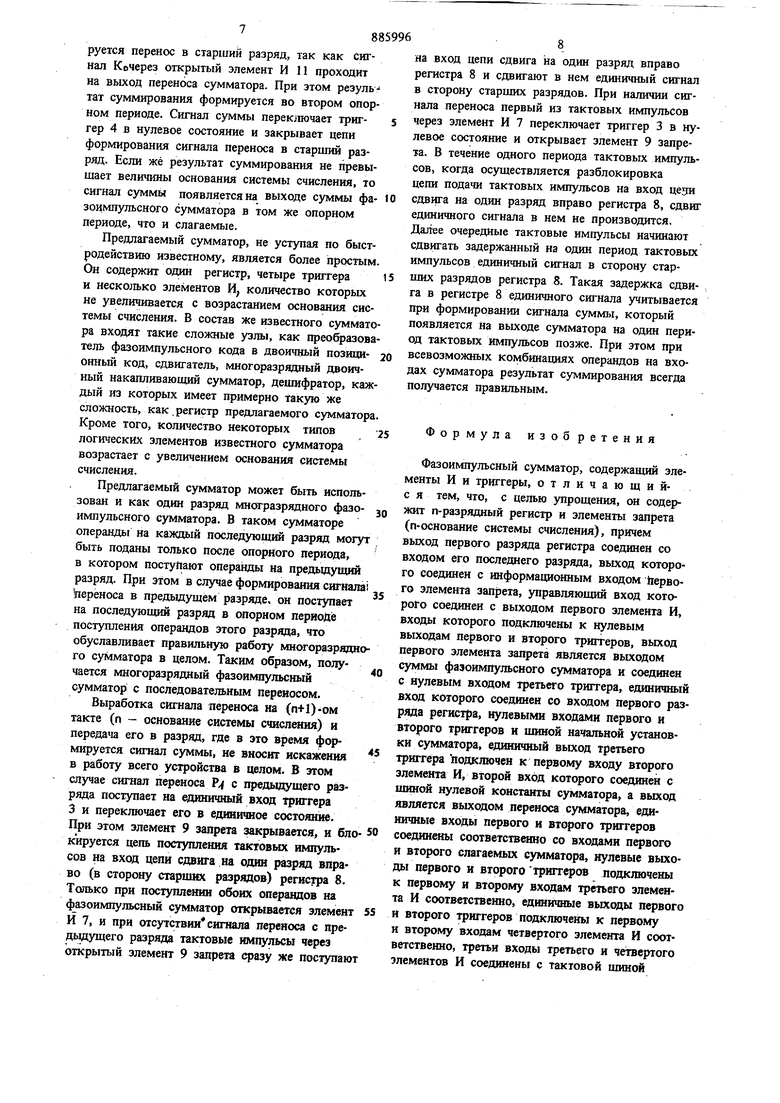

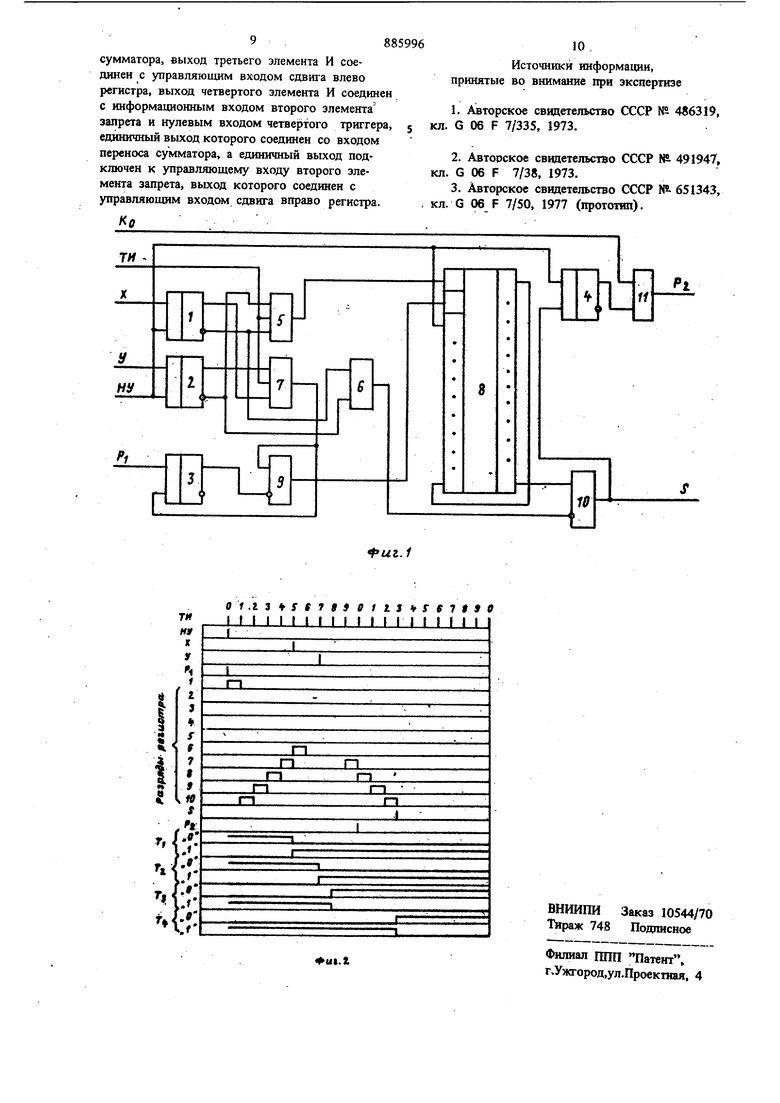

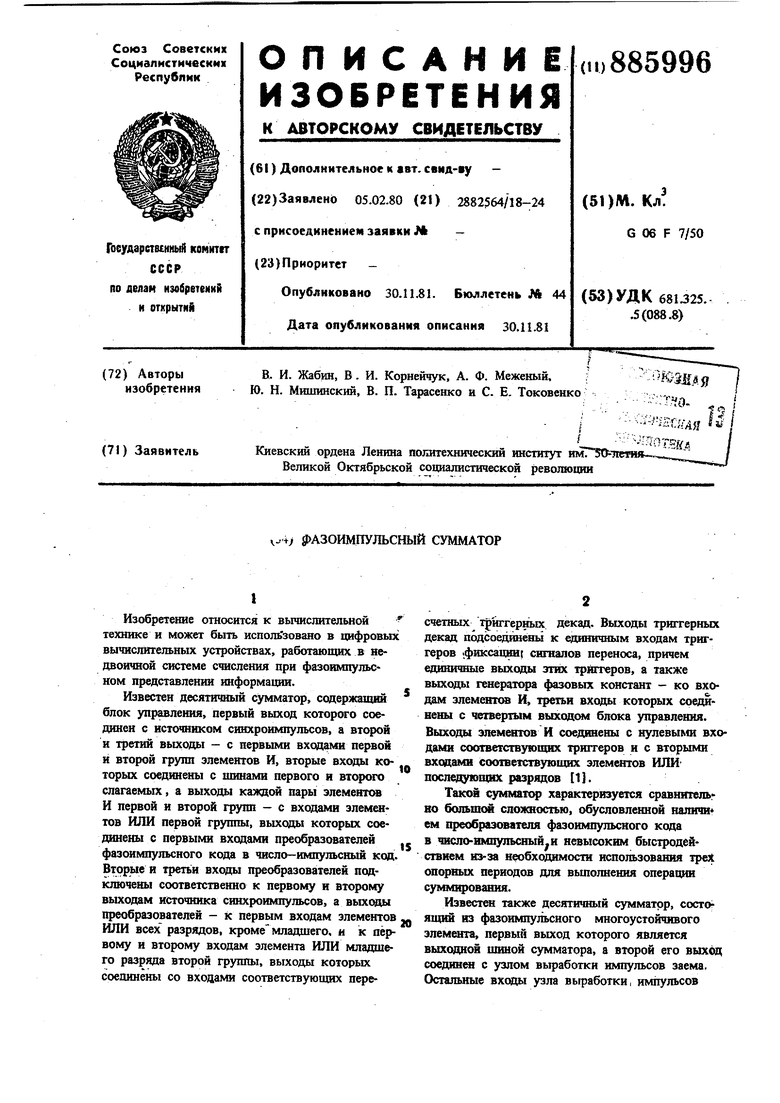

Изобретение относится к вычислительной техника и может быть использовано в цифровых вычислительных устройствах, работающих в недвоичной системе счисления при фазоимпульс ном представлении информации. Известен десятичный сумматор, содержащий блок управления, первый выход которого соединен с источником снихроимпульсов, а второй и третий выходы - с первыми входами первой и второй групп злементов И, вторые входы которых соединены с щинами первого и BTqraro слагаемых, а выходы каждой пары элементе И первой и второй групп - с входами злементов ИЛИ первой группы, выходы которых соединены с первыми входами преобразователей фазоимпульсного кода в число-импульсный код Вторые и третьи входы преобразователей подключены соответственно к первому и второму выходам источника синхроимпульсов, а выхо1аы преобразователей - к первым входам злементов ИЛИ всех разрядов, кромемладшего, и к первому и второму входам элемента ИЛИ младшего разряда второй rpjonai, выходы которых соединены со входами соответствующих пересчетных триггерных декад. Выходы трштерных декад подсоединень к единичным входам триггеров фиксации; сигналов переноса, причем единичные выходы зтих триггеров, а также выходы генератора фазовых констант - ко входам злемевтс И, третьи входы которых соединены с четвертым выходсям блока управлання. Выходы 31юментов И соединены с нулевымн входами соответствующих и с вторыми входам соответствующих элементов ИЛИ последующих разрядов 1. Такой сумматор характеризуется сравшггельг но большсж слохшостью, обусловленной налнчи« fM преобразователя фазоимпульсного кода в число-импульсный.и невысоким быстродействием из-за необхош(мости использования тре;1 опорных периодов для вьшолнения операции суммирования. Известен также десятичный сумматор, состог ящий из фазонмпульсного многоустойчнвого элемента, первый выход которого является выходной шиной сумматора, а второй его выхсщ соедини с узлом выработки импульсов заема. Остальные входы узла вьфаботки, импульсов 38 заема связаны с шинами знака второго слагаемого и опроса заема, а его выход является шиной импульсов заема в старший разряд. К ус тановочному входу фазоимпульсного многоустойчивого элемента подведена шина установочного сигнала, а к его счетному входу подклю. чен выходом элемент ИЛИ, первый вход которого соединен с шиной импульсов переноса. Второй вход элемента ИЛИ соединен через злемент И с преобразователем фазоимпульсного кода первого слагаемого в число-импульсный код, а третий его вход- с преобразователем фазоимпульсного кода второго слагаемого в число-импульсный код. На второй и третий входы элемента И подведены шины тактовых импульсов и импульсов заема. Первые входы преобразователей связаны с шинами, слагаемых, а их вторые входы - с шинами знака слагаемых, на третьи же входы зтих преобразователей подведена шина импульсов опорной частоты; кроме того, четвертый вход преобразователя первого слагаемого соединен с шиной тактовых импульсов, а второго слагаемого - с шиной знака второго слагаемого. Преобразователи фазоимпульсного кода первого и второго елагаемых в число-импульсный код соединены соответственно с первым и вторым входами узла выработки импульсов переноса, третий и четвертый входы которого связаны соответственно с Шинами знака первого и второго слагаемых , пятый же вход этого узла сбединен с шиной опроса переноса, а его выход является шиной импульсов переноса в старший разряд {2 Сложность такого сумматора обусловлена наличием в его схеме преобразователей фазоимпульсного кода в число-импульсный и фазоимпульсного многоустойчивого элемента, а необходимость сдвига на половину периода тактовых импульсов число-импульсного кода одного из слагаемых сушественно снижает быстродействие такого сумматора. Наиболее близким к предлагаемому является фазоимпульсный сумматор содержащий многоразрядный двоичный накапливающий сумматор, вход младшего разряда которого соединен с шиной сигнала переноса с предыдущего разряда. К информационным входам двойного сумматора подключен выходами сдвигатель соедине1шый входом цепи сдвига и входом разрешения передачи информации без сдвига соответственно с единичным и нулевым выходами триггера. Единичный вход триггера связан с вы ходом элемента И, а его нулевый вход - с шиной нулевой фазоимпульсной константы. Ко входам сдвигателя подсоедини выходами преобразователь фазоимпульсного кода в двоичный позиционный код. К управляющему входу преобразователя подсоединен выходом элемент ИЛ а ко входам преобразователя подведены шины фазоимпульсных констант. Первые входы элементов И и ИЛИ соединены с шиной первого слагаемого, а их вторые входы - с шиной второго слагаемого. К выходам двоичного сумматора подключен дешифратор, связанный выходами с первыми входами злементов И, ко вторым входам которых подведены шины соответствзтощих фазоимпульсных констант. Выходы злементов И соединены со входами элемента ИЛИ, выход которого является выходной шиной фазоимпульсного сумматора. Выходы . пере носа сдвигателя и двоичного сумматора связаны со входами элемента ИЛИ, выход которого является шиной сигнала переноса в старший разРЯД 3.. . Такой сумматор характеризуется большой сложностью, так как в его состав входят преобразователь фазоимпульсного кода в двоичный позиционный код, сдвигатель, многоразрядный двоичный накаплнваюшнй сумматор, дешифратор. Цель изобретения - упрощение сумматора. - Поставленная цетть достигается тем, что в. фазоимпульсный сумматор, содержащий элементы И и триггеры, введены п-разрядный регистр и элементы запрета (п - основание системы счисления), причем выход первого разряда регистра соединен со входом его последнего разряда, выход которого соединен с информационным входом первого элемента запрета, управляющий вход которого соединен с выходом первого элемента И, входы которого подключены к нулевым выходам первого и второго триггеров, выход первого элемента запрета является выходом суммы фазоимпульсного сумматора и соединен с нулевым входом третьего триггера, единичный вход которого соединен со входом первого разряда регистра, нулевыми входами первого и второго триггеров и шиной начальной установки сумматора, единичный выход третьего триггера подключен к первому входу второго элемента И, второй вход которого соединен с шиной нулевой константы сумматора, а выход является выходом переноса сумматора, единичные входы первого и второго триггеров соединены соответственно со входами первого и второго слагаемых сумматора, нулевые выходы первого и второго триггеров подключены к первому и второму входам третьего элемента И соответственно, единичные выходы первого и второго триггеров подключены к первому и второму входам четвертого элемента И соответствеиио, третьи входы третьего и четвертого злемеитов И соединены с тактовой шиной сумматора, выход третьего элемента И соединен с управляющим входом сдвига влево регистра, выход четвертого элемента И соединен с информационным входом второго элемента запрета и нулевым входом четвертого триггера, единичный вход которого соединен со входом переноса сумматора, а единичный выход подключен к управляющему входу второго элемента запрета, выход которого соединен с управляющим входом сдвига вправо регистра. На фиг. 1 изображена функциональная схема фазоимпульсного сумматора; на фиг. 2 - временная диаграмма, шипострирующая его работу, при основании системы счисления и при прямом кодировании числовой шформации. Фазоимпульсный сумматор содержит триггер 1 первого слагаемого, триггер 2 второго слагаемого, триггер 3 запоминания сигнала переноса с младшего разряда и триггер 4 формирования сигнала переноса в старший разряд. К нулевым выходам триггеров 1 и 2 подсоединены входы злемента И 5 и входы злемента И 6, а к их единичным выходам подключены входы злемента И 7. Ко входам элементов И 5 и 7 подключена шина тактовых импульсов (ТИ) сумматора. К выходу элемента И 5 входом цепи сдвига на один разряд влево подключен регистр 8, разрядность которого соответствует принятому основанию системы счисления.Вход цепи сдвига на один разряд вправо регистра 8 соединен с выходом элемента 9 запрета,первый вхо которого соединен с выходом злемента И 7 и с нулевым входом триггера 3. Единичный вход триггера 3 соединен с тиной сигнала переноса с младшего разряда Е|, а единичный выход триггера 3 соединен со вторым входом элемента 9 запрета. Единичные входы триггеров 1 и 2 соединены со входами слагаемых х и у сумматора, а нулевые входы триггеров 1 и 2, а также единичный вход триггера 4 и вход первого разряда регистра 8 - с шиной сигнала начальной установки (НУ) сумматора. Выход первого разряда регистра 8 связан со входом его последнего разряда, выход которого соединен с первым входом злемента Ю запрета. Второй вход злемента 10 запрета соединен с выхог дом элемента И 6, а его выход является выходом суммы, на котором формируется сигнал S, и связан с нулевым входом триггера 4. Еди- , ничный выход триггера 4 связан со вторым вхо элемента И 11, первый вход которого соединен с шиной нулевой константы К, а его выход является выходом сигнала переноса в ртарший разряд 1 сумматора. Сумматор работает следующим образом. Работу сумматора рассмотрим при численных значениях слагаемых х-5 и у-7, а также при наличии сигнала переноса с младшего разря С началом работы сигнал НУ, поступающий с периодом 2Т, где Т - длительность опорного периода, и проходящий в момент действия нулевой фазоимпульсной константы К|},устанавли88- 6 ваег ipHirepM I и 2 в нулевое сосшяние, триггер 4 - в единичное состояние и первый разряд регистра 8 - в единичное состояние. В этот же момент времени сигнал переноса с младшего разряда Р поступающий на единичный вход триггера 3, переключает его в единичное состояние. Вслед за этим триггеры 1 и 2 открывают элемент И 5 и на вход цепи сдвига на один разряд влево регистра 8 поступают тактовые импульсы. При этом ранее установленный в первом разряде регистра 8 единичный сигнал передается в его последний разряд и оттуда посредством тактовых импульсов сдвигается в сторону младших разрядов. Так как на второй вход элемента 10 запрета с выхода элемента И 6 поступает запрещающий сигнал, то при передаче единичного сигнала с первого разряда регистра 8 на его последний разряд t на выходе сумматора сигнал отсутствует. С поступлением на сумматор сигнала первого слагаемого (а при фазоимпульсном принципе представления информации сигнал меньшего щюла поступает первым), соответствующий триггер переключается в единичное состояние и элемент И 5 закрывается, а элемент 10 запрета открыт. При этом поступление тактовых импульсов на вход цепи сдвига на один разряд влево регистра 8 прекращается и единичный сигнал в нем не сдвигается. В момент поступления на сумматор сигнала второго слагаемого соответствующий триггер переключается в ещшичное состояние и открывает элемент И 7, Первый тактовый импульс через элемент И 7 поступает на нулевой вход триггера 3, кото- рый до этого момента хранит сигнал переноса с младщего разряда, и ; переключает ; его в нулевое состояние. После этого тактовые импульсы через открытые элемент И 7 и элемент 9 запрета поступают на вход цепи сдвига на один разряд вправо регистра 8 и сдвигают ранее задержанный на определенное количество тактов (в данном случае с учетом единицы переноса с предыдущего разряда - на три такта) единичный сигнал в сторону старших разрядов. При достижении единичным сигналом последнего разряда регистра 8 он через открытый элемент 10 запрета поступает на выходную шину сумматора и на. нулевой вход триггера 4. При одновременном поступлении на сумматор обоих слагаемых, в случае равенства их численных значений, сдвиг единичного сигнала в сторону старших разрядов в регистре 8 начинается через период тактовых импульсов, необходимый для учета единищ.1 переноса с предыдущего разряда. Если результат суммирования двух чисел и единиць переноса с младшего разряда превышает величину основания системы счисления (как в данном случае), то в начале следующего опорного периода форми88руется перенос в старший разряд, так как сигнал Кочерез открытый элемент И 11 проходит на выход переноса сумматора. При этом резуль- тат суммирования формируется во втором опорном периоде. Сигнал суммы переключает тригrep 4 в нулевое состояние и закрывает цепи формирования сигнала переноса в старший разряд. Если же результат суммировашм не превышает величины основания системы счисления, то сигнал суммы появляется на выходе суммы фазоимпульсного сумматора в том же опорном периоде, что и слагаемые. Предлагаемый сумматор, не уступая по быстродействию известному, является более простым Он содержит один регистр, четыре триггера и несколько элементов И, количество которых не увеличивается с возрастанием основания системы счисления. В состав же известного суммато ра входят такие сложные узлы, как преобразова тель фазоимпульсного кода в двоичный позиционный код, сдвигатель, многоразрядный двоичный накапливающий сумматор, дешифратор, каж дый из которых имеет примерно такую же сложность, как регистр предлагаемого сумматора Кроме того, количество некоторых типов логических злементов известного сумматора возрастает с увеличением основания системы счисления. Предлагаемый сумматор может быть использован и как один разряд многразрядного фазоимпульсного сумматора. В таком сумматоре операнды на каждый последующий разряд могут быть поданы только после опорного периода, в котором поступают операнды на предыдущий разряд. При этом в случае формирования сигнала ViepeHoca в предыдущем разряде, он поступает на послед}аощий разряд в опорном периоде поступления операндов этого разряда, что обуславливает правильную работу многоразрядно го сумматора в целом. Таким образом, получается многоразрядный фазовмпульсный сумматор с последовательным переносом. Выработка сигнала переноса на (пИ)-ом такте (п - основание системы счисления) и передаш его в разряд, где в это время формируется сигнал суммы, не вносит искажения в работу всего устройства в целом. В этом случае сигнал переноса Р с предыдущего разряда поступает на единичный вход триггера 3 и переключает его в единичное состояние. При этом элемент 9 запрета закрывается, и блокируется цепь поступления тактовых импульсов на вход цепи сдвига .на один разряд вправо (в сторону старших разрядов) регистра 8. при поступлении обоих операндов на фазоимпульсный сумматор открывается элемент И 7, и при отсутствии сигнала переноса с предьщущего разряда тактовые импульсы через открытый элемент 9 запрета сразу же поступают на вход цепи сдвига на один разряд вправо регистра 8 и сдвигают в нем единичный сигнал в сторону старших разрядов. При наличии сигнала переноса первый из тактовых импульсов через элемент И 7 переключает триггер 3 в нулевое состояние и открывает элемент 9 запрета. В течение одного периода тактовых импульсов, когда осуществляется разблокировка цепи подачи тактовых импульсов на вход цези сдвига на один разряд вправо регистра 8, сдвиг единичного сигнала в нем не производится. Далее очередные тактовые импульсы начинают сдвигать задержанный на один период тактовых импульсов единичный сигнал в сторону старших разрядов регистра 8. Такая задержка сдвига в регистре 8 единичного сигнала учитывается при формировании сигнала , который появляется На выходе сумматора на один период тактовых импульсов позже. При этом при всевозможных комбинациях операндов на входах сумматора результат суммирования всегда получается правильным. Формула изобретения Фазоимпульсный сумматор, содержащий элементы И и триггеры, отличающийс я тем, что, с целью )шрощения, он содержит п-разрядный регистр и элементы запрета (п-основание системы счисления), причем выход первого разряда регистра соединен со входом его последнего разряда, выход которого соединен с информациданым входом йервого элемента запрета, управляющий вход которого соединен с выходом первого элемента И, входы которого подключены к нулевым выходам первого и второго триггеров, выход первого элемента запрета является выходом суммы фазоимпульсного сумматора и соединен с нулевым входом третьего триггера, единичный вход которого соединен со входом первого разряда регистра, нулевыми входами первого и второго триггеров и шиной начальной установки сумматора, единичный выход третьего триггера подключен к первому входу второго элемента И, второй вход которого соединен с щиной нулевой константы сумматора, а вькод является выходом переноса сумматора, единичные входы первого и второго триггеров соединены соответственно со входами первого и второго слагаемых с}гмматора, нулевые выходы первого и второго триггеров подключены к первому и второму входам третьего элемента И соответственно, единичные выходы первого и второго триггеров подключены к первому и второму входам четвертого элемента И соответственно, третьи входы третьего и четвертого элементов И соединены с тактовой щиной

9885996

сумматора, выход третьего элемента И соединен с управляющим входом сдвига влево регистра, выход четвертого элемента И соединен с информационным входом второго элемента запрета и нулевым входом четвертого триггера, j единичный выход которого соединен со входом переноса сумматора, а единичный выход подключен к управляющему входу второго элемента запрета, выход которого соединен с управляющим входом сдвига вправо регистра.

Ко

10

Источники информации, принятые во внимание при экспертизе

.f

Авторы

Даты

1981-11-30—Публикация

1980-02-05—Подача