Изобретение относится к контрольно-измерителъной технике и может быть использовано для контроля генег раторов постоянного тока.

Известен щуп для диагностирования технического состояния дискретных устройств, содержащий коммутаторы, блок перек;точателей, коммутнруйвдий элемент, Д-триггеры, ftS-Tpkrrepu, счетчик, дешифратор, блок индикации tl.

Недостатком известного щупа является сложность, обусловленная необ- ходимос-гью использованяя специальных элементов для установки и стробированйя работы ftS-триггеров. .,

Наиболее близким .к предлагаемому изобретению является пробник для индикации импульсных, сигналов, содержаащй блок стробирования, блок установки, первый и второй инверторы, , образующие RS-триггер., выключатель, индикатор С2. .

Недостатком известного пробника является сложность, обусловленная наличинем блока стробирования ера- батывания RS-триггера, задающего вреMrt, в течение которого он чувствителен к входным импульсньпл сигналам, и наличием блока установки, включающего, выкЛ1очй:тель и специальный вход первого инвертора, ;

Цель изобретения - упрощение кровника. / ,.: ... ., ;.

цортлвленная цель достйГатвтся тем, что и 11 обник для дйагностцрования технического состЬяния источников постоянного тока, срдержгоцнй первый инвертор, соединенный выходом с

10 входом индикатора н входом второго инвертора, введены диод, первый резистор и второй р зистор, соединенный первым выводом с входом проОНика, вторым выводом через первый резистор

15 с вторым входом ycTpioftcTBa и нёпос- . редственно с входом первого инвертог ра и анодом диода, катод которого соединен через выключатель с выхо- . дом ВТОРОГО инйертора.

20

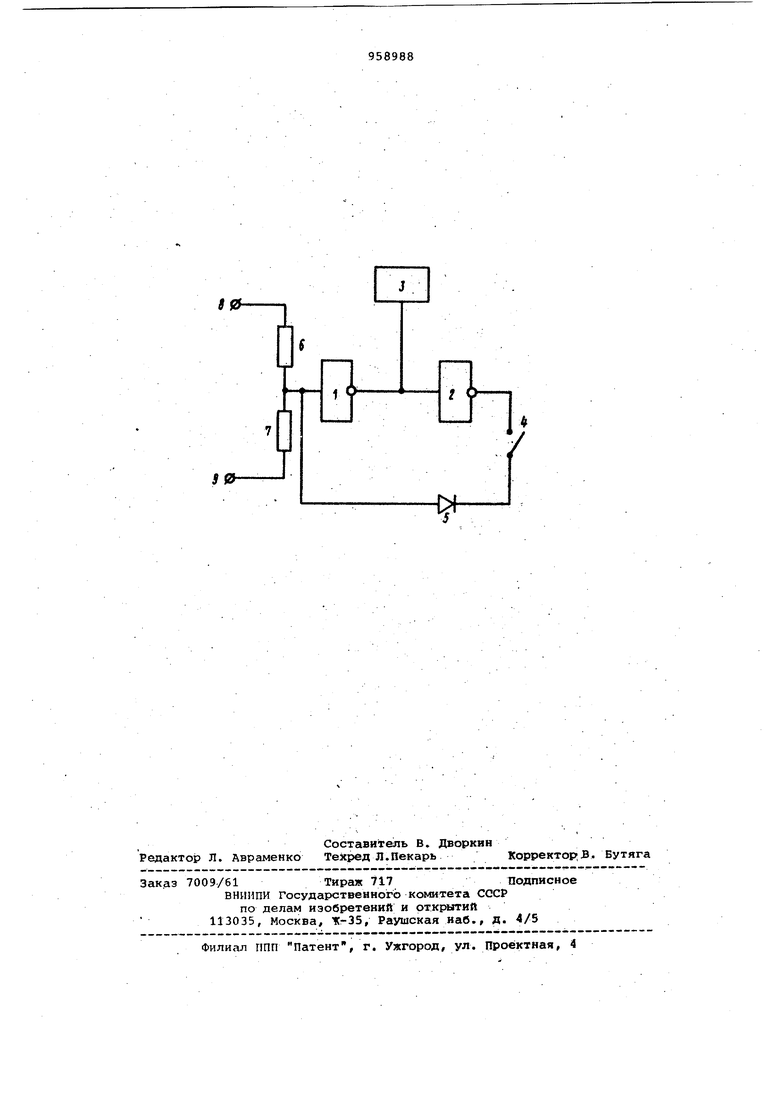

На чертеже показана структурная схема пробника

Прсабник содержит первый инвертор 1, второй инвертор 2, индикатор 3, выключатель 4; диод 5, первый б и

25 второй 7.резисторы, первый 8 и 9 входы.. ... ;

Пробник работает следу ощим обраарм. . .

Входы 8 и 9 пробника подсоединяют30ся к выходным клеммам диагностируеМОго источника, имеющим положительную и отрицательную полярность соответственно. Шина отрицательной поляр ности внутреннего источника, питания пробника, питакяцего инверторы 1 и 2 соединена со входом 9 пробника. В исходном состоянии выключатель 4 размыкает цепь обратной связи с выхода инвертора 2 на вход инвертора 1, что не позволяет им образовать триггер. f Высокий уровень напряжения со входа 8 пробника делится на делителе напряжения, включающем резисторы б и. 7, и, поступая на вход инвертора 1,переводит его в состояние с логическим на выходе, что приводит к загоранию индикатора 3, запиранию инвертора 1, вырабатывающего логичес кую единицу на выходе. Горение индикатора 3 при разомкнутом выключателе свидетельствует о наличии положительного напряжения на входе 8 пробника, при этом кратковременное импульсное снижение этого напряжения не обнаруживается вследствии инерционности индикатора 3. После замыкапия выключателем 4 цепи обратной связи инверторов 1 и 2 они образуют триггер, сохраняющий ранее установленное состояние с логической единицей на выходе инверто ра 2 и логическим нулем на выходе инвертора 1, следовательно размыкание выключателя 4 эквивалентно установке указанного триггера. При кратковременном (импульсном) снижении положительного напряжения На входе 8 до нуля, что .может произ ти, например, при пропадании одной фазы трехфазного переменного напряжения, питающего диагностируемый источник постоянного тока, в случае замкнутого выключателя 4, происходи сброс триггера, образованного инвер торами 1 и 2, в состояние с логичес кой единицей на выходе инвертора 1 и логическим нулем на выходе инвертора 2.. При этом индикатор 3 гаснет сигнализируя о неисправности диагно тируемого источника постоянного ток Диод 5 обеспечивает защиту выход инвертора 2 от кратковременного нулевого уровня, поступающего с входа .8 от неисправного источника постоян ного тока на вход инвертора 1, в те чение времени задержки срабатывания инверторов 1 и 2. Делитель напряжения на резисторах 6 и 7 рассчитывается так, чтобы при логическом нуле на выходе инвертора 2, замкнутом выключателе 4 и положительном уровне напряжения на входе В инвертор 1 находился в запертом состоянии с логической единицей на выходе.. Включение выключателя 4 эквивалентно стробированию приема в триггер из инверторов 1 и 2, так как при замкнутом состоянии выключателя этот триггер фиксирует наличие импульсов нулевого уровня. . Таким образом, введение элементов 4, 5, 6 и 7 позволяет производить установку триггера из инверторов 1 и 2 без специальной схемы установки и специального установочного входа инвертора 2 с помощью выключателя 4, а также стробировать работу триггера на прием кратковременного нулевого сигнала включением выключателя 4 без наличия специального блока стробирования, что существенно упрощает пробник. Формула изобретения .: Пробник для диагностирования техни,ческого состояния источников прстоян.ного тока, содержащий первый инвертор, соединенный выходом с входом индикатора и входом второго инвертора, о тл ич а ющи йся тем, что, с целыэ упрощения пробника, в него введены диод, первый резистор и второй резистор, соединенный первым выводом с входом пробника, вторым выводом через первый резистор - с вторым входом устройства и непосредственно с входом первого инвертора и анодом диода, катод которого соединен через выключатель с выходом второго инвертора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 651276, кл. G 01 R 31/28, 1979. 2.Дятлов Л.И., Мамонов Н.Д. Приборы индикации логических сигналов. Обмен опытом в радиопромышленности, 1978, 8, с. 49 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический пробник | 1980 |

|

SU938221A1 |

| Электрический пробник СИП | 1987 |

|

SU1492317A1 |

| Логический пробник | 1980 |

|

SU917144A1 |

| Устройство для настройки регулятора тока возбуждения тягового дизель-генератора | 1983 |

|

SU1258724A1 |

| Логический пробник | 1981 |

|

SU995030A1 |

| Логический пробник | 1984 |

|

SU1239661A2 |

| СИСТЕМА ОХРАННОЙ СИГНАЛИЗАЦИИ | 1993 |

|

RU2092903C1 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Логический пробник | 1983 |

|

SU1112327A1 |

| Логический пробник | 1983 |

|

SU1158877A1 |

Авторы

Даты

1982-09-15—Публикация

1980-11-21—Подача