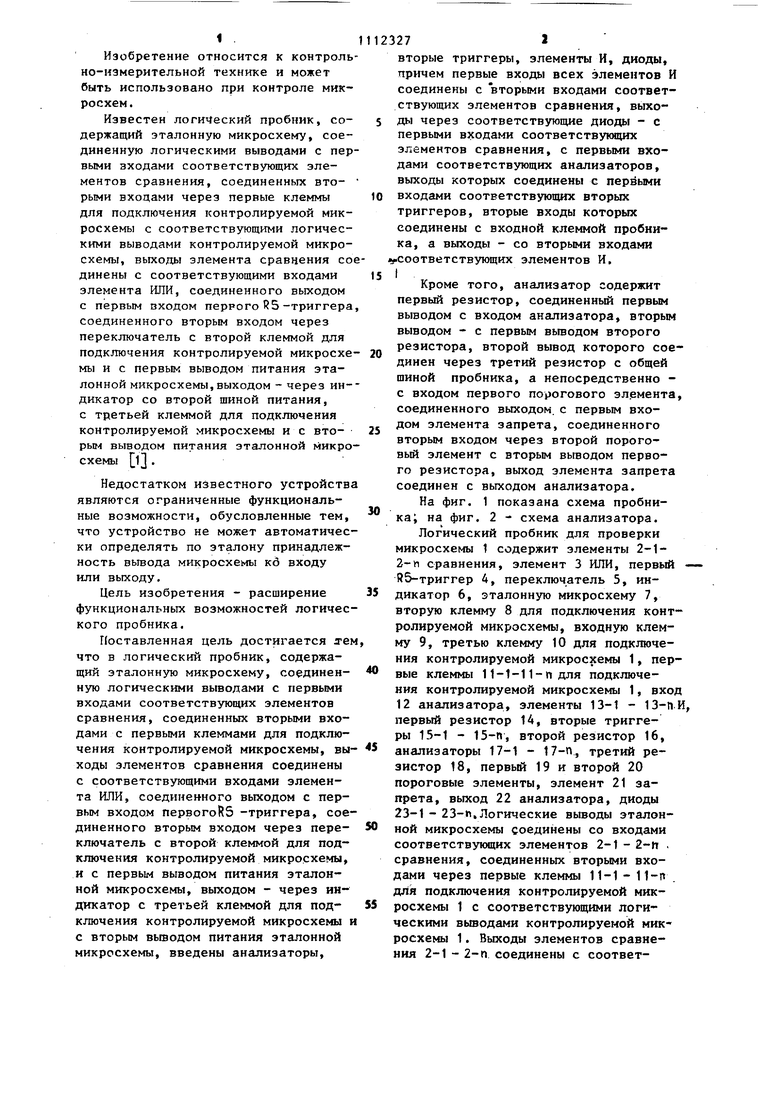

Изобретение относится к контроль но-измерительной технике и может быть использовано при контроле микросхем. Известен логи еский пробник, содержащий эталонную микросхему, соединенную логическими выводами с пер выми входами соответствующих элементов сравнения, соединенных вторыми входами через первые клеммы для подключения контролируемой микросхемы с соответствующими логическими выводами контролируемой микросхемы, выходы элемента сравнения со динены с соответствующими входами элемента ИЛИ, соединенного выходом с первым входом перрого R5-триггера соединенного вторым входом через переключатель с второй клеммой для подключения контролируемой микросхе мы и с первым выводом питания эталонной микросхемы,выходом - через индикатор со второй шиной питания, с третьей клеммой для подключения контролируемой микросхемы и с вторым выводом питания эталонной микро схемы lj . Недостатком известного устройств являются ограниченные функциональные возможности, обусловленные тем, что устройство не может автоматичес ки определять по эталону принадлежность вьтода микросхемы кб входу или выходу. Цель изобретения - расширение функциональных возможностей логичес кого пробника. Поставленная цель достигается я-е что в логический пробник, содержащий эталонную микросхему, соединенную логическими выводами с первыми входами соответствующих элементов сравнения, соединенных вторыми входами с первыми клеммами для подключения контролируемой микросхемы, вы ходы элементов сравнения соединены с соответствующими входами элемента ИЛИ, соединенного выходом с первым входом nepBoroRS -триггера, сое диненного вторым входом через переключатель с второй клеммой для подключения контролируемой микросхемы, и с первым выводом питания эталонной микросхемы, выходом - через индикатор с третьей клеммой для подключения контролируемой микросхемы с вторым вьшодом питания эталонной микросхемы, введены анализаторы. 27I вторые триггеры, элементы И, диоды, причем первые входы всех элементов И соединены с вторыми входами соответствующих элементов сравнения, выходы через соответствующие диоды - с первыми входами соответствуюпщх элементов сравнения, с первыми входами соответствующих анализаторов, выходы которых соединены с первыми входами соответствующих вторых триггеров, вторые входы которых соединены с входной клеммой пробника, а выходы - со вторыми входами соответствующих элементов И, Кроме того, анализатор содержит первый резистор, соединенный первым выводом с входом анализатора, вторым выводом - с первым вьшодом второго резистора, второй вывод которого соединен через третий резистор с общей щиной пробника, а непосредственно с входом первого порогового элемента, соединенного выходом, с первым входом элемента запрета, соединенного вторым входом через второй пороговый элемент с вторым выводом первого резистора, выход элемента запрета соединен с выходом анализатора. На фиг. 1 показана схема пробника; на фиг. 2 - схема анализатора. Логический пробник для проверки микросхемы 1 содержит элементы 2-12-м сравнения, элемент 3 ИЛИ, первый - й5-триггер 4, переключатель 5, индикатор 6, эталонную микросхему 7, вторую клемму 8 для подключения контролируемой микросхемы, входную клемму 9, третью клемму 10 для подключения контролируемой микросхемы 1, первые клеммы 11-1-11-пдля подключения контролируемой микросхемы 1, вход 12 анализатора, элементы 13-1 - 13-пИ, первый резистор 14, вторые триггеры 15-1 - 15-п, второй резистор 16, анализаторы 17-1 - 17-п, третий резистор 18, первый 19 и второй 20 пороговые элементы, элемент 21 запрета, выход 22 анализатора, диоды 23-1 - 23-п.Логические выводы эталонной микросхемы соединены со входами соответствуюпщх элементов 2-1 - 2-п , сравнения, соединенных вторыми входами через первые клеммы 11-1 - 11-п . для подключения контролируемой микросхемы 1 с соответствующими логическими выводами контролируемой микросхемы 1. Выходы элементов сравнения 2-1 - 2-п соединены с соответ3 ствующими входами элемента 3 ИЛИ, соединенного выходом с первым входом первогоКЗ-триггера 4, соединенного вторым входом через переключатель 5 с второй клеммой 8 для подклЬчения контролируемой микросхемы 1, соединенной с первым выводом питания эталонной микросхемы 7, выходом - через индикатор 6 с третьей клеммой 10 для подключения контролируемой микросхемы 1 и с вторым вьгоодом питания эталонной микросхемы 7. Первые входы всех элементов 13-1 - 13-п И соединены со вторыми входами соответствующих элементов 2-1 - 2-п. сравнения, выходы через соответствующие диоды 23-1 - 23-п соединены с первыми входами соответствующих элементов 2-1 - 2-п сравнения с первыми входами соответствующих аналиэаторов 17-1 - 17-л, выходы которых соединены с первыми входами соответствующих вторых триггеров 15-1 - 15-п, вторые входы которых соединены с входной клеммой пробника, а выходы - со вторыми входами соответствующих элементов 13-113- и.

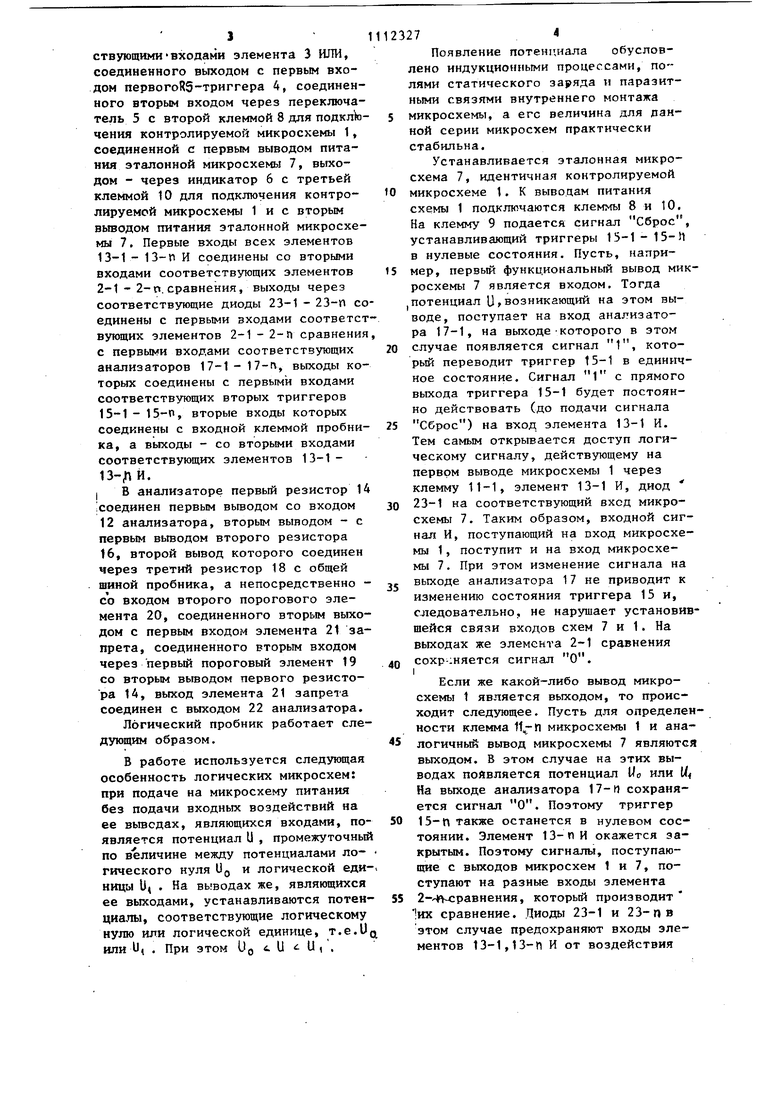

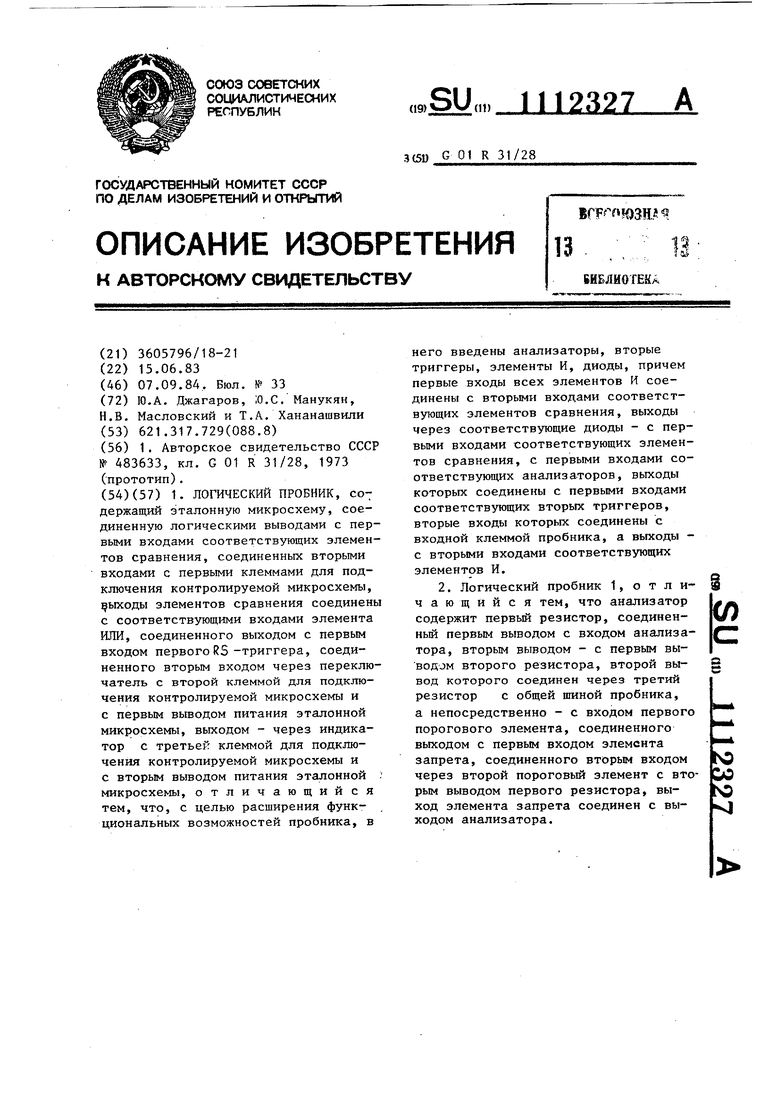

I в анализаторе первый резистор 14 соединен первым выводом со входом 12 анализатора, вторым выводом - с первым вьгеодом второго резистора 16, второй вывод которого соединен через третий резистор 18 с общей шиной пробника, а непосредственно со входом второго порогового элемента 20, соединенного вторым выходом с первым входом элемента 21 запрета, соединенного вторым входом через первый пороговый элемент 19 со вторым вьшодом первого резистора 14, выход элемента 21 запрета соединен с выходом 22 анализатора.

Логический пробник работает следующим образом,

В работе используется следующая особенность логических микросхем: при подаче на микросхему питания без подачи входньк воздействий на ее вьшсдах, являющихся входами, появляется потенциал II , промежуточный по величине между потенциалами логического нуля U и логической единицы U . На выводах же, являющихся ее выходами, устанавливаются потенциалы, соответствующие логическому нулю или логической единице, T.e.U или и, . При этом 0(5 с U U , ,

123274

Появление потенциала обусловлено индукционными процессами, полями статического заряда и паразитными связями внутреннего монтажа

5 микросхетчы, а его величина для данной серии микросхем практически стабильна.

Устанавливается эталонная микросхема 7, идентичная контролируемой

10 микросхеме 1. К выводам питания

схемы 1 подключаются клеммы 8 и 10. На клемму 9 подается сигнал Сброс, устанавливающий триггеры 15-1 - 15-51 в нулевые состояния. Пусть, напри15 мер, первый функциональный вывод микросхемы 7 является входом. Тогда Iпотенциал U возникающий на этом выводе, поступает на вход анализатора 17-1, на выходеКоторого в этом

20 случае появляется сигнал 1, который переводит триггер 15-1 в единичное состояние. Сигнал 1 с прямого выхода триггера 15-1 будет постоянно действовать (до подачи сигнала

25 Сброс) на вход элемента 13-1 И, Тем самым открывается доступ логическому сигналу, действующему на первом выводе микросхемы 1 через клемму 11-1, элемент 13-1 И, диод

30 23-1 на соответствующий вход микросхемы 7, Таким образом, входной сигнал И, поступающий на вход микросхемы 1, поступит и на вход микросхемы 7, При этом изменение сигнала на

,- выходе анализатора 17 не приводит к изменению состояния триггера 15 и, следовательно, не нарушает установившейся связи входов схем 7 и 1, На выходах же элемента 2-1 сравнения

40 сохр-:няется сигнал О.

Если же какой-либо вывод микросхемы 1 является выходом, то происходит следующее, Пусть для определенности клемма 11,-П микросхемы 1 и логичный вывод микросхемы 7 являются выходом. В этом случае на этих выводах появляется потенциал Но или W На выходе анализатора 17-и сохраняется сигнал О. Поэтому триггер

50 15-п также останется в нулевом состоянии. Элемент 13-п И окажется закрытым. Поэтому сигналы, поступающие с выходов микросхем 1 и 7, поступают на разные входы элемента

55 2- сравнения, который производит 1их сравнение. Диоды 23-1 и 23-п в этом случае предохраняют входы элементов 13-1,13-ц И от воздействия

51

сигналов с выхода эталоР1ной микросхемы 7.

После подключения питания клеммами 8 и 10 и подачи сигнала Сброс на клемму 9 происходит автоматическая классификация функциональных выводов микросхем 7 и 1 на входы и выходы. После этого к логическим выводам подключаются клеммы 11-1 - 11-Г1 и однократным замыканием нормально разомкнутого переключателя 5 триггер 4 переводится в единичное состояние. При этом включается индикатор 6, что свидетельствует о наличии питания и земли. Если сигнал на выходе микросхемы 1 не совпадает с аналогичным сигналом микросхемы 7, то на выходе соответствующего элемента 2-1 -2-И сравнения появляется сигнал 1, который через элемент 3 ИЛИ переводит триггер 4 в нулевое состояние. При этом индикатор 6 перейдет в невозбужденное состояние, что свидетелйствует о неисправности схемы. Если сигналы с элементов 2-1-2- п сравнения не поступают, то индикатор 6 остается в возбужденном состоянии, что свидетельствует об исправности микросхемы 1.

12327

Работа анализаторов 17 происходит следующим образом (фиг. 2). Величины резисторов 14, 16 и 18 подбираются таким образом, что при пода5 че на вход 12 потенциала UQ (логический 0) пороговые элементы 19 и 20 не срабатывают и на выходе 22 сохраняется сигнал О. При появлении на входе 12 потенциалаU UQ срабатывает пороговьй элемент 19, а элемент .20 не срабатывает. На прямой вход элемента 21 действует сигнал 1, а на его инверсный вход - сигнал О. Поэтому на выходе 22 появляется сигнал 1. При появлении потенциала Ui (логическая 1) срабатывают пороговые элементы 19 и 20. На оба входа элемента 21 действует сигнал 1, поэтому на его выходе 22 действует сигнал О.

Таким образом, за счет введения анализаторов 17-1 - 17-п,триггеров 15-1 - 15-п, диодов 23-1 - 23-П, элементов 13-1 - 13-пИ обеспечивается автоматическое обнаружение входов и выходов контролируемой микросхемы, что расширяет функциональные возможности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки логических микросхем | 1988 |

|

SU1596291A1 |

| Устройство для контроля интегральных микросхем | 1982 |

|

SU1056089A1 |

| Устройство для контроля микросхем | 1986 |

|

SU1504631A1 |

| Устройство для контроля логических микросхем | 1982 |

|

SU1026096A1 |

| Устройство для контроля микросхем | 1990 |

|

SU1758610A1 |

| Логический пробник | 1990 |

|

SU1839242A1 |

| Устройство для проверки логических микросхем | 1980 |

|

SU918867A1 |

| Устройство для защиты трехфазного электродвигателя с выведенной нейтралью от перегрева | 1988 |

|

SU1607042A1 |

| Логический пробник | 1988 |

|

SU1594459A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

1. ЛОГИЧЕСКИЙ ПРОБНИК, содержащий эталонную микросхему, соединенную логическими выводами с первыми входами соответствующих элементов сравнения, соединенных вторыми входами с первыми клеммами для подключения контролируемой микросхемы, 1 ыходы элементов сравнения соединены с соответствующими входами элемента ИЛИ, соединенного выходом с первым входом первого RS-триггера, соединенного вторым входом через переключатель с второй клеммой для подключения контролируемой микросхемы и с первым выводом питания эталонной микросхемы, выходом - через индикатор с третьей клеммой для подключения контролируемой микросхемы и с вторым выводом питания эталонной микросхемы, отличающийся тем, что, с целью расширения функциональных возможностей пробника, в него введены анализаторы, вторые триггеры, элементы И, диоды, причем первые входы всех элементов И соединены с вторыми входами соответствующих элементов сравнения, выходы через соответствующие диоды - с первыми входами соответствующих элементов сравнения, с первыми входами соответствующих анализаторов, выходы которых соединены с первыми входами соответствующих вторых триггеров, вторые входы которых соединены с входной клеммой пробника, а выходы с вторыми входами соответствующих элементов И. 2. Логический пробник 1, отличающийся тем, что анализатор (Л содержит первый резистор, соединенС ный первым выводом с входом анализатора, вторым выводом - с первым выводом второго резистора, второй вывод которого соединен через третий резистор с общей шиной пробника, а непосредственно - с входом первого порогового элемента, соединенного выходом с первым входом элемента запрета, соединенного вторым входом через второй пороговый элемент с вторым выводом первого резистора, выход элемента запрета соединен с выходом анализатора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логический пробник | 1973 |

|

SU483633A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-09-07—Публикация

1983-06-15—Подача