Изобретение относится к контрольно-измерительной технике и может быть использовано для поиска неисправностей в логических схемных плаTaXi

Известна контрольно-измерительная система для проверки сложных функциональных схем, содержащая за-: датчик тестов, пробники, блок сравнения мини-ЭВМ, блок анализа.

Известная система позволяет локализоват1з неисправности в диагностируемых схемных платах по методу управляемого пробника. В процессе поиска неисправности в цифровой схеме системная программа дает указание оператору подключить пробник к очередной микросхеме на пути, ведущем к началу схемы от выходного контакта с неправильным сигналом. Тестовая программа выполняется снова и измеренный сигнал сравнивается с ожидаемым. Таким образом можно обнаружить микросхему, имеющую пра вильные входные и неправильные выходные сигналы. К базовым данным, необходимым для управляющего пробником программного обеспечения, относятся описание диагностируемой

схемы и таблица правильных реакций для всех ее узлов 1.

Недостатком известной системы является сложность, обусловленная наличием мини-ЭВМ и необходимостью использования ряда блоков для задания и анализа регулярных тестов.

Наиболее близким техническим решением к предлагаемому является уст10ройство для поиска кратных дефектов, содержащее пробники, блок управления, счетчик тактов, дешифратор, первый триггер, генератор псевдослучайных кодов, элемент несовпа15дения, элемент ИЛИ, индикаторы несовпадения и индикатор исправности.

Для работы известного устройства не требуется составление тестовых последовательностей и расчет пра20вильных реакций в различных точках диагностируемой схемы 2.

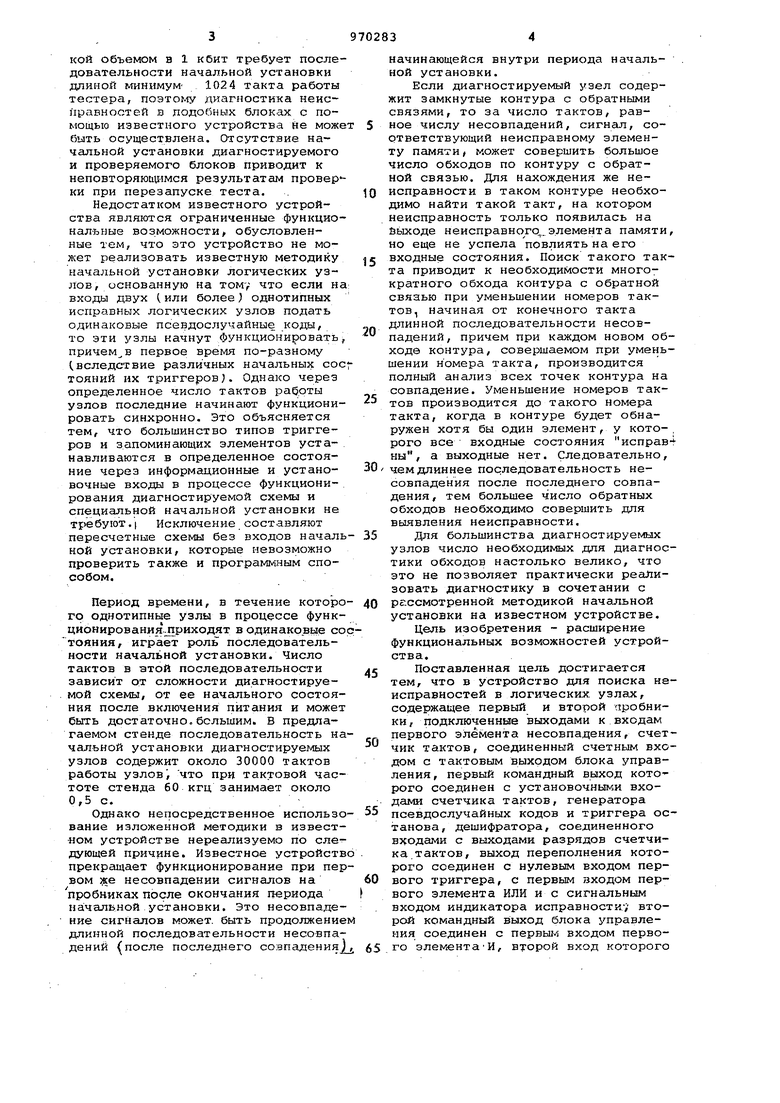

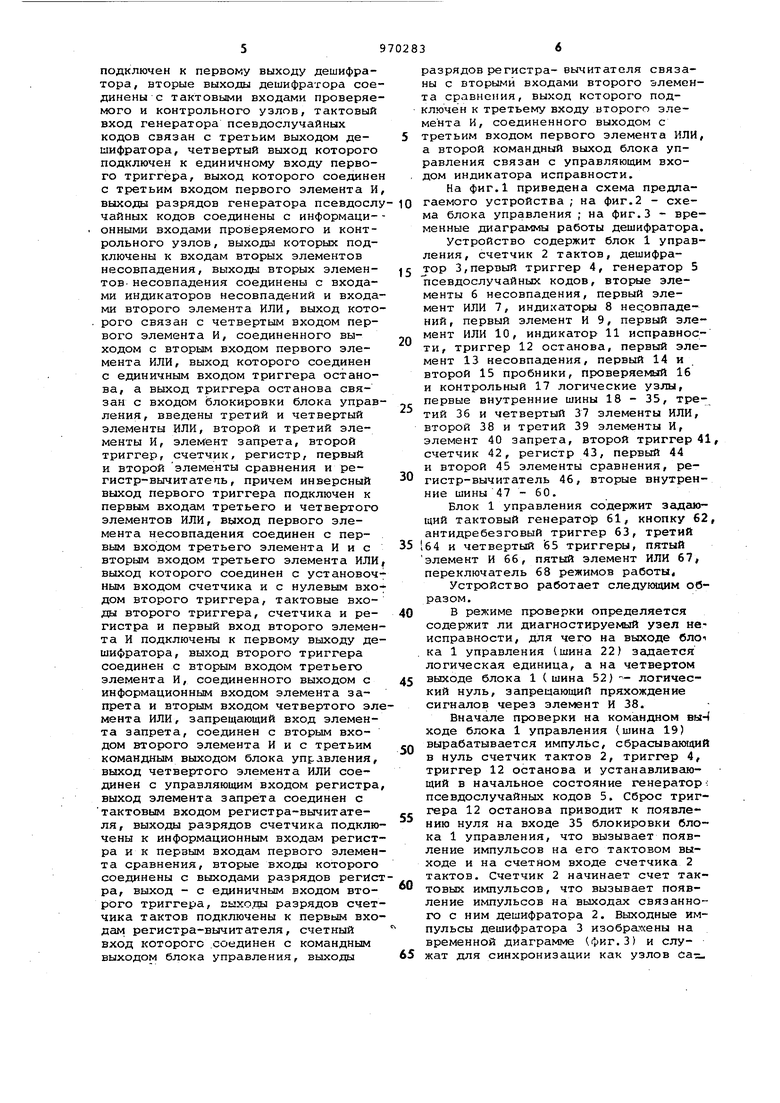

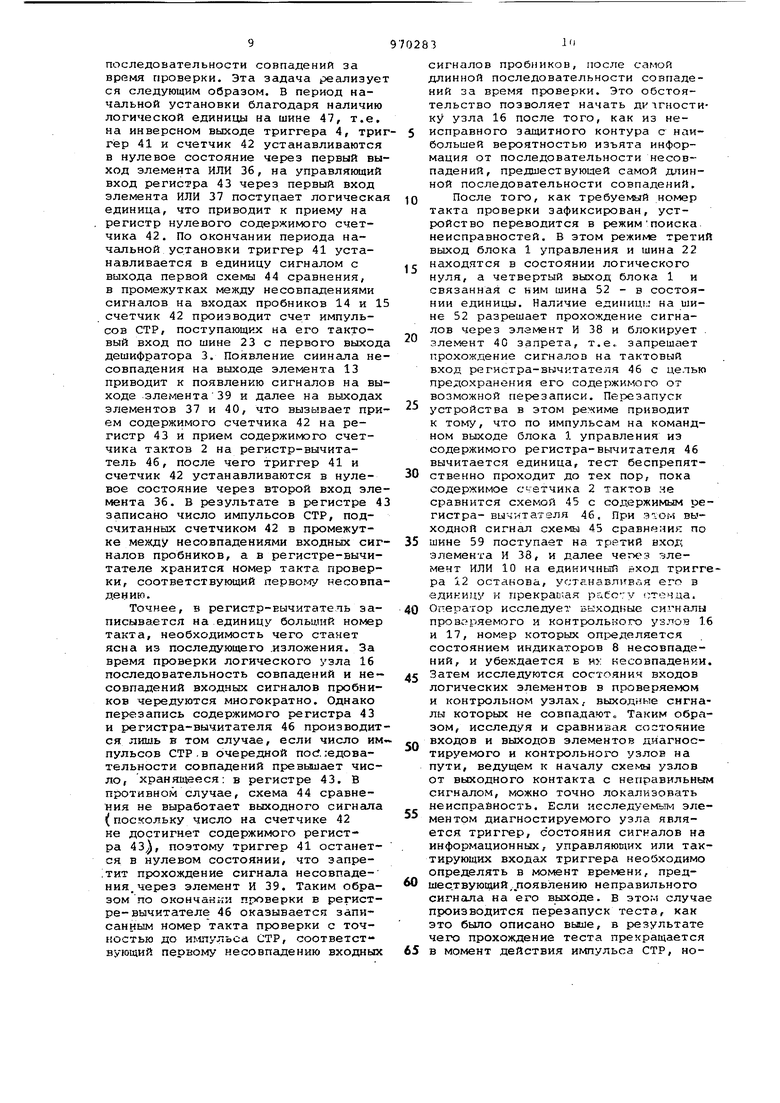

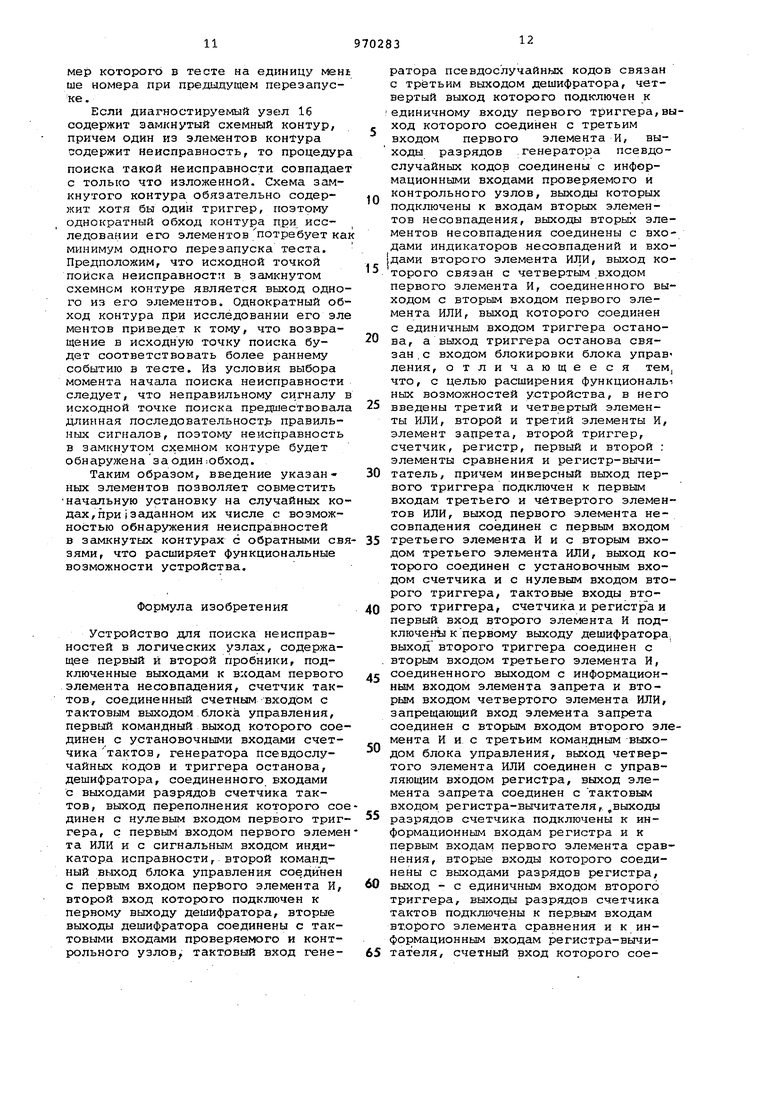

Однако процедура поиска неисправностей, реализованная в известном устройстве, требует наличие цепи на25чального установа у всех триггеров диагностируемого блока, что значительно суживает номенклатуру диагностируемых блоков. Например, наличие в диагностируемом блоке мик30росхем памяти с произвольной выборкой объемом в 1 кбит требует после довательности начальной установки длиной МИНИМУМ 1024 такта работы тестера, поэтому диагностика неисправностей в подобных блоках с помощью известного устройства йе мож быть осуществлена. Отсутствие начальной установки диагностируемого и проверяемого блоков приводит к неповторяюишмся результатам провер ки при перезапуске теста. . Недостатком известного устройства являются ограниченные функцио нальные возможности, обусловленные тем, что это устройство не может реализовать известную методику начальной установки логических узлов, основанную на тому что если н входы двух (или более) однотипных исправных логических узлов подать одинаковые псевдослучайные коды, то эти узлы начнут функционировать причем в первое время по-разному (.вследствие различных начальных coc тояний их триггеров к Однако через определенное число тактов работы узлов последние начинают функционировать синхронно. Это объясняется тем, что большинство типов триггеров и запоминающих элементов устанавливаются в определенное состояние через информационные и установочные входы в процессе функционирования диагностируемой схемы и специальной начальной установки не требуют. I Исключение составляют пересчетные схемы без входов начал ной установки, которые невозможно проверить также и програм шым способом. Период времени, в течение которо го однотипные узлы в процессе функционнрованиялтриходят в одинаковые со тояния, играет роль последовательности начальной установки. Число тактов в этой последовательности зависит от сложности диагностируемой схемы, от ее начального состояния после включения питания и может Сыть достаточно,большим. В предлагаемом стенде последовательность на чальной установки диагностируег/1ых узлов содержит около 30000 тактов работы узлов , что при тактовой частоте стенда 60 кгц занимает около 0,5 с.Однако непосредственное использо вание изложенной методики в известном устройстве нереализуемо по следующей причине. Известное устройств прекращает функционирование при пер вом :«е несовпадении сигналов на пробниках после окончания периода на чальной установки. Это несовпадение сигналов может, быть продолжение Д.ПИННОЙ последовательности несовпадений (после последнего со:ападения начинающейся внутри периода начальной установки. Если диагностируемый узел содержит замкнутые контура с обратными связями, то за число тактов, равное числу несовпадений, сигнал, соответствующий неисправному элементу памяти, может совершить большое число обходов по контуру с обратной связью. Для нахождения же неисправности в таком контуре необходимо найти такой такт, на котором неисправность только появилась на Вьоходе неисправно го. элемент а памяти, но еще не успела повлиять на его входные состояния. Поиск такого такта приводит к необходимости многократного обхода контура с обратной связью при уменьшении номеров тактов, начиная от конечного такта длинной последовательности несовпадений , причем при каждом новом обходе контура, совершаемом при уменьшении номера такта, производится полный анализ всех точек контура на совпадение. Уменьшение номеров тактов производится до такого номера такта, когда в контуре будет обнаружен хотя бы один элемент, у кото-, рого все входные состояния исправ4 ны, а выходные нет. Следовательно, чем длиннее последовательность несовпадения после последнего совпадения, тем большее число обратных обходов необходимо совершить для выявления неисправности. Для большинства диагностируемых узлов число необходимых для диагностики обходов настолько велико, что это не позволяет практически реализовать диагностику в сочетании с рессмотренной методикой начальной установки на известном устройстве. Цель изобретения - расширение функциональных возможностей устройства. Поставленная цель достигается тем/ что в устройство для поиска неисправностей в логических, узлах, содержащее первый и второй пробники, подключенные выходами к входам первого элемента несовпадения, счетчик тактов, соединенный счетным входом с тактовым выходом блока управления, первый командный выход которого соединен с установочными входами счетчика тактов, генератора псевдослучайных кодов и триггера останова, дешифратора, соединенного входами с выходами разрядов счетчика, т актов, выход переполнения которого соединен с нулевым входом первого триггера, с первым входом первого элемента ИЛИ и с сигнальным входом индикатора исправности-;- второй командный выход блока управления соединен с первьи входом первого элементами, второй вход которого подключен к первому выходу дешифратора, вторые выходы дешифратора сое динены с тактовыми входами проверяе мого и контрольного узлов, тактовый вход генератора псевдослучайных кодов связан с третьим выходом дешифратора, четвертый выход которого подключен к единичному входу первого триггера, выход которого соедине с третьим входом первого элемента И выходы разрядов генератора псевдосл чайных кодов соединены с информационными входами проверяемого и контрольного узлов, выходы которых подключены к входам вторых элементов несовпадения, выходы вторых элементов- несовпадения соединены с входами индикаторов несовпадений и входа ми второго элемента ИЛИ, выход кото рого связан с четвертым входом первого элемента И, соединенного выходом с вторым входом первого элемента ИЛИ, выход которого соединен с единичным входом триггера останова, а выход триггера останова связан с входом блокировки блока управ ления, введены третий и четвертый элементы ИЛИ, второй и третий элементы И, элемент запрета, второй триггер, счетчик, регистр, первый и второй элементы сравнения и регистр-вычитатепь, причем инверсный выход первого триггера подключен к первым входам третьего и четвертого элементов ИЛИ, выход первого элемента несовпадения соединен с первым входом третьего элемента И и с вторым входом третьего элемента ИЛИ выход которого соединен с установоч ным входом счетчика и с нулевым вхо дом второго триггера, тактовые входы второго триггера, счетчика и регистра и первый вход второго элемен та И подключены к первому выходу де шифратора, выход второго триггера соединен с вторым входом третьего элемента И, соединенного выходом с информационным входом элемента запрета и вторым входом четвертого эл мента ИЛИ, запрещающий вход элемента запрета, соединен с вторым входом второго элемента И и с третьим командным выходом блока управления, выход четвертого элемента ИЛИ соединен с управляющим входом регистра выход элемента запрета соединен с тактовым входом регистра-вычитателя, выходы разрядов счетчика подклю чены к информационным входам регист ра и к первым входам первого элемен та сравнения, вторые входы которого соединены с выходами разрядов регис ра, выход - с единичным входом второго триггера, выходы раэрядов счет чика тактов подключены к первым вхо дам регистра-вычитателя, счетный вход которого .соединен с командным выходом блока управления, выходы разрядов регистра- вычитателя связаны с вторыми входами второго элемента сравнения, выход которого подключен к третьему входу второго элемента И, соединенного выходом с третьим входом первого элемента ИЛИ, а второй командный выход блока управления связан с управляю аим входом индикатора исправности. На фиг.1 приведена схема предлагаемого устройства ; на фиг.2 - схема блока управления ; на фиг.З - временные диаграммы работы дешифратора. Устройство содержит блок 1 управления, счетчик 2 тактов, дешифратор 3,первый триггер 4, генератор 5 севдослучайных кодов, вторые элементы 6 несовпадения, первый элемент ИЛИ 7, индикаторы 8 нес овпадений, первый элемент И 9, первый элемент ИЛИ 10, индикатор 11 исправности, триггер 12 останова, первый элемент 13 несовпадения, первый 14 и второй 15 пробники, проверяемый 16 и контрольный 17 логические узлы, первые внутренние шины 18 - 35, третий 36 и четвертый 37 элементы ИЛИ, второй 38 и третий 39 элементы И, элемент 40 запрета, второй триггер 41, счетчик 42, регистр 43, первый 44 и второй 45 элементы сравнения, регистр-вычитатель 46, вторые внутренние шины 47 - 60. Блок 1 управления содержит задгиощий тактовый генератор 61, кнопку 62, антидребезговый триггер 63, третий б4 и четвертый 65 триггеры, пятый элемент И 66, пятый элемент ИЛИ 67, переключатель 68 режимов работы. Устройство работает следующим образом. В режиме проверки определяется содержит ли диагностируемый узел неисправности, для чего на выходе блоч ка 1 управления шина 22) задается логическая единица, а на четвертом выходе блока 1 ( шина 52) - логический нуль, запрещающий пряхождение сигналов через элемент И 38. Вначале проверки на командном выходе блока 1 управления (шина 19) вырабатывается импульс, сбрасывающий в нуль счетчик тактов 2, триггер 4, триггер 12 останова и устанавливгиощий в начальное состояние генератор-: псевдослучайных кодов 5. Сброс триггера 12 останова приводит к появлению нуля на входе 35 блокировки блока 1 управления, что вызывает появление импульсов на его тактовом выходе и на счетном входе счетчика 2 тактов. Счетчик 2 начинает счет тактовых импульсов, что вызывает появление импульсов на выходах связанного с ним дешифратора 2. Выходные импульсы дешифратора 3 изобра1т ены на временной диагра1-1ме (фиг.З) и служат для синхронизации как узлов Са-г.

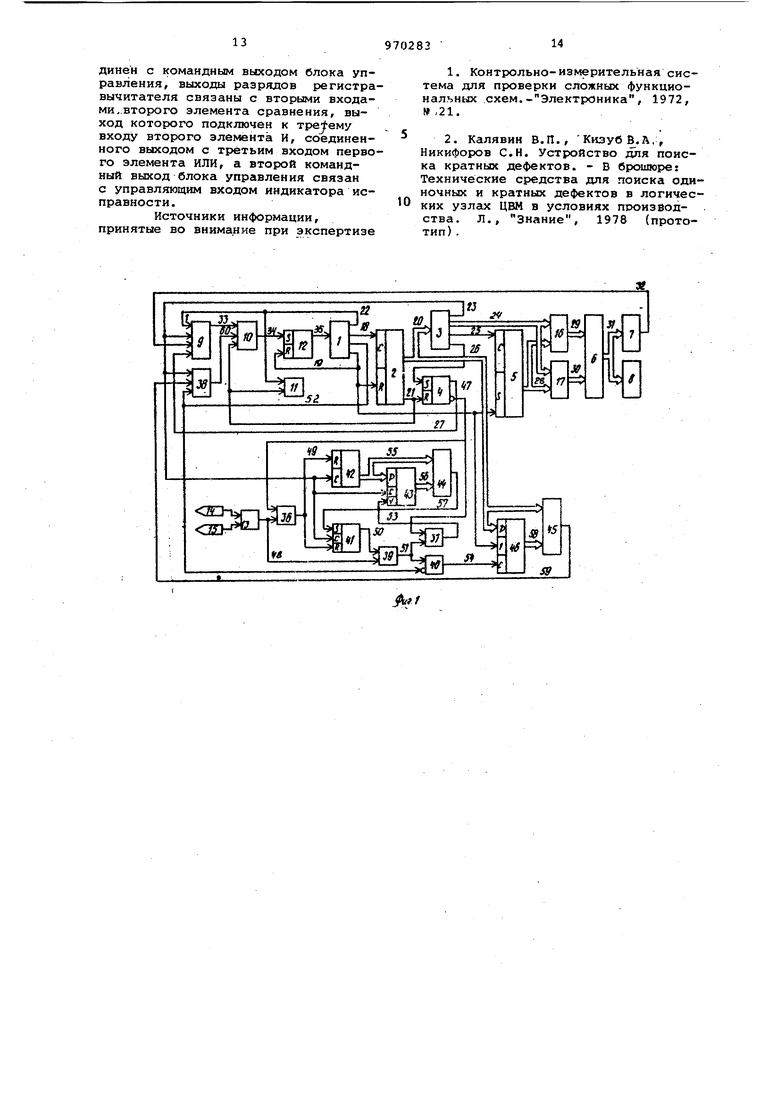

мого стенда, так и проверяемого контрольного) узлов. На этой диаграмме СТР-стробсигно1л стенда, вырабатываемый первым выходом дешифратора 3 и используемый для стробирования, по шине 23 триггера 12 оста нова,второго триггера 41, счетчика 42 и регистра 43, СИ1-СИ4-синхроимпульсы, формируемые второй группой выходов дешифра,тора 3 для синхронизации проверяемого 16 и контрольного 17 узлов по шинам 24, - СДВИГ - тактирующие импульсы генератора 5 псевдослучайных кодов.

Наличие импульсных сигналов на выходах дешифратора 3 приводит к периодической смене выходных кодов генератора 5 и функционированию проверяемого и контрольного узлов 16 и 17.

Проверка логических узлов устройством производится потактно. Каждый такт проверки включает в себя смену выходного кода генератора 5 и прохождение синхроимпульсов СИ1СИ4 на тактовые входы проверяемого и контрольных узлов. Рарположение стробсигналов СТР стенда по отношеНию к синхроимпульсам СИ1-Си4, как это показано на диаграмме фиг.З, позволяет учесть все возможные неисправности в проверяемом узле. Счет чик 2 тактов не только производит счет тактов проверки, но и формирует временную диаграмму сигналов внут ри ка кдого такта.

Триггер 4 вырабатывает на своем выходе сигнал РЛЗРЕШЕНИЕ ПРОВЕРКИ, который по шине 27 поступает на третий вход элемента И 9. Триггер 4 устанавливается в единицу импульсом с четвертого выхода дешифратора 3, который формируется спустя приблизительно 30000 тактов работы стенда с начала проверки, сброс триггера 4 осуществляется сигналом переполне.ния счетчика 2 тактов но окончании проверки. Возможные несовпадения сигналов на выходах проверяемого и контрольного узлов не могут произвести останова стенда в течение периода начальной установки узлов, поскольку третий вход элемента 9 заблокирован в это время логическим нулем.

Если проверяемый узел 16 содержит неисправность, то по окончании периода начальной установки это прО явится : в несовпадении сигналов на какой-либо паре выходов проверяемого 16 и контрольного 17 узлов. Сигнал несовпадения, сформированный соответствующим элементом несовпадения 6, поступает на соответствующий вход индикатора 8 несовпадения, а также через ИЛИ 7 на четвертый вход элемента И 9. Будучи простробированным импульсом СТР, сигнал несовпадения пройдет через элементы 9 и 10 на единичный вход триггера 12 останова, что вызовет появление единицы на входе блокировки блока 1 управления и прекращение поступления TaKTOBfc)ix импульсов на счетный вход счетчика 2 тактов. В результате работа устройства прекращается, а по состоянию индикатора несовпадений 8 можно определить номер выхода проверяемого узла 16 с неправильным выходным сигналом.

Если проверяемый узел 16 идентичен контрольному узлу 17, то работа устройства прекратится по окончании проверки, когда на выходе переполнения счетчика 2 тактов сформируется сигнал переполнения. Этот сигнал по шине 21 поступит на сигнальный вход индикатора 11 исправности, а также через элемент ИЛИ 10 на единичный вход триггера 12 остано ва, что вызовет прекращение работы стенда, по состоянию индикатора исправности 11 можно судить об исправности проверяемого узла.

Если факт наличия неисправности в проверяемом узле 16 установлен и номер неисправного выхода известен, то устройство переводится в режим поиска и запоминания надлежащего номера такта проверки, начиная с которого в дальнейшем будет производиться поиск неисправности. В этом режиме на третьем и четвертом выходах блока 1 управления, т.е. на шинах 22 и 52, устанавливаются значения логических нулей. Оператор устанавливает пробники 14 и 15 на выходы проверяемого 16 и контрольного 17 узлов, номер которых определяется состоянием индикаторов несовпадений 8, после чего на командном выходе блока 1 управления формируется пусковой импульс и стенд отрабатывает диаграмму сигналов проверки до ее окончания таким же образом, как это описано выше. Однако в этом режиме преждевременный останов стенда Невозможен, поскольку элементы И 9 и 38 заблокирюваны нулевыми :-начения ми сигналов на шинах 22 и 52. Невозможно также срабатывание индикатора 11 исправности благодаря наличию логического нуля на его управляюheM входе.

При работе стенда в режиме поиска и запоминания номера такта проверки на выходе элемента, 1. несовпадения присутствуют сигналы, представ ляющие собой последовательность несовпаде.ний входных сигналов пробников 14 и 15. Задача блока управления перезапуском теста в этом режиме заключается в определении и запоминании такого номера такта проверки, в котором произошло первое несовпадение входных сигналов пробников 14 и 15 после самой длинной

последовательности совпадений за вркмя проверки. Эта задача реализует ся следующим образом. В период начальной установки благодаря наличию логической единицы на шине 47, т.е. на инверсном выходе триггера 4, триггер 41 и счетчик 42 устанавливаются в нулевое состояние через первый выход элемента ИЛИ 36, на управляющий вход регистра 43 через первый вход элемента ИЛИ 37 поступает логическая единица, что приводит к приему на регистр нулевого содержимого счетчика 42. По окончании периода начальной установки триггер 41 устанавливается в единицу сигналом с выхода первой схемы 44 сравнения, в промежутках между несовпадениями сигналов на входах пробников 14 и 15 счетчик 42 производит счет импульсов СТР, поступающих на его тактовый вход по шине 23 с первого выхода дешифратора 3. Появление сиинала несовпадения на выходе элеьданта 13 приводит к появлению сигналов на выходе элемента39 и далее на выходах элементов 37 и 40, что вызывает прием содержимого счетчика 42 на регистр 43 и прием содержимого счетчика тактов 2 на регистр-вычитатель 46, после чего триггер 41 и счетчик 42 устанавливаются в нулевое состояние через второй вход элемента 36. В результате в регистре 43 записано число импульсов СТР, подсчитанных счетчиком 42 в промежутке между несовпадениями входных сигналов пробников, а в регистре-вычитателе хранится номер такта проверки, соответствующий перво ту несовпадению.

Точнее, в регистр-вычитатель записывается на единицу больший номер такта, необходимость чего станет ясна из последующего .изложения. За время проверки логического узла 16 последовательность совпадений и несовпадений входных сигналов прюбников чередуются многократно. Однако перезапись содержимого регистра 43 и регистра-вычитателя 46 производится лишь в том случае, если число им пульсов СТР,в очередной nocf.:едовательности совпадений превышает число, хранящееся; в регистре 43. В пЕютивном случае, схема 44 сравнения не выработает выходного сигнала (поскольку число на счетчике 42 ке достигнет содержимого регистра 43, поэтому триггер 41 останется в нулевом состоянии, что запре;тит прохождение сигнала несовпадения, через элемент И 39. Таким образом по окончании проверки в регистре- вычитателе 46 оказывается записанным номер такта проверки с точностью до имлульса СТР, соответствующий первому несовпадению входных

сигналов пробников, после самой длинной последовательности совпадений за время проверки. Это обстоятельство позволяет начать диагностику узла 16 после того, как из неисправного Зсицитного контура с наибольшей вероятностью изъята информация от последовательности несовпадений, предшествующей самой длинной последовательности совпадений. После того, как требуемый HONKP

0 такта проверки зафиксирован, устрюйство переводится в режимпоиска неисправностей. В этом режиме третий выход блока 1 управления и шина 22 находятся в состоянии логического

5 нуля, а четвертый выход блока 1 и связанная с ним шина 52 - в состоянии единицы. Наличие едипицк; на шине 52 разрешает прохождение сигналов через элемент И 38 и блокирует .

0 элемент 40 запрета, т.е.. запрещает прохождение сигналов на тактовый вход регистра-вычитателя 46 с целью предохранения его содержимого от возможной перезаписи. Перезапуск

5 устройства в этом приводит к тому, что по импульсам на командном выходе блока 1 управления из содержимого регистра-вычитателя 46 вычитается единица, тест беспрепят0ственно проходит до тех пор, пока содержимое счетчика 2 тактов не сравнится схемой 45 с содержимым регистра- вычитатзля 46. При этом выходной сигнал схемы 45 сравнемик по

5 шине 59 поступает на третий вход элемента И 38, и далее чепез элемент ИЛИ 10 на единичный йход триггера 12 останова, устанаБ.п1твая его в единицу и прекращая рае о .у отечца. Оператор исследует выходные сигналы

0 проверяемого и контрольного узлов 16 и 17, номер которых определяется состоянием индикаторов 8 несовпадений, и убеждается в кесовпадекии. Затем исследуются состояние входов

5 логических элементов в проверяемом и контрольном уэлах, выходные сигналы которых не совпадают Таким образом, исследуя и сравнивая состояние входов и выходов элементов диагнос0тируемого и контрюльного узлов на пути, ведущем к началу схемы узлов от выходного контакта с неправильным сигналом, можно точно локализовать неиспрайность. Если исследуемым эле5ментом диагностируемого узла является триггер, состояния сигналов на информационных, управляющих или тактирующих входо1Х триггера необходимо определять в момент времени, пред0шес.твующий,,появлению неправильного сигнала на его выходе, в этом случае производится перезапуск теста, как это бъто описано выше, в результате чего прохождение теста прекращается

5 в момент действия импульса СТР, номер которого в тесте на единицу мень ше номера при предыдущем пефезапуске.

Если диагностируемый узел 16 содержит замкнутый схемный контур, причем один из элементов KOHtypa содержит неисправность, то процедура

поиска такой неисправности совпадает с только что изложенной. Схема замкнутого контура обязательно содержит хотя бы один триггер, поэтому однократный обход контура при исследовании его элементовпотребует как минимум одного перезапуска теста. Предположим, что исходной точкой поиска неисправности в замкнутом схемном контуре является выход одного из его элементов. Однократный обход контура при исследовании его эле ментов приведет к тому, что возвращение в исходную точку поиска будет соответствовать более раннему событию в тесте. Из условия выбора момента начала поиска неисправности следует, что неправильному сигналу в исходной точке поиска предаюствовала длинная последовательности правильных сигналов, поэтому неисправность в замкнутом схемном контуре будет обнаружена за один юбход.

Таким образом, введение указанных элементов позволяет совместить начальную установку на случайных кодах, при (заданном их числе с возможностью обнаружения неисправностей в замкнутых контурах с обратными связями, что расширяет функциональные возможности устройства.

Формула изобретения

Устройство для поиска неисправностей в логических узлах, содержащее первый и второй пробники, подключенные выходами к входам первого элемента несовпадения, счетчик тактов, соединенный счетным входом с тактовым выходом блока управления, первый командный выход которого соединен с установочными входами счетчика тактов, генератора псевдослучайных кодов и триггера останова, дешифратора, соединенного входами с выходами разрядоЁ счетчика тактов, выход переполнения которого содинен с нулевым входом первого триггера, с первым входом первого элеме та ИЛИ и с сигнальным входом индикатора исправности, второй командный выход блока управления соединен с первыгд входом первого элемента И, второй вход которого подклк1чен к первому выходу дешифратора, вторые выходы дешифратора соединены с тактовыми входами проверяемого и контрольного узлов тактовый вход генератора псевдослучайных кодов связан с третьим выходом дешифратора, четвертый выход которого подключен к

;единичному входу первого триггера,выход которого соединен с третьим входом первого элемента И, выходы разрядов генератора псевдослучайных кодов соединены с информационными входами проверяемого и контрольного узлов, выходы которых подключены к входам вторых элементов несовпадения, выходы вторых элементов несовпадения соединены с входами индикаторов несовпадений и второго элемента ИЛИ, выход которого связан с четвертым входом первого элемента И, соединенного выходом с вторым входом первого элемента ИЛИ, выход которого соединен с единичным входом триггера останова, а выход триггера останова связан ,с входом блокировки блока управ ления, отличающееся тем, что, с целью расширения функционалы ных возможностей устройства, в него введены третий и четвертый элементы ИЛИ, второй и третий элементы И, элемент запрета, второй триггер, счетчик, регистр, первый и второй ; элементы сравнения и регистр-вычитатель, причем инверсный выход первого триггера подключен к первым входам третьего и четвертого элементов ИЛИ, выход первого элемента несовпадения соединен с первым входом третьего элемента И и с вторым входом третьего элемента ИЛИ, выход которого соединен с установочным входом счетчика и с нулевым входом второго триггера, тактовые входы второго триггера, счетчика и регистра и первый вход второго элемента И подключе нЬ к первому выходу дешифратора, выход второго триггера соединен с вторым входом третьего элемента И, соединенного выходом с информационным входом элемента запрета и вторым входом четвертого элемента ИЛИ, запрещающий вход элемента запрета соединен с вторым входом второго элемента И и с третьим командным выходом блока управления, выход четвертого элемента ИЛИ соединен с управляющим входом регистра, выход элемента запрета соединен с тактовым входом регистра-вычитателя, ,выходы разрядов счетчика подключены к информационным входам регистра и к первым входам первого элемента сравнения, вторые входы которого соединены с выходами разрядов регистра, выход - с единичным входом второго триггера, выходы разрядов счетчика тактов подключены к первым входам второго элемента сравнения и к информационным входам регистра-вычитателя, счетный вход которого соединен с командным выходом блока управления, выходы разрядов регистравычитателя связаны с вторыми входами, второго элемента сравнения, выход которого подключен к входу второго элемента и, соединенного выходом с третьим входом первого элемента ИЛИ, а второй командный выход блока управления связан с управляющим входом индикатора исправности.

Источники информации, принятые во внимание при экспертизе

1.Контрольно-измерительная система для проверки сложных функциональных схем.- Электроника, 1972,

W.21.

2.Калявин В.П., КизубВ.Д,, Никифоров С.Н. Устройство для поиска кратных дефектов. - в брошюре: Технические средства для поиска одиночных и кратных дефектов в логических узлах ЦВМ в условиях производства, л., Знание, 1978 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Логический пробник | 1986 |

|

SU1352420A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU993168A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Устройство для нахождения кратных неисправностей в схемах цвм | 1974 |

|

SU533894A1 |

| Устройство для диагностики неисправностей цифровых блоков | 1981 |

|

SU1024925A1 |

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

| Устройство для поиска дефектов цифровых узлов | 1985 |

|

SU1302282A2 |

стр JJlJUrUIJLJLJlJL

Авторы

Даты

1982-10-30—Публикация

1981-04-29—Подача