(St) СЧЕТНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Система автоматического пожаротушения | 1987 |

|

SU1461486A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1987 |

|

SU1442047A1 |

| Датчик испытательных текстов | 1988 |

|

SU1571786A1 |

| Многодвигательный электропривод переменного тока | 1985 |

|

SU1307521A1 |

| Устройство для ввода информации | 1980 |

|

SU926647A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1991 |

|

SU1832976A1 |

| Устройство для ввода информации | 1982 |

|

SU1056175A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией | 1984 |

|

SU1185604A1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2011 |

|

RU2494006C2 |

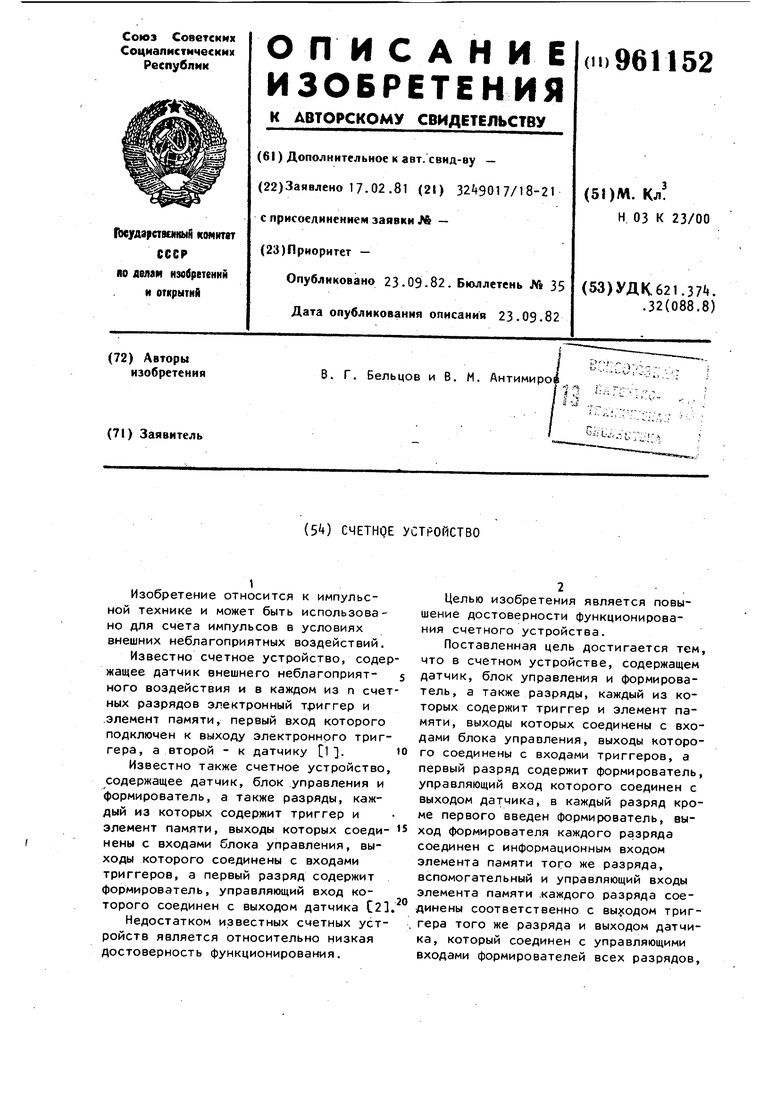

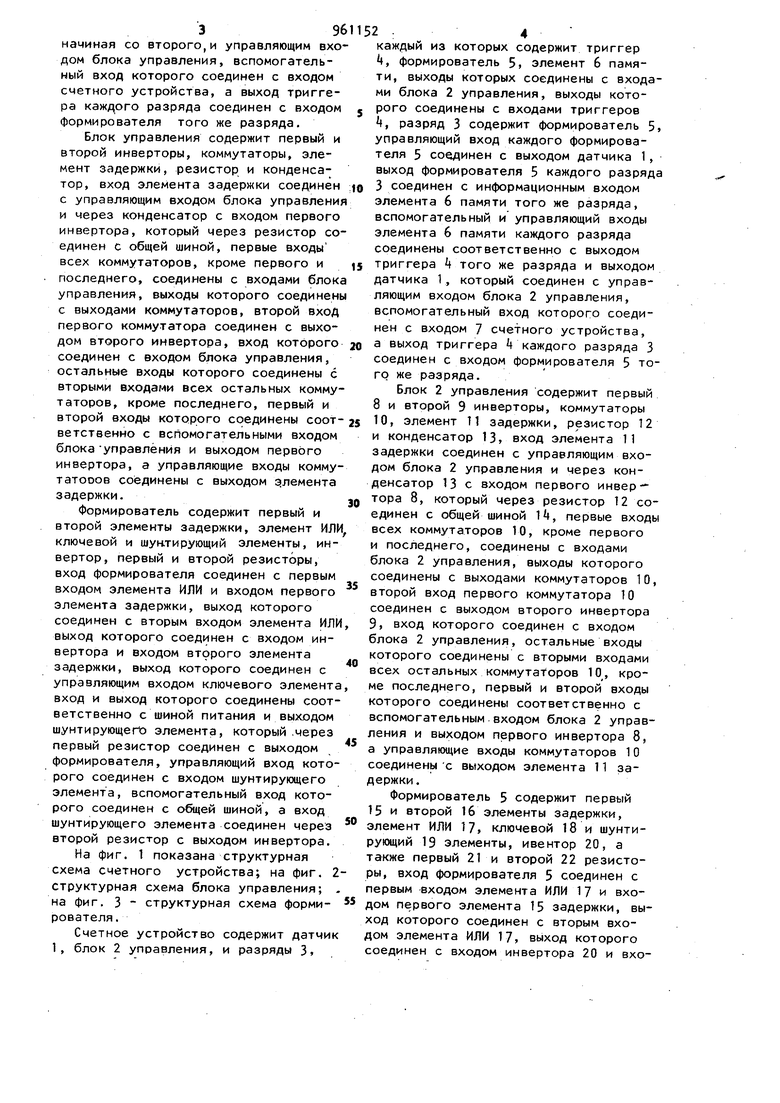

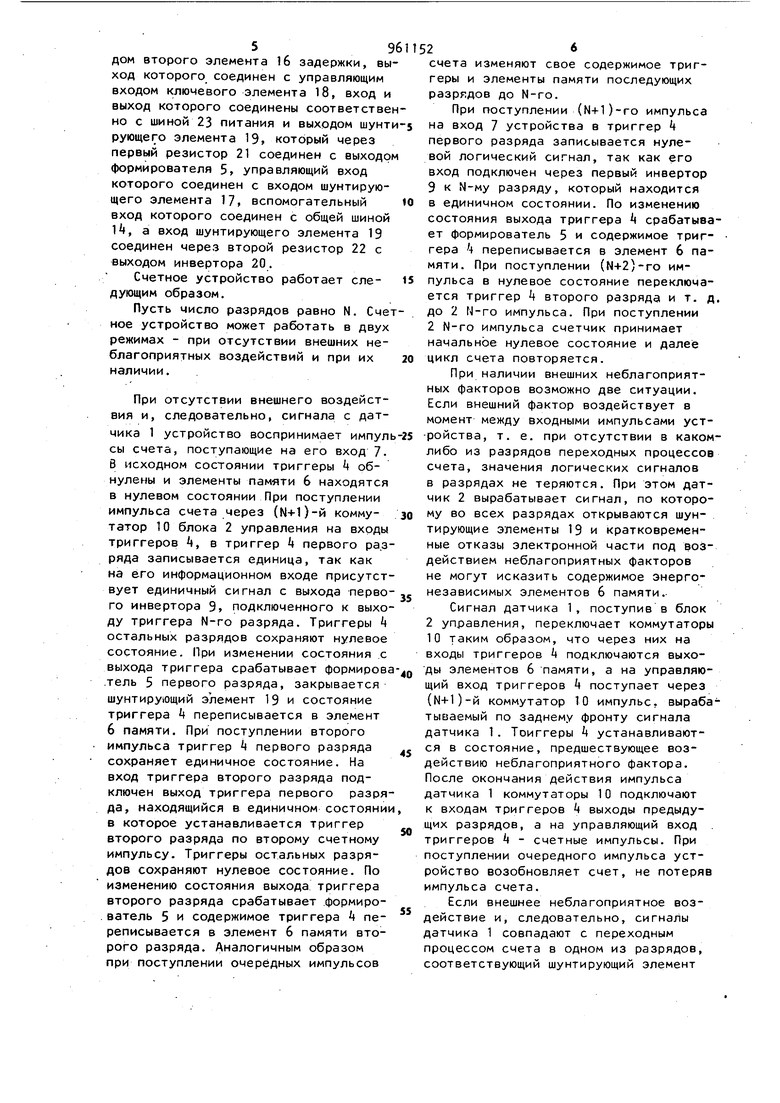

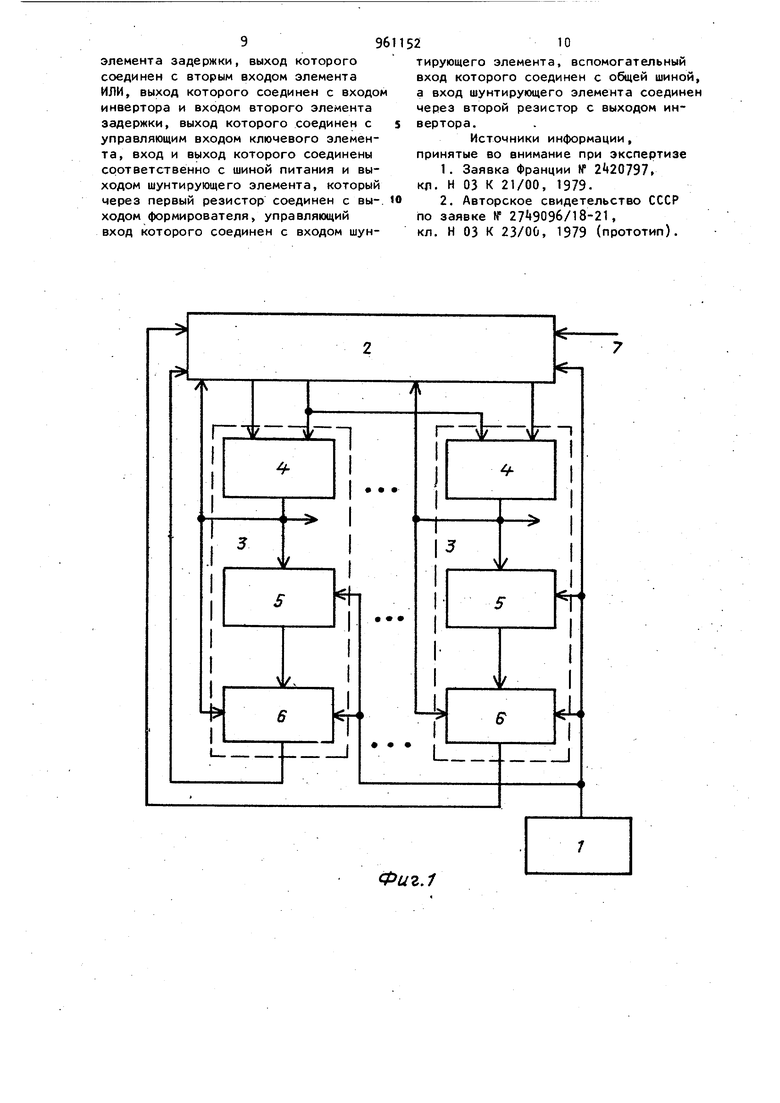

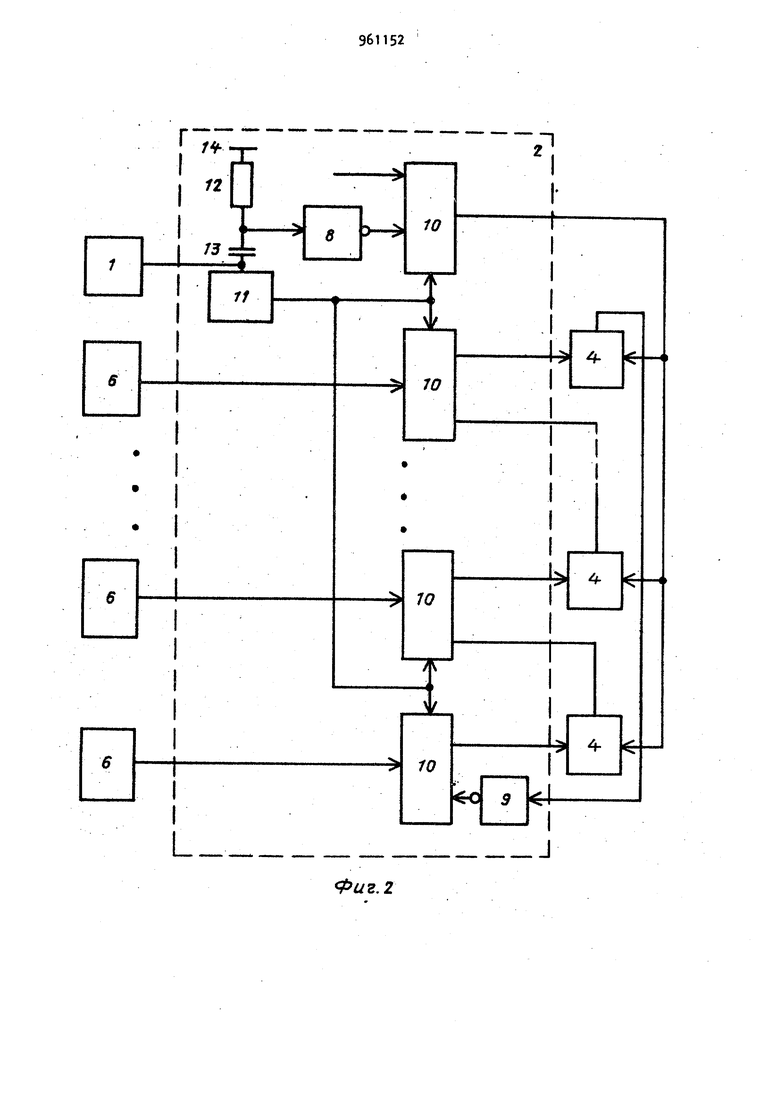

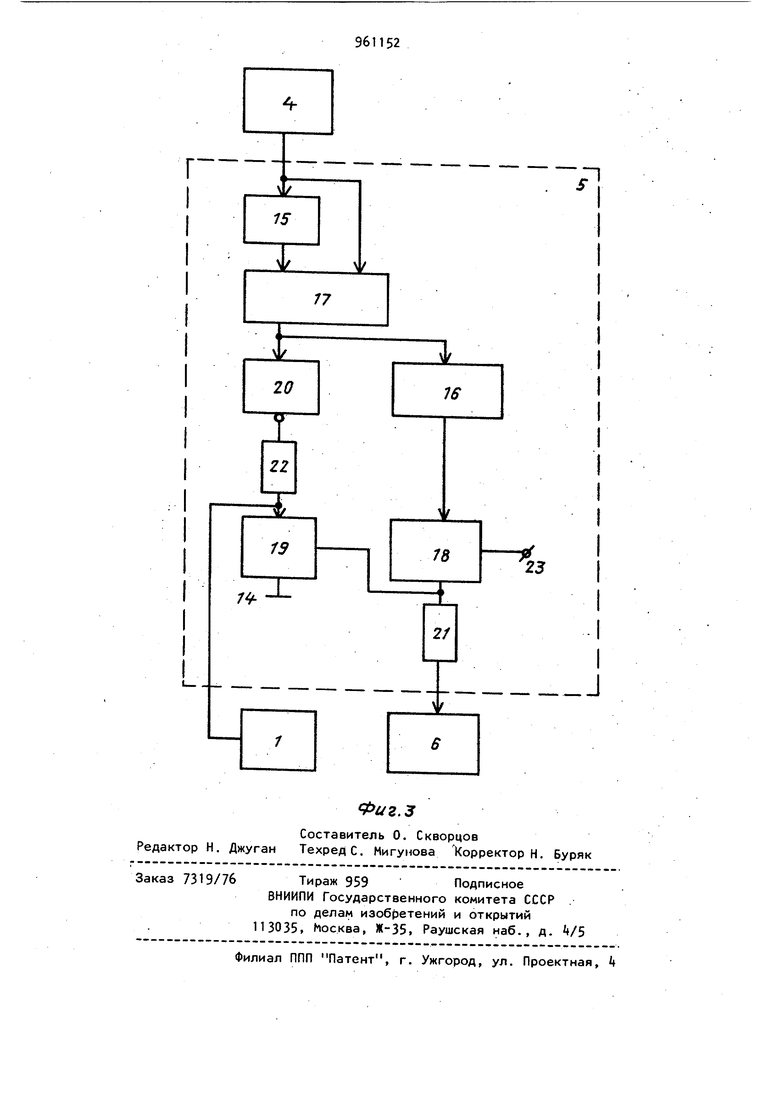

Изобретение относится к импульсной технике и может быть использовано для счёта импульсов в условиях внешних неблагоприятных воздействий. Известно счетное устройство, содер жащее датчик внешнего неблагоприятного воздействия и в каждом из п счет ных разрядов электронный триггер и .элемент памяти, первый вход которого подключен к выходу электронного триггера, а второй - к датчику 1. Известно также счетное устройство содержащее датчик, блок .управления и формирователь, а также разряды, каждый из которых содержит триггер и элемент памяти, выходы которых соединены с входами блока управления, выходы которого соединены с входами триггеров, а первый разряд содержит формирователь, управляющий вход которого соединен с выходом датчика С2 Недостатком известных счетных устройств является относительно низкая достоверность функционирования. Целью изобретения является повышение достоверности функционирования счетного устройства. Поставленная цель достигается тем, что в счетном устройстве, содержащем датчик, блок управления и формирователь, а также разряды, каждый из которых содержит триггер и элемент памяти, выходы которых соединены с входами блока управления, выходы которого соединены с входами триггеров, а первый разряд содержит формирователь, управляющий вход которого соединен с выходом датчика, в каждый разряд кроме первого введен формирователь, выход формирователя каждого разряда соединен с информационным входом элемента памяти того же разряда, вспомогательный и управляющий входы элемента памяти .каждого разряда соединены соответственно с выводом триггера того же разряда и выходом датчика, который соединен с управляющими входами формирователей всех разрядов. начиная со второго,и управляющим входом блока управления, вспомогательный вход которого соединен с входом сметного устройства, а выход триггера каждого разряда соединен с входом формирователя того же разряда. Блок управления содержит первый и второй инверторы, коммутаторы, элемент задержки, резистор и конденсатор, вход элемента задержки соединен с управляющим входом блока управления и через конденсатор с входом первого инвертора, который через резистор соединен с общей шиной, первые входы всех коммутаторов, кроме первого и последнего, соединены с входами блока управления, выходы которого соединены с выходами коммутаторов, второй вхоД первого коммутатора соединен с выходом второго инвертора, вход которого соединен с входом блока управления, остальные входы которого соединены с вторыми входами всех остальных коммутаторов, кроме последнего, первый и второй входы которого соединены соответственно с вспомогательными входом блока управления и выходом первого инвертора, а управляющие входы коммутатооов соединены с выходом элемента задержки. Формирователь содержит первый и второй элементы задержки, элемент ИЛИ ключевой и шунтирующий элементы, инвертор, первый и второй резисторы, вход формирователя соединен с первым входом элемента ИЛИ и входом первого элемента задержки, выход которого соединен с вторым входом элемента ИЛИ выход которого соединен с входом инвертора и входом второго элемента задержки, выход которого соединен с управляющим входом ключевого элемента вход и выход которого соединены соответственно с шиной питания и выходом шунтирующегъ элемента, который .через первый резистор соединен с выходом формирователя, управляющий вход которого соединен с входом шунтирующего элемента, вспомогательный вход которого соединен с общей шиной, а вход шунтирующего элемента соединен через второй резистор с выходом инвертора. На фиг. 1 показана структурная схема счетного устройства; на фиг, 2 структурная схема блока управления; на фиг, 3 - структурная схема формирователя. Счетное устройство содержит датчик 1, блок 2 управления, и разряды 3, каждый из которых содержит триггер 4, формирователь 5, элемент 6 памяти, выходы которых соединены с входами блока 2 управления, выходы которого соединены с входами триггеров 4, разряд 3 содержит формирователь 5, управляющий вход каждого формирователя 5 соединен с выходом датчика 1, выход формирователя 5 каждого разряда 3 соединен с информационным входом элемента 6 памяти того же разряда, вспомогательный и управляющий входы элемента 6 памяти каждого разряда соединены соответственно с выходом триггера 4 того же разряда и выходом датчика 1, который соединен с управляющим входом блока 2 управления, вспомогательный вход которого соединен с входом 7 счетного устройства, а выход триггера t каждого разряда 3 соединен с входом формирователя 5 того же разряда. Блок 2 управления содержит первый 8 и второй 9 инверторы, коммутаторы 10, элемент 11 задержки, резистор 12 и конденсатор 13, вход элемента 11 задержки соединен с управляющим входом блока 2 управления и через конденсатор 13 с входом первого инвертора 8, который через резистор 12 соединен с общей шиной Т, первые входы всех коммутаторов 10, кроме первого и последнего, соединены с входами блока 2 управления, выходы которого соединены с выходами коммутаторов 10, второй вход первого коммутатора 10 соединен с выходом второго инвертора 9, вход которого соединен с входом блока 2 управления, остальные входы которого соединены с вторыми входами всех остальных KOMMyTatopOB 10, кроме последнего, первый и второй входы которого соединены соответственно с вспомогательным входом блока 2 управления и выходом первого инвертора 8, а управляющие входы коммутаторов 10 соединены с выходом элемента 11 задержки. Формирователь 5 содержит первый 15 и второй 16 элементы задержки, элемент ИЛИ 17, ключевой 18 и шунтирующий 19 элементы, ивентор 20, а также первый 21 и второй 22 резисторы, вход формирователя 5 соединен с первым входом элемента ИЛИ 17 и входом первого элемента 15 задержки, выход которого соединен с вторым входом элемента ИЛИ 17, вЫход которого соединен с входом инвертора 20 и вхо59дом второго элемента 16 задержки, выход которого соединен с управляющим входом ключевого элемента 18, вход и выход которого соединены соответствен но с шиной 23 питания и выходом шунти рующего элемента 19, котбрый через первый резистор 21 соединен с выходом формирователя 5, управляющий вход которого соединен с входом шунтирующего элемента 17, вспомогательный вход которого соединен с общей шиной 1, а вход шунтирующего элемента 19 соединен через второй резистор 22 с выходом инвертора 20. Счетное устройство работает еледующим образом. Пусть число разрядов равно N. Счет ное устройство может работать в двух режимах - при отсутствии внешних неблагоприятных воздействий и при их наличии. При отсутствии внешнего воздействия и, следовательно, сигнала с датчика 1 устройство воспринимает импул сы счета, поступающие на его вход 7В исходном состоянии триггеры k обнулены и элементы памяти 6 находятся в нулевом состоянии При поступлении импульса счета через (М+1)-й коммутатор 10 блока 2 управления на входы триггеров , в триггер первого разряда записывается единица, так как на его информационном входе присутствует единичный сигнал с выхода первого инвертора 9, подключенного к выходу триггера N-ro разряда. Триггеры 4 остальных разрядов сохраняют нулевое состояние. При изменении состояния .с выхода триггера срабатывает формирова .тель 5 первого разряда, закрывается шунтирующий элемент 19 и состояние триггера t переписывается в элемент 6 памяти. При поступлении второго импульса триггер k первого разряда сохраняет единичное состояние. На вход триггера второго разряда подключен выход триггера первого разря да, находящийся в единичном состояни в которое устанавливается триггер второго разряда по второму счетному импульсу. Триггеры остальных разрядов сохраняют нулевое состояние. По изменению состояния выхода триггера второго разряда срабатывает формирователь 5 и содержимое триггера переписывается в элемент 6 памяти второго разряда. Аналогичным образом при поступлении очередных импульсов 26 счета изменяют свое содержимое три1- геры и элементы памяти последующих разрядов до N-ro. При поступлении (N+I)-го импульса на вход 7 устройства в триггер k первого разряда записывается нулевой логический сигнал, так как его вход подключен через первый инвертор 9к N-му разряду, который находится в единичном состоянии. По изменению состояния выхода триггера А срабатывает формирователь 5 и содержимое триггера 4 переписывается в элемент 6 памяти. При поступлении (N+2)-ro импульса в нулевое состояние переключается триггер k второго разряда и т. д. до 2 N-ro импульса. При поступлении 2 N-ro импульса счетчик принимает начальное нулевое состояние и далее цикл счета повторяется. При наличии внешних неблагоприятных факторов возможно две ситуации. Если внешний фактор воздействует в момент между входными импульсами устройства, т. е. при отсутствии в какомлибо из разрядов переходных процессов счета, значения логических сигналов в разрядах не теряются. При этом датчик 2 вырабатывает сигнал, по которому во всех разрядах открываются шунтирующие элементы 19 и кратковременные отказы электронной части под воздействием неблагоприятных факторов не могут исказить содержимое энергонезависимых элементов 6 памяти.. Сигнал датчика 1, поступив в блок 2 управления, переключает коммутаторы 10таким образом, что через них на входы триггеров k подключаются выходы элементов 6 памяти, а на управляющий вход триггеров А поступает через (N+l)-й коммутатор 10 импульс, вырабатываемый по заднему фронту сигнала датчика 1. Тоиггеры k устанавливаются в состояние, предшествующее воздействию неблагоприятного фактора. После окончания действия импульса датчика 1 коммутаторы 10 подключают к входам триггеров выходы предыдущих разрядов, а на управляющий вход . триггеров k - счетные импульсы. При поступлении очередного импульса устройство возобновляет счет, не потеряв импульса счета. Если внешнее неблагоприятное воздействие и, следовательно, сигналы датчика 1 совпадают с переходным процессом счета в одном из разрядов, соответствующий шунтирующий элемент 79 19 сигналом датчика 1 открывается и замыкает цепь тока записи на общую шину Il. В остальных формирователях 5 шунтирующие элементы 19 поддерживаются в открытом состоянии. В том разряде, где происходила запись нового содержимого триггера k в элемент 6 памяти, информация может исказиться и при восстановлении содержимое счетчика может оказаться На единицу меньше. После восстановления содержимого триггеров f устройство продолжает счет как в первом режиме. Таким образом, использование предлагаемого устройства позволяет решить задачу обеспечения счета в условиях воздействия провалов по питанию мощных электромагнитных помех и других неблагоприятных факторов. Это достигается тем, что при совпадении переходных процессов счета с неблагоприятным внешним воздействием может прои.ойти искажение информации только в одном разряде и погрешность счета при этом не превышает половины цены (дискрета) одного импульса. Искажение содержимого одного из разрядов носит вероятностный характер и зависит, в частности, от соотношения интервала между импульсами счета и времени восстановления состо яния электронной части устройства после сбоя от воздействия неблагоприятного фактора. Если длительность восстановления электронной части существенно меньше интервала счетных импульсов, вероятность совпадения переходных процессов счета с переходными процессами восстановления достаточ но мала. Например, при действии электромагнитного импульса длительность переходных процессов восстановления триггеров на 1-2 порядка меньше и вероятность искажения разряда не превысит значение 0,1-0,01. Использование данного счетного уст ройства позволяет увеличить точность счета, например времени, что особенно важно для автономных, необслуживаемых систем и устройств, которые работают в условиях неблагоприятных внешних воздействий. Формула изобретения 1. Счетное устройство, содержащее датчик, блок управления и формирователь, а также разряды, каждый из ко28торых содержит триггер и элемент памяти, выходы которых соединены с входами блока управления, выходы которого соединены с входами триггеров, а первый разряд содержит формирователь, управляющий вход которого соединен с выходом датчика, отличаю щ ее с я тем, что с целью повышения достоверности функционирования, в каждый разряд, кроме первого, введен формирователь, выход формирователя каждого разряда соединен с информационным входом элемента памяти того же разряда, вспомогательный и управляющий входы элемента памяти каждого разряда соединены соответственно с выходом триггера того же разряда и выходом датчика, который соединен с управляющими входами .формирователей всех разрядов, начиная со второго, и управляющим входом блока управления, вспомогательный вход которого соединен с входом счетного устройства, а выход триггера каждого разряда соединен с входом формирователя того же разряда. 2.Устройство по п. 1, отличающееся тем, что блок управления содержит первый и второй инверторы, коммутаторы, элемент задержки, резистор и конденсатор, вход элемента задержки соединен с управляющим входом блока управления и через конденсатор с входом первого инвертора, который через резистор соединен с общей шиной, первые входы всех коммутаторов, кроме первого и последнего, соединены с входами блока управления, выходы которого соединены с выходами коммутаторов, второй вход первого комкоммутатора соединен с выходом второго инвертора, вход которого соединен с входом блока управления, остальные входы которого соединены с вторыми входами всех остальных коммутаторов, кроме последнего, первый и второй входы которого соединены соответственно с вспомогательным входом блока управления и выходом первого инвертора, а управляющие входы коммутаторов соединены с выходом элемента задержки. 3.Устройство по п. 1, отличающееся тем, что формирователь содержит первый и второй элементы задержки, элемент ИЛИ, ключевой элемент, шунтирующий элемент, инвертор и первый и второй резисторы, вход формирователя соединен с первым входом элемента ИЛИ и входом первого

элемента задержки, выход которого соединен с вторым входом элемента ИЛИ, выход которого соединен с входом инвертора и входом второго элемента задержки, выход которого соединен с управляющим входом ключевого элемента, вход и выход которого соединены соответственно с шиной питания и выходом шунтирующего элемента, который через первый резистор соединен с вы-, ходом формирователя, управляющий вход которого соединен с входом шунтирующего элемента, вспомогательный вход которого соединен с общей шиной, а вход шунтирующего элемента соединен через второй резистор с выходом инвертора.

Источники информации, принятые во внимание при экспертизе

кл. Н 03 К 23/00, 1979 (прототип).

Фиг.1

Фи.2

Авторы

Даты

1982-09-23—Публикация

1981-02-17—Подача