Изобретение относится к вычислительной технике и автоматике, в частности к устройствам автоматического управления, где требуется включение различных механизмов в определенной последорателыю- §ТИ во. рремен.и, и мажет быть цепрльзованд для управления технологическими прдц§&

69МИ.

Известно программное временное устройство, содержащее генератор импульсов и последовательно соединенные счетчик импульсов, блок набора программ, дешифратор, элементы И, дополнительный элемент И, несимметричный триггер и исполнительные элементы.

В это устройство с целью повышения надежности и обеспечения возможности автоматической остановки устройства пделе отработки программы дрп@лните.льн9 введены элементы ИЛИ, втерей эл§м§нт И, т- датиик режимов, фермиреватель импульсов, симметричный триггер.

Недостатками этих устройств являются: постоянная длительность выдаваемых команд, недостаточная точность выдаваемых команд, низкий коэффициент использования объема памяти, оперативной возможности изменять длительность, время выдачи и количество команд.

Из известных наиболее близким по технической сущности к заявляемому является программное устройство управления, со- держащее генератор импульсов, счетчик, первый и второй дешифратор, блок памяти, первую и вторую группу дешифраторов, триггер, элемент И, регистр адреса, выходной регистр, элемент задержки, группу мультиплексоров, группу дешифраторов.

Недостатками известного устройства, выбранного в качестве прототипа, являются:

-ограниченные функциональные воз- можности, в частности, оно не может обеспечить автономную выдачу более одной команды, коды которой записаны в блоке памяти, для выдачи всех команд дополнительно необходим блок управления;

-блок управления только асинхронными командами может инициировать устройство к выдаче последующих команд;

-выдаваемые команды имеют постоянную длительность, а время их выдачи долж- но дополнительно определяться блоком управления;

-блок управления асинхронно инициирует устройство к выдаче команд, что снижает точность их выдачи относительно первоначального сигнала признак начала работы.

Целью изобретения является расширение функциональных возможностей за счет автономности при выдаче команд, времени их появления и формирования по длительности и повышение точности выдачи всех команд относительно сигнала признак начала работы.

Поставленная цель достигается тем, что в программное временное устройство, содержащее генератор импульсов, регистр адреса, блок оперативной памяти (ОЗУ), триггер пуска, счетчик импульсов, первую и вторую группу коммутаторов, первый эле- мент И, первый элемент задержки и выходной регистр, дополнительно введены элемент сравнения, первый, второй .третий, четвертый и пятый элементы ИЛИ, формирователь сигнала разрешение выборки, инвертор, триггер блокировки, второй и третий элементы задержки, выходной регистр выполнен на D-триггерах, а генератор импульсов представляет собой последовательно соединенные генератор опорной частоты, второй элемент И и делитель частоты, причем группа информационных ьло- дов регистра адреса и группа информационных входов коммутаторов первой группы подключены к магистрали

дрес-данные. Управляющий вход регистра адреса соединен с шиной команд управления запись адреса, выходы регистра адреса подключены к группе информационных входов блока оперативной памяти, группа выходов коммутаторов второй группы подключена к первой группе входов элемента сравнения, вторая группа входов которого соединена с разрядными выходами счетчика импульсов, счетный вход которого подключен к выходу делителя частоты генератора импульсов и к первому входу первого элемента ИЛИ, а установочный вход счетчика импульсов, первые входы второго и третьего элементов ИЛИ, входы сброс триггера пуска, делителя частоты и D-триггеров выходного регистра подключены к шине команды управления сброс, вход запись триггера пуска и вторые входы четвертого и третьего элемента ИЛИ подсоединены к шине команд управления признак начала работы, а выход триггера пуска подключен к первому разрешающему входу первого элемента И, к управляющему входу блока оперативной памяти и ко второму входу коммутаторов второй группы и через инвертор к управляющему входу коммутаторов первой группы, выходы которых соединены с группой входов-выходов блока оперативной памяти коммутаторов второй группы информационных входов, первый вход второго элемента l/ ПИ подсоединен к шине команд управления конец обмена его выход к входу сброс регистра адреса, выход элемента сравнения подключен к первому входу второго элемента И, выход которого через первый и второй элементы задержки соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом сброс триггера блокировки, инверсный выход которого соединен со вторым разрешающим входом первого элемента И, выход первого элемента задержки подключен ко входу запись триггера блокировки, ко второму входу четвертого элемента ИЛИ, а выход второго элемента задержки к тактовому входу D-триггеров выходного регистра D входы D-триггеров выходного регистра подключены к соответствующим разрядам магистрали выдачи данных, выходы D-триггеров выходного регистра соединены через группу элементов гальванической развязки с группой информационных выходов устройства, выход второго элемента задержки соединен с третьим входом четвертого элемента ИЛИ, выход которого подключен к счетному входу регистра адреса, а через первый элемент ИЛИ, формирователь сигналов разрешение вы- бррки и пятый элемент ИЛИ соединен управляющим блоком оперативной памяти со вторым входом, второй вход пятого элемента ИЛИ подключен к шине команд управле- ния запись данных.

Положительный эффект при осуществлении изобретения заключающийся в расширении его функциональных возможностей достигается:

-строгим поячеечным чередованием информации о премеии.появления команды и значением кода команды, начала записи с первой ячейки и последовательность записи информации в ячейках ОЗУ от времени появления команды;

-временем элемента сравнения позволяющего устройству определять время выдачи команды за счет сравнения кода времени хранимого в ОЗУ с текущим временным кодом со счетчика, что позволяет оперативно перестраивать время начала выдачи команд и их длительности предварительно изменяя код о ячейках ОЗУ;

-введение второго, третьего, четвертого и пятого элемента ИЛИ, формирователя сигнала разрешение выборки, третьего элемента задержки, триггера блокировки и соответствующих связей позволяет осуществить модификацию содержимого регистра адреса и устройству автономно формировать остальные команды, воспринимать сигналы сравнения только от ячеек ОЗУ, в которых хранится кед времени, л введение второго элемента задержки с соответствующими связями записывать без- сбойно информацию позиционного кода команды в D-триггеры выходного регистра по тактовому входу;

-позиционная разводка магистрали выдачи данных на соответствующие входы D D-триггеров выходного регистра позволяет исключить применение дешифратора в устройстве;

-применение генератора опорной частоты на четыре-шесть порядков превышающих тактовую частоту и делителя частоты, работающего в ждущем режиме повышает точность выдачи команд относительно признака начала работы.

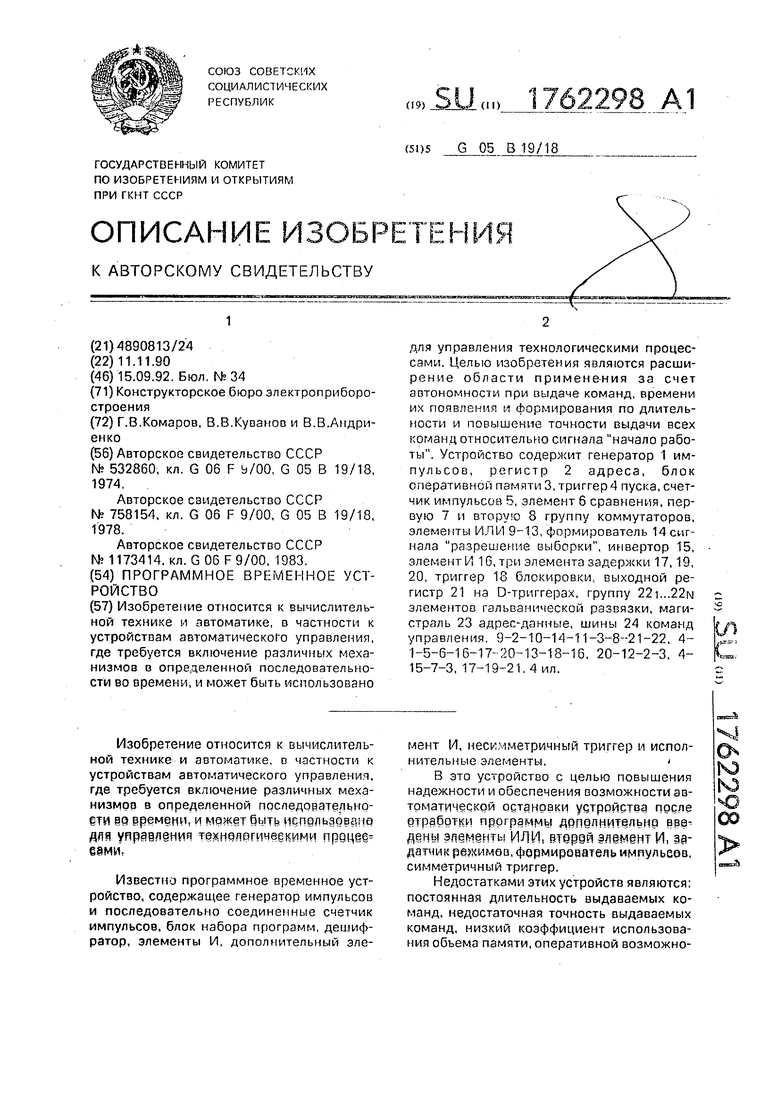

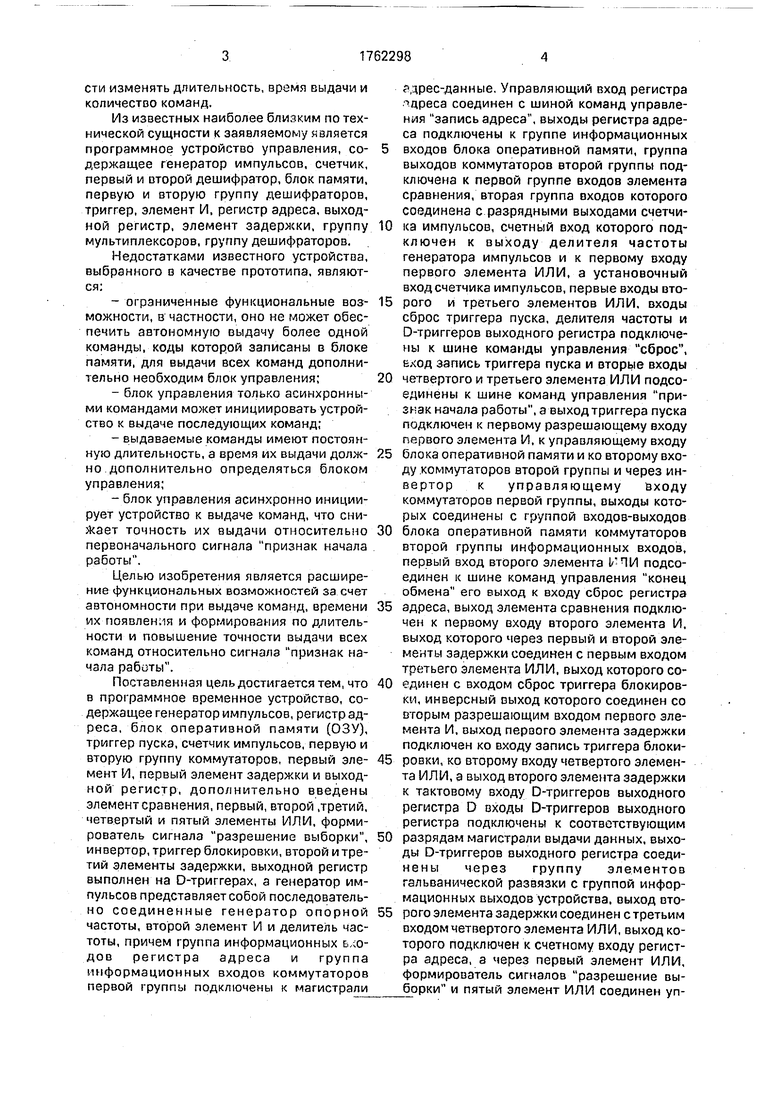

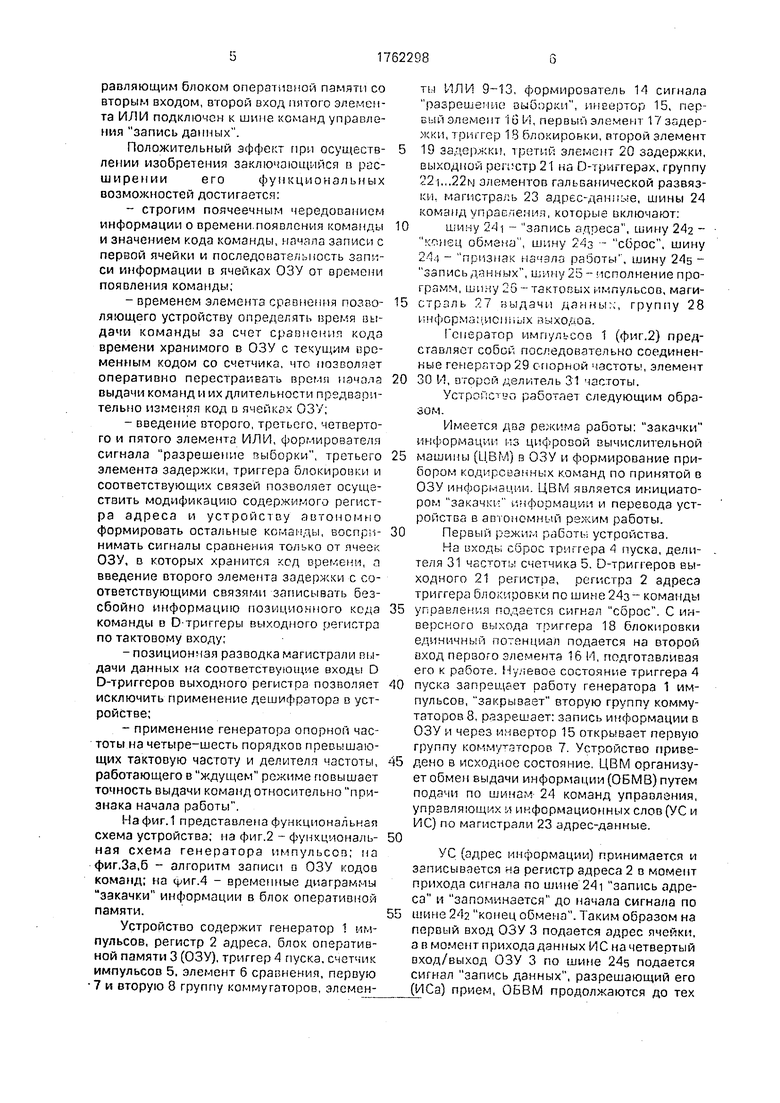

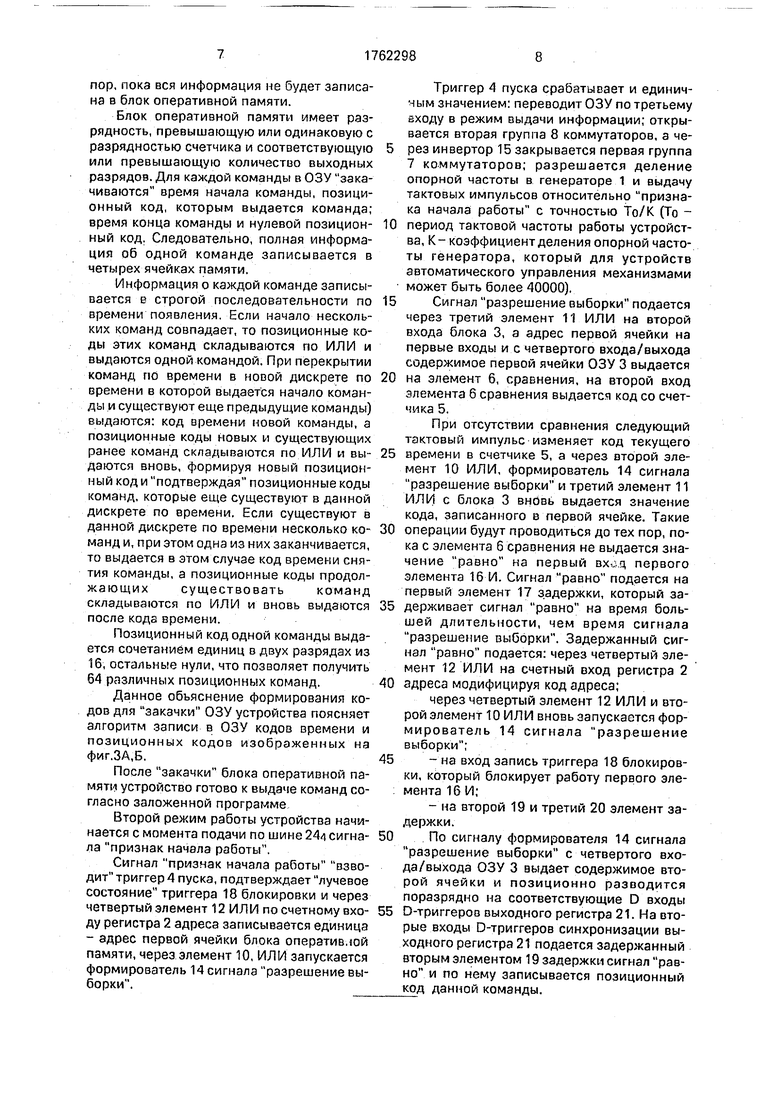

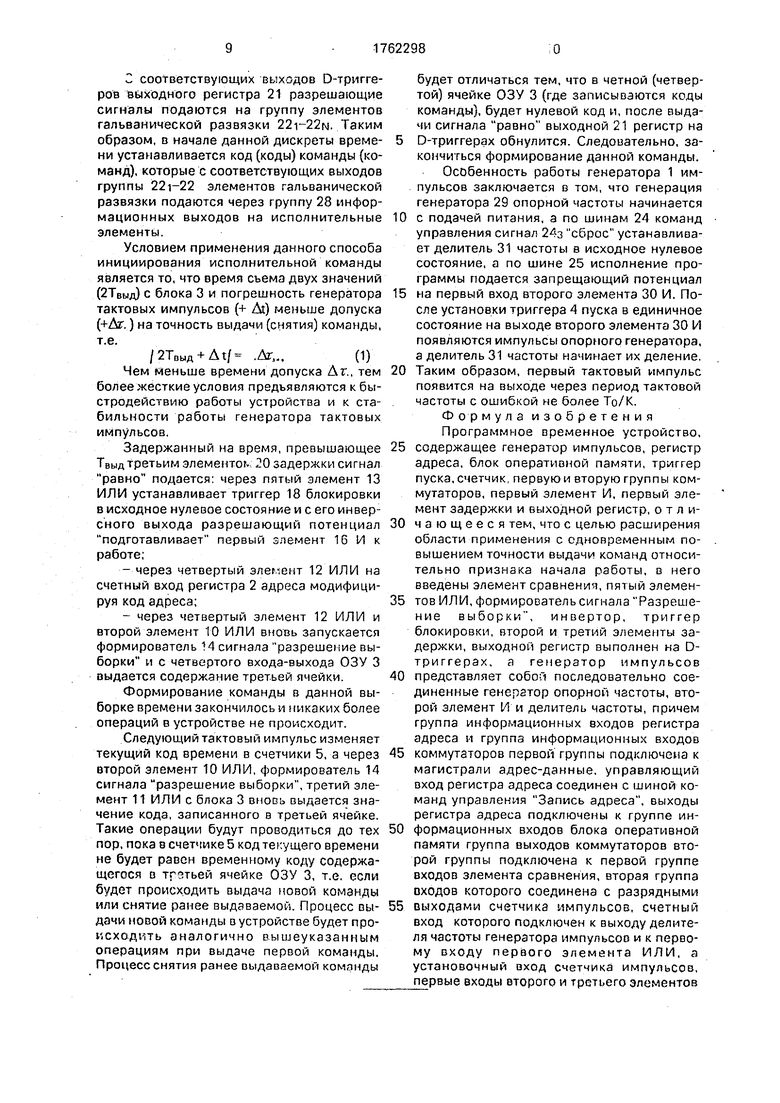

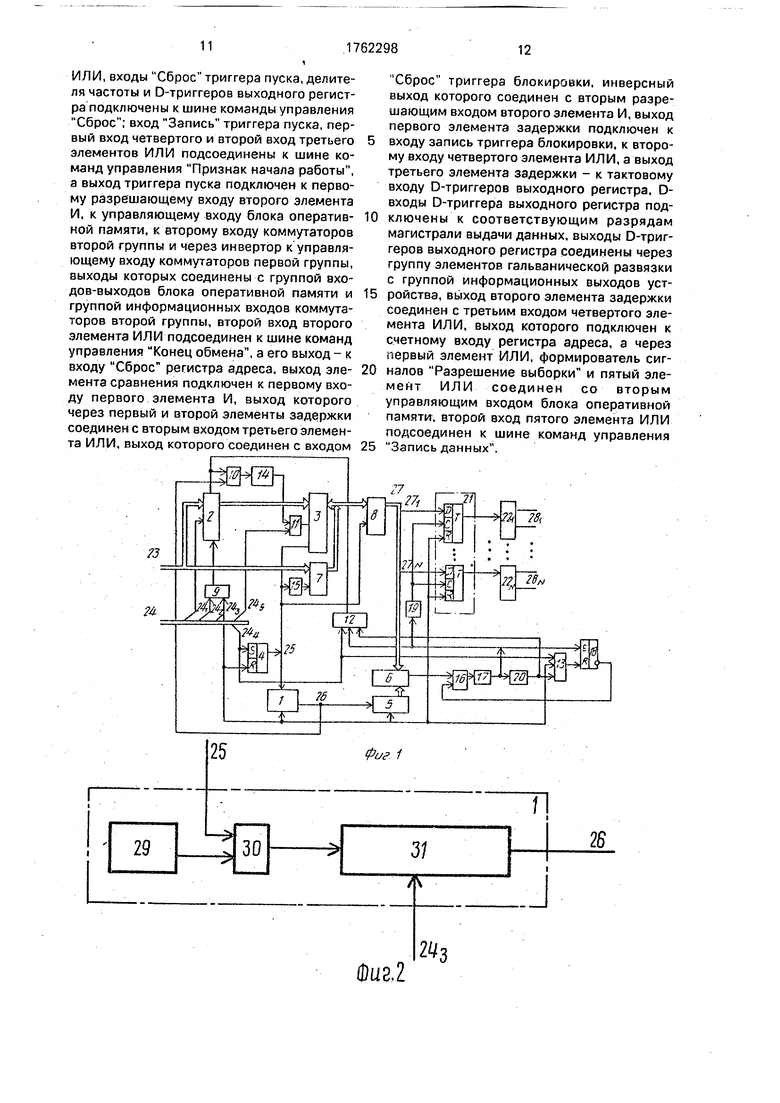

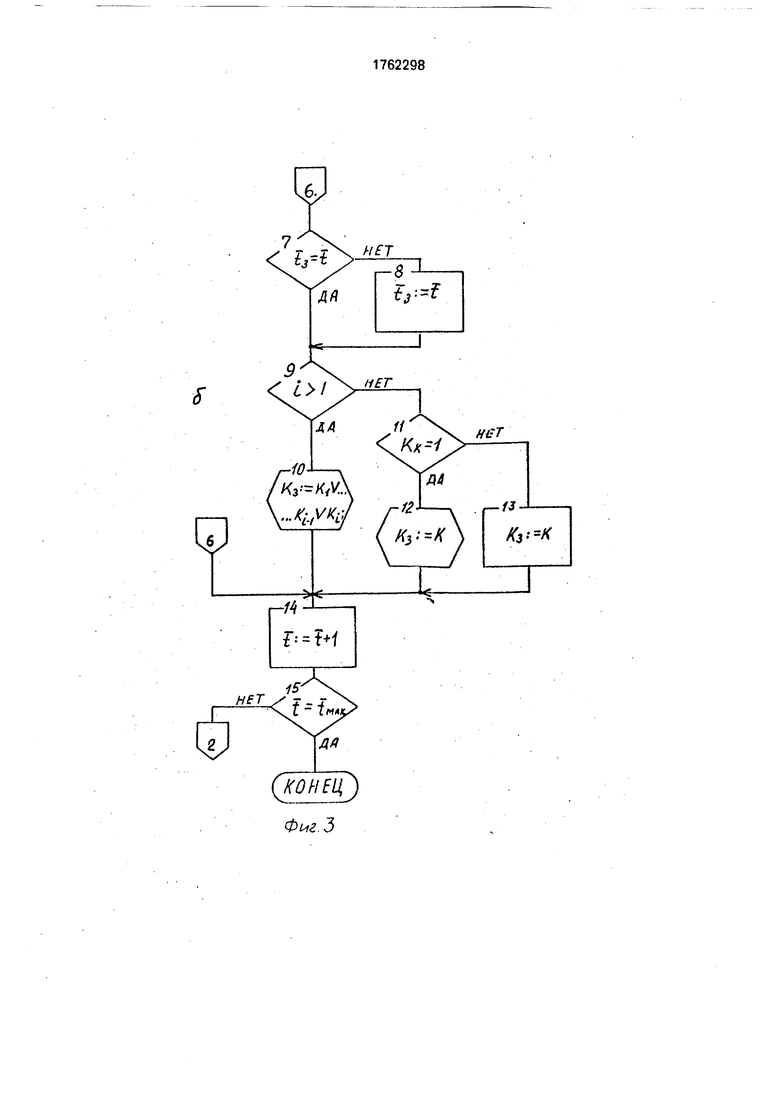

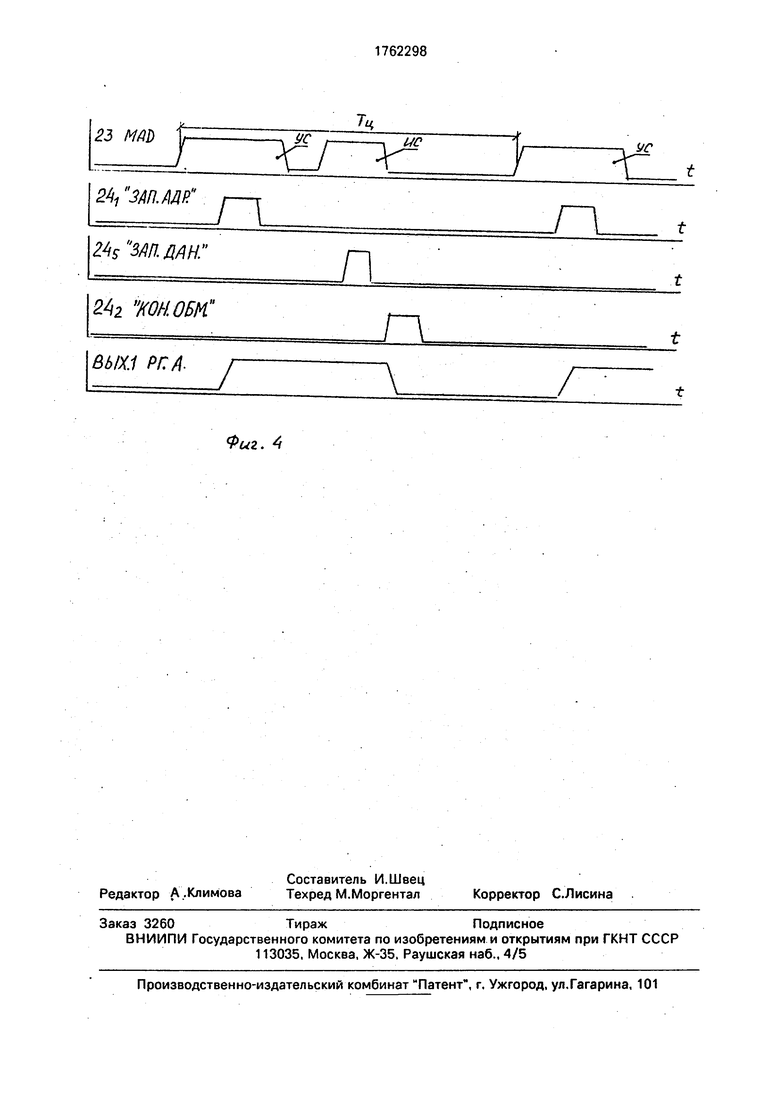

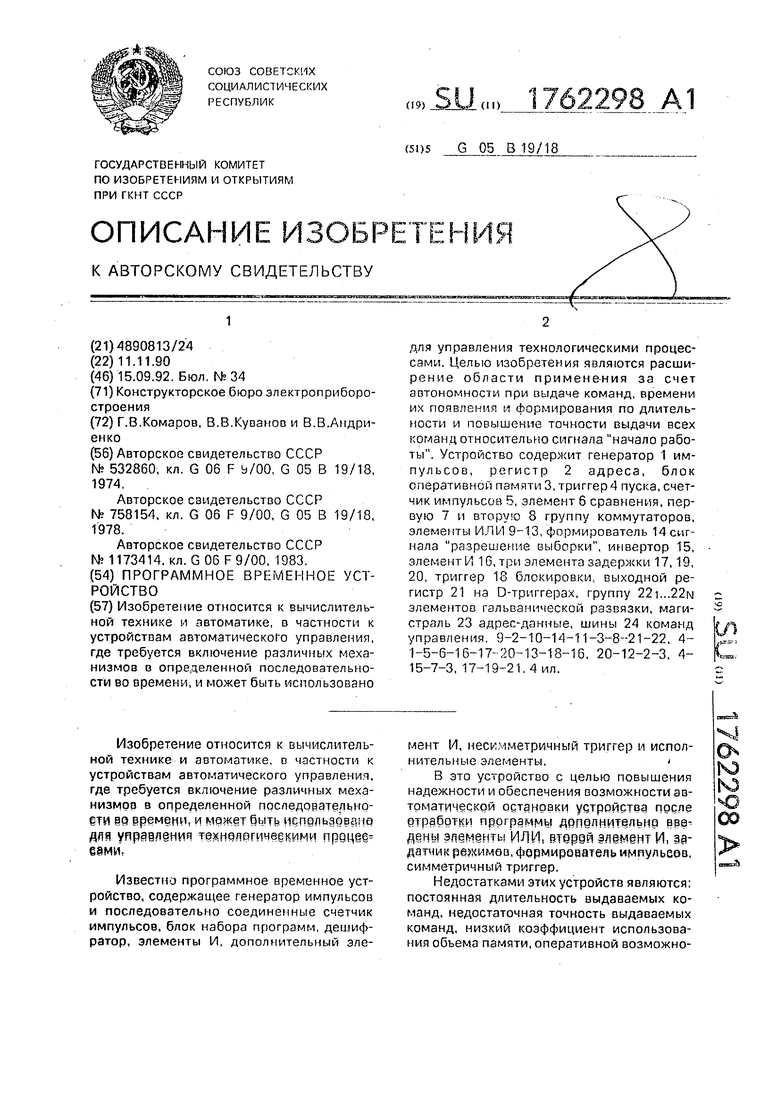

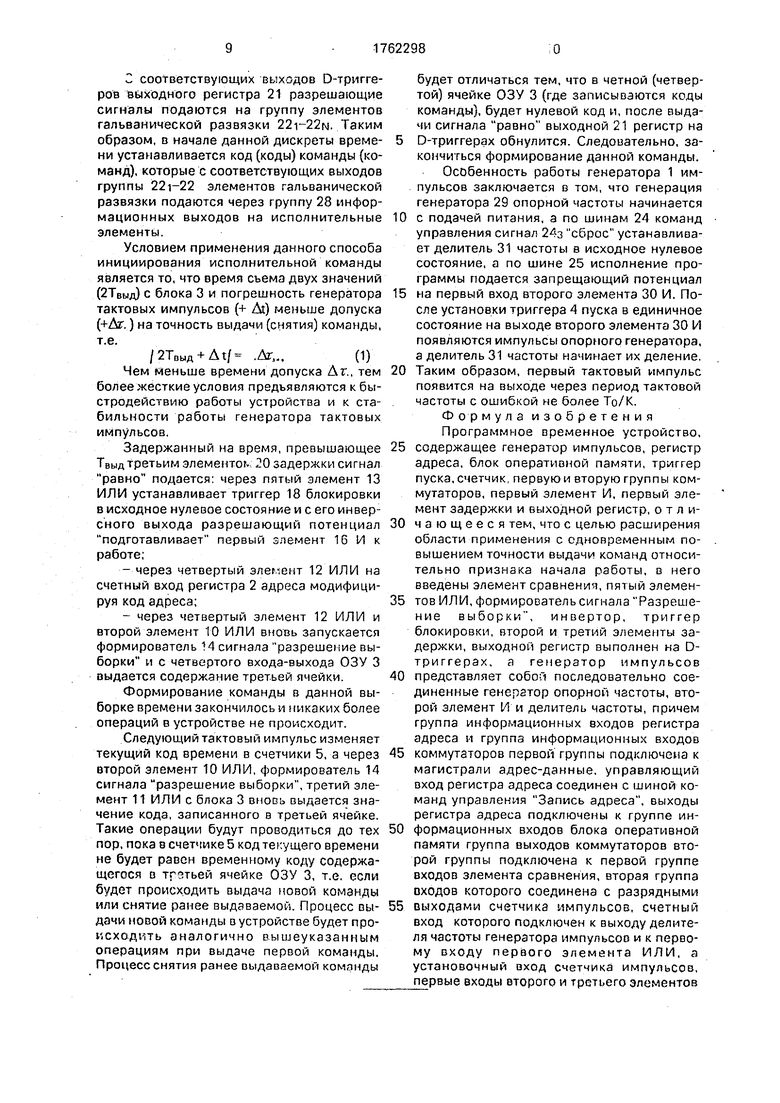

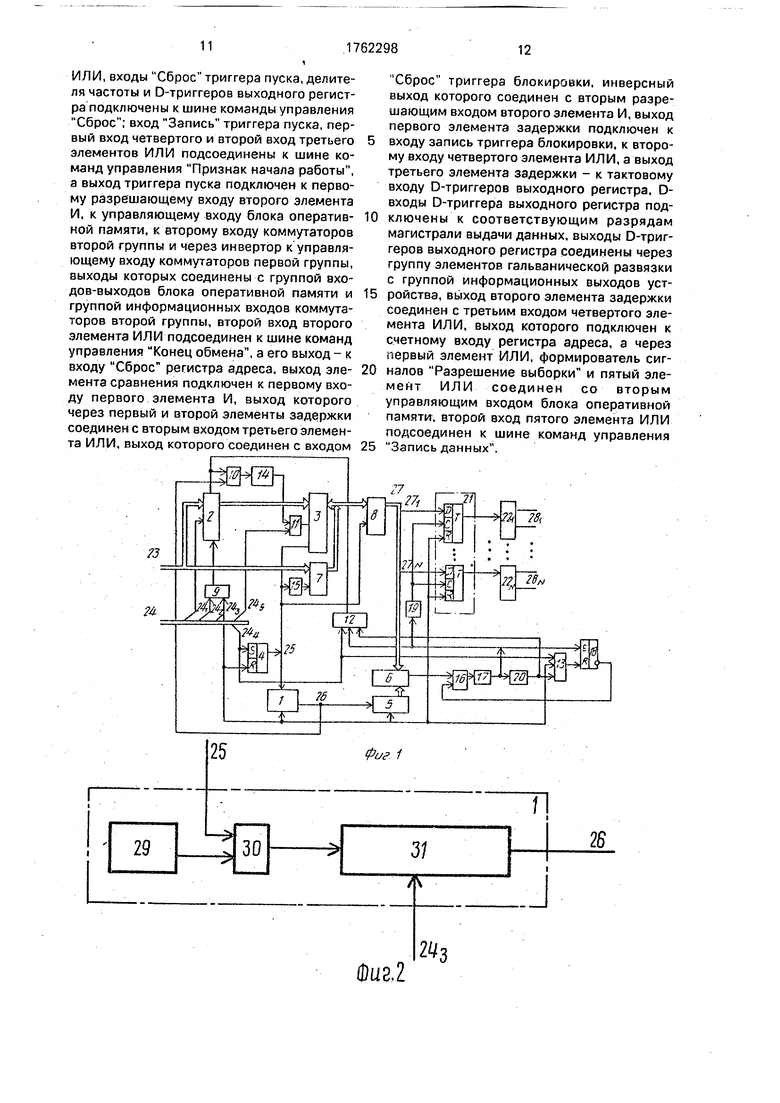

Нафиг.1 представлена функциональная схема устройства; на фиг.2 - функциональная схема генератора импульсов; па фиг.За,б - алгоритм записи в ОЗУ кодов команд; на фиг.4 - временные диаграммы закачки информации в блок оперативной памяти.

Устройство содержит генератор 1 импульсов, регистр 2 адреса, блок оперативной памяти 3 (ОЗУ), триггер А пуска, счетчик импульсоо 5, элемент б сравнения, первую 7 и вторую 8 группу коммутаторов, элементы ИЛИ 9-13, формирователь 14 сигнала разрешение аыборки, инвертор 15, первый элемент 1G И, первый элемент 17 задержки, триггер 18 блокировки, второй элемент 19 задержки, третий элемент 20 задержки, выходной регистр 21 на D-триггерах, группу 221...22м элементов гальванической развязки, магистраль 23 адрес-данные, шины 24 команд упраспения, которые включают:

шину 241 - запись адреса, шину 242 конец обмена, шину 24з - сброс, шину 2-1.| - признак начала работы, шину 24g - запись дчнных, шину 25- исполнение программ, шину 25 - тактовых импульсов, магистрзль 27 выдачи данны:;, группу 28 информационных ЛЫХОАОЗ.

Генератор импульсов 1 (фиг.2) представляет собой последовательно соединенные генератор 29 спорной частоты, элемент

30 И, второй делитель 31 частоты.

Устройство работает следующим образом.

Имеется два режима работы: закачки информации из цифровой вычислительной

машины (ЦВМ) в ОЗУ и формирование прибором кодированных команд по принятой в ОЗУ информации. ЦВМ является инициатором закачки информации и перевода устройства в автономный рэжим работы.

Первый рэжим работы устройства.

На входы сброс триггера 4 пуска, делителя 31 частоту счетчика 5. D-триггеров выходного 21 регистра, регистра 2 адреса триггера блокировки пошине24з- команды

управления подается сигнал сброс. С инверсного выхода триггера 18 блокировки единичный потенциал подается на второй вход первого элемента 16 И, подготавливая его к работе. Нулевое состояние триггера 4

пуска запрещает работу генератора 1 импульсов, закрывает вторую группу коммутаторов 8, разрешает: запись информации в ОЗУ и через инвертор 15 открывает первую группу коммутаторов 7. Устройство приведено в исходное состояние. ЦВМ организует обмен выдачи информации (ОБМВ) путем подачи по шинам 24 команд управления, управляющих и информационных слов (УС и ИС) по магистрали 23 адрес-данные.

УС (адрес информации) принимается и записывается ча регистр адреса 2 в момент прихода сигнала по шине 24ч запись адреса и запоминается до начала сигнала по

шине 24. конец обмена. Таким образом на первый вход ОЗУ 3 подается адрес ячейки, а в момент прихода данных ИС на четвертый вход/выход ОЗУ 3 по шине 24д подается сигнал запись данных, разрешающий его

(ИСа) прием, ОБВМ продолжаются до тех

пор, пока вся информация не будет записана в блок оперативной памяти.

Блок оперативной памяти имеет разрядность, превышающую или одинаковую с разрядностью счетчика и соответствующую или превышающую количество выходных разрядов. Для каждой команды в ОЗУ закачиваются время начала команды, позиционный код, которым выдается команда; время конца команды и нулевой позиционный код. Следовательно, полная информация об одной команде записывается в четырех ячейках памяти.

Информация о каждой команде записывается в строгой последовательности по времени появления. Если начало нескольких команд совпадает, то позиционные коды этих команд складываются по ИЛИ и выдаются одной командой. При перекрытии команд по времени в новой дискрете по времени в которой выдается начало команды и существуют еще предыдущие команды) выдаются: код времени новой команды, а позиционные коды новых и существующих ранее команд складываются по ИЛИ и выдаются вновь, формируя новый позиционный код и подтверждая позиционные коды команд, которые еще существуют в данной дискрете по времени. Если существуют в данной дискрете по времени несколько команд и, при этом одна из них заканчивается, то выдается в этом случае код времени снятия команды, а позиционные коды продолжающих существовать команд складываются по ИЛИ и вновь выдаются после кода времени.

Позиционный код одной команды выдается сочетанием единиц в двух разрядах из 16, остальные нули, что позволяет получить 64 различных позиционных команд.

Данное объяснение формирования кодов для закачки ОЗУ устройства поясняет алгоритм записи в ОЗУ кодов времени и позиционных кодов изображенных на фиг.ЗА.Б.

После закачки блока оперативной памяти устройство готово к выдаче команд согласно заложенной программе

Второй режим работы устройства начинается с момента подачи по шине 244 сигнала признак начала работы.

Сигнал признак начала работы взводит триггер 4 пуска, подтверждает лучевое состояние триггера 18 блокировки и через четвертый элемент 12 ИЛИ по счетному входу регистра 2 адреса записывается единица - адрес первой ячейки блока оператив.юй памяти, через элемент 10, ИЛИ запускается формирователь 14 сигнала разрешение выборки.

Триггер 4 пуска срабатывает и единич- чым значением: переводит ОЗУ по третьему входу в режим выдачи информации; открывается вторая группа 8 коммутаторов, а через инвертор 15 закрывается первая группа 7 коммутаторов; разрешается деление опорной частоты в генераторе 1 и выдачу тактовых импульсов относительно признака начала работы с точностью То/К (То 0 период тактовой частоты работы устройства, К- коэффициент деления опорной частоты генератора, который для устройств автоматического управления механизмами может быть более 40000).

5 Сигнал разрешение выборки подается через третий элемент 11 ИЛИ на второй входа блока 3, а адрес первой ячейки на первые входы и с четвертого входа/выхода содержимое первой ячейки ОЗУ 3 выдается

0 на элемент 6, сравнения, на второй вход элемента 6 сравнения выдается код со счетчика 5.

При отсутствии сравнения следующий тактовый импульс изменяет код текущего

5 времени в счетчике 5, а через второй элемент 10 ИЛИ, формирователь 14 сигнала разрешение выборки и третий элемент 11 ИЛИ с блока 3 вновь выдается значение кода, записанного в первой ячейке. Такие

0 операции будут проводиться до тех пор, пока с элемента 6 сравнения не выдается значение равно на первый первого элемента 16 И. Сигнал равно подается на первый элемент 17 задержки, который за5 держивает сигнал равно на время большей длительности, чем время сигнала разрешение выборки. Задержанный сигнал равно подается: через четвертый элемент 12 ИЛИ на счетный вход регистра 2

0 адреса модифицируя код адреса;

через четвертый элемент 12 ИЛИ и второй элемент 10 ИЛИ вновь запускается фор- мирователь 14 сигнала разрешение выборки ;

5 - на вход запись триггера 18 блокировки, который блокирует работу первого элемента 16 И;

- на второй 19 и третий 20 элемент задержки.

0 По сигналу формирователя 14 сигнала разрешение выборки с четвертого входа/выхода ОЗУ 3 выдает содержимое второй ячейки и позиционно разводится поразрядно на соответствующие D входы

5 D-триггеров выходного регистра 21. На вторые входы D-триггеров синхронизации выходного регистра 21 подается задержанный вторым элементом 19 задержки сигнал равно и по нему записывается позиционный код данной команды.

С соответствующих выходов D-тригге- ров выходного регистра 21 разрешающие сигналы подаются на группу элементов гальванической развязки 22ч-22м. Таким образом, в начале данной дискреты времени устанавливается код (коды) команды (команд), которые с соответствующих выходов группы 22i-22 элементов гальванической развязки подаются через группу 28 информационных выходов на исполнительные элементы.

Условием применения данного способа инициирования исполнительной команды является то, что время сьема двух значений (2Твыд) с блока 3 и погрешность генератора тактовых импульсов (+ At) меньше допуска (+Дг.) на точность выдачи (снятия) команды, т.е.

/2ТВЫд + Дг/ .Дг...(1)

Чем меньше времени допуска Аг., тем более жесткие условия предъявляются к быстродействию работы устройства и к стабильности работы генератора тактовых импульсов.

Задержанный на время, превышающее Твыд третьим элементог. 20 задержки сигнал равно подается: через пятый элемент 13 ИЛИ устанавливает триггер 18 блокировки в исходное нулевое состояние и с его инверсного выхода разрешающий потенциал подготавливает первый элемент 16 И к работе;

-через четвертый элемент 12 ИЛИ на счетный вход регистра 2 адреса модифицируя код адреса;

-через четвертый элемент 12 ИЛИ и второй элемент 10 ИЛИ вновь запускается формирователь М сигнала разрешение выборки и с четвертого входа-выхода ОЗУ 3 выдается содержание третьей ячейки.

Формирование команды в данной выборке времени закончилось и никаких более операций в устройстве не происходит.

Следующий тактовый импульс изменяет текущий код времени в счетчики 5, а через второй элемент 10 ИЛИ, формирователь 14 сигнала разрешение выборки, третий элемент 11 ИЛИ с блока 3 вновь выдается значение кода, записанного в третьей ячейке. Такие операции будут проводиться до тех пор, пока в счетчике 5 код текущего времени не будет равен временному коду содержащегося в тг-зтьей ячейке ОЗУ 3, т.е. если будет происходить выдача новой команды или снятие ранее выдаваемой. Процесс выдачи новой команды в устройстве будет происходить аналогично вышеуказанным операциям при выдаче первой команды, Процесс снятия ранее выдаваемой команды

будет отличаться тем, что в четной (четвертой) ячейке ОЗУ 3 (где записываются коды команды), будет нулевой код и, после выдачи сигнала равно выходной 21 регистр на

D-триггерах обнулится. Следовательно, закончиться формирование данной команды. Особенность работы генератора 1 импульсов заключается в том, что генерация генератора 29 опорной частоты начинается

0 с подачей питания, а по шинам 24 команд управления сигнал 2&з сброс устанавливает делитель 31 частоты в исходное нулевое состояние, а по шине 25 исполнение программы подается запрещающий потенциал

5 на первый вход второго элемента 30 И. После установки триггера А пуска в единичное состояние на выходе второго элемента 30 И появляются импульсы опорного генератора, а делитель 31 частоты начинает их деление.

0 Таким образом, первый тактовый импульс появится на выходе через период тактовой частоты с ошибкой не более То/К. Формула изобретения Программное временное устройство,

5 содержащее генератор импульсов, регистр адреса, блок оперативной памяти, триггер пуска, счетчик, первую и вторую группы коммутаторов, первый элемент И, первый элемент задержки и выходной регистр, о т л и0 чающееся тем, что с целью расширения области применения с одновременным повышением точности выдачи команд относительно признака начала работы, в него введены элемент сравнения, пятый элемен5 тов ИЛИ, формирователь сигнала Разрешение выборки, инвертор, триггер блокировки, второй и третий элементы задержки, выходной регистр выполнен на D- триггерах, а генератор импульсов

0 представляет собой последовательно соединенные генератор опорной частоты, второй элемент И и делитель частоты, причем группа информационных входов регистра адреса и группа информационных входов

5 коммутаторов первой группы подключена к магистрали адрес-данные, управляющий вход регистра адреса соединен с шиной команд управления Запись адреса, выходы регистра адреса подключены к группе ин0 формационных входов блока оперативной памяти группа выходов коммутаторов второй группы подключена к первой группе входов элемента сравнения, вторая группа оходов которого соединена с разрядными

5 выходами счетчика импульсов, счетный вход которого подключен к выходу делителя частоты генератора импульсоо и к первому входу первого элемента ИЛИ, а установочный оход счетчика импульсов, первые входы второго и третьего элементов

ИЛИ, входы Сброс триггера пуска, делителя частоты и D-триггеров выходного регистра подключены к шине команды управления Сброс ; вход Запись триггера пуска, первый вход четвертого и второй вход третьего элементов ИЛИ подсоединены к шине команд управления Признак начала работы, а выход триггера пуска подключен к первому разрешающему входу второго элемента И, к управляющему входу блока оперативной памяти, к второму входу коммутаторов второй группы и через инвертор к управляющему входу коммутаторов первой группы, выходы которых соединены с группой входов-выходов блока оперативной памяти и группой информационных входов коммутаторов второй группы, второй вход второго элемента ИЛИ подсоединен к шине команд управления Конец обмена, а его выход - к входу Сброс регистра адреса, выход элемента сравнения подключен к первому входу первого элемента И, выход которого через первый и второй элементы задержки соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с входом

Сброс триггера блокировки, инверсный выход которого соединен с вторым разрешающим входом второго элемента И, выход первого элемента задержки подключен к

входу запись триггера блокировки, к второму входу четвертого элемента ИЛИ, а выход третьего элемента задержки - к тактовому входу D-триггеров выходного регистра. D- входы D-триггера выходного регистра подключены к соответствующим разрядам магистрали выдачи данных, выходы D-триггеров выходного регистра соединены через группу элементов гальванической развязки с группой информационных выходов устройства, выход второго элемента задержки соединен с третьим входом четвертого элемента ИЛИ, выход которого подключен к счетному входу регистра адреса, а через первый элемент ИЛИ, формирователь сигналов Разрешение выборки и пятый элемент ИЛИ соединен со вторым управляющим входом блока оперативной памяти, второй вход пятого элемента ИЛИ подсоединен к шине команд управления

Запись данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для ввода информации | 1991 |

|

SU1800452A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

| Устройство для захвата магистрали ЭВМ | 1982 |

|

SU1075247A1 |

Изобретение относится к вычислительной технике и автоматике, в частности к устройствам автоматического управления, где требуется включение различных механизмов в определенной последовательности во времени, и может быть использовано для управления технологическими процессами. Целью изобретения являются расширение области применения за счет автономности при выдаче команд, времени их появления и формирования по длительности и повышение точности выдачи всех команд относительно сигнала начало работы. Устройство содержит генератор 1 импульсов, регистр 2 адреса, блок оперативной памяти 3, триггер 4 пуска, счетчик импульсов 5, элемент 6 сравнения, первую 7 и вторую 8 группу коммутаторов, элементы ИЛИ 9-13, формирователь 14 сигнала разрешение выборки, инвертор 15, элемент И 16, три элемента задержки 17,19, 20, триггер 18 блокировки выходной регистр 21 на D-триггерах, группу 221...22N элементов гальванической развязки, магистраль 23 адрес-данные, шины 24 команд управления. 9-2-10-14-11-3-8--21-22. 4- 1-5-6-16-17-20-13-18-16, 20-12-2-3. 4- 15-7-3, 17-19-21.4 ил. С

25

Фиг 1

Шиг.2

Щ

НАЬАЛО)

t -.0;

О

ч

t nTo; n 0t1,2,... ;

То длительность лериодо. тО.то8ь/Х НМПуЯЬСоб:

Мк конец позиционной

комО.нЭы f

К - позиционная команда 6 данной временной

Выборке )

I -количество команд сущест&унэщцх в данной бакенной Вы&орке;

Кз ,з 3° 1ись/даемь/е Значень/ft хсдо&.

Фиг.3

(КОНЕЦ Фаг 3

Фиг. 4

| Программное временное устройство | 1974 |

|

SU532860A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 758154, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Программное устройство управления | 1983 |

|

SU1173414A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-09-15—Публикация

1990-11-11—Подача