Изобретение относится к цифровой .вычислительной технике и может быть использовано в системах ввода данных в ЭВМ для контроля одновременного нажатия клавиш в клавиатуре;

Известно устройство для контроля одновременного нажатия нескольких клавиш, содержащее элемент задержки и петли обратной связи на транзисторе по числу клавиш Cl.

Известно также устройство, содержащее схему формирования многоразрядного кода: при нажатии на каждую клавишу код поступает в контрольный декодер, где он вычитается из установленного Б регистре кодового сигнала, кроме, этого код нажатой клавиши поступает в выходной декодер. Если сумма выходных сигналов контрольного и выходного декодеров не достигает установленной величины, которая фиксируется устройством сравнения, вырабатывается сигнал об одновременном нажатии на две клавиши 2.

Основным недостатком указанных устройств является ограниченная надежность из-за сложности технической реализации и требуемого для этого большого количества элементов, которое при количестве клавиш 30 может превышать количество элементов для реализаций Функций самого устройства ввода.

Наиболее близким по тезснической сущности к предлагаемому является устройство для контроля одновременного нажатия клавиш, содержащее блок клавиатуры, блок анализа состояния клавиш, блок блокировки одновреtoменного нажатия клавиш, блок деблокировки одновременного нажатия клавиш, соединенные таким образом, что выводы блока клавиатуры соединены с входами блока состояния клавиш,

15 выходы блока анализа состояния клавиш соединены с входами блоков блокировки, выход блока блокировки поступает в устройство ввода ЭВМ З.

Недостатком известного устройст20ва является его сложность.

Цель изобретения - упрощение устройства.

Указанная цель достигается тем, что в устройство для КОНТРОЛЯ одновре25менного нажатия клавиш, содержащее триггер, единичный вход которого соединен с входом формирователя сигналов, выход которого подключен к нулевому входу триггера, выход которо30го является выходом устройства, введены анализатор четного числа сигналов и анализатор нечетного числа сигналов; входы.анализаторов четного и нечетного числа сигналов являются входами устройства, выходы анализаторов подключены к входу формирователя сигналов.

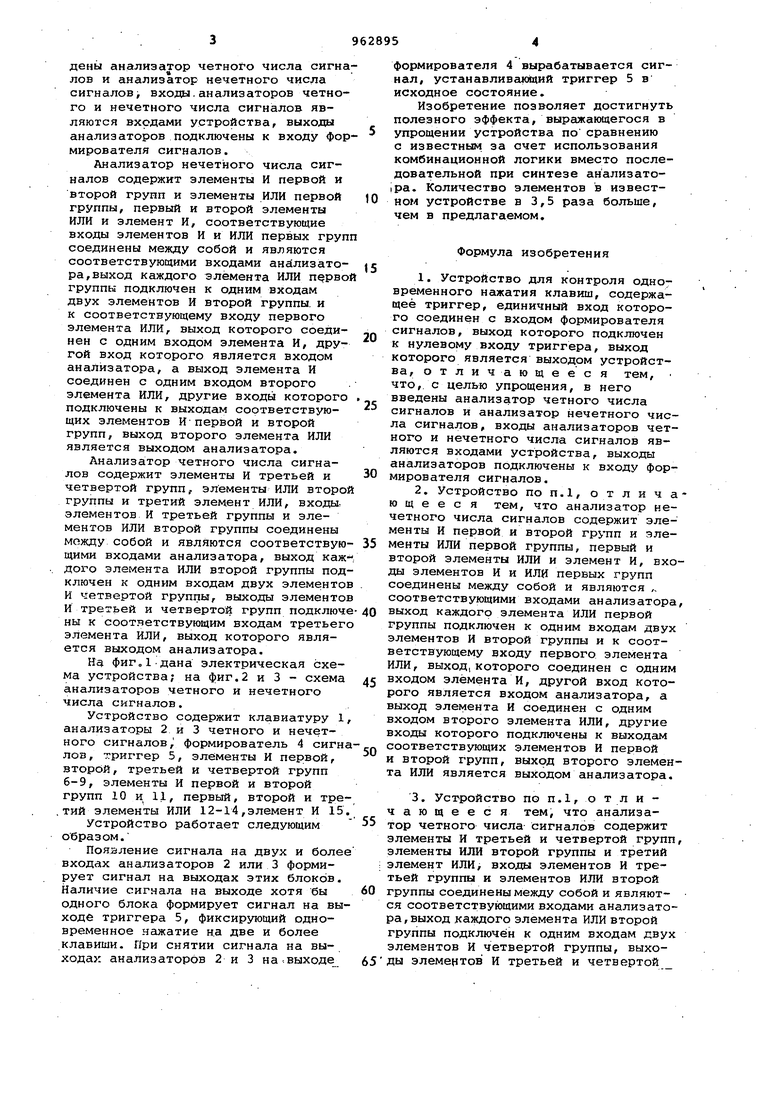

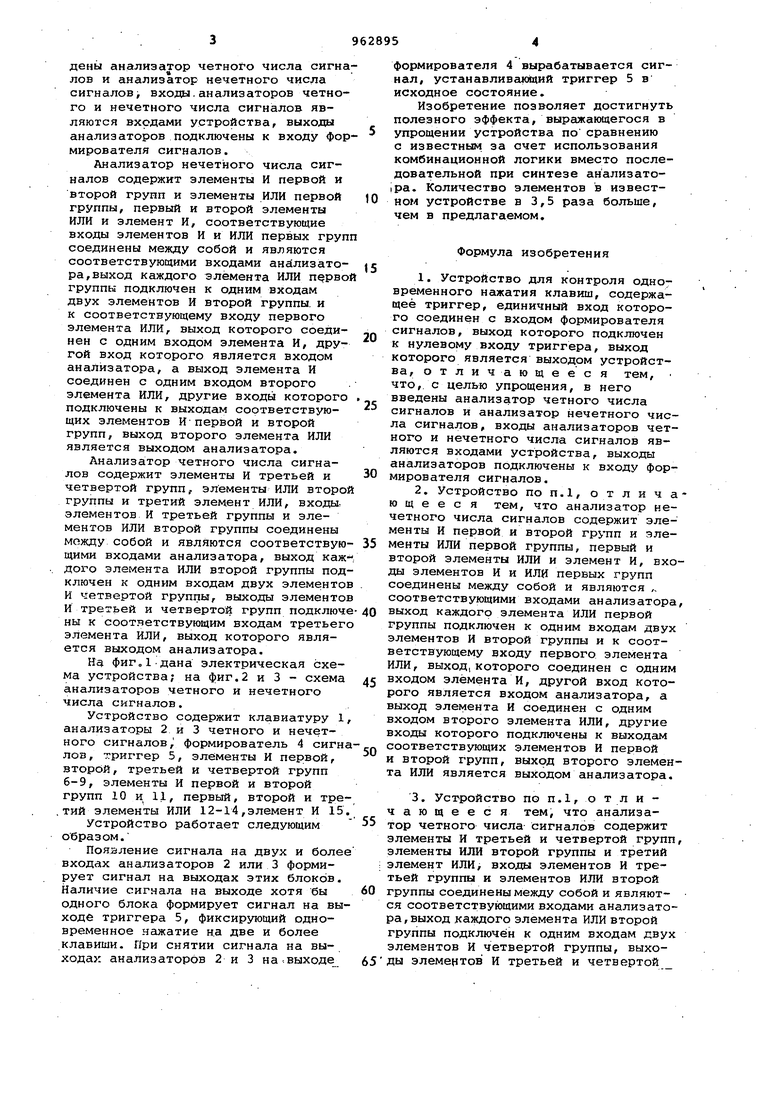

Анализатор нечетного числа сигналов содержит элементы И первой и второй групп и элементы ИЛИ первой группы, первый и второй элементы ИЛИ и элемент И, соответствующие входы элементов И и ИЛИ первых групп соединены между собой и являются соответствующими входами анализатора, выход каждого элемента ИЛИ первой группы подключен к одним входам двух элементов И второй группы, и к соответствующему входу первого элемента ИЛИ, выход которого соединен с одним входом элемента И, другой вход которого является входом анализатора, а выход элемента И соединен с одним входом второго элемента ИЛИ, другие входы которого подключены к выходам соответствующих элементов И первой и второй групп, выход второго элемента ИЛИ является выходом анализатора.

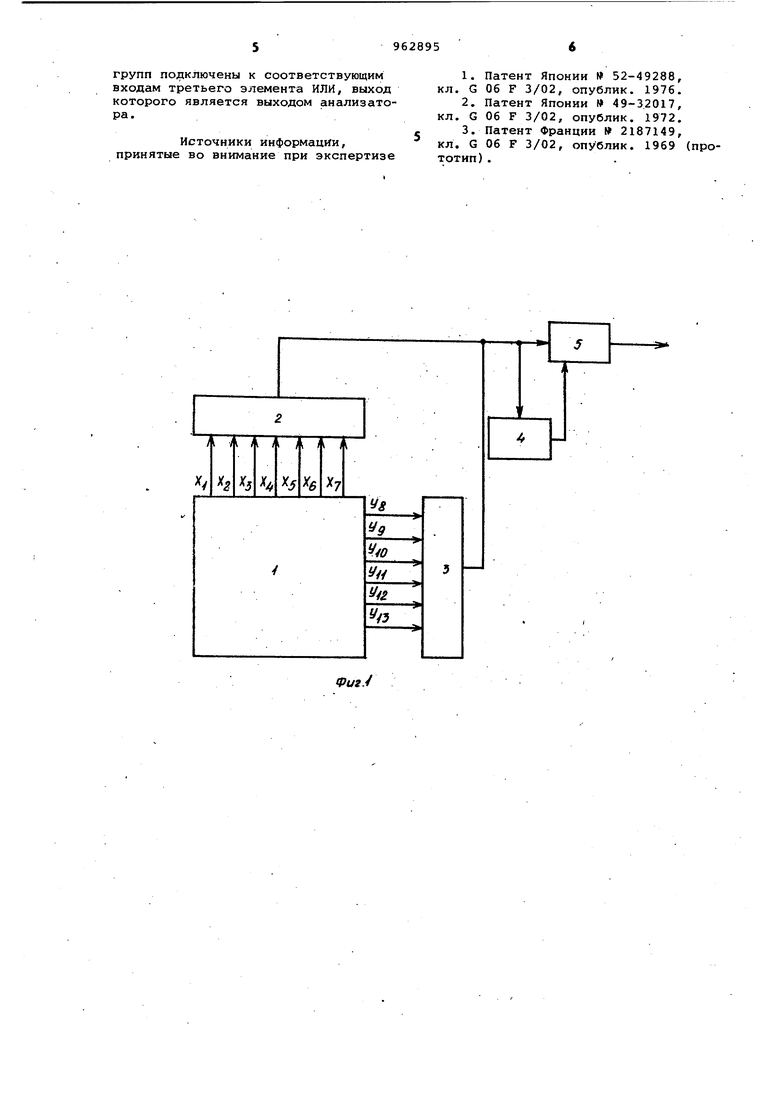

Анализатор четкого числа сигналов содержит элементы И третьей и четвертой групп, элементы ИЛИ второй группы и третий элемент ИЛИ, входы, элементов И третьей группы и элементов ИЛИ второй группы соединены можду собой и являются соответствующими входами анализатора, выход каждого элемента ИЛИ второй группы подключен к одним входам двух элементов И четвертой группы, выходы элементов И третьей и четвертой групп подключены к соответствующим входам третьего э:г1емента ИЛИ, выход которого является выходом анализатора.

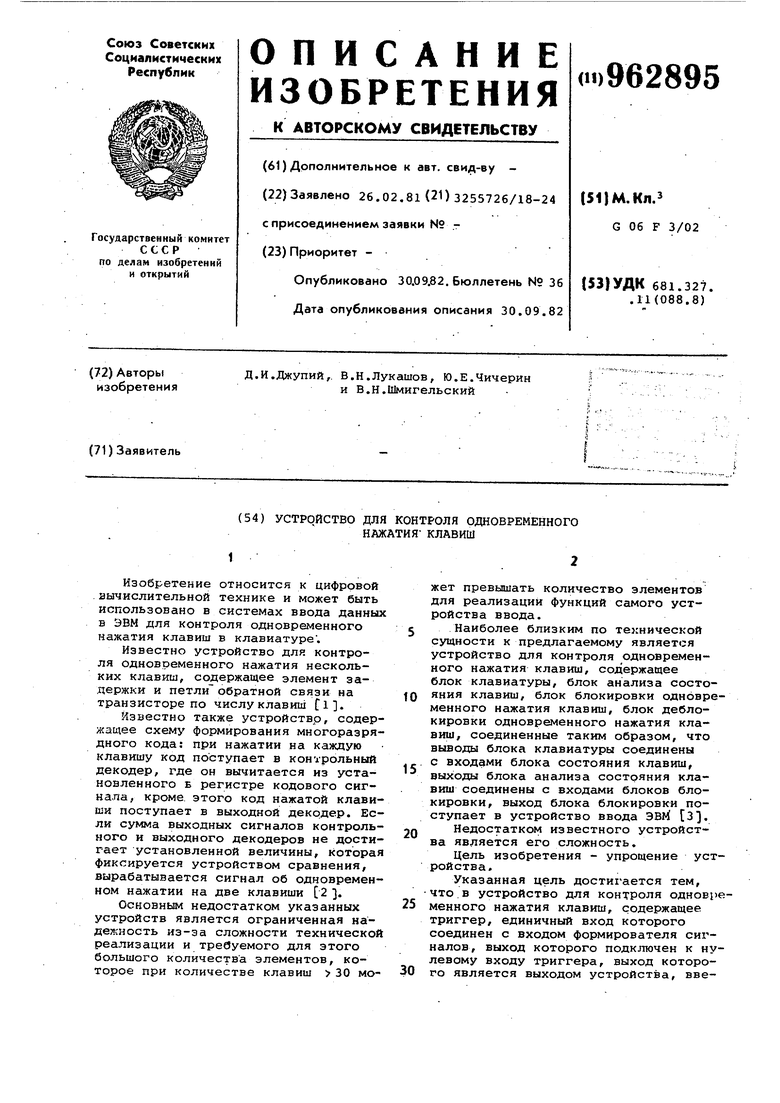

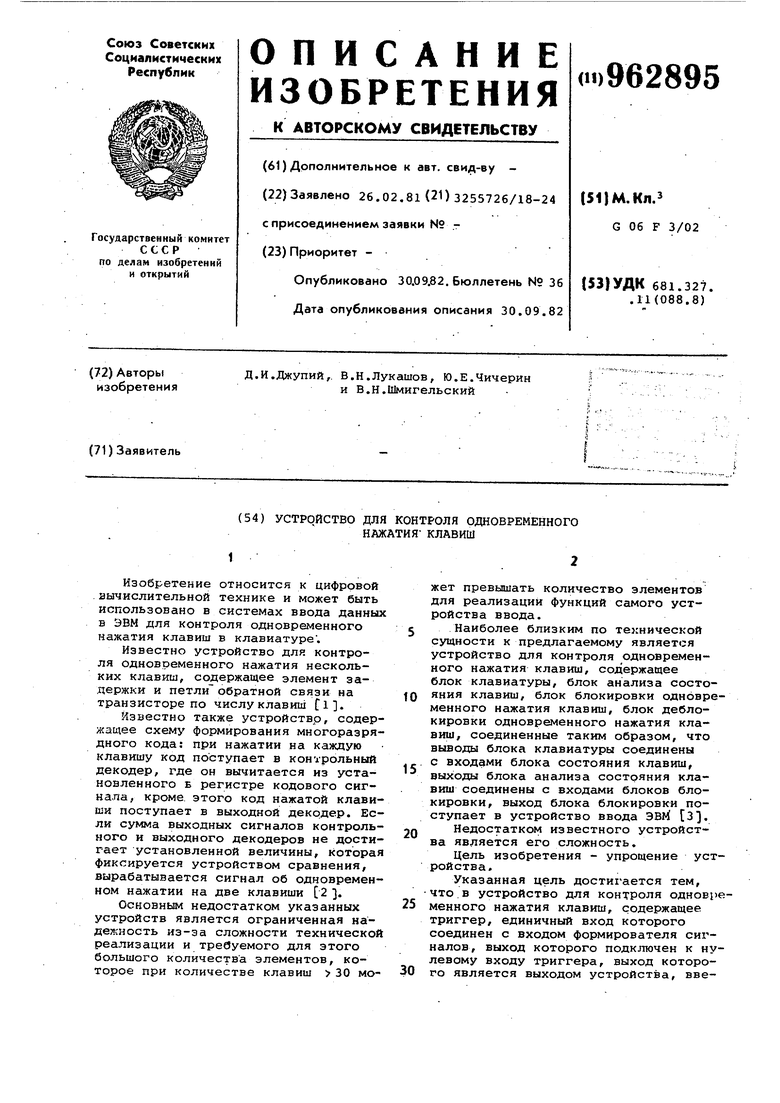

На фиг„1.дана электрическая схема устройства; на фиг.2 и 3 - схема анализаторов четного и нечетного числа сигналов.

Устройство содержит клавиатуру 1, анализаторы 2 и 3 четного и нечетного сигналов, формирователь 4 сигналов, триггер 5, элементы И первой, второй, третьей и четвертой групп 6-9, элементы И первой и второй групп 10 и, 11, первый, второй и тре.тий элементы ИЛИ 12-14,элемент И 15.

Устройство работает следующим образом.

Появление сигнала на двух и более входах анализаторов 2 или 3 формирует сигнал на выходах этих блоков. Наличие сигнала на выходе хотя бы одного блока формирует сигнал на выходе триггера 5, фиксирующий одновременное нажатие на две и более клавиши. При снятии сигнала на выходах анализаторов 2 и 3 на выходе

формирователя 4 вырабатывается сигнал, устанавливакиций триггер 5 в исходное состояние.

Изобретение позволяет достигнуть полезного эффекта, выражающегося в упрощении устройства по сравнению с известным за счет использования комбинационной логики вместо последовательной при синтезе анализатоipa. Количество элементов в известном устройстве в 3,5 раза больше, чем в предлагаемом.

Формула изобретения

1.Устройство для контроля одновременного нажатия клавиш, содержащее триггер, единичный вход которого соединен с входом формирователя сигналов, выход которого подключен к нулевому входу триггера, выход которого является выходом устройства, отличающеес я тем, что,, с целью упрощения, в него введены анализатор четного числа сигналов и анализатор нечетного числа сигналов, входы анализаторов четного и нечетного числа сигналов являются входами устройства, выходы анализаторов подключены к входу формирователя сигналов.

2.Устройство по П.1, от л и ч аю щ е е с я тем, что анализатор нечетного числа сигналов содержит элементы И первой и второй групп и элементы ИЛИ первой группы, первый и второй элементы ИЛИ и элемент И, входы элементов И и ИЛИ первых групп соединены между собой и являются ,, соответствующими входами анализатора выход каждого элемента ИЛИ первой группы подключен к одним входам двух элементов И второй группы и к соответствующему входу первого элемента ИЛИ, выход, которого соединен с одним входом элемента И, другой вход которого является входом анализатора, а элемента И соединен с одним входом второго элемента ИЛИ, другие входы которого подключены к выходам соответствующих элементов И первой

и второй групп, выход второго элемента ИЛИ является выходом анализатора.

3.Устройство по П.1, о т л и чающееся тем, что анализатор четного числа сигналов содержит элементы И третьей и четвертой групп элементы ИЛИ второй группы и третий элемент ИЛИ, входы элементов И третьей группы и элементов ИЛИ второй группы соединены между собой и являются соответствующими входами анализатора, выход каждого элемента ИЛИ второй группы подключён к одним входам двух элементов И четвертой группы, выходы элементов и третьей и четвертой

групп по;с1ключены к соответствующим входам третьего элемента ИЛИ, выход которого является выходом анализатора.

Источники информации, принятые во внимание при экспертизе

1.Патент Японии 52-49288, кл. G Об F 3/02, опублик. 1976.

2.Патент Японии 49-32017, кл. G 06 F 3/02, опублик. 1972.

3.Патент Франции № 2187149,

кл. G 06 F 3/02, опублик. 1969 (прототип) .

/4

Б 1 Гл t

L

У/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1980 |

|

SU885986A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЕЛ ИЗ ДЕСЯТИЧНОЙ В ДВОИЧНУЮ СИСТЕМУ СЧИСЛЕНИЯ | 1991 |

|

RU2006909C1 |

| Устройство для ввода и вывода информации | 1985 |

|

SU1265755A1 |

| Синтезатор сигналов для электромузыкального инструмента | 1979 |

|

SU864326A1 |

| Устройство для дистанционного управления топливораздаточными колонками | 1983 |

|

SU1117678A1 |

| Устройство для ввода-вывода информации | 1989 |

|

SU1686432A1 |

| Устройство для психологических исследований | 1989 |

|

SU1688845A1 |

| Устройство для ввода и вывода информации | 1982 |

|

SU1048466A1 |

| Устройство для управления вызовом информации | 1985 |

|

SU1300540A1 |

Авторы

Даты

1982-09-30—Публикация

1981-02-26—Подача