первого по шестой элементы И, первые входы первого и второго элементов И соединены соответственно с первым и вторым входами формирователя одиночных импульсов, и являются первым и вторым входами блока управления соответственно, выход формирователя одиночных импульсов подключен к вторым входам первого и второго элементов И, выход первого тригге ра соединен с первым входом третьего элемента И, выход первого элемента И соединен с первым входом смчронизатора по тактовым импульсам выход которого подключен к второму входу третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу четверто го элемента И, а выход является вось мым выходом блока, выход второго слемента И соединен с первыми входами четвертого, пятого и шестого элементов И, первые входы счетчика -актовых импульсов и формирователя управляющих импульсов являются третьим входом блока, второй вход счетчика тактовых импульсов и первый вход счетчика кодов адресов соединены с выходом шестого элемента И и являются первым выходом блока, выход 66 счетчика тактовых импульсов соединен с вторыми входами счетчика кодов адресов и формирователя управляющих импульсов, выходы которых являются группой выходов блока и третьим и четвертым его выходами, пятый выход блока объединен с вторым входом синхронизатора по тактовым импульсам, выход пятого элемента И подключен к входу установки в ноль первого триггера, выход четвертого элемента ИЛИ соединен с входом установки в ноль второго триггера и с вторым входом i шестого элемента И, выход пятого элемента ИЛИ подключен к второму входу четвертого элемента И, первые и вторые входы четвертого и пятого элементов ИЛИ соединены с входами установки в единицу и в ноль третьего и четвертого триггеров соответственно, вход установки в единицу первого триггера, соединенный с входом установки в единицу второго триггера, второй вход пятого элемента И, первые и вторые входы четвертого и пятого элементов ИЛИ являются соответствующими входами группы блока, выходы второго, третьего и четвертого триггеров являются шестым, вторым и седьмым выходами блока соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода и вывода информации | 1985 |

|

SU1265755A1 |

| Устройство для ввода и вывода информации | 1980 |

|

SU920692A1 |

| Устройство для ввода информации | 1983 |

|

SU1092486A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Устройство для ввода информации | 1985 |

|

SU1327087A1 |

| Устройство для управления дозированием | 1986 |

|

SU1310795A1 |

| Электронная клавишная вычислительная машина | 1982 |

|

SU1068945A1 |

| Устройство для формирования и передачи сообщения | 1990 |

|

SU1778767A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Динамический шифратор позиционного кода | 1988 |

|

SU1545328A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах с вводом информации от клавиатуры, в частности для ввода и вывода информации о параметрах выходного сигнала, вырабатываемого синтезатором частоты

Известно устройство для ввода-вывода информации в автоматизированных системах управления, содержащее клавиатуру , подключенную через шифратор к регистру сдвига, выход которого соединен с входом регистра индикации, блок индикации, через элементы И подключенный к регистру индикации, регистр команд, выход которого через дешифратор команд подключен к блоку управления, и блок синхронизации Q .

Наиболее близким по технической сущности к изобретению является устройство для ввода.и вывода информации, содержащее клавиатуру, первый шифратор, регистр индикации, буферный регистр, первый элемент ИЛИ, первый и второй регистры, мультиплексор, преобразователь двоичного кода в де- . сятичный, группу мультиплексоров, блок индикации, второй шифратор, второй элемент ИЛИ, дешифратор, блок

управления и генератор тактовых -импульсов 2j.

К Недостаткам известного устройства можно отнести снижение быстродействия При корректировке значений частоты,лежащих на границе между разрядами.

Цель изобретения - повышение быстродействия устройства.

Указанная цель достигается тем, что в устройство дПя ввода и вывода

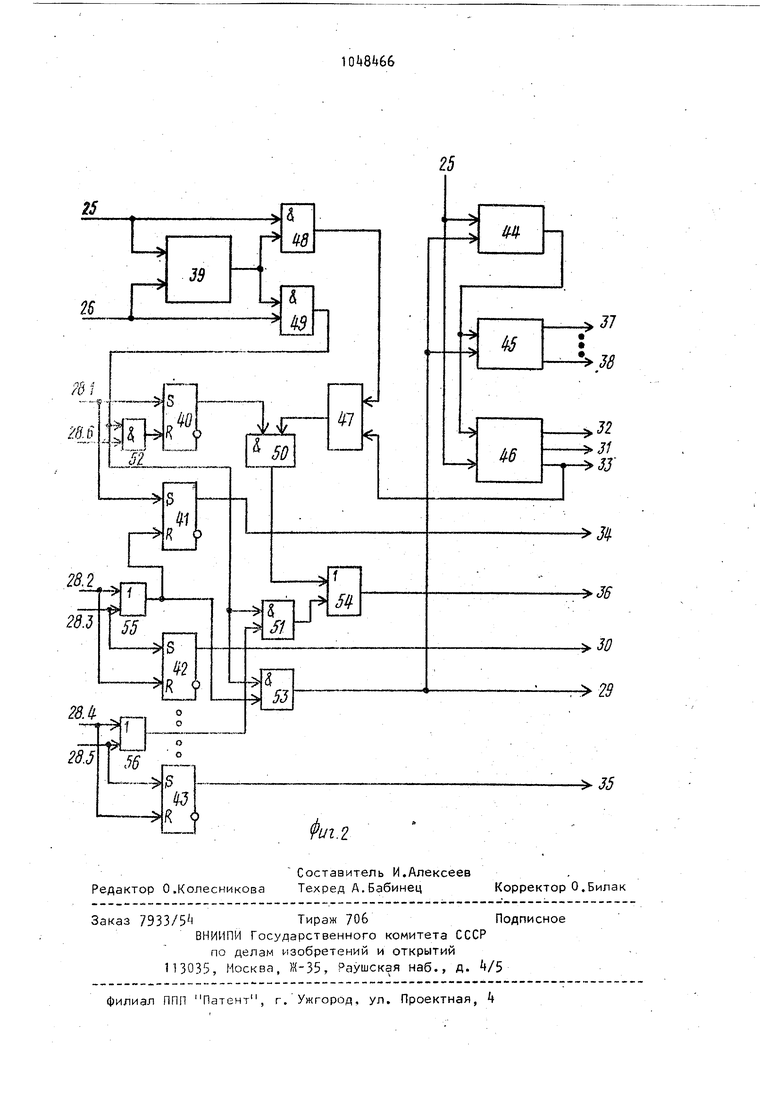

информации, содержащее, клавиатуру цифр, выход которой соединен с входом первого шифратора, выход которого через первый элемент ИЛИ соединен с первым входом блока упрабления, генератор тактовых импульсов, клавиатуру операций, выход кото рой через второй шифратор подключен к входам второго элемента ИЛИ дешифратора, выходы которых и выход генератора тактовых импульсов подключены к второму входу, группе входов и к третьему входу блока управления соответственно, выходы блока управления, с первого по четвертый, подключены к входам синхронизации и реверса счетчика номеров разрядов, входами чтение-запись и обращения блока памяти соответственно, выходы группы блока управления соединены с адресными входами групп блока памяти входами блока индикации и рлока муль типдексоров, выход блока мульти.плексоров подключен к входу данных блока памяти, выход которого соединен с входом данных блока индикации и является выходом устройства, выходы счетчика номера разряда подключены к соответствующим входам преобразова теля кодов, введены .буферный и сдвигающий регистры и блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, один из входов первой группы которого является входом устройства, другие входы первой груп пы подключены к соответствующим выхо дам переноса буферного регистра, входы второй группы блока элементов. ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выхода-. ми группы преобразователя кодов, вых ды группы - с соответствующими входа ми переноса буферного регистра, входы установки которого подключены к г соответствующим выходам сдвигающего регистра, информационные выходы - к соответствующим информационным входа блока мультиплексоров, пятый и шесто выходы блока управления соединены с синхронизирующим и установочным входами сдвигающего регистра, седьмой выход блока управления соединен с ; входом реверса буферного регистра, восьмой выход - с входом синхронизации буферного регистра и с входом данных сдвигающего регистра, выход первого шифратора подключен к входу данных буферного регистра. Блок управления содержит с пер- вого по четвертый триггеры, формирователь одиночного импульса, синхронизатор по тактовым импульсам, формирователь управляющих импульсов .счетчики тактовых импульсов и кода адре- са, с третьего по пятый элементы ИЛИ, с первого по шестой элементы И, первые входы первого и второго элементов И соединены соответственно с первым и вторым входами формирователя одиночных импульсов и являются первым и вторым входами блока управления соответственно, выход формирователя одиночных импульсов подключен к вторым входам первого и второго элементов И, выход первого триггера соединен с первым входом третьего элемента И, выход первого элемента И соединен с первым входом синхронизатора по тактовым импульсам, выход которого подключен к второму входу третьего элемента .И, выс первым вхо которого соединен дом третьего элемента ИЛИ, второй вход которого подключен к .выходу четвертого элемента И, а выход является восьмым выходом блока, выход второго элемента И, а выход является восьмым выходом блока, выход второго элемента И соединен с первыми входами четвертого, пятого и шестого элементов И, первые входы счетчика тактовых импульсов и формирователя управляющих импульсов являются .третьим входом блока, второй вход счетчика тактовых импульсов и первый вход счетчика кодов адресов соединены с выходом шестого элемента И и являются первым выходом блока, выход счетчика тактовых импульсов соединен с вторыми входами счетчика кодов адресов и формирователя управляющих импульсов, выходы которых являются группой выходов блока и третьим, четвертым его выходами блока, пятый выход блока соединен с вторым входом синхронизатора по тактовым импульсам, выход пятого элемента И подключен к входу установки в ноль первого триггера, выход четвертого элемента ИЛИ соединен с входом установки в ноль второго триггера и с вторым входом шестого элемента И, выход пятого элемента ИЛИ подключен к второму входу четвертого элемента И, первые и вторые входы четвертого и пятого элементов ИЛИ соединены с входами установки в единицу и в ноль третьего и четвертого триггеров соответственно, вход установки в единицу первого триггера, соединенный с входом установки в единицу второго триггера, второй вход пятого элемента И, первые и вторые входы четвертого и пятого элементов ИЛИ являются соответствующими входами группы блока, выходы второго, третьего и четвертого триггеров являются шестым, вторым и седьмым выходами блока соответственно.

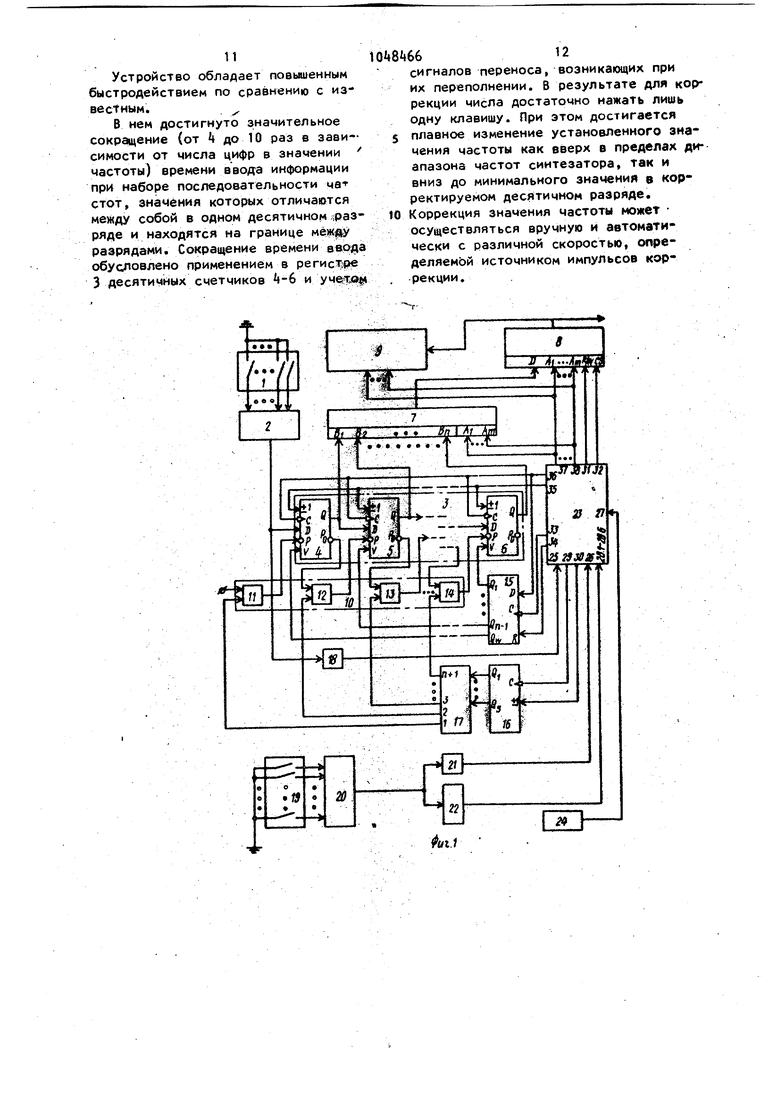

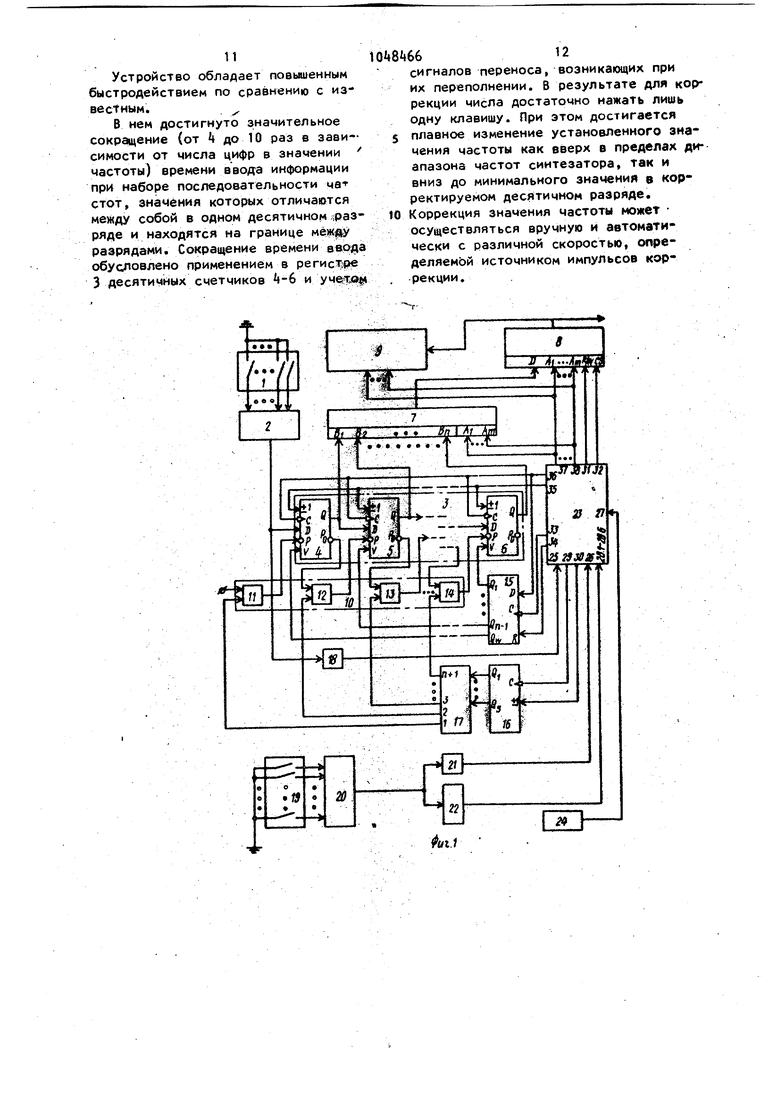

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - схема блока управления.

На фиг. 1 и 2 обозначены: клаbi-iarypa 1 цифр, первый шифратор 2, буферный регистр .3, состоящий из реверсивных счетчиков-регистров 4-6 ,-lУJ bTиплeкcopoв 7, блок памяти 8 в виде оперативного запоминающего уст.ройства (ОЗУ), блок индикации 9, блок 10 элементов 11-1 ИСКЛЮЧАЮii EE ИЛИ, сдвигающий регистр 15, счетчик 6 номера разряда, преобразователь кода 17 первый элемент ИЛИ 18, клавиатура 19 операций, второй шифратор 20, второй элемент ИЛИ 21, дешифратор 22, блок 23 управления и генератор 2 тактовых импульсов, с первого по третий входы блока управления 25-27, входы группы блока управления 28,1-28,6, выходы блока управления 29-36, выходы группы блока управления 37, 38, формирователь 39 одиночных импульсов, триггеры А0-43 признака операции, счетчик А тактовых импульсов, счетчик kS кода адреса ОЗУ, формировател управляющих импульсов +6, синхронизатор по тактовым импульсам 47, а также элементы И 48-53 и ИЛИ .

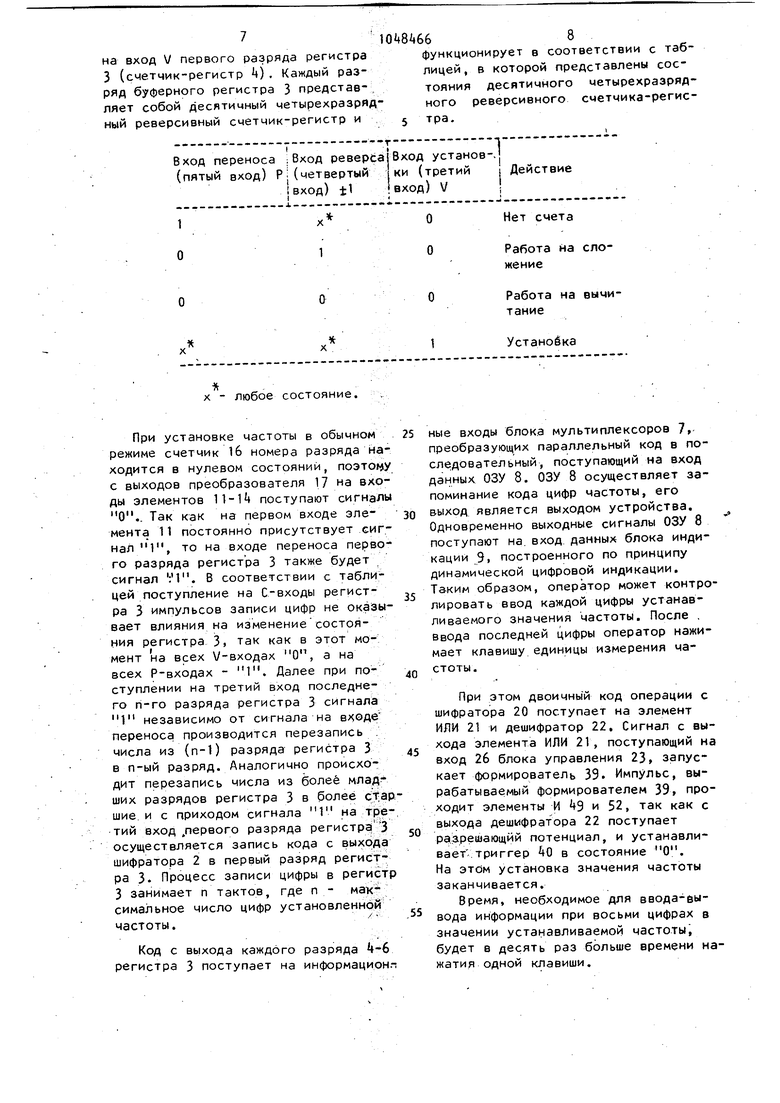

Счетчики-регистры 4-6, входящие в буферный регистр 3, предназначены для хранения двоичного кода цифры -соответствующего разряда. Каждый регистр 4-6 представляет собой десятичный четырехразрядный реверсивный счетчик с параллельным вводом и выводом информации.

Устройство работает следующим образом.

В исходном состоянии тактовые импульсы поступают на вход 27 блока управления 23 от генератора тактовых импульсов , обеспечивая появление на выходах 37...38 блока управления 23 сигналов управления синхронной работой блока мультиплексоров 7s ОЗУ 8 и блока индикации 9, а также - на выходах 31 и 32 сигнаЛОВ управления записью и считыванием информации ОЗУ 8.

В зависимости от характера работы с синтезатором частоты оператор нажимает ту или иную клавишу клавиатуры 19 операций. Такими операциями могут быть Установка частоты, Установка уровня, Единица измерения частоты, Выбор корректируемого разряда, справа-налево, Выбор корректируемого разряда слева - направо, Корректировка числа вверх, Корректировка числа вниз и т.п.

Предположим, что оператор осуществляет установку частоты выходного сигнала генератора. При этом шиф- ратор 20 (фиг. 1) осуществляет преобразование- десятичного кода операции в двоичной четырехразрядный код,

поступающий на второй элемент ИЛИ 21 и на дешифратор 22. Сигнал, поступающий с выхода дешифратора 22 на вход 28.1 блока управления 23, устанавливает триггер 40 (фиг. 2) в состояние 1. Далее оператор осуществляет набор значения частоты, последовательно нажимая клавиши цифр (первой набирается цифра старшего десятичного разряда). При этом шифратор 2 (фиг. 1) преобразует десятичный код цифры в двоичный код, поступающий на О-вход первого разряда буферного регистра 3 и на вход первого элемента ИЛИ 18. Сигнал с выхода элемента ИЛИ 18, поступающий на вход 25 блока управления 23, запускаетформирователь 39 одиночного импульса. Импульс положительной полярности, вырабатываемый формирователем 39, проходит элемент И 48 и попадает на вход синхронизатора 47 ло тактовым импульсам, формируемым формирователем k6. С выхода синхронизатора 7 импульс длительностью равной периоду тактовых импульсов через элемент И 50 и элемент ИЛИ Sk поступает на С-входы разрядов буферного регистра Зи на1)-вход , сдвига.юще.го регистра - 15, на .С-вход которого подаются тактовые импульсы с выхода 33 блока управления 23. Сдвигающий регистр 15 на своих выходах обеспечивает импульсы, сдвинутые один относительно -другого на период тактовых импульсов. При этом импульсы с выхода первого разряда Q. регистра 15 поступают на вход V последнего разряда буферногорегистра 3 (счет1 ик-регистр 6) , а импульсы с выхода последнего разряда Q( регистра 15 на вход V первого разряда регистра 3 (счетчик-регистр k). Каждый разряд буферного регистра 3 представ-, ляет собой десятичный четырехразрядный реверсивный счетчик-регистр и

X - любое состояние.

При установке частоты в обычном режиме счетчик 1б номера разряда находится в нулевом состояний, поэтог у с выходов преобразователя 17 на входы элементов ll-l поступают сигналы О.. Так как на первом входе элемента 11 постоянно присутствует сигнал, то на входе переноса первого разряда регистра 3 также будет сигнал :М. В соответствии с таблицей поступление на С-входы регистра 3 импульсов записи цифр не оказывает влияния на изменениесостояния регистра 3, так как в этот момент на всех V-входах О, а на всех Р-входах - 1. Далее при поступлении на третий вход последнего п-го разряда регистра 3 сигнала 1 независимо от сигнала на переноса производится перезапись . числа из {п-1) разряда регистра 3 в п-ый разряд. Аналогично происходит перезапись числа из более млад ших разрядов регистра 3 в более старшие, и с приходом сигнала 1 на тре-, тий вход .первого разряда регистра3 осуществляется запись кода с выхода шифратора 2 в первый разряд регистра 3. Процесс записи цифры в регистр 3 занимает п тактов, где п - максимальное число цифр установленнс й частоты.

Код с выхода каждого разряда k-6 регистра 3 поступает на информационп

Нет счета

Работа на жение

Работа на тание

Установка

ные входы блока мультиплексоров 7, преобразующих параллельный код в последовательный, поступающий на вход данных ОЗУ 8. ОЗУ 8 осуществляет запоминание кода цифр частоты, его выход является выходом устройства. Одновременно выходные сигналы ОЗУ 8 поступают на. вход данных блока индикации Э, построенного по принципу динамической цифровой индикации. Тзким образом, оператор может контролировать ввод каждой цифры устанавливаемого значения частоты. После , Ввода последней цифры оператор нажимает клавишу единицы измерения частоты.

При этом двоичный код операции с шифратора 20 поступает на элемент ИЛИ 21 и дешифратор 22, Сигнал с выхода элемента ИЛИ 21, поступающий на вход 26 блока управления 23, запускает формирователь 39. Импульс, вырабатываемый формирователем 39, проходит элементы И +9 и 52, так как с выхода деш1(фратора 22 поступает РЭ.арешающйй потенциал, и устанавливает, триггер в состояние О. На этом установка значения частоты заканчивается.

Время, необходимое для ввода-вывода информации при восьми цифрах в значении устанавливаемой частотыi будет в десять раз больше времени нажатия одной клавиши. +ВАбб8 функционирует в соответствии с таб лицей, в которой представлены состояния десятичного четырехразрядного реверсивного счетчика-регистра. Если необходимо изменить ранее введенное значение частоты в младше десятичном разряде, то оператор нажимает сначала клавишу Выбор корре тируемого разряда справа-налево. П этом двоичный код операции с шифратора 20 поступает на вход 28.3 бл ка управления .23 (фиг. 2), проходит через элемент ИЛИ 55 и устанавливае триггер 1 в состояние 1. Кроме того, сигнал с выхода элемента ИЛИ 55 разрешает прохождение одиноч ного импульса с выхода формирователя 3 через элемент И 53 на сброс счет чиков и 5 и на выход 29 блока у равления 23. Сигнал с выхода дешифратора 22 устанавливает также тригге k2 в состояние 1. Сигнал с выхода триггера 2 поступает на выход 30 блока управления 23 и определяет направление смета в счетчике 16, В результате импульс, поступающий на тактовый вход счетчика Тб с выхода 29 блока управления 23, увеличивает его содержимое на единицу. Соответственно на первом выходе преобразователя 17 появляется сигнал 1, а на. выходе элемента 11 (входе переноса Р первого разряда регистра 3) сигнал О. На входах переноса Р остальных разрядов регистра 3 продолжает оставаться сигнал 1, Далее в зависимости от Направления корректировки числа оператор нажимает клавишу Корректировка числа вверх или Корректировка числа вниз. Пусть необходимо увеличить чи ло в младшем |эазряде установленного значения частоты. Тогда досле нажатия клавиши Корректировка, числа вверх триггер 3 устанавливается в состояние 1 сигналом с выхода дешифратора 22. Выходной сигнал триггера определяет направление изменения числа в младшем разряде регистра 3 в соответствии с Таблицей. Кроме того, сигнал с выхода дешифратора 22, прошедший через элементы ИЛИ 5б, И 51 и Или 5, поступает на тактовые входы регистра 3. Так как только у счетчика t младшего разряда регистра 3 сигнал на входе переноса Р.равен О, то его состояние увеличится на 1. Состояние остальных разрядов при этом не изменится. Для того, чтобы увеличить состояние счетчика младшего разряда еще +6610 на единицу, необходимо нажать еще раз клавишу Корректировка числа вверх и т.д. Если число в счетчике-регистре k окажется после нескольких нажатий равным девяти, то сигнал на выходе переполнения станет равным О. Такой же сигнал будет и на входе переноса Р счетчика-регистра 5 второго разряда регистра 3. Поэтому при последующем нажатии клавиши Корректировка числа вверх состояниесчетчика-регистра становится равным нулю, а состояние счетчика-регистра 3 равным единице,Таким образом, в отличие от известного устройствакорректировка значения частоты осуществляется с учетом сигнала переноса в следующий, более старший разряд, что существенно сокращает время ввода информации, при корректировке значений частоты, лежащих на границе между разрядами. Учитывая, что откорректированйое значение частоты практически мгновенно поступает на выход устройства, пройдя блок 7 мультиплексоров и ОЗУ 8 , время необходимое, для ввода равно 7в1 Ц, где t --время нажатия одной клавиши. Для известного устройства в аналогичном случае время корректировки Тв2 равно времени нового набора. Если необходимо уменьшить значение установленной частоты, то оператор нажимает клавишу Корректировка числа вниз. 8 этом случае триггер 43 переключается в состояние О сигналом с выхода /дешифратора 22. Тогда cчetчики-peгиcтpы -6 регистра 3 будут работать на вычитание при поступлении импульсов с выхода 36 блока управления 23 на тактовые входы С регистра 3. При уменьшении числав корректируемом разряде регистра 3 до нуля осуществляется заем единицы из более старших разрядов. Следовательно, плавность корректировки частоты и в этом случае сохраняется. Номер корректируемого разряда в значении- частоты определяется количеством нажатий клавиши Выбор корректируемого разряда справа-налево. Если необходимо уменьшить номер корректируемого разряда, то оператор нажимает клавишу Выбрр корректируемого разряда слева-направо. При этом число, зафиксированное .в счетчике 16, меньшается на единицу.

11

Устройство обладает повышенным быстродействием по сравнению с известным.

В нем достигнуто значительное сокращение (от k до 10 раз а зависимости от числа цифр в значении частоты) времени информации при наборе последовательности частот, значения которых отличаются между собой в одном десятичном разряде и находятся на границе мё:ж0 разрядами. Сокращение времени обусловлено применением в рагистгре 3 десятичных счетчиков -б и

сигналов переноса, возникающих при их переполнении. В результате для кор рекции числа достаточно нажать лишь одну клавишу. При этом достигается 5 плавное изменение установленного зна чения частоты как вверх а пределах диапазона частот синтезатора, так и вниз до минимального значения в корректируемом десятичном разряде.

10 Коррекция значения частоты ножет осуществляться вручную и автоматически с различной скоростью, определяемой источником импульсов кор. рекции. .

Авторы

Даты

1983-10-15—Публикация

1982-05-21—Подача