(S) УСТРОЙСТВО для ИСПЫТАНИЯ ДИСКРЕТНЫХ ИНТЕГРАТОРОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для испытания дискретныхиНТЕгРАТОРОВ | 1979 |

|

SU822302A1 |

| Устройство для измерения погрешности дискретных электрохимических интеграторов | 1983 |

|

SU1137543A1 |

| Устройство для контроля дискретных интеграторов | 1985 |

|

SU1397980A1 |

| Автоматическое измерительное устройство для определения параметров дискретных интеграторов | 1976 |

|

SU555453A1 |

| Устройство для испытаний дискретных электрохимических интеграторов | 1980 |

|

SU953676A1 |

| ЭЛЕКТРОХИМИЧЕСКОЕ ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU284156A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| Цифровой измеритель резистивных параметров кабеля | 1986 |

|

SU1406517A1 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ | 1984 |

|

SU1841014A1 |

| ЦИФРОВОЙ АНАЛИЗАТОР ВРЕМЕИНЫХ ХАРАКТЕРИСТИК ТРАНЗИСТОРНЫХ СХЕМ | 1971 |

|

SU297011A1 |

Изобретение относится к системам автоматического контроля и может быть использовано при исследованиях и испытаниях интеграторов дискретного действия.

По основному авт. св. № 822302 известно устройство для испытания дискретных интеграторов, обеспечивающее проверку погрешности зарядноразрядного цикла при многократном циклировании, содержащее генератор меток, соединенный со схемой управления; генератор тока разряда, который через логический ключ соединен с выходом, схемы управления, а второй выход этого логического ключа подключен к последовательно соединенным счетчику времени разряда, дешифратору и индикаторному устройству; генератор тока заряда, который через второй логический ключ также соединен со схемой управления, а второйвыход этого ключа подключен к последовательно, соединенным счетчику времени заряда, дешифратору и индикат6|эному устройству, при этом дешифратор этой цепи и задатчик времени заряда через схему совпадения подключены к схеме управления. Генераторы тока заряда и разряда соединены также с 1исследуемым интегратором, который через параллельно включенные устройство сравнения и схему защиту подключен к схеме управления. Кроме того, имеется, цепочка последовательно соеди- , ненных между собой и подключенных к схеме управления через логический ключ счетчика циклов, дешифратора и индикаторного устройства 1.

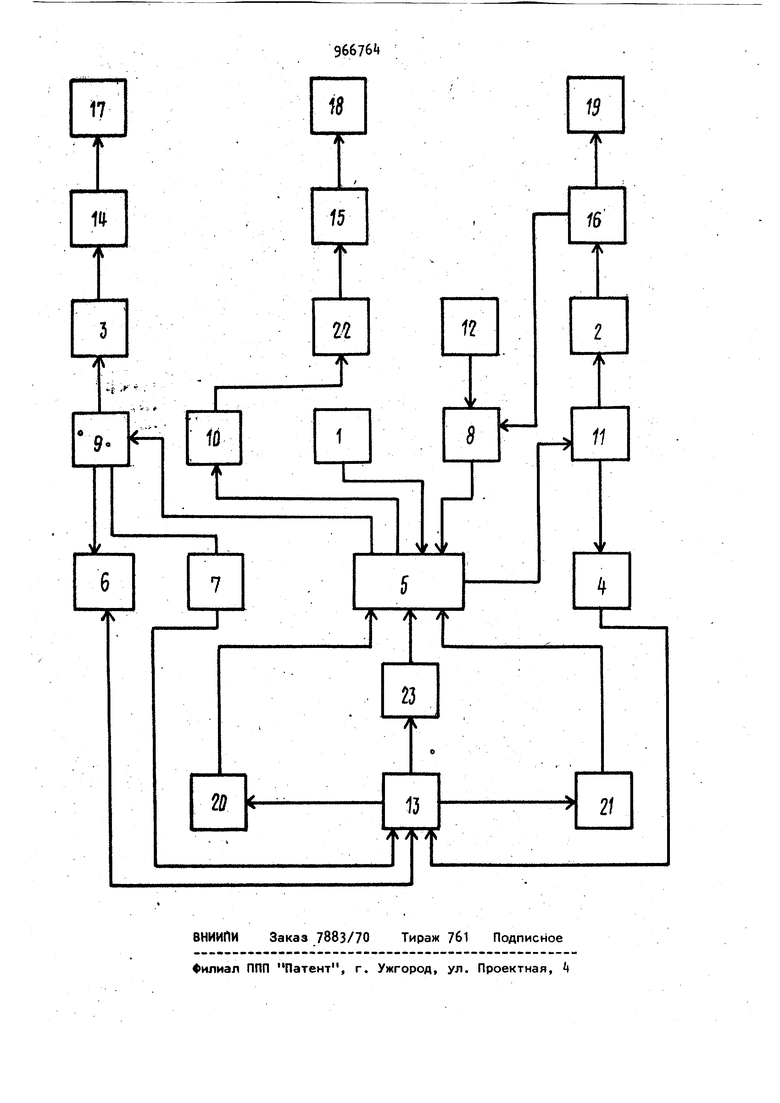

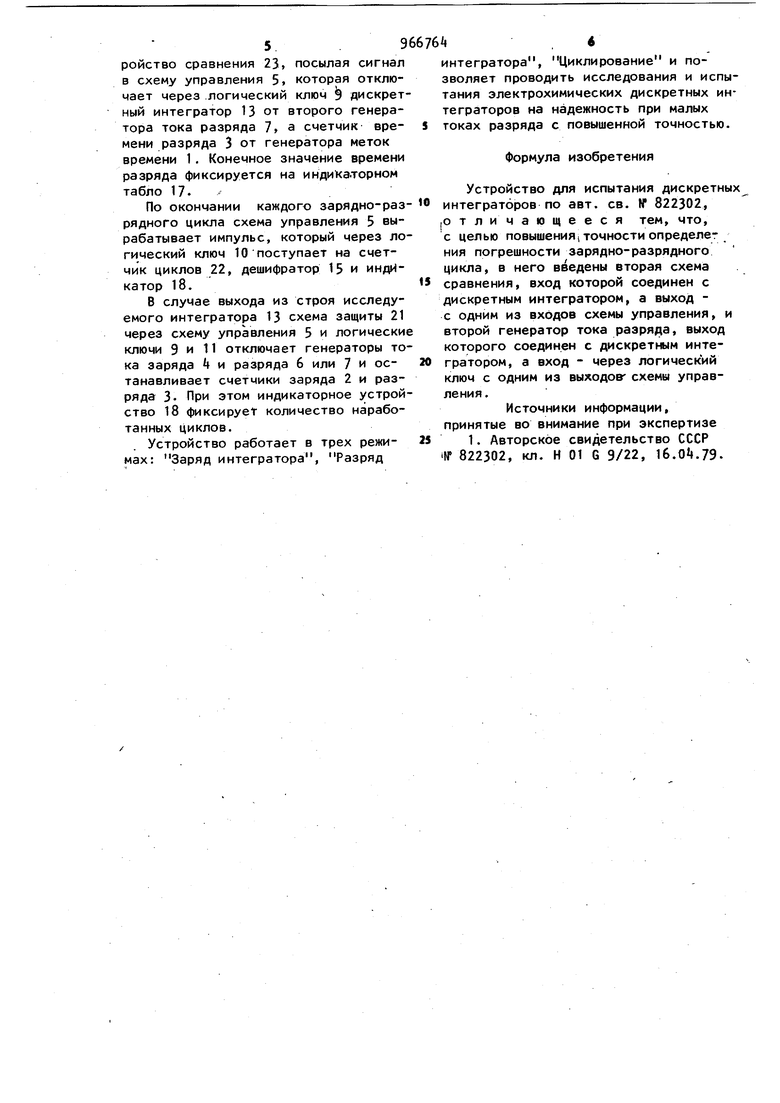

Недостатком известного устройства является дополнительная погрешность, возникающая при разряде интеграторов малым током, менее 10 мкА и обусловленная тем,что при малых токах разряда напряжение отсечки(пддение напряжения на электродах интег затора Ьосле выработки рабочего вещества) нарастает медленно вследствие протекания на электрбдах неуправляемых электрохимических процессов не связанных с переносом основного рабочего вещества. При этом для различных интеграт .ров наблюдается значительный разброс по времени протекания этих Лроцессов. Цель изобретения - повышение tO4ности определения погрешности зарядно-разрядного цикла. Указанная цель достигается тем, что в устройство для испытания дискретных интеграторов введены вторая схема сравнения, вход которой соединен с дискретным интегратором, а выход - с однсм из входов схемы управления, и второй генератор тока разря да, выход которого соединен дискретным интегратором, а вход - через :логический ключ с одним из выходов схемы управления .На чертеже представлена структурная схема устройства. «Устройство содержит генератор меток врЬмени 1 , счетчик времени заряда 2, счетчик времени разряда 3, ге нератор тока заряда Ц, схему управления 5 первый генератортока разряда 6, второй .генератор тока разряда 7 схему совпадений 8, логические ключи , задатчик времени заряда 12, дискретный интегратор,13. дешифраторы , индикаторные устройства первое устройство сравнения 20, схему защиты 21, счетчик цик лов 22 и второе устройство сравнения 23 Устройство работает следующим образом. При необходимости занесения в интегратор определенного количества электричества при известной величине тока заряда оператор задает необходимое время заряда задатчиком BPJ мени заряда 12. При этом соответству щий выход дешифратора 16 счетчика вр мени заряда 2 подключается к схеме совпадения 8. Время заряда начинается при подаче оператором команды Пуск в схему управления 5- При этой команде схема управления 5 подключает дискретный интегратор 13 к генератору тока заря да k через логический ключ 11. Одновременно со- схемой управления 5 и логическим Ключом 11 разрешается лро хождение импульсовс генератора меток времени 1 на счетчик времени заряда 2, дешифратор 16 и индикатор 19. По Л мере заполнения счетчика на индикаторном табло индицируется время заряда дискретного интегратора. По окончании заданного времени положи.тельный уровень с дешифратора 16 поступает на схему совпадения 8, которая через схему управления 5 и логический ключ 11 отключает дискретный интегратор 13 от генератора тока заряда Ц, а счетчик времени заряда 2 от генератора меток времени 1. Конечное значение врейени заряда фиксируется на индикаторном табло 19. При необходимости снятия с интегратора занесенного количества электричества при малом токе разряда оператор задает его величину первым ге-: нератором тока разряда 6. Первое устг ройство сравнения 20 настраивается на порог, превышающий падение напряжения на интеграторе в процессе разряда с учетом температурных вариаций, т.е. порог, соответствующий началу увеличения напряжения на интеграторе в процессе разряда. Второе устройство сравнения 23 со ответственно настраивается на максимально допустимое напряжение отсечки. Второй генератор тока разряда 7 настроен на величину максимально допустимого тока для данного типа интегратора. Время разряда начинается при подаче команды Пуск в схему управления 5 При этой команде схема управления 5 подключает дискретный интегратор 13 к первому генератору тока и первому и второму устройствам сравнения 20 и 23. Одновременно схемой управления 5 и логическим ключом 9 разрешается прохождение импульсов с генератора меток времени 1 на счетчик времени разряда 3 дешифратор и индикатор 17. По мере заполнения учетчика 3 на индикаторном табло 17 индицируется время разряда дискретного интегратора 13. По окончании разряда на интегратор 13 начинает расти напряжение, которое фиксирует первое устройство сравнения и подает сигнал в схему управления 5 которая через логический ключ 9 отключает первый генератор тока разряда 6 от интегратора 13 и подключает к нему второй генератор тока разряда 7. При этом скорость нарастания напряжения на интеграторе 13 резко возрастает, и по достижению максимально допустимого напряжения отсечки срабатывает второе устройство сравнения 23, посылая сигнал в схему управления 5, которая отключает через логический ключ 9 дискретный интегратор 13 от второго генераторе тока разряда 7, а счетчик времени разряда 3 от генератора меток времени 1. Конечное значение времени разряда фиксируется на индикаторном табло 17.

По окончании каждого зарядно-разрядного цикла схема управления 5 вырабатывает импульс, который через логический ключ 10 поступает на счетчик циклов 22, дешифратор 15 и индикатор 18.

В случае выхода из строя исследуемого интегратора 13 схема защиты 21 через схему управления 5 и логические ключи 9 и 11 отключает генераторы тока заряда k и разряда 6 или 7 и останавливает счетчики заряда 2 и разряда 3 При этом индикаторное устройство 18 фиксирует количество наработанных Циклов.

Устройство работает в трех режимах: Заряд интегратора, Разряд

интегратора, Циклирование и позволяет проводить исследования и испытания электрохимических дискретных интеграторов на надежность при малых токах разряда с повышенной точностью.

Формула изобретения

Устройство для испытания дискретны интеграторов по авт. св. № 822302, |0тличающееся тем, что, с целью повышенияi точности определет ния погрешности зарядно-разрядного цикла, в него введены вторая схема сравнения, вход которой соединен с дискретным интегратором, а выход с одним из входов схемы управления, и второй генератор тока разряда, выход которого соединен с дискретным интегратором, а вход - через логический ключ с одним из выходов схемы управления.

Источники информации, принятые во внимание при экспертизе

f8

17

f5

1tf

II

fd I

2/

W

16

M

a

f

13

21

Авторы

Даты

1982-10-15—Публикация

1981-03-23—Подача