(5А) УСТРОЙСТВО ДЛЯ ИСПЫТАНИЙ ДИСКРЕТНЫХ ЭЛЕКТРОХИМИЧЕСКИХ ИНТЕГРАТОРОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения погрешности дискретных электрохимических интеграторов | 1983 |

|

SU1137543A1 |

| Устройство для испытания дискретныхиНТЕгРАТОРОВ | 1979 |

|

SU822302A1 |

| Устройство для испытания дискретных интеграторов | 1981 |

|

SU966764A2 |

| Устройство для контроля дискретных интеграторов | 1985 |

|

SU1397980A1 |

| Устройство для регистрации параметров химических источников тока | 1979 |

|

SU877658A2 |

| Устройство для регистрации парамет-POB ХиМичЕСКиХ иСТОчНиКОВ TOKA | 1978 |

|

SU817823A1 |

| Формирователь управляющих импульсов | 1981 |

|

SU1018214A1 |

| Ультразвуковой дефектоскоп | 1986 |

|

SU1385064A1 |

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1989 |

|

SU1600000A1 |

| Программируемый источник питания | 1988 |

|

SU1597875A1 |

1

Изобретение относится к информационно-измерительной технике и представляет собой автоматизированную измерительную систему; предназначенную для испытаний большой партии электрохимических интеграторов одноп временно.

Известно устройство для определения параметров и испытаний электрохимических интеграторов, включающее стабилизированный источник тока, генератор стабилизированной частоты, управляющий элемент, задатчик длительности импульса, синхронизатор, задающий мультивибратор, счетчик числа импульсов, блок отсчета и управления. Устройство является универсальным и предназначено для контроля параметров интеграторов как при зарядных, так и при разрядных .ис пытаниях tl3.;

Однако оно рассчитано на испытания одновременно нескольких интеграторов.

Наиболее близким к изобретению является устройство, содержащее . источник тока, схему сравнения, схему управления, генератор меток времени, устройство для измерения временного интервала. Для занесения в интегратор определенного количества электричества при зарядных испытаниях оператор задает необходимое , в этом, случае время заряда переключа10телем, подключающим соответствующий выход .дешифратора к схеме управления. Одновременно выбирается необходимый ток заряда стабилизированного источника.

15

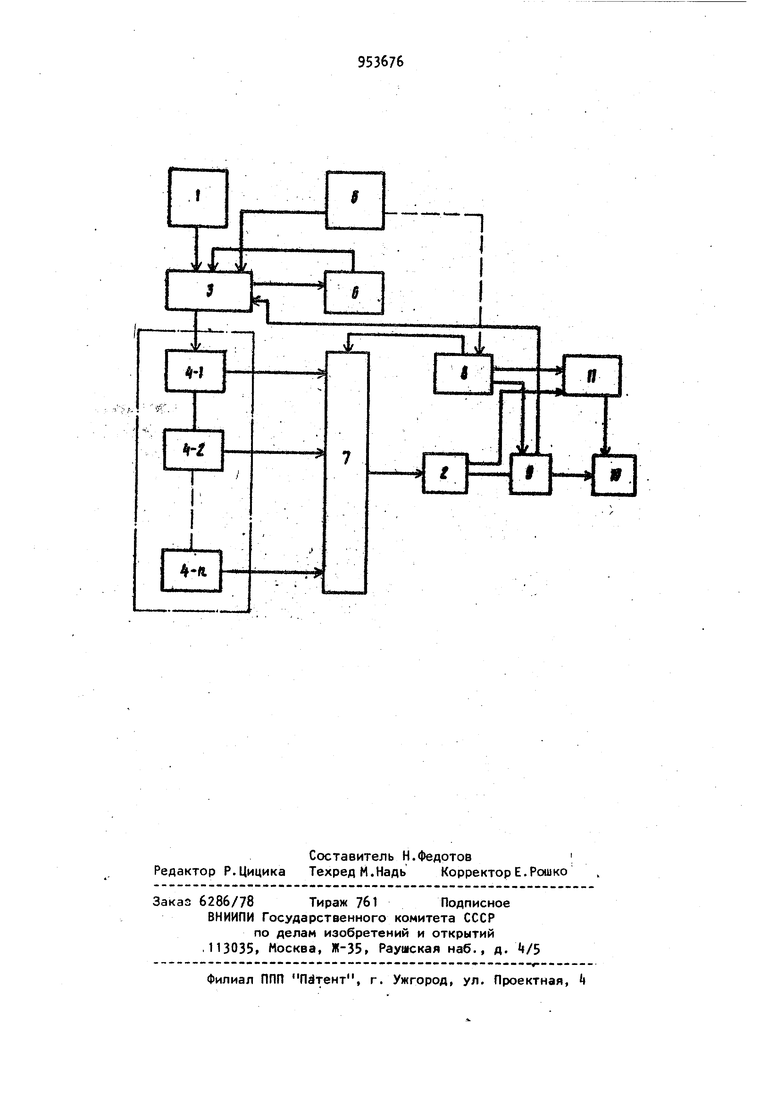

Процесс заряда начинается при подаче оператором в схему управления команды Пуск. По этой команде схв ма управления контактами реле под20ключает испытываемый интегратор к источнику тока и схеме сравнения. Одновременно с этим сигнал со схемы управления разрешает прохождение импульсов i; генератора меток времени на устройство измерения временного интервала, которое состоит из двоично-десятичного счетчика, двоично-десятичного дешифратора и цифрового десятичного табло. По мере заполнения счетчика на табло индиц 1руется время заряда. По окончании необходимого временного инте вала заряда положительный уровень с дешифратора, служащий для поджигания катодов первых цифровых инди каторных ламп, поступает на схему управления, которая отключает интегратор от зарядной цепи и прекращае прохождение импульсов счета с генератора меток времени на устройство измерения временного интервала. Одновременно с заполнением временного устройства импульсами с генератора меток времени схема сравнения осуществляет допусковый контроль напря жения на интеграторе и при превышении им определенного уровня, что свидетельствует о неисправности интегратора, формирует сигнал на схем управления, прекращающую процесс заряда 2. Однако известное устройство не рассчитано на испытание нескольких интеграторов одновременно., и мгобы повысить его производительность, пришлось бы в соответствующее число раз увеличить количество источников тока-и схем сравнения, что привело бы к резкому увеличению веса, габаритов и потребляемой мощности установки. Цель изобретения - повышение про изводительности. Указанная цель достигается тем, что в устройство, содержащее источник тока и интегратор меток времени подключенные к входу схемы управления, выход которой соединен с входо блока измерения временного интервал схему сравнения,введены коммутатор, оперативное запоминающее устройство схема совпадения, схема сигнализации и распределитель, причем выходы распределителя связаны с адресными входами оперативного запоминающего устройства, первым входом схем совпадения и входами управления ком мутатора, информационные входы кото рого подключены к испытываемым интеграторам, а выход - к входу схемы сравнения, выход которой связан с 4 входом Запись оперативного запоминающего устройства и вторым входом схемы совпадения, а выход схемы совпадения вместе с выходом оперативного запоминающего устройства подключен к схеме сигнализации. На чертеже показана структурная схема устройства. , Схема содержит источник 1 тока йнтегрированйя , схему сравнения 2 , схему управления 3, интеграторы ,генератор 5 меток времени, формирователь 6 временных интервалов, коммутатор 7, распределитель 8, оперативное запоминающее устройство {ОЗУ) 3, схему 10 сигнализации совпадения. Процесс испытаний интеграторов начинается по команде оператора и состоит в следующем. управления 3 включает интеграторы в цепь источника 1 тока интегрирования и разрешает прохождение меток времени на формирователь 6 временных интервалов. Он в свою очередь осуществляет подсчет этих меток и сравнение текущего значения временного интервала и заданного значения этого интервала. Одновременно метки времени запускают распределитель 8, на выходах которого появляется сдвинутая во времени последовательность импульсов. В соответствии с сигналами распределителя 8 коммутатор 7 начинает поочередно подключать к входу схемы сравнения заряжаемые интеграторы. Схема сравнения 2 осуществляет контроль напряжения на интеграторе по двум уровням. При достижении напряжения на каком-либо интеграторе первого контролируемого уровня сигнал со схемы сравнения 2 поступает на вход схемы # совпадения 11, которая осуществляет временное разделение этого сигнала в соответствии с сигналами распределителя 8. После этого схема совпадения 11 своими выходными сигналами включает сигнализацию о номере интегратора, напряжение на котором вышло за первый контролируемый уровень. При превышении напряжением на интеграторе второго контролируемого уровня сигнал со схемы сравнения 2 поступает на шину Запись ОЗУ 9 и записывается в ячейку, на входе которой присутствует тактовый импульс с распределителя. ОЗУ 9 в свою очередь своими выходными сигналами включает сретовую сигнализацию о выходе напряжения на этом интеграторе за второй контролируемый уровень и одновременно формирует сигнал на схему управления 3, по которому данный интегратор выводитс из зарядной цепи. Таким образом, введение в установку коммутатора, ОЗУ и схемы совпадения, управляемых распределителе позволило резко повысить производительность зарядных испытаний одной установкой и сократить число схем сравнения и высокостабильных источн ков тока при использовании известно установки. Формула изобретения . Устройство для испытаний дискрет ных электрохимических интеграторов, содержащее источник тока и генерато меток времени, подключенные к входу схемы управления,- выход которой соединен с входом блока измерения временного интервала, схему сравнения, отличающееся тем, что, с целью повышения производи66тельности, в нее введены коммутатор, оперативное запоминающее устройство, схема совпадения, схема сигнализации и распределитель, причем выходы распределителя связаны с адресный ми входами оперативного запоминающего устройства, первым входом схемы совпадений и входами управления коммутатора информационные входы которого подключены к испытываемым интеграторам, а выход - к входу схемы сравнения, выход которой связан d входом Запись оперативного запоминающего устройства и вторым входом хемы совпадения,а выход схемы совадения вместе с выходом оперативного запоминающего устройства подклюен к схеме сигнализации. Источники информации, , принятые,во внимание при экспертизе 1. Приборы и системы управления. Машиностроение, 1968 , № 11, с.55., 2. Авторское свидетельство ССрР , кл. Н 01 G 9/22, 197Ь (прототип).

Авторы

Даты

1982-08-23—Публикация

1980-07-09—Подача