Изобретение относится к измерительной технике и может быть использовано для измерения параметров емкостей, индуктив- ностей и сопротивлений.

Изобретение наиболее эффективно может быть использовано для входного контроля элементов, лабораторного измерения LCR-элементов и внутрисхемного контроля функциональных печатных плат.

Известен измеоитель интегрирующего типа 4262А фирмы Hewlett-Packard (США), который содержит генератор синусоидального напряжения, объект измерения, преобразователь ток - напряжение, выполненный на операционном усилителе, четыре ключа, фазовращатель, синхронный детектор, интегратор, компаратор, схему логического совпадения, генератор счетных импульсов и счетчик.

Один вывод объекта измерения соединен с выходом генератора синусоидального напряжения и сигнальными входами двух ключей, выходы которых соединены с входами синхронного детектора и фазовращателя соответственно, другой вывод объекта измерения соединен с токовым и потенциальными входами преобразователя ток - напряжение, выход которого соединен с сигнальными входами двух ключей, выходы которых соединены с входами синхронного детектора и фазовращателя соответственно, выход фазовращателя соединен с управляющим входом синхронного детектора, выход которого соединен с управляющим входом интегратора, выход которого соединен с входом компаратора, выход которого соединен с одним из входов схемы логического совпадения, другой вход которой соединен с выходом генератора счетных импульсов, выход схемы логического совпадения соединен с входом счетчика.

Недостатки данного измерителя заключаются в наличии погрешности за счет смещений синхронного детектора и интегратора, дрейфа фазы фазовращателя, сложности получения точного и стабильного сдвига напряжения на угол, кратный п II.

Наиболее близкими к предлагаемому изобретению являются измерители 4274А, 4275А фирмы Hewlett-Packard (США), основанные на интегрирующем методе измерения с относительным опорным напряжением с применением микропроцессора, каждый из которых содержит генератор синусоидального напряжения, делитель частоты, фазовращатель, выполненный на схеме поглощения импульсов и делителя частоты, измеряемое сопротивление, преобразователь ток - напряжение, выполненный на операционном усилителе, два ключа.

синхронный детектор, источник разрядного напряжения, интегратор, компаратор, элемент совпадения, генератор счетных импульсов и счетчик.

Выход генератора синусоидального напряжения соединен с входом делителя частоты и входом схемы поглощения импульсов, выход делителя частоты соединен с первым выводом измеряемого сопротивления и первым входом первого ключа, выход которого соединен с первым входом синхронного детектора, второй вывод объекта измерения соединен с первым входом

преобразователя ток - напряжение, выход которого соединен с первым входом второго ключа, выход которого соединен с первым входом синхронного детектора, выход схемы поглощения импульсов соединен с входом делителя частоты, выход которого соединен с вторым входом синхронного детектора, выход синхронного детектора и выход источника разрядного напряжения через соответствующие резисторы соединены с входом интегратора, выход которого соединен с входом компаратора, выход которого соединен с первым входом элемента совпадения, второй вход которого соединен с выходом генератора счетных импульсов.

выход элемента совпадения соединен с входом счетчика.

Данные измерители позволяют исключить погрешность, вызванную смещением нуля интегратора и дрейфа фазы фазовращзтеля. Сдвиг фазы опорного напряжения на угол, кратный п/2, осуществляется цифровым фазовым фазовращателем, состоящим из схемы поглощения импульсов и делителя частоты на четыре. Такой фазовращатель дает достаточно точный сдвиг напряжения на л /2. Однако измерение проводится в пять тактов, что существенно снижает быстродействие измерителей. Целью изобретения является повышение быстродействия при измерении параметров емкостей, индуктивностей и сопротивлений.

Использование предлагаемого измерителя существенно уменьшает время измерения, а также позволяет практически полностью избавиться от влияния напряжений смещения на результат измерения. В отличие от прототипа измерение параметров комплексного сопротивления в предлагаемом устройстве проводится не измерением составляющих векторов UT и UH в декартовой системе координат, а измерением их модулей с одновременным измерением сдвига фаз между векторами UT и Ун в полярных координатах.

Поставленная цель достигается тем, что в измеритель, параметров комплексных сопротивлений, содержащий генератор сину- соидального напряжения, преобразователь ток - напряжение, первый вход которого соединен с первым выводом измеряемого сопротивления, элемент совпадения, первый вход которого соединен с выходом ге- нератора счетных импульсов, а выход - с первым входом счетчика, и компаратор, введены блок управления, дешифратор команд, дифференциальный усилитель, блок коммутации каналов, интегрирующий детектор, аналого-цифровой преобразователь, цифровой фазовый детектор и второй компаратор, причем второй вывод измеряемого сопротивления соединен с выходом генератора синусоидального напряжения и пер- вым входом дифференциального усилителя, второй вход которого соединен с первым входом преобразователя ток - напряжение, а выход - с первым входом блока коммутации каналов, выход которого соединен с первым входом интегрирующего детектора, первый и второй выходы которого соединены с первым и вторым входами аналого- цифровогопреобразователя соответственно, выходы первого и второго компараторов подключены соответственно к первому и второму входам цифрового фазового детектора, выход которого соединен с вторым входом элемента совпадения, выход счетчика соединен с выходом аналоге- цифрового преобразователя и входом блока управления, выход которого соединен &вхо- дом дешифратора команд, выход которого соединен с вторыми входами преобразователя ток - напряжение, интегрирующего де- тектора и счетчика и третьими входами цифрового фазового детектора, блока коммутации каналов и аналого-цифрового преобразователя, вторые входы первого и второго компараторов соединены с общей шиной измерителя.

Измерение параметров комплексного сопротивления посредством известного устройства осуществляется в пять тактов, каждый из которых состоит из трех идентичных этапов измерения.

Первый такт измерения сводится к измерению и запоминанию напряжения смещения на выходе интегратора при отключенном генераторе синусоидального напряжения,

На первом этапе первого такта происходит интегрирующее детектирование по полупериоду рабочей частоты- посредством синхронного детектора, в результате чего на

выходе синхронного детектора выделяется напряжение смещения UcM1(t);

uUt)dt-ruCM2+j; dt,(i)

где UCM(- напряжение смещения на входе синхронного детектора;

UCMЈ- напряжение смещения на выходе синхронного детектора в процессе детектирования;

TD - постоянная времени синхронного детектора,

ц - момент времени окончания детектирования и начало заряда интегратора: ti .

Тр - период рабочей частоты, на которой происходит измерение.

В момент времени т на выходе детектора выделяется напряжение UCM (ti).

На втором этапе первого такта происходит процесс заряда интегратора, в результате чего на2 его выходе выделяется напряжение UCM (t):

)M(ti) +

+ Цмз+Л,,

(2)

12 Ти

где UCM напряжение смещения на выходе интегратора;в

напряжение смещения выхода синхронного детектора после его сброса (момент t2)5

12 - момент времени окончания заряда интегратора и начала его разряда;

T2 t2-ti - время заряда интегратора;

Ти - постоянная времени интегратора.

В момент времени t2 на выходе интегратора выделяется напряжение UCM fe):

2 ч , , f 1 T2 j ,, Г2

+ U

СМ2ТЙ

+

UЈM(t2) UCMl

+ Цм1ГГ Тг; + (3)

На третьем этапе первого такта происходит процесс разряда.интегратора посредством подключения к его входу источника разрядного напряжения (условимся: постоянная времени цепи разряда интегратора равна постоянной времени цепи заряда Ти). В результате процесса разряда на выходе интегратора выделится напряжение

U-U

if I)

,, UP f „ . UcM4.

CM

M-ffdt Ml «

Ј|

JcM«2T

tu

UcMa.4

4U

CM ,

(4)

где Up - величина напряжения источника разрядного напряжения

t3 момент времени перехода выходно-В конце третьего этапа измерения в мого напряжения интегратора через нулевоемент времени t3 на выходе интегратора вызначение (конец измерения напряженияделяется напряжение UsfeH): смещения): 13-12 A rx.t xp,) 2UTЈ2

В момент времени ta на выходе интегра- 5(J5( + UCM co5cp1 - тopa выделяется напряжение UCM ( u °u WTDTU/

U)-Up- - Ue«4- UCMl jr-+ / T 11

ГЪ Ьч1 где гхр1-реальное время, зафиксированное

+ UCM 2.7 т Tu f CfA ,известным устройством без компенсации

u Dwпаразитных смещений.

Из уравнения (6) можно найти времяИз уравнения (11)

Дгх, которое зафиксирует счетчик и кото-0,, лпл„ л л

«с л IC.UT-ипuCMi С/, Се

рое будет вычитаться из результата измере- 5Ј .C05q +L. ,,, ,/ t

ния составляющих как величина, ( Up-(JCM TOCO Up-UCW( TD

пропорциональная величине смещения: 2 UCAAUUcw T

. UCMI ,2. cwi 2+UcM, сй+ГГТй

хМ-Пт +ГШ- T+№nn Up Uwt Up (/CM (11)

Up-UcM4 TD UrUCM4 2Q Вычитаяиз(11)уравнение(6)1ПОлу им;

UCM д Ц см г j-окончательную величину rxpi, которая ис+Up-UCM4 °2 U p - U см v U (б)пользуется в дальнейших расчетах:

В следующие4 такта измерения извест-rxpi тхр - Агх д у у-Т а; 008 1 ное устройство измеряет две синфазные со- 25р см4 °

ставляющие Re UT; Re UH и

квадратурные составляющие Ц-ит; fm-UH.. Определим погрешность измерения

Рассмотрим на примере измерения Re-UTX1

насколько полно компенсируется напряже-§r TXUI txpi UcM4 ,

ние смещения известного устройства. Иде- 30х1гхщUp - UCM4

альное измеренное время тхи1.На точность измерения гхр в известном

пропорциональное величине Re Ur (при ус-устройстве влияет величина смещения синловии отсутствия напряжения смещения)хронного детектора (UCM/I)равно:В табл. 1 приведены погрешности изме 21)т. 2 .-пс...,/7 рения известным устройством при

--Ор-ТБЙ005 1 С7)исм4 +10-2ВпРииР 1:10В.

где (о- круговая частота сигнала, посредст-Однако в результате преобразований, вывом которого проводится измерение;полненных по формулам (39) и (40) (измере р -угол сдвига фаз между напряжени-НИе параметров цепей с сосредоточенным

ем UT и опорным напряжением Uon-постоянными, с. 29) эта погрешность сущеИспользуя те же математические опера-ственноуменьшается, и практически не влиции, что и в первом такте измерения, най-яет на точность измерения параметров

дем реально измеренную известнымкомплексных сопротивлений, устройством величину гхр1. 45 Время всего цикла измерения «)опреВ конце первого этапа измерения в мо-деляется по формуле мент времени ti на выходе синхронного ..,Ал.1.

тектора выделяется постоянноегц-5(Г1 4-г2) + дтх+гхр1 чнап ряжение U i(ti):+ гхр2 + гхр3 + Гхр4,(14)

Ui(ti)J5Y-cos i +иСмГ - + иСМ2.(8) 50где rxpi - время разряда интегратора во

оDDвтором такте измерения (ReUr);

В конце второго этапа измерения в мо-F с«т/,

мент времени г на выходе интегратора вы-Г Р2 время разряда интегратора в

деляется напряжение U2(t2):третьем такте измерения (ImUT):

fj. У-У гЪ{$г-55гхрз время разряда интегратора в

й. QT т cosc i4 С(Л TDTU четвертом такте измерения (ReUH);

д ТХР4 время разряда интегратора в пя4l1cwftY:-|-lJCM1-2:pr+UcM5 (9)том такте измерения (lmUH).

Время разряда интегратора обычно находится в пределах Агх - 10 тг, причем, как

правило, если rxpi гхрз Дгх, то

Тхр2 7хр4 (Г2 - 10 Г2) при измерении высокодобротных емкостей или индуктивностей или, если гхр1 тхрз (Т2 - Юга), то

( А

ГХР2 1хр4 , при измерении сопротивлений, на основании чего можно определить максимальное и минимальное время измерения известного устройства:

Тцмакс 5n + 15T2 +3 Агх;(15)

Тцмин 5 П + 7 Г2 + 3 АТХ.(16)

В вышеприведенном анализе учитывается только чистое время измерения без учета времени переходных процессов и времени ожидания синхронного детектирования, максимальная величина которого равна периоду рабочей частоты.

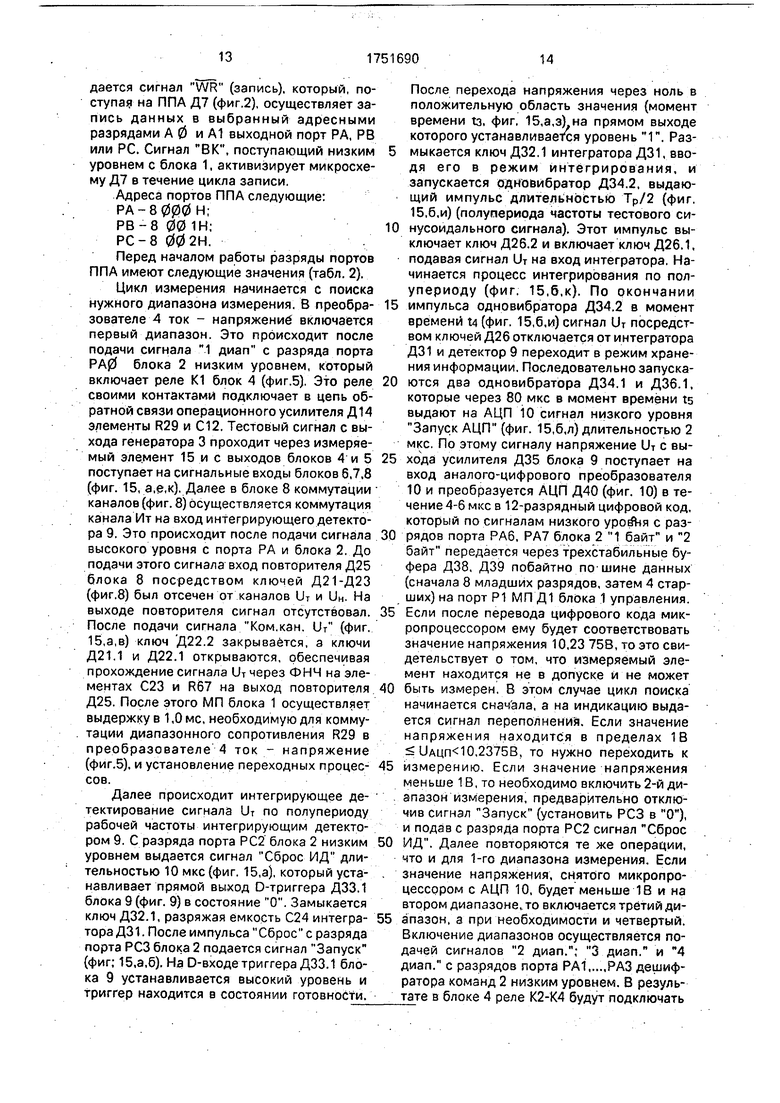

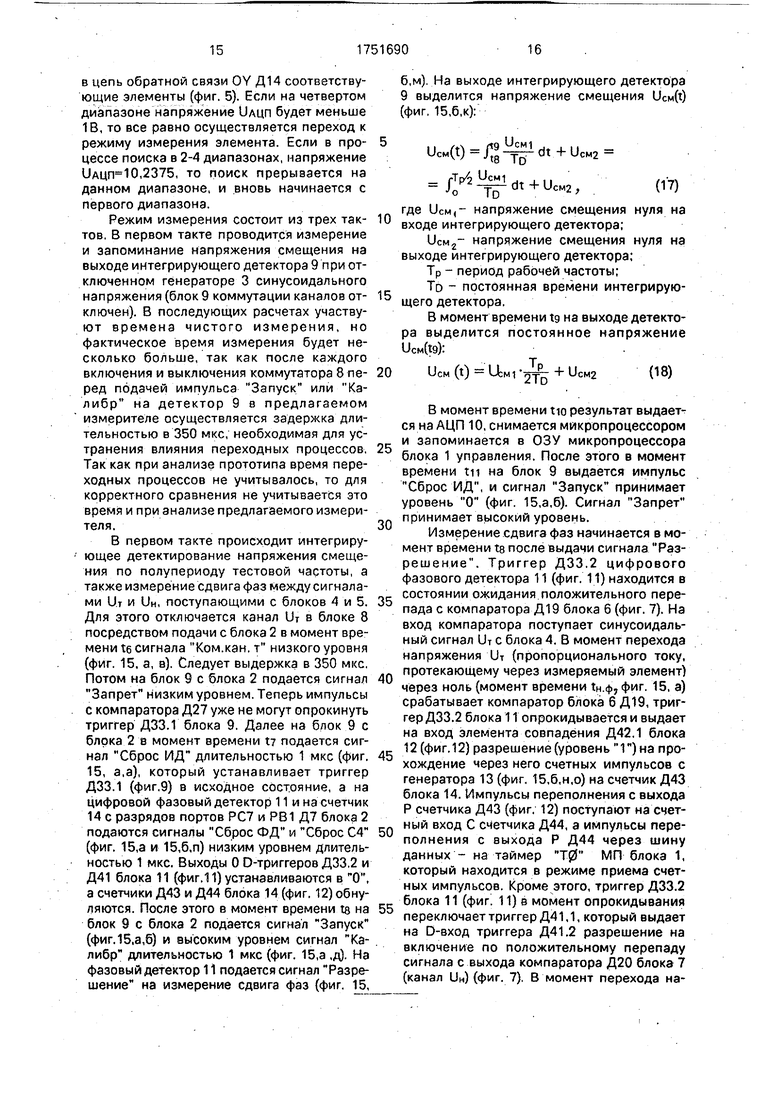

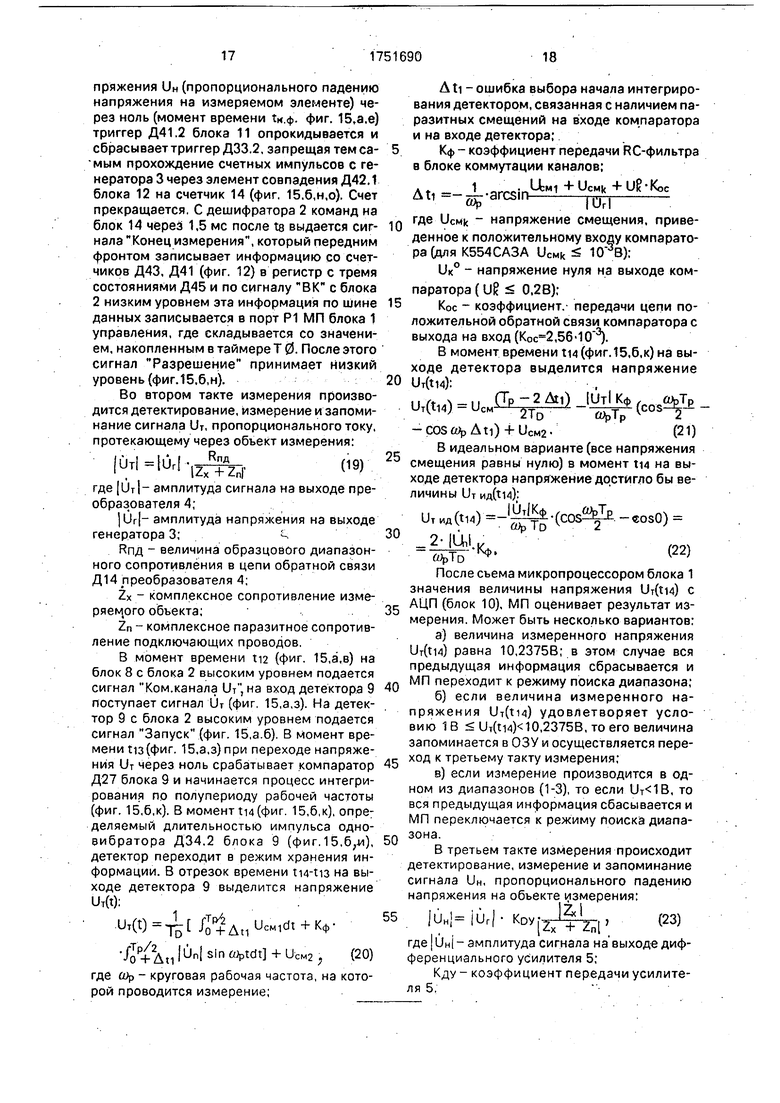

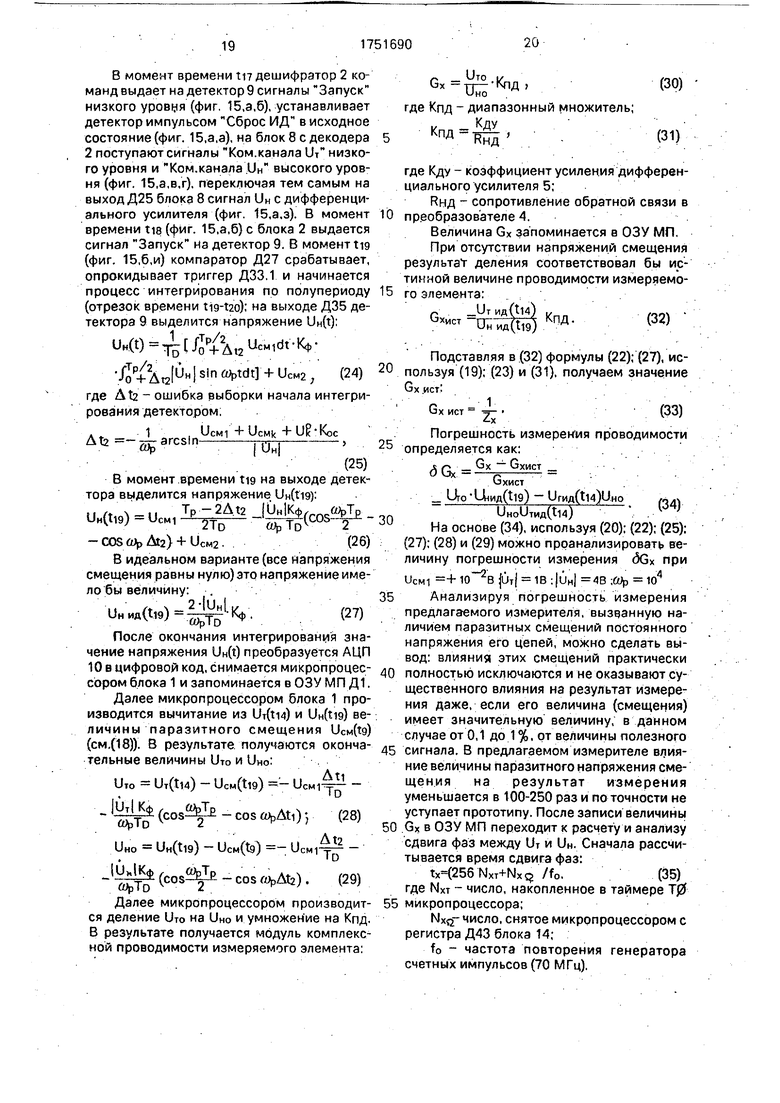

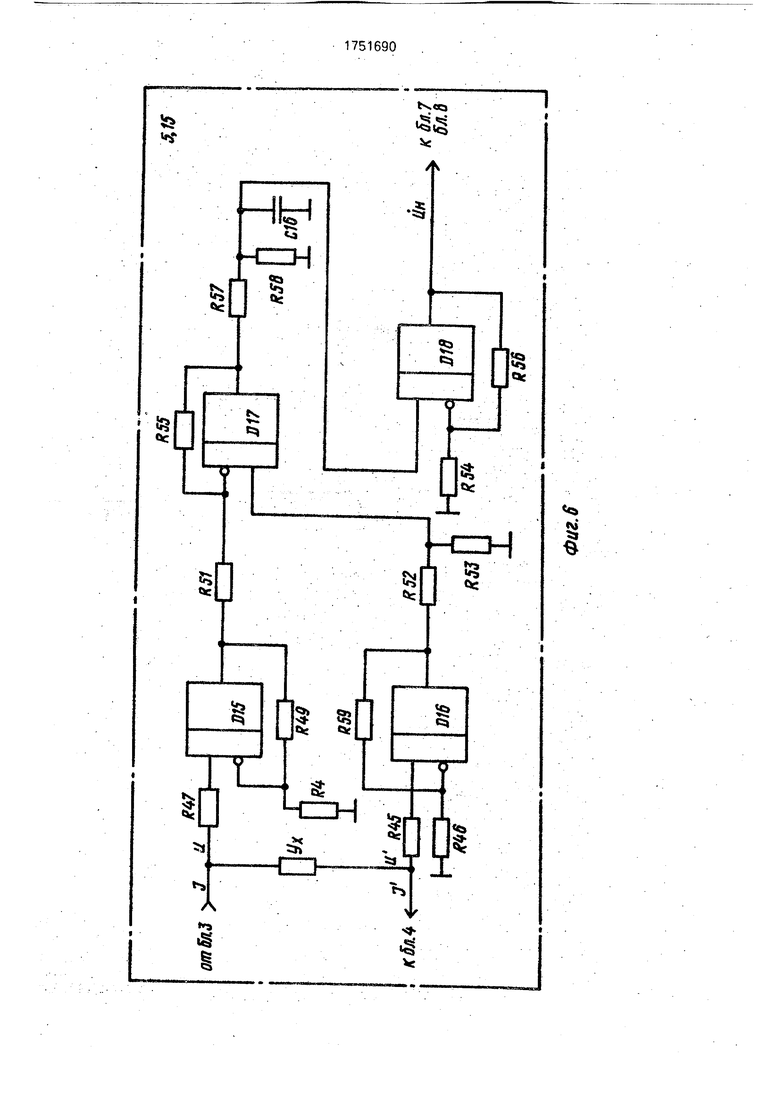

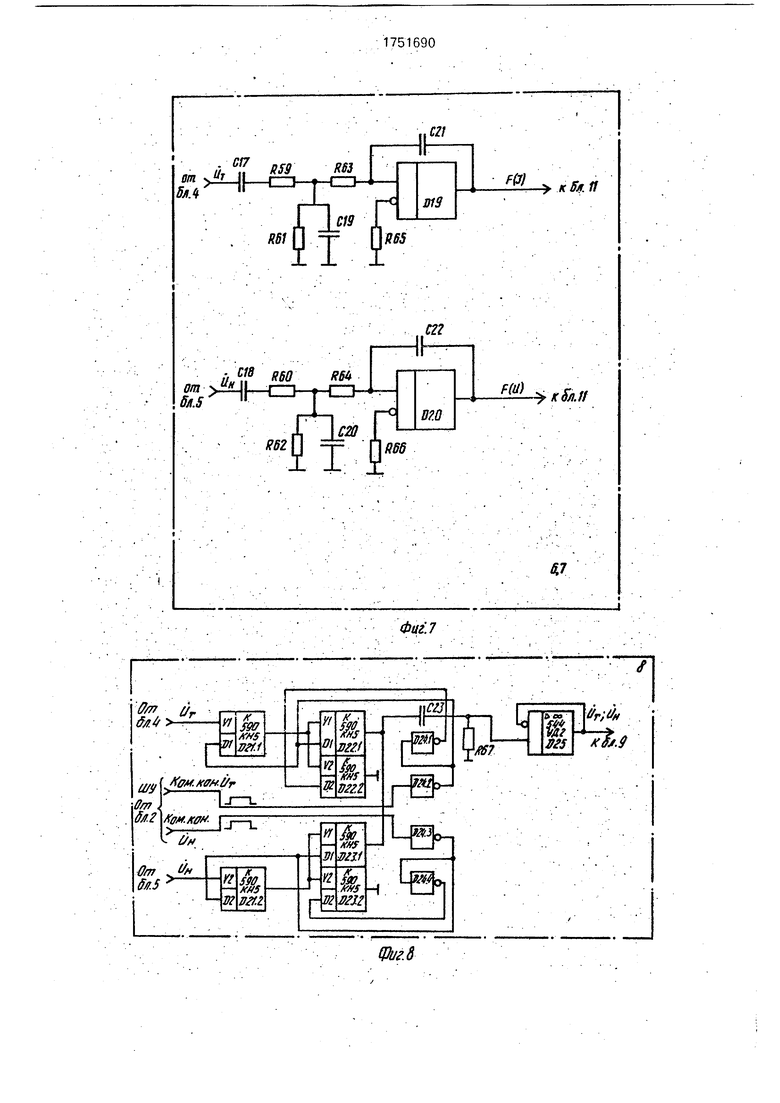

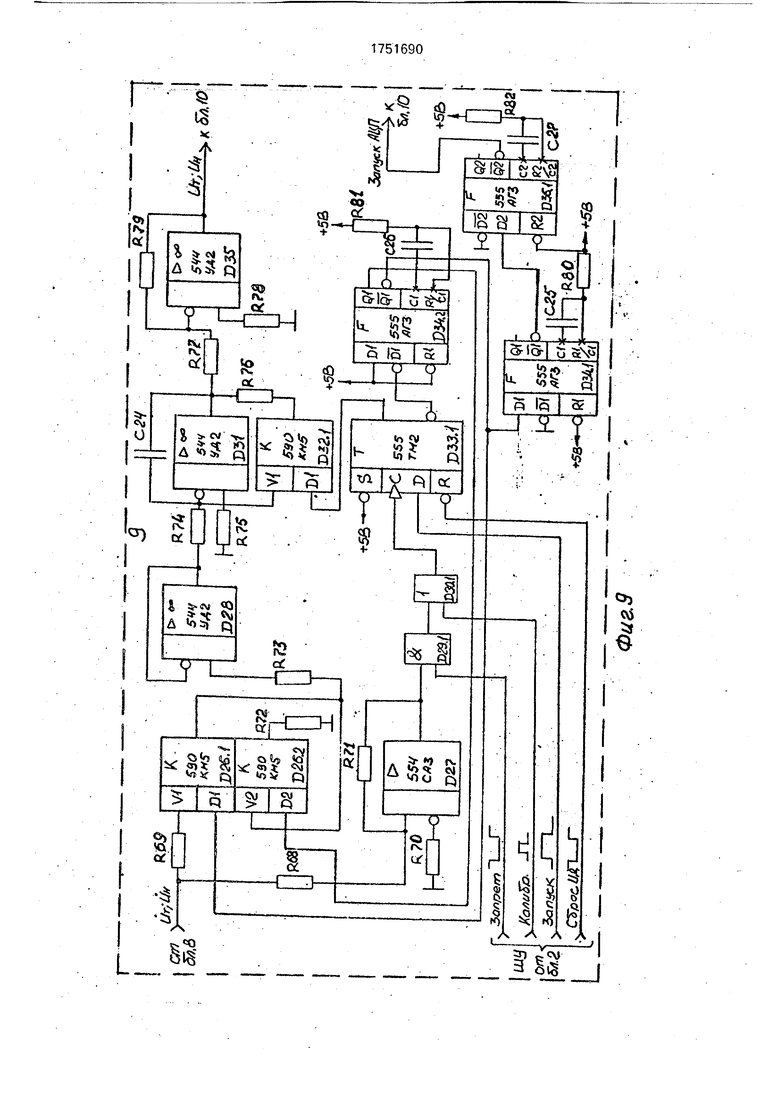

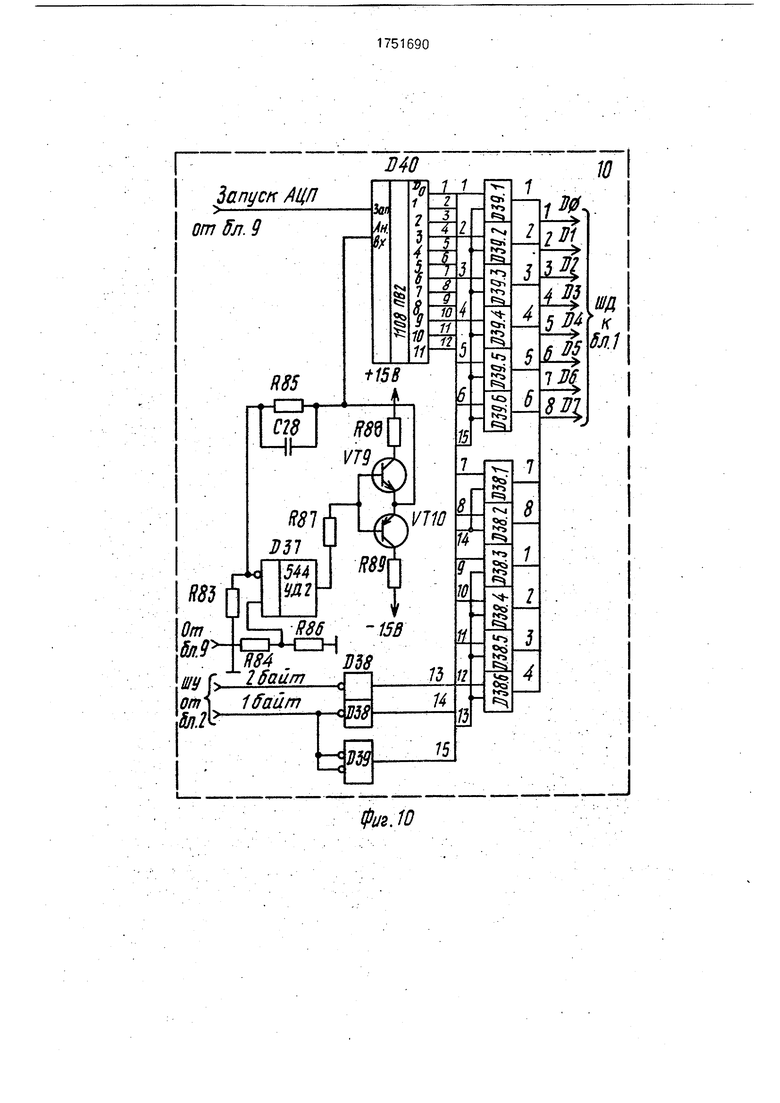

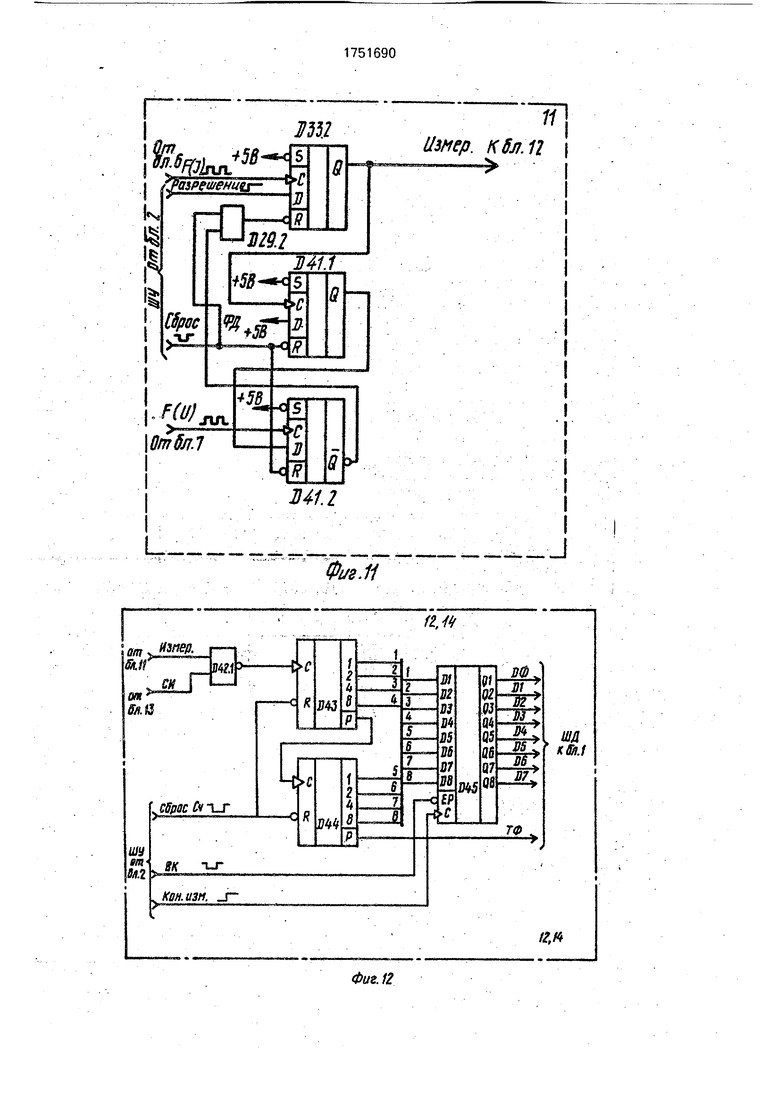

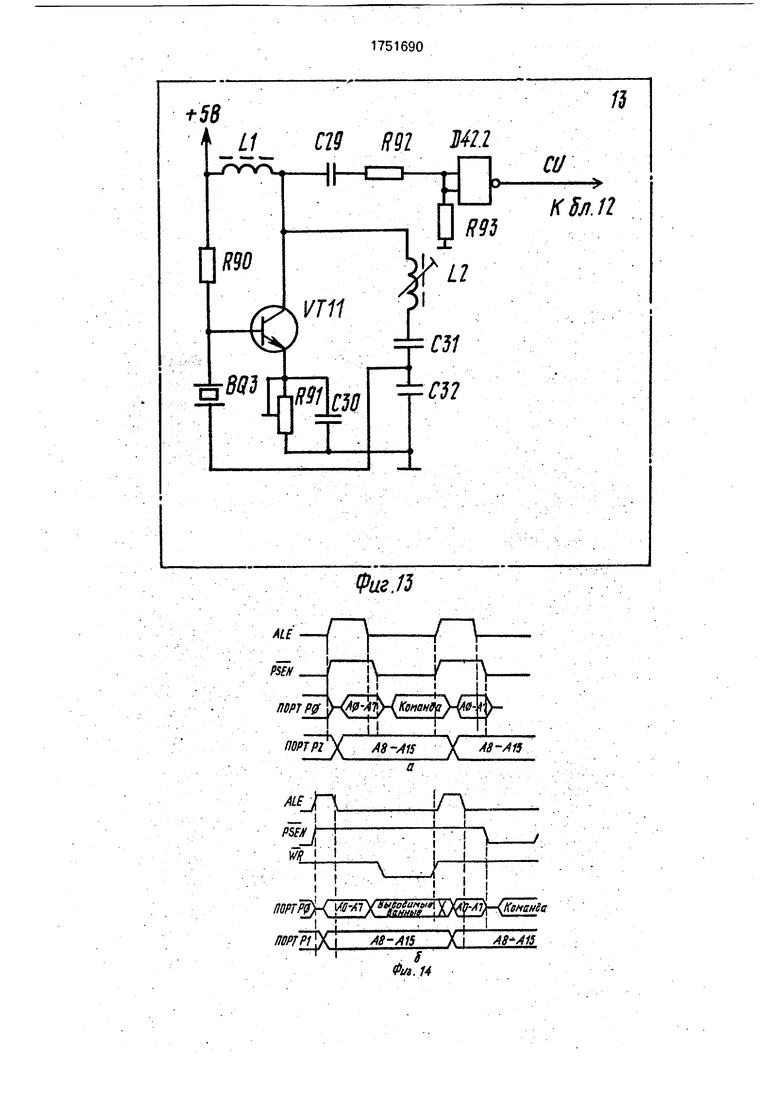

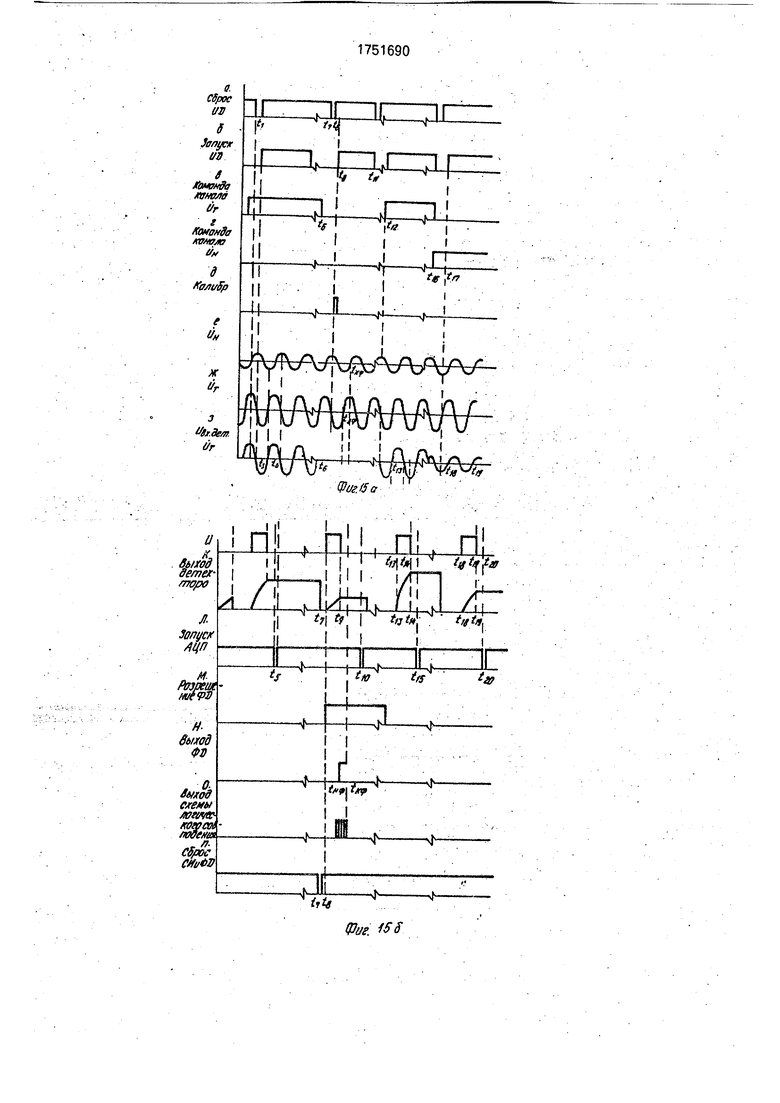

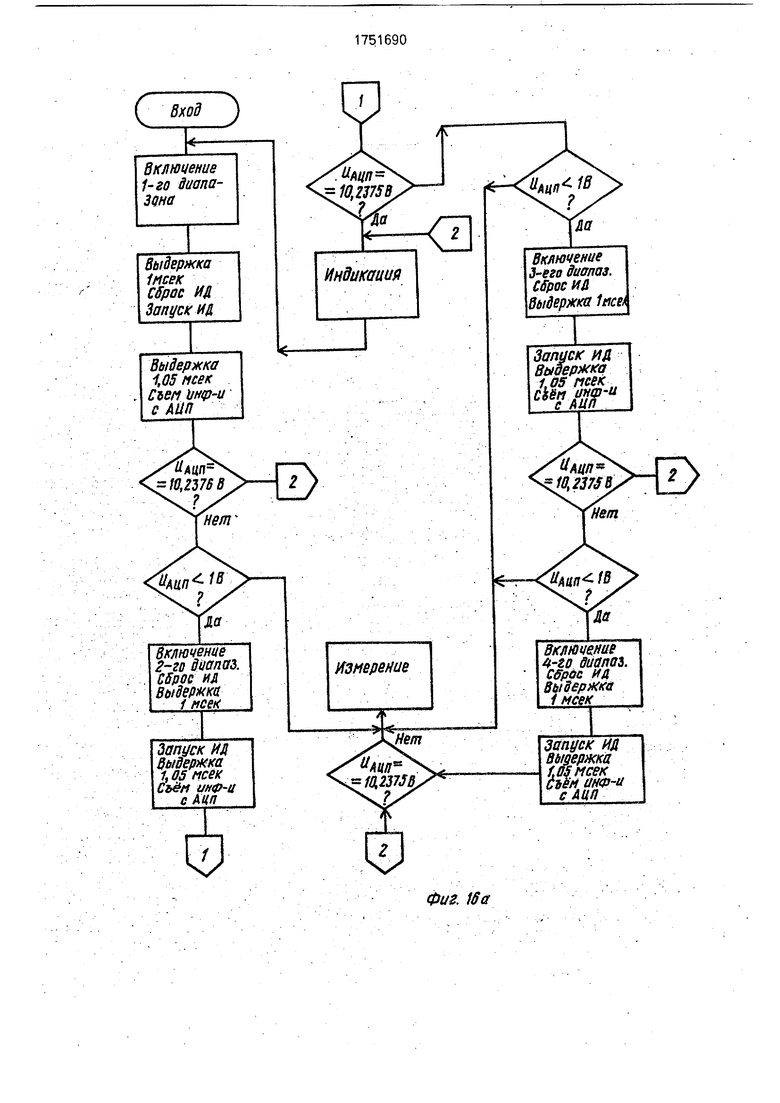

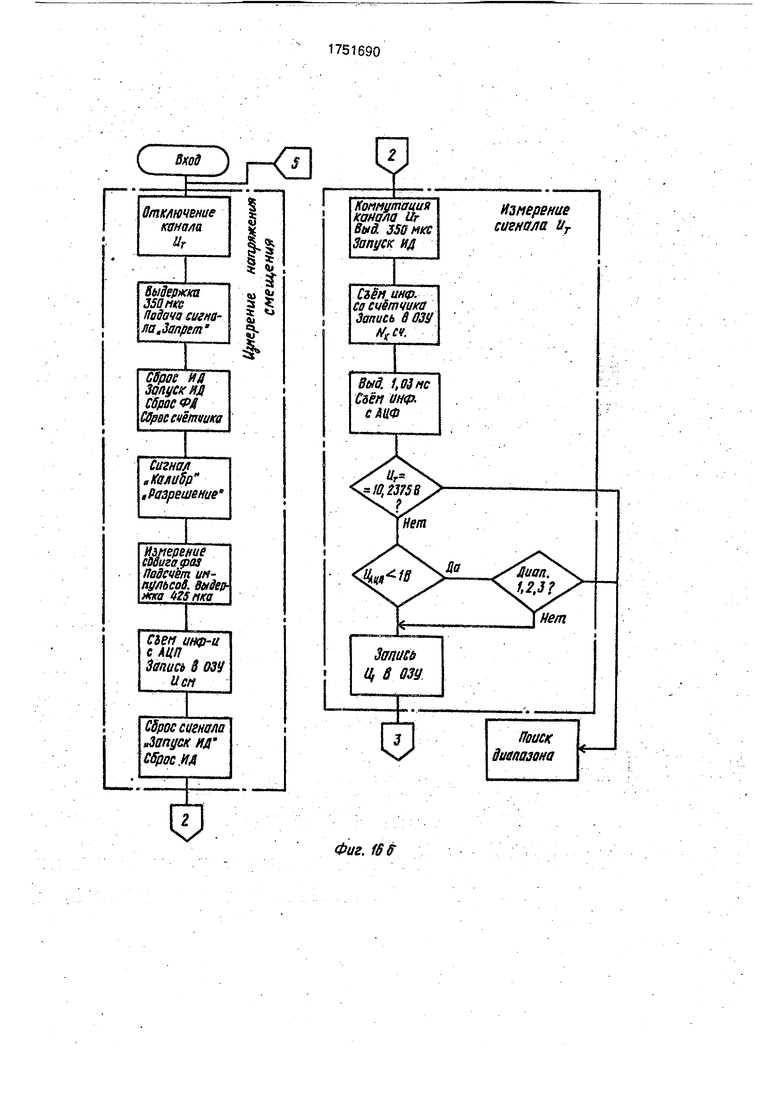

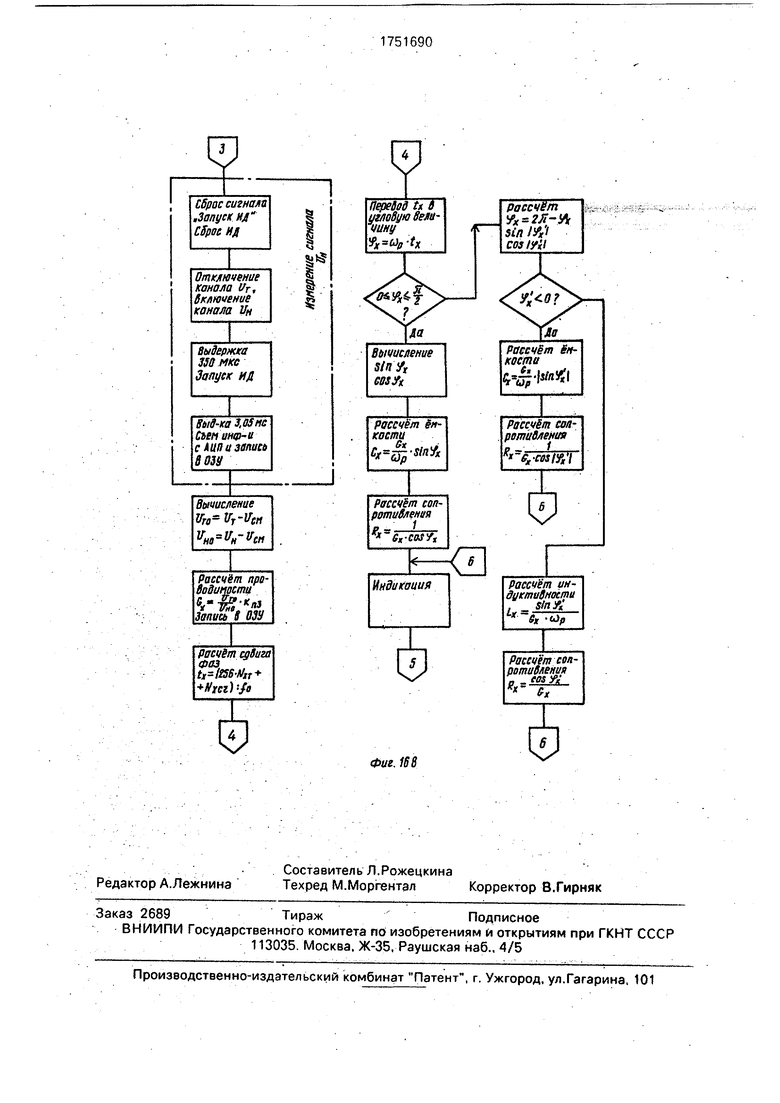

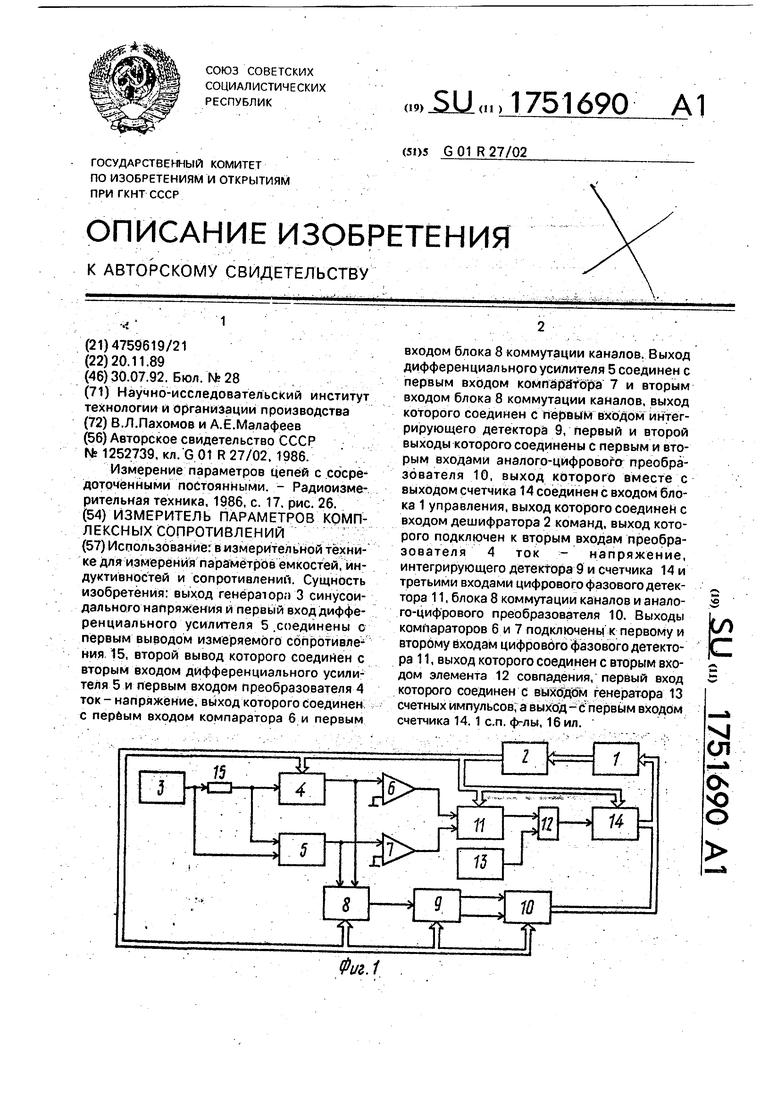

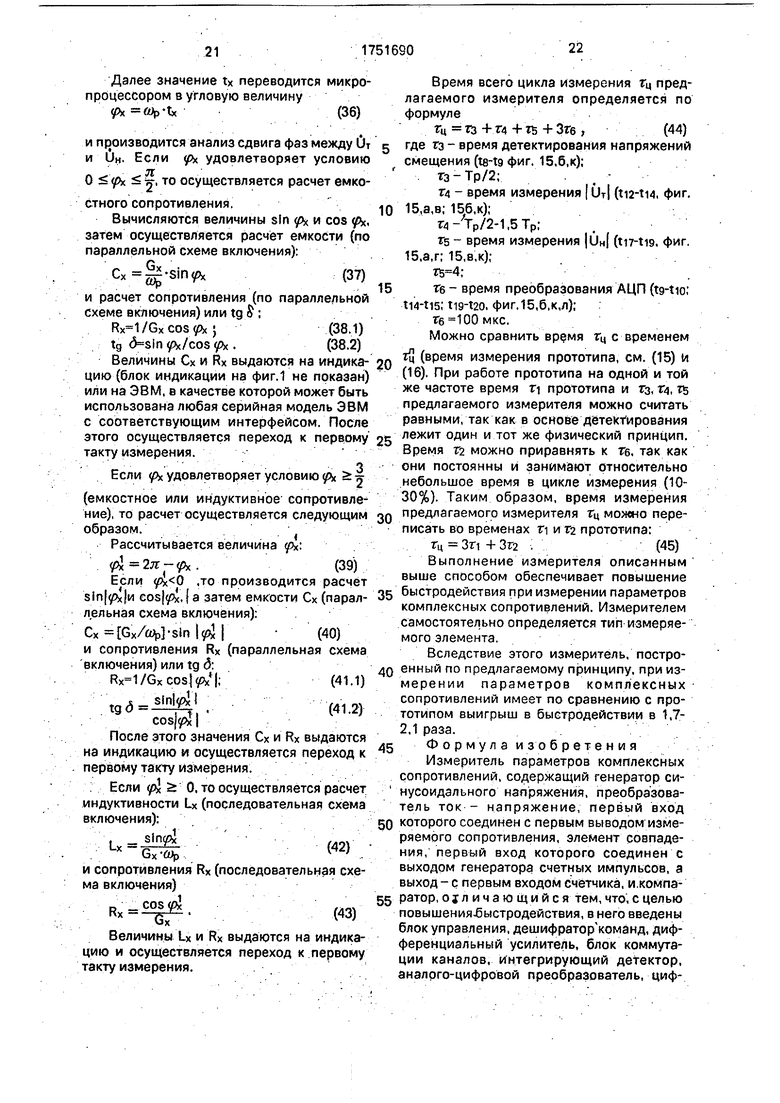

На фиг. 1 изображена структурная схема измерителя параметров комплексных сопротивлений; на фиг. 2 - принципиальная схема блока управления; на фиг. 3 - принципиальная схема дешифратора команд; на фиг.4 - принципиальная схема генератора синусоидального сигнала; на фиг. 5 - принципиальная схема преобразователя ток - напряжение; на фиг. 6 - принципиальная схема дифференциального усилителя; на фиг. 7 - принципиальная схема компараторов; на фиг. 8 - принципиальная схема блока коммутации каналов; на фиг. 9 - принципиальная схема интегрирующего детектора; на фиг. 10 - принципиальная схема аналого-цифрового преобразователя; на фиг. 11 - принципиальная схема цифрового фазового детектора; на фиг. 12 - принципиальная схема элемента совпадения и счетчика; на фиг. 13 - принципиальная схема генератора счетных импульсов; на фиг. 14 - циклограмма работы микропроцессора; на фиг. 15а, б - временная диаграмма работы предлагаемого измерителя; на фиг. 16а, в - алгоритм работы предлагаемого устройства.

Измеритель параметров комплексных сопротивлений (фиг. 1) выполнен из блока 1 управления, дешифратора 2 команд, генератора 3 синусоидального напряжения, пре- образователя ток - напряжение 4, дифференциального усилителя 5, компараторов 6 и 7, блока 8 коммутации каналов, интегрирующего детектора 9, аналого-цифрового преобразователя 10, цифрового фазового детектора 11, элемента 12 совпадения, генератора 13 счетных импульсов, счетчика 14 и измеряемого сопротивления 15.

Выход генератора синусоидального напряжения 3 и первый вход дифференциального усилителя 5 соединены с первым выводом измеряемого сопротивления 15,

второй вывод которого соединен с вторым входом дифференциального усилителя 5 и первым входом преобразователя ток - напряжение 4, выход которого соединен с первым входом компаратора 6 и первым входом

0 блока 8 коммутации каналов. Выход дифференциального усилителя 5 соединен с первым входом компаратора 7 и вторым входом блока 8 коммутации каналов, выход которого соединен с первым входом интегрирую5 щего детектора 9. Его первый и второй выходы соединены с первым и вторым входами аналого-цифрового преобразователя 10 соответственно, выход которого вместе с выходом счетчика 14 соединен с входом бло0 ка 1 управления, выход которого соединен с входом дешифратора 2 команд. Выход дешифратора 2 команд подключен к вторым входам преобразователя ток - напряжение 4, интегрирующего детектора 9 и счетчика

5 14 и третьими входами цифрового фазового детектора 11, блока 8 коммутации каналов и аналого-цифрового преобразователя 10. Выходы компараторов 6 и 7 подключены к первому и второму входам цифрового фазо0 вого детектора 11 соответственно, выход которого соединен с вторым входом элемента 12 совпадения, первый вход которого соединен с выходом генератора 13 счетных импульсов, а выход - с первым входом

5 счетчика 14.

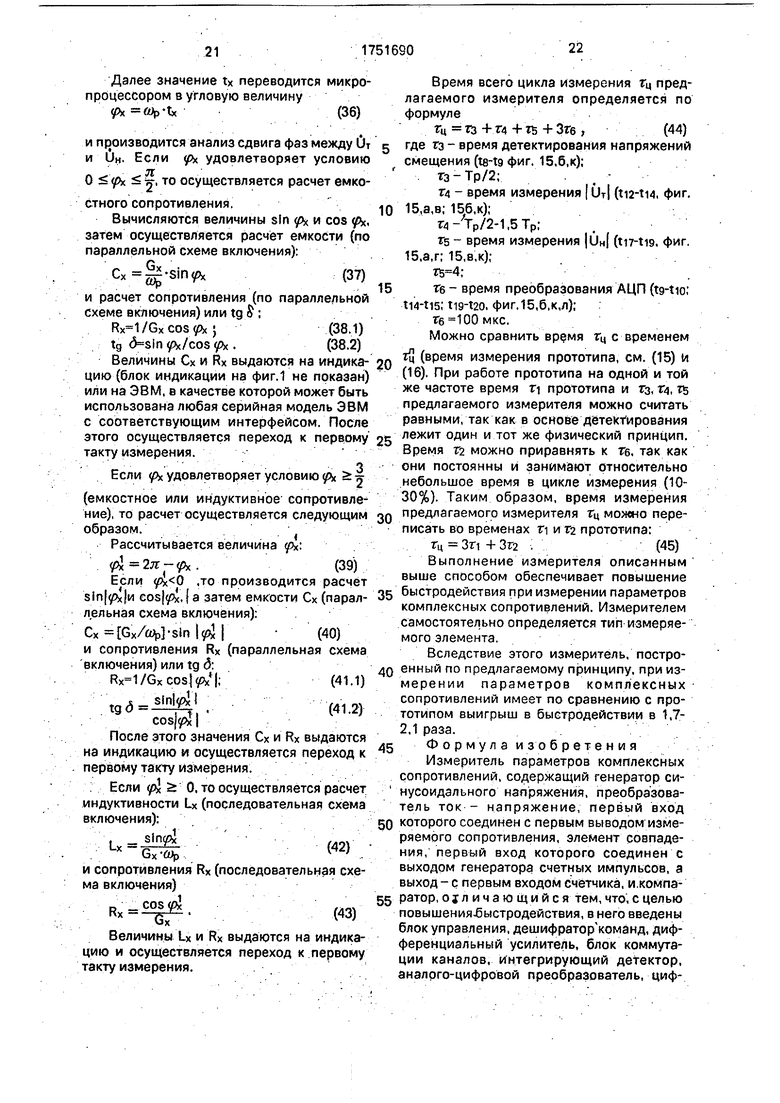

Блок 1 управления (фиг.2) выполнен на микропроцессоре серии К1816ВЕ31 и предназначен для приема информации по шине данных, выполнения математических опе0 раций и выдачи адресных сигналов на дешифратор 2 команд. Он состоит из микропроцессора Д1, элементов начальной установки МП R1 и СЗ, формирователя тактовой частоты на конденсаторах С1 и С2 и

5 резонаторе В01, адресных регистров Д2 и Д4, шинного формирователя ДЗ, постоянного запоминающего устройства Д6 и элемента Д5.1.

Дешифратор 2 команд (фиг.З) служит

0 для распределения сигналов с блока 1 управления по шине управления и выдачи их на управляющие входы соответствующих блоков. Он состоит из параллельно-программируемого адаптера Д7 и элементов

5 начальной установки R2 и С4.

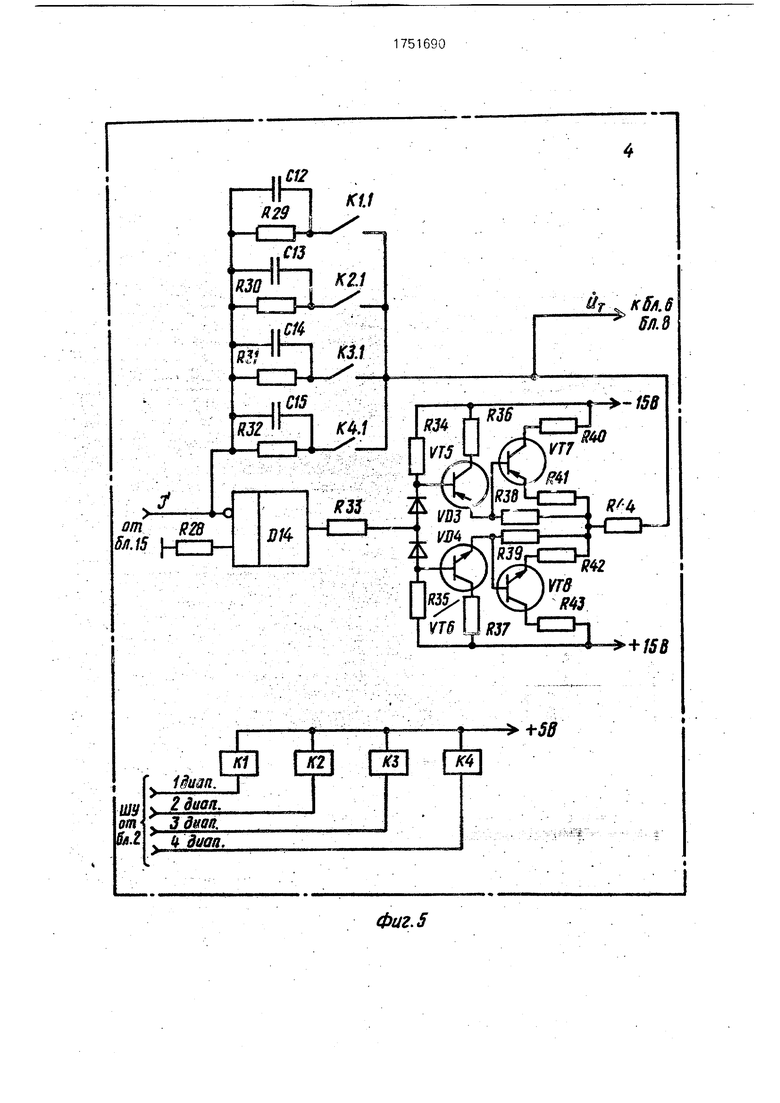

Генератор 3 синусоидального напряжения (фиг.4) предназначен для задания тестового синусоидального сигнала и содержит генератор прямоугольной последовательности импульсов, выполненный на элеменах Д8.1-Д8.3, резисторах R3-R5, конденсаторах С5-С7, частота которого задается кварцевым резонатором BQ2 (fK.p.159 кГц счетчик-делитель частоты на 100, выполненный на микросхемах Д9, Д10, полосовой фильтр, настроенный на частоту 1,59 кГц, который содержит элементы R6-R13, С8-С11 и микросхемы Д11, Д12, умощнитель на элементах Д13, R14-R27,Vfl1,Vfl2,VT1,...,Vr4.

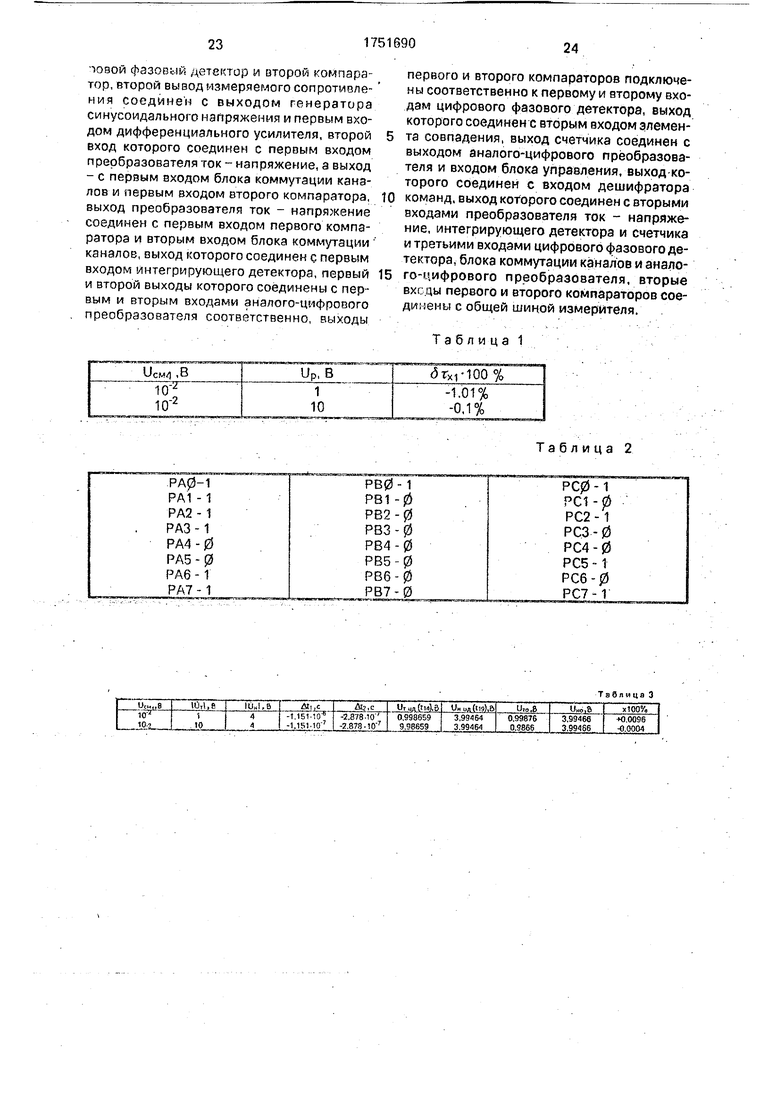

Преобразователь 4 ток - напряжение (фиг.5) предназначен для преобразования тока, протекающего через измеряемый элемент, в пропорциональное ему напряжение и содержит собственно преобразователь, выполненный на микросхеме Д14, элемен- TaxR28-R32,C12-C15, реле К1-К4, и умощнитель, содержащий транзисторы VT5,./., VT8, диоды УДЗ, УД4 и резисторы R33-R44.

Дифференциальный усилитель 5 (фиг.6) предназначен для выделения сигнала, про- порционального падению напряжения на измеряемом сопротивлении Ух 15 (фиг. 6) и содержит микросхемы Д15Д18, резисторы R45R58 и конденсатор С16,

Компараторы 6 и 7 (фиг.7) идентичны и предназначены для преобразования синусоидального сигнала в меандр, и состоят из микросхем Д19, Д20 и элементов R59-R66. С17-С22.

Блок 8 коммутации каналов (фиг.8) пред- назначен для переключения сигналов с диф- ференциального усилителя 5 и преобразователя 4 на интегрирующий детектор 9 и содержит микросхемы Д21Д25

и элементы R67 и С23.

Интегрирующий детектор 9 (фиг.9) предназначен для преобразования синусоидального напряжения в пропорциональное ему постоянное, выдачи этой величины на аналого-цифровой преобразователь 10 и запуска этого преобразователя. Детектор

состоит из микросхем Д26Д28, Д29.1,

Д30.1, Д31, Д32. Д33.1, Д34, Д35, Д36.1 и элементов R68-R82, С24-С27.

Аналого-цифровой преобразователь 10 (фиг. 10) предназначен для преобразования аналогового сигнала в цифровой код и состоит из входного усилителя и умощнителя на микросхеме Д37, транзисторах VT9,

VT10, элементах R83R89 и С28; собствен-

но АЦП Д40 и схемы с тремя логическими состояниями Д38, Д39 для вывода цифрового кода на блок 1 управления.

Цифровой фазовый детектор 11 (фиг. 11) предназначен для выделения импульса, длительность которого равна сдвигу фаз между сигналами, поступающими с компараторов 6 и 7. Он состоит из микросхем Д29.2,Д33.2иД41.

Элемент 12 совпадения (фиг. 12) предназначен для выдачи на счетчик 14 определенного количества счетных импульсов, соответствующих сдвигу фаз, выделенному детектором 11. Она состоит из элемента Д42.1.

Генератор 13 счетных импульсов (фиг. 13) предназначен для заполнения временного интервала сдвига фаз прямоугольной последовательностью импульсов с частотой 70 МГц и состоит из кварцевого резонатора BQ3, транзистораVT11, элемента Д42.2, резисторов R90R93, конденсаторов С29-С32 и индуктивностей L1,12,

Счетчик 14 (фиг. 12) предназначен для подсчета количества импульсов выхода схемы 12 логического совпадения и выдачи его через регистр с тремя состояниями на блок 1 управления по шине данных. Он содержит микросхемы Д43,...,Д45.

Устройство работает следующим образом.

После начальной установки элементами R1 и СЗ блока 1 (фиг.2) и элементами R2 и С4 соответственно после включения напряжения питания запускается тактовый генератор на элементах С1, С2 и BQ1 с частотой 12 МГц (фиг. 2). Порт Р0 микропроцессора (МП) Д1 является мультиплексированным, т.е. по нему передаются младший байт адреса и байт данных. Через порт Р2 передается старший байт адреса. Младший байт адреса записывается в регистр Д2, а старший - в регистр Д4 по сигналу с МП ALE. Далее МП выдает сигнал PSEN, который поступает на вход ПЗУ Д6 CS (выбор кристалла), осуществляя выборку по заданному адресу внешней программной памяти. Этот же сигнал поступает на вход А/В приемопередатчика ДЗ, настраивая его на передачу данных к микропроцессору (). Далее МП, расшифровав команду из ПЗУ, производит соответствующее действие, повторяя в нужный момент обращение к внешней программной памяти. Цикл этого обращения показан на фиг. 14,а. Прием информации по шине данных от блоков 10 и 14 осуществляется через пор г Р1 МП, а подсчет импульсов переполнения от блока 14 Т0 -встроенным таймером в соответствии с заданным алгоритмом. В соответствии с этим алгоритмом работы, приведенным на фиг. 16, осуществляется запись информации от МП в дешифратор 2 команд. Это происходит согласно фиг. 14,6 следующим образом. Адрес записывается в регистры Д2 и Д4 по сигналу ALE. Сигнал PSEN в этом случае не подается, а после того, как на выходе приемопередатчика ДЗ через порт Р0 установлены уводимые данные (разряды Д0Д7) подается сигнал WR (запись), который, поступая на ППА Д7 (фиг.2), осуществляет запись данных в выбранный адресными разрядами А 0 и А1 выходной порт РА, РВ или PC. Сигнал ВК, поступающий низким уровнем с блока 1, активизирует микросхему Д7 в течение цикла записи.

Адреса портов ППА следующие:

РА-8 000 Н;

РВ-8 00 1Н;

PC-8 00 2Н.

Перед началом работы разряды портов ППА имеют следующие значения (табл. 2).

Цикл измерения начинается с поиска нужного диапазона измерения. В преобразователе 4 ток - напряжение включается первый диапазон. Это происходит после подачи сигнала 1 диап с разряда порта РА0 блока 2 низким уровнем, который включает реле К1 блок 4 (фиг.5). Это реле своими контактами подключает в цепь обратной связи операционного усилителя Д14 элементы R29 и С12. Тестовый сигнал с выхода генератора 3 проходит через измеряемый элемент 15 и с выходов блоков 4 и 5 поступает на сигнальные входы блоков 6,7,8 (фиг. 15, а,е,к). Далее в блоке 8 коммутации каналов (фиг. 8) осуществляется коммутация канала Ит на вход интегрирующего детектора 9. Это происходит после подачи сигнала высокого уровня с порта РА и блока 2. До подачи этого сигнала вход повторителя Д25 блока 8 посредством ключей Д21-Д23 (фиг.8) был отсечен от каналов UT и 1)н. На выходе повторителя сигнал отсутствовал. После подачи сигнала Ком.кан. UT (фиг. 15,а,в) ключ Д22.2 закрывается, а ключи Д21.1 и Д22.1 открываются, обеспечивая прохождение сигнала UT через ФНЧ на элементах С23 и R67 на выход повторителя Д25. После этого МП блока 1 осуществляет выдержку в 1,0мс, необходимую для коммутации диапазонного сопротивления R29 в преобразователе 4 ток - напряжение (фиг.5), и установление переходных процессов.

Далее происходит интегрирующее детектирование сигнала UT по полупериоду рабочей частоты интегрирующим детектором 9. С разряда порта РС2 блока 2 низким уровнем выдается сигнал Сброс ИД длительностью 10 мкс (фиг. 15,а), который устанавливает прямой выход D-триггера Д33.1 блока 9 (фиг. 9) в состояние О. Замыкается ключ Д32.1, разряжая емкость С24 интегратора Д31. После импульса Сброс с разряда порта РСЗ блока 2 подается сигнал Запуск (фиг; 15,а,б). На D-входе триггера Д33.1 блока 9 устанавливается высокий уровень и триггер находится в состоянии готовности.

После перехода напряжения через ноль в положительную область значения (момент времени ta, фиг, 15,а,з),на прямом выходе которого устанавливается уровень Г. Размыкается ключ Д32.1 интегратора Д31, вводя его в режим интегрирования, и запускается одновибратор Д34.2, выдающий импульс длительностью Тр/2 (фиг. 15,б,и) (полупериода частоты тестового си0 нусоидального сигнала). Этот импульс выключает ключ Д26.2 и включает ключ Д26.1, подавая сигнал UT на вход интегратора. Начинается процесс интегрирования по полупериоду (фиг. 15,б,к). По окончании

5 импульса одновибратора Д34.2 в момент времени t4 (фиг. 15,б,и) сигнал UT посредством ключей Д26 отключается от интегратора Д31 и детектор 9 переходит в режим хранения информации. Последовательнозапуска0 ются два одновибратора Д34.1 и Д36.1, которые через 80 мкс в момент времени ts выдают на АЦП 10 сигнал низкого уровня Запуск АЦП (фиг. 15,б,л) длительностью 2 мкс. По этому сигналу напряжение UT с вы5 хода усилителя Д35 блока 9 поступает на вход аналого-цифрового преобразователя 10 и преобразуется АЦП Д40 (фиг. 10) в течение 4-6 мкс в 12-разрядный цифровой код, который по сигналам низкого уровня с раз0 рядов порта РА6, РА7 блока 2 1 байт и 2 байт передается через трехстабильные буфера Д38, Д39 побайтно по шине данных (сначала 8 младших разрядов, затем 4 старших) на порт Р1 МП Д1 блока 1 управления.

5 Если после перевода цифрового кода микропроцессором ему будет соответствовать значение напряжения 10,23 758, то это свидетельствует о том, что измеряемый элемент находится не в допуске и не может

0 быть измерен. В этом случае цикл поиска начинается сначала, а на индикацию выдается сигнал переполнения. Если значение напряжения находится в пределах 1В ,2375В, то нужно переходить к

5 измерению. Если значение напряжения меньше 1 В, то необходимо включить 2-й диапазон измерения, предварительно отключив сигнал Запуск (установить РСЗ в О), и подав с разряда порта РС2 сигнал Сброс

0 ИД. Далее повторяются те же операции, что и для 1-го диапазона измерения. Если значение напряжения, снятого микропроцессором с АЦП 10, будет меньше 1В и на втором диапазоне, то включается третий ди5 апазон, а при необходимости и четвертый. Включение диапазонов осуществляется подачей сигналов 2 диап.; 3 диап. и 4 диап. с разрядов порта РА1РАЗ дешифратора команд 2 низким уровнем. В резуль- тате в блоке 4 реле К2-К4 будут подключать

в цепь обратной связи OY Д14 соответствующие элементы (фиг. 5). Если на четвертом диапазоне напряжение УЛЦП будет меньше 1В, то все равно осуществляется переход к режиму измерения элемента. Если в процессе поиска в 2-4 диапазонах, напряжение ,2375, то поиск прерывается на данном диапазоне, и вновь начинается с первого диапазона.

Режим измерения состоит из трех тактов, В первом такте проводится измерение и запоминание напряжения смещения на выходе интегрирующего детектора 9 при отключенном генераторе 3 синусоидального напряжения (блок 9 коммутации каналов отключен). В последующих расчетах участвуют времена чистого измерения, но фактическое время измерения будет несколько больше, так как после каждого включения и выключения коммутатора 8 перед подачей импульса Запуск или Калибр на детектор 9 в предлагаемом измерителе осуществляется задержка длительностью в 350 мкс, необходимая для устранения влияния переходных процессов, Так как при анализе прототипа время переходных процессов не учитывалось, то для корректного сравнения не учитывается это время и при анализе предлагаемого измерителя.

В первом такте происходит интегрирующее детектирование напряжения смещения по полупериоду тестовой частоты, а также измерение сдвига фаз между сигналами DT и UH, поступающими с блоков 4 и 5. Для этого отключается канал UT в блоке 8 посредством подачи с блока 2 в момент времени te сигнала Ком.кан, т низкого уровня (фиг. 15, а, в). Следует выдержка в 350 мкс. Потом на блок 9 с блока 2 подается сигнал Запрет низким уровнем. Теперь импульсы с компаратора Д27 уже не могут опрокинуть триггер Д33.1 блока 9. Далее на блок 9 с блока 2 в момент времени t подается сигнал Сброс ИД длительностью 1 мкс (фиг. 15, а,а), который устанавливает триггер Д33.1 (фиг.9) в исходное состояние, а на цифровой фазовый детектор 11 и на счетчик 14 с разрядов портов РС7 и РВ1 Д7 блока 2 подаются сигналы Сброс ФД и Сброс С4 (фиг. 15,а и 15,б,п) низким уровнем длительностью 1 мкс. Выходы 0 D-триггеров Д33.2 и Д41 блока 11 (фиг. 11) устанавливаются в О, а счетчики Д43 и Д44 блока 14 (фиг. 12) обнуляются. После этого в момент времени te на блок 9 с блока 2 подается сигнал Запуск (фиг.15,а,б) и высоким уровнем сигнал Калибр длительностью 1 мкс (фиг. 15,а ,д). На фазовый детектор 11 подается сигнал Разрешение на измерение сдвига фаз (фиг. 15,

б.м). На выходе интегрирующего детектора 9 выделится напряжение смещения 11См(т) (фиг. 15,6,к):

UCM(t) Г

ftp UCMI 18 То

dt + UCM2

/y2 ldt+UcM2,(17)

где напряжение смещения нуля на входе интегрирующего детектора;

UCMZ напряжение смещения нуля на выходе интегрирующего детектора;

Тр - период рабочей частоты;

TD - постоянная времени интегрирующего детектора.

В момент времени tg на выходе детектора выделится постоянное напряжение UCM(t9):

UCM (t) Цм т + исм2

(18)

В момент времени tio результат выдается на АЦП 10, снимается микропроцессором

и запоминается в ОЗУ микропроцессора блока 1 управления. После этого в момент времени tn на блок 9 выдается импульс Сброс ИД, и сигнал Запуск принимает уровень О (фиг. 15,а,б). Сигнал Запрет

принимает высокий уровень.

Измерение сдвига фаз начинается в момент времени te после выдачи сигнала Раз- решение. Триггер ДЭЗ,2 цифрового фазового детектора 11 (фиг. 11) находится в

состоянии ожидания положительного перепада с компаратора Д19 блока 6 (фиг. 7). На вход компаратора поступает синусоидальный сигнал UT с блока 4. В момент перехода напряжения UT (пропорционального току,

протекающему через измеряемый элемент) через ноль (момент времени т,н.ф7фиг. 15, а) срабатывает компаратор блока 6 Д19, триггер ДЭЗ.2 блока 11 опрокидывается и выдает на вход элемента совпадения Д42.1 блока

12 (фиг. 12) разрешение (уровень Г)на прохождение через него счетных импульсов с генератора 13 (фиг, 15,б,н,о) на счетчик Д43 блока 14. Импульсы переполнения с выхода Р счетчика Д43 (фиг. 12) поступают на счетный вход С счетчика Д44, а импульсы переполнения с выхода Р Д44 через шину данных - на таймер Т0 МП блока 1, который находится в режиме приема счетных импульсов. Кроме этого, триггер Д33.2 блока 11 (фиг. 11) в момент опрокидывания переключает триггер Д41,1, который выдает на D-вход триггера Д41.2 разрешение на включение по положительному перепаду сигнала с выхода компаратора Д20 блока 7 (канал UM) (фиг. 7), В момент перехода напряжения UH (пропорционального падению напряжения на измеряемом элементе) через ноль (момент времени т.ф. фиг. 15ta,e) триггер Д41.2 блока 11 опрокидывается и сбрасывает триггер ДЭЗ.2, запрещая тем са- мым прохождение счетных импульсов с генератора 3 через элемент совпадения Д42.1 блока 12 на счетчик 14 (фиг. 15,б,н,о). Счет прекращается. С дешифратора 2 команд на блок 14 через 1.5 мс после te выдается сигнала Конец измерения, который передним фронтом записывает информацию со счетчиков Д43, Д41 (фиг. 12) в регистр с тремя состояниями Д45 и по сигналу ВК с блока 2 низким уровнем эта информация по шине данных записывается в порт Р1 МП блока 1 управления, где складывается со значением, накопленным в таймере Т 0. После этого сигнал Разрешение принимает низкий уровень (фиг.15,б,н).

Во втором такте измерения производится детектирование, измерение и запоминание сигнала UT, пропорционального току, протекающему через объект измерения:

N-llW-яЗЪ} 9)

где |UT|- амплитуда сигнала на выходе преобразователя 4;

амплитуда напряжения на выходе генератора

Кпд - величина образцового диапазонного сопротивления в цепи обратной связи Д14 преобразователя 4;

Zx - комплексное сопротивление изме- ряемрго объекта;

Zn - комплексное паразитное сопротивление подключающих проводов.

В момент времени ti2 (фиг. 15,а,в) на блок 8 с блока 2 высоким уровнем подается сигнал Ком.канала UT, на вход детектора 9 поступает сигнал UT (фиг. 15,а,з). На детектор 9 с блока 2 высоким уровнем подается сигнал Запуск (фиг. 15,а.б). В момент времени ш(фиг. 15.а,з)при переходе напряжения UT через ноль срабатывает компаратор Д27 блока 9 и начинается процесс интегрирования по полупериоду рабочей частоты (фиг. 15,б,к). В момент ti4 (фиг 15,б,к), определяемый длительностью импульса одно- вибратора Д34.2 блока 9 (фиг.15,6,), детектор переходит в режим хранения информации. В отрезок времени ti4-tia на выходе детектора 9 выделится напряжение UT«:

итЮ т / $д:1исм1Л+Кф#+ Дп °biati + UcM2, V®

где Шр - круговая рабочая частота, на которой проводится измерение;

Д ti - ошибка выбора начала интегрирования детектором, связанная с наличием паразитных смещений на входе компаратора и на входе детектора;

Кф - коэффициент передачи RC-фильтра в блоке коммутации каналов;

0

5

0

5

0

5

0

5

0

5

Um+UcMh+Ug-Koc

ГШ

Ati -gbarcsi

где UcMk напряжение смещения, приведенное к положительному входу компаратора (для К554САЗА UCMR Ј ):

U«° - напряжение нуля на выходе компаратора (Ui Ј 0,2В);

Кос - коэффициент, передачи цепи положительной обратной связи компаратора с выхода на вход (Кос-З.).

В момент времени tn (фиг.15,б,к) на выходе детектора выделится напряжение UT(ti4):

(Tp-2Ati) iUTJKd

UT идОк) (COS -wsO)

UT(tu) UCM

2Ъ

-COStop Ati) + UcM2-(21)

В идеальном варианте (все напряжения смещения равны нулю) в момент ti4 на выходе детектора напряжение достигло бы величины UT ид(ш):

lUtlK,) а)р То

.

После съема микропроцессором блока 1 значения величины напряжения UT(ti4) с АЦП (блок 10), МП оценивает результат измерения. Может быть несколько вариантов:

а)величина измеренного напряжения UT(ti4) равна 10,2375В; в этом случае вся предыдущая информация сбрасывается и МП переходит к режиму поиска диапазона;

б)если величина измеренного напряжения UT(ti4) удовлетворяет условию 1В UT(ti4) 10,2375В, то его величина запоминается в ОЗУ и осуществляется переход к третьему такту измерения;

в)если измерение производится в одном из диапазонов (1-3), то если , то вся предыдущая информация сбасывается и МП переключается к режиму поиска диапазона.

В третьем такте измерения происходит детектирование, измерение и запоминание сигнала UH, пропорционального падению напряжения на объекте измерения:

ш

UH |Ur KDy,

(23)

Hj-iurr

где |ин|- амплитуда сигнала на выходе дифференциального усилителя 5;

Кду - коэффициент передачи усилителя 5.

В момент времени tn дешифратор 2 команд выдает на детектор 9 сигналы Запуск низкого уровня (фиг. 15,а,б), устанавливает детектор импульсом Сброс ИД в исходное состояние (фиг. 15,а,а), на блок 8 с декодера 2 поступают сигналы Ком.канала UT низкого уровня и Ком.канала UH высокого уровня (фиг. 15,а,в,г), переключая тем самым на выход Д25 блока 8 сигнал UH с дифференциального усилителя (фиг. 15,а.з). В момент времени tie (фиг. 15,а,б) с блока 2 выдается сигнал Запуск на детектор 9. В момент tig (фиг. 15,б,и) компаратор Д27 срабатывает, опрокидывает триггер Д33.1 и начинается процесс интегрирования по полупериоду (отрезок времени tig-t2o); на выходе Д35 детектора 9 выделится напряжение UH(t):

UH(t)yJpAt2uCM1dt-iv

4Р+Дts H I dt + UcM2 , (24)

где Д1г - ошибка выборки начала интегрирования детектором.

А. 1 , UCMI +UcMk+UB Koc At -йЈ arcslnГЩ

(25)

В момент времени tig на выходе детектора выделится напряжение UH(ti9):

ti rt -ч ТР 2At2 {иИКф оуГр UH(tig) - UCMI -Tf5 TrjCcOS-T

- COS (Op At2 + UCM2 .(26)

В идеальном варианте (все напряжения смещения равны нулю) это напряжение имело бы величину:

|felK -W

После окончания интегрирования значение напряжения UH(t) преобразуется АЦП 10 в цифровой код, снимается микропроцессором блока 1 и запоминается в ОЗУ МП Д1. Далее микропроцессором блока 1 производится вычитание из Ur(ti4) и Un(ti9) величины паразитного смещения UcM(tg) (см.(18)). В результате получаются окончательные величины UTO и UHO:

UTO UT(tt4) - UCM(tig) - UCMI - Й (cos - cos wp&i) j (28)

(ОрТо

At2

UHO UH(tl9) - UCM(t9) - UCMI

lt№ (cos - cos At2) - P9)

Далее микропроцессором производится деление UTO на UHO и умножение на Кпд. В результате получается модуль комплексной проводимости измеряемого элемента:

Gx U Knfl где Кпд - диапазонный множитель;

Кпп - КЛУ

где Кду - коэффициент усиления дифференциального усилителя 5;

Ннд - сопротивление обратной связи в преобразователе 4.

Величина Gx запоминается в ОЗУ МП.

При отсутствии напряжений смещения результат деления соответствовал бы истинной величине проводимости измеряемого элемента:

г Цт ид(114) vrto. .

-ГТ--П КПД-(32)

Подставляя в (32) формулы (22); (27), ис- пользуя (19); (23) и (31). получаем значение

Gx ист

GX ИСТ -J- (33)

Погрешность измерения проводимости определяется как:

5Gx

Gx GXHCT

(34)

GXHCT

Uro-Lbnfl(tl9) - Цгид(114)Цно UHolW(tl4)

На основе (34), используя (20): (22); (25): (27); (28) и (29) можно проанализировать величину погрешности измерения 5GX при

UCMI +Ю 2в|ит| 1В:|ин| 1В,СУр 104

Анализируя погрешность измерения предлагаемого измерителя, вызванную наличием паразитных смещений постоянного напряжения его цепей, можно сделать вывод: влияния этих смещений практически

полностью исключаются и не оказывают существенного влияния на результат измерения даже, если его величина (смещения) имеет значительную величину, в данном случае от 0,1 до 1 %, от величины полезного

сигнала. В предлагаемом измерителе влияние величины паразитного напряжения сме- щения на результат измерения уменьшается в 100-250 раз и по точности не уступает прототипу. После записи величины

Gx в ОЗУ МП переходит к расчету и анализу сдвига фаз между UT и UH. Сначала рассчитывается время сдвига фаз:

tx(256NxT+Nxq /fo.(35)

где NXT число, накопленное в таймере Т0 микропроцессора;

NXЈ число, снятое микропроцессором с регистра Д43 блока 14;

fo - частота повторения генератора счетных импульсов (70 МГц).

Далее значение tx переводится микропроцессором в угловую величину

fb Wp tx(36)

и производится анализ сдвига фаз между От и UH. Если р удовлетворяет условию

JT

Q р тг,то осуществляется расчет емкостного сопротивления.

Вычисляются величины sin р и cos p, затем осуществляется расчет емкости (по параллельной схеме включения):

Cx |bsin (37)

и расчет сопротивления (по параллельной схеме включения) или tg § ;

Rx 1/Gxcospx ;(38.1)

tg yv/cos .(38.2)

Величины Сх и Rx выдаются на индикацию (блок индикации на фиг.1 не показан) или на ЭВМ, в качестве которой может быть использована любая серийная модель ЭВМ с соответствующим интерфейсом. После этого осуществляется переход к первому такту измерения.

3 Если уЗх удовлетворяет условию фе 2: -х

(емкостное или индуктивное сопротивление), то расчет осуществляется следующим образом.

Рассчитывается величина

0х 2л:-рх.(39)

Если .то производится расчет , f а затем емкости Сх (параллельная схема включения):

pi:

Сх Gx/Wt 3 Sln #J

(40)

и сопротивления Rx (параллельная схема включения) или tg 6:

Rx 1/Gxcoslpx4;(41.1)

(41.2)

cos|pxr I

После этого значения Сх и Rx выдаются на индикацию и осуществляется переход к первому такту измерения.

Если /Ј 0. то осуществляется расчет индуктивности Lx (последовательная схема включения):

л. 1 Л Л

LX

(42)

Gx uJp

и сопротивления Rx (последовательная схема включения)

(43)

Величины LX и Rx выдаются на индикацию и осуществляется переход к первому такту измерения.

Время всего цикла измерения Гц предлагаемого измерителя определяется по формуле

Гц ТЗ + Г4 + ТВ + ЗГб ,(44)

где гз - время детектирования напряжений смещения (te-tg фиг, 15,б,к); тз-Тр/2;т

Г4 - время измерения | UT| (ti2-tu, фиг. 15,а,в; 15б,к);

Г4-Тр/2-1,5Тр;

TS - время измерения |UH( (ti7-tis, фиг. 15,а,г; 15,в,к);

те- время преобразования АЦП (tg-trc;

ti4-ti5; tig-t20, фиг.15,б,к,л); мкс. Можно сравнить время тгч с временем

Гц (время измерения прототипа, см. (15) И (16). При работе прототипа на одной и той же частоте время л прототипа и гз, ТА, тв предлагаемого измерителя можно считать равными, так как в основе детектирования

лежит один и тот же физический принцип. Время Г2 можно приравнять к те, так как они постоянны и занимают относительно небольшое время в цикле измерения (10- 30%). Таким образом, время измерения

предлагаемого измерителя гц можно переписать во временах ri и га прототипа: Гц 3ri + Зг2 .(45)

Выполнение измерителя описанным выше способом обеспечивает повышение

быстродействия при измерении параметров комплексных сопротивлений. Измерителем самостоятельно определяется тип измеряемого элемента.

Вследствие этого измеритель, построенный по предлагаемому принципу, при измерении параметров комплексных сопротивлений имеет по сравнению с прототипом выигрыш в быстродействии в 1,7- 2.1 раза.

Формула изобретения

Измеритель параметров комплексных сопротивлений, содержащий генератор си- нусоидального напряжения, преобразователь ток - напряжение, первый вход

которого соединен с первым выводом измеряемого сопротивления, элемент совпадения, первый вход которого соединен с выходом генератора счетных импульсов, а выход- с первым входом счетчика, и.компаратор, сличающийся тем, что, с целью повышения-быстродействия, в него введены блок управления, дешифратор команд, дифференциальный усилитель, блок коммутации каналов, интегрирующий детектор, аналого-цифровой преобразователь, цифювой фазовой детектор и второй компаратор, второй вывод измеряемого сопротивления соединен с выходом генератора синусоидального напряжения и первым входом дифференциального усилителя, второй вход которого соединен с первым входом преобразователя ток - напряжение, а выход - с первым входом блока коммутации каналов и первым входом второго компаратора, выход преобразователя ток - напряжение соединен с первым входом первого компаратора и вторым входом блока коммутации каналов, выход которого соединен с первым входом интегрирующего детектора, первый и второй выходы которого соединены с первым и вторым входами аналого-цифрового преобразователя соответственно, выходы

первого и второго компараторов подключены соответственно к первому и второму входам цифрового фазового детектора, выход которого соединен с вторым входом элемента совпадения, выход счетчика соединен с выходом аналого-цифрового преобразователя и входом блока управления, выход ко- торого соединен с входом дешифратора

0 команд, выход которого соединен с вторыми входами преобразователя ток - напряжение, интегрирующего детектора и счетчика и третьими входами цифрового фазового детектора, блока коммутации каналов и аналого-цифрового преобразователя, вторые BXL цы первого и второго компараторов соединены с общей шиной измерителя.

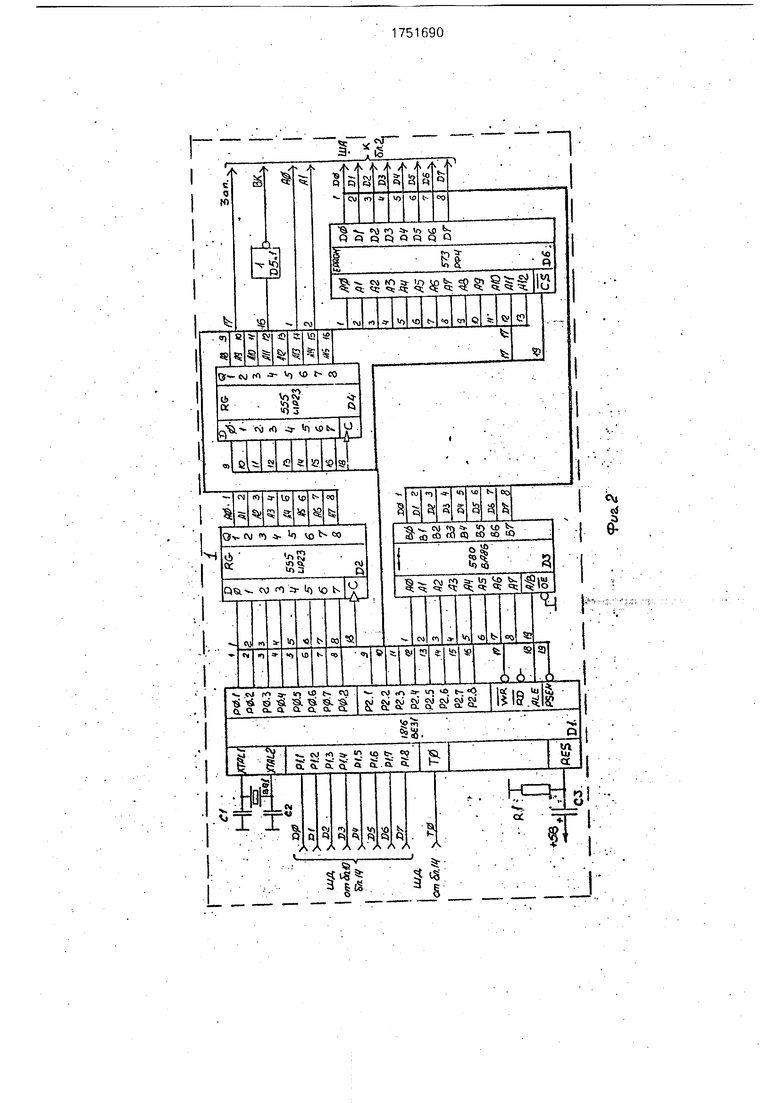

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения гистерезиса @ характеристик | 1985 |

|

SU1247797A1 |

| Интегрирующий преобразователь постоянного напряжения в код | 1988 |

|

SU1672565A1 |

| Устройство для измерения температуры | 1981 |

|

SU979891A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО КОНТРОЛЯ ТЕМПЕРАТУРЫ | 2015 |

|

RU2631018C2 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1681384A1 |

| Устройство время-импульсного преобразования постоянного напряжения в код | 1982 |

|

SU1091333A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Способ измерения относительной разности амплитуд двух гармонических напряжений | 1988 |

|

SU1732287A1 |

| Интегрирующий аналого-цифровой преобразователь | 1984 |

|

SU1314457A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

Использование: в измерительной технике для измерения параметров емкостей, ин- дуктивностей и сопротивлений. Сущность изобретения: выход генератора 3 синусоидального напряжения и первый вход дифференциального усилителя 5.соединены с первым выводом измеряемого сопротивления 15, второй вывод которого соединен с вторым входом дифференциального усилителя 5 и первым входом преобразователя 4 ток - напряжение, выход которого соединен с первым входом компаратора 6 и первым входом блока 8 коммутации каналов. Выход дифференциального усилителя 5 соединен с первым входом компаратора 7 и вторым входом блока 8 коммутации каналов, выход которого соединен с первым входом интегрирующего детектора 9, первый и второй выходы которого соединены с первым и вторым входами аналого-цифрового преобразователя 10, выход которого вместе с выходом счетчика 14 соединен с входом блока 1 управления, выход которого соединен с входом дешифратора 2 команд, выход которого подключен к вторым входам преобразователя 4 ток - напряжение, интегрирующего детектора 9 и счетчика 14 и третьими входами цифрового фазового детектора 11, блока 8 коммутации каналов и аналого-цифрового преобразователя 10. Выходы компараторов 6 и 7 подключены к первому и второму входам цифрового фазового детектора 11, выход которого соединен с вторым входом элемента 12 совпадения, первый вход которого соединен с выходом генератора 13 счетных импульсов, а выход-с первым входом счетчика 14. 1 с.п. ф-лы, 16 ил. 3 ON О О

Таблица 2

Таблица 3

о

CD ID

Ю Г|

O J

1$

Фаг. 5

БлЛ

R6Q

R№

Т

шу

ffffi

Г

si

Ш1

mz

R56

9°l

Фиг. Ю

Г

im

n

+tt

в

Л 41.2

Фиг.11

Фиг. 12

+58

LI

CIS Ш Wl

гЩ(

ffWPrjC Jt-jis X i ла-лк

и

си

KSji.12

Фиг.13

Фаг. 14

1C

№

II

Д г

1

гг

1

I If t

т

W

в а

4

ч

ъ-

Г7

№к 15 S

( Вход

Включение 1-го диапа- Звна

Выдержка 1мсек Сброс ИД

Запуск И А

Выдержка 1,05 псе к Съем инф-и s AIM

Включение 2-ZD диапаз. Сброс ид Выдержка 1 ft сек

Запуск ИД Выдержка 1,05 мсек Съём инф-ц С АЦП

4}

Включение Э-его даапаз. Cffpoc Ии Выдержка leicek

Запуск ИЛ Выдержка 1.05 псек

включение 4-го дивпаз.

CffpUC ИД

Выдержка 1 мсек

Запуск ИД выдержка / 05мсек съем инФ-а с АЦП

Фиг. 16 а

н

eg

N

- л

Т

з

&

S.

Фае 158

V

| Цифровой измеритель @ -параметров | 1984 |

|

SU1252739A1 |

| кл | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Измерение параметров цепей с сосредоточенными постоянными | |||

| - Радиоизмерительная техника, 1986, с | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| рис | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

Авторы

Даты

1992-07-30—Публикация

1989-11-20—Подача