(54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАПИИ

1

Изобретение относится к телемеханике и х люжет быть применено для обмена информацией в автоматизированных системах управления.

Известно устройство для передачи и приема информации, содержащее передатчик, информационные выходы которого подключены к информационным каналам,и приемник 1.

Это устройство обладает низкой помехоустойчивостью при одновременном и одинаковом искажении прямого и инверсного синхроканалов.

Н шболее близким по технической сущности к предлагаемому изобретению является устройство для передачи и приема сигналов, содержащее прямой и инверсный синхроканалы элементы И и полусумматор, выходы информационных каналов подключены к первым входам элементов И, выходы которых -подключены к входам приемника, выход которого через канал обратной связи соединен с . входом передатчика, выходы синхронизации передатчика через прямой и инверсный синхроканапы подключены к входам полусумматора, выход которого подключен к вторым входам элементов И и к входу синхронизации приемника, выход прямого синхроканала соединен с третьими входами злементов И 2.

Данное устройство достаточно сложно из-за наличия нескольких сикхроканалов и имеет недостаточную помехозащищенность при возникновении двухполярной помехи, ощговременно во всех передающих каналах, в том

to числе и в каналах синхросигналов.

Цель изобретения - упрощение устройства за счет исключения инверсного синхро. канала.

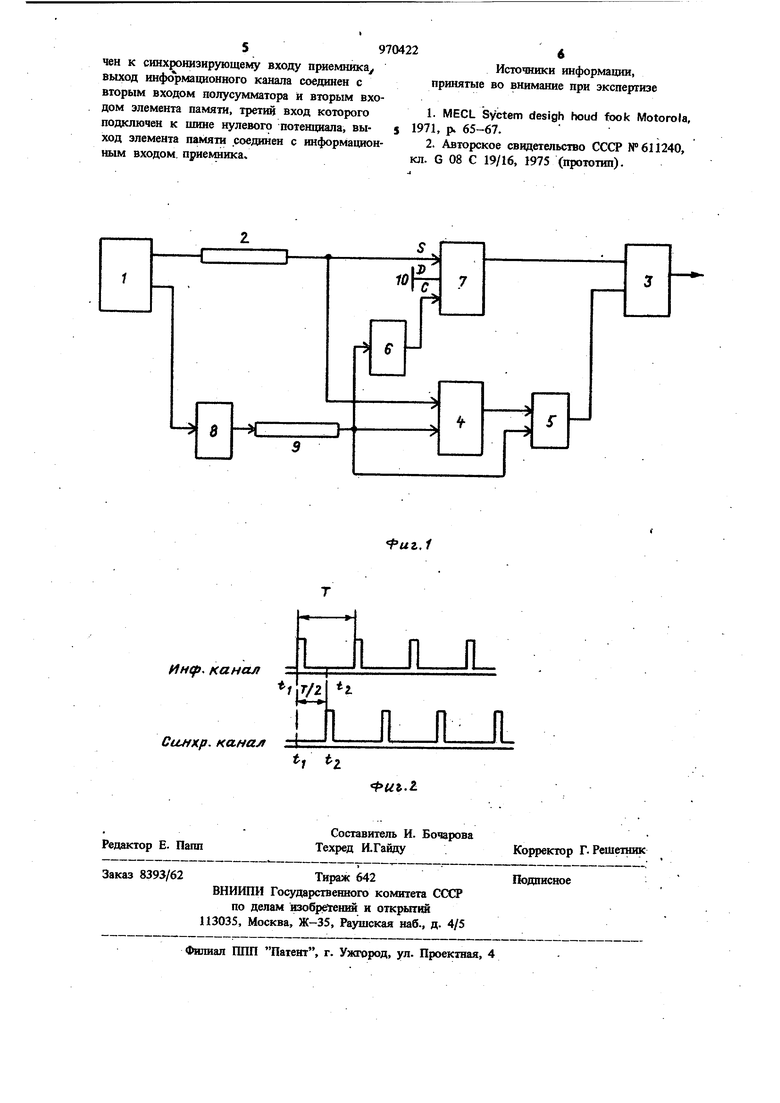

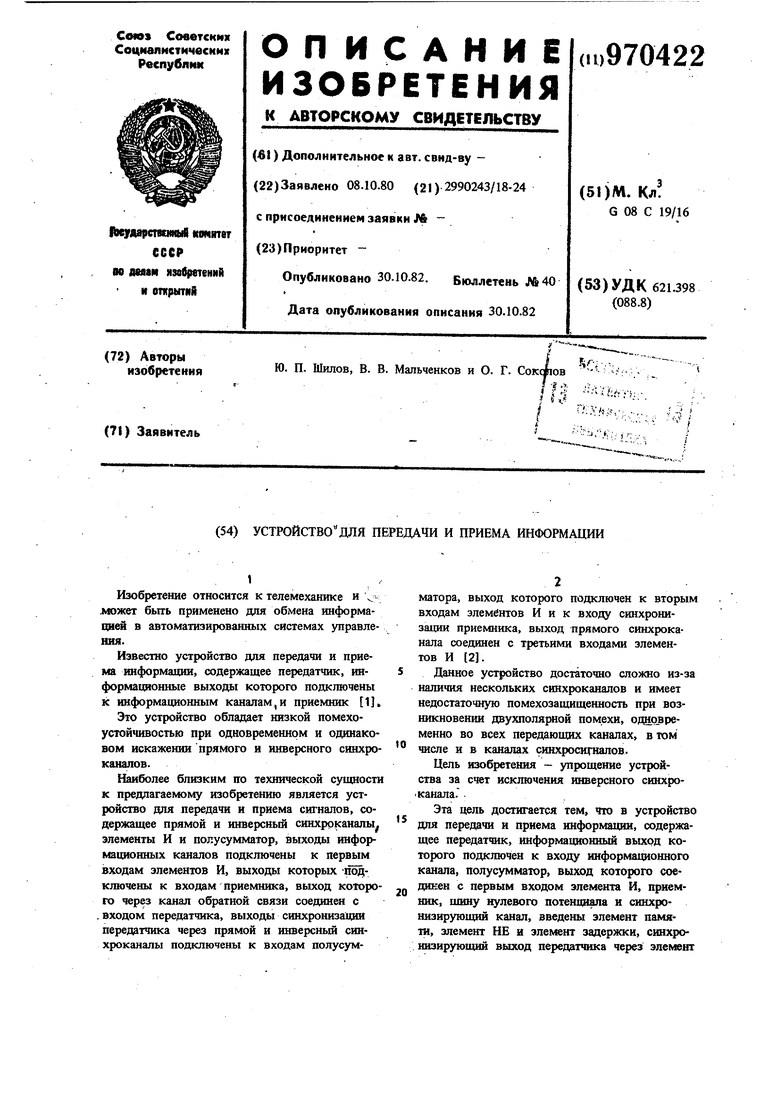

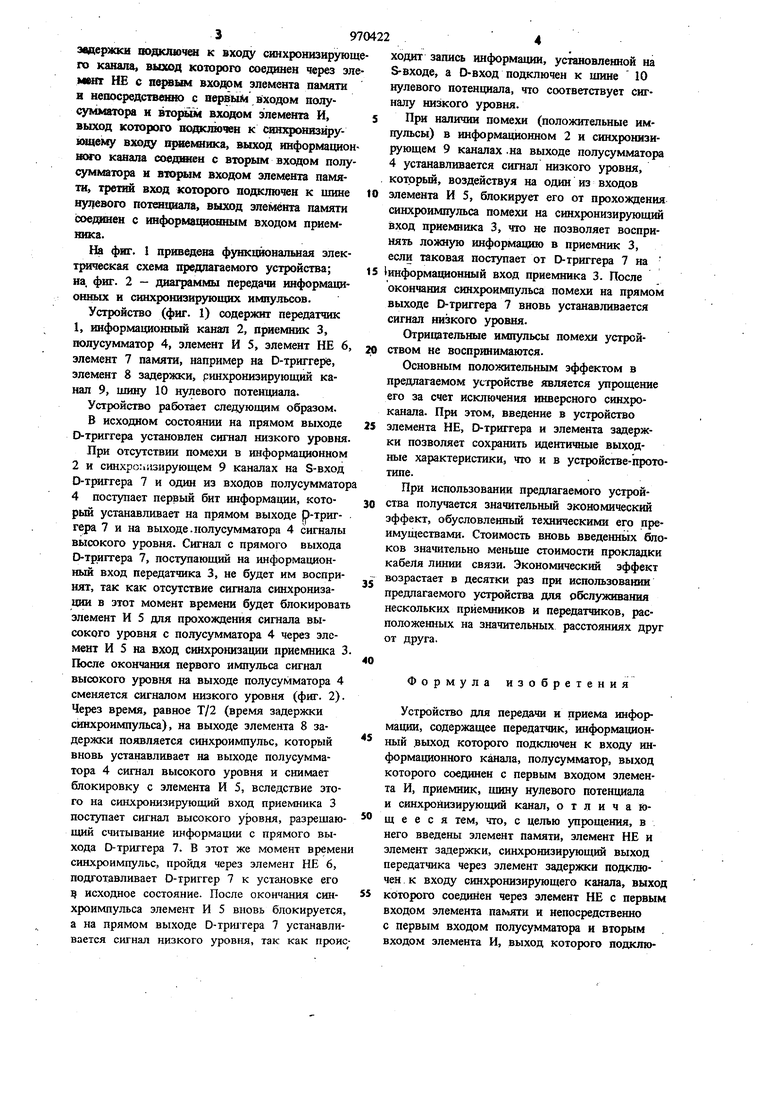

Эта цель достигается тем, что в устройство для передачи и приема информации, содержащее передатчик, ииформациоиный выход которого подключен к входу информационного канала, полусумматор, выход которого соединен с первым входом элемшта И, прием20ник, цщну нулевого потенциала и синхронизирующий канал, введены элемент памяти, элемент НЕ и элемент задержки, синхронизирующий выход передатчика через элелюнт 39 задержки шщкдючен к входу синхронизирующ го канала, выход которого соединен через эл мент НЕ с первым входом элемента памяти я неоосредственио с вервым входом полусумматора и вторым входом элемшта И, выход которого нодключен к сиихронкзир/юздему входу вриеюаякя, выход информащюн всию канала совдшюн с вторым входом полу сумматора и входом элемента памяти, третий вход которого подключен к шине нут евого потен1щала, выход элемента памяти соеданен с информащояным входом приемшоса. На фиг. 1 приведена функцйоналы ая элект жческая схема предлагаемого устройства; иа. фиг. 2 - диаграммы передачи информашошв 1Х и синхронизирующих импульсов. Устройство (фиг. 1) содержит передатчик 1, информационный канал 2, П1жемник 3, полусумматор 4, элемент И 5, элемент НЕ 6 элемент 7 памяти, например на D-триггере, элемент 8 задержки, ринхронизирующий канал 9, шину 10 нулевого потенциала. Устройство работает следующим образом. В исходном состоянии на прямом выходе D-триггера установлен сигнал низкого уровня При отсутствии помехи в информационном 2 и синхрсьязирующем 9 каналах на S-вход О-трштера 7 и один из входов полусумматор 4 поступает первый бит информации, который устанавливает на прямом выходе р-триггера 7 и на выходе.полусумматора 4 сигналы высокого уровня. Сигнал с прямого выхода D-триггера 7, поступающий на информационный вход передатчика 3, не будет им воспринят, так как отсутствие сигнала синхронизации в этот момент времени будет блокироват элемент И 5 для прохождения сигнала высокого уровня с полусумматора 4 через элемент И 5 на вход синхронизации приемника 3 После оконтания первого импульса сигнал высокого уровня на выходе полусумматора 4 сменяется сигналом низкого уровня (фиг. 2). Через время, равное Т/2 (время задержки синхроимпульса), на выходе элемента 8 задержки появляется синхроимпульс, который вновь устанавливает на выходе полусумматора 4 сигнал высокого уровня и снимает блокировку с элемента И 5, вследствие этого на синхронизирующий вход приемника 3 поступает сигнал высокого уровня, разрешаю щий считывание информации с прямого выхода D-триггера 7. В этот же момент времен синхроимпульс, пройдя через элемент НЕ 6, подготавливает D-триггер 7 к установке его Э исходное состояние. После окончания синхроимпульса элемент И 5 вновь блокируется а на прямом выходе D-Tpmrepa 7 устанавли вается сигнал низкого уровня, так как прон ходит запись информации, установленной на S-входе, а О-вход подключен к шине 10 нулевого потенциала, что соответствует сигналу низкого уровня. При наличии помехи (положительные импульсы) в информационном 2 и синхронизирующем 9 каналах .на выходе полусумматора 4 устанавливается сигнал низкого уровня, который, воздействуя на один из входов элемента И 5, блокирует его от прохождения синхроимпульса помехи на синхронизирующий вход приемника 3, что не позволяет воспринять ложную информацию в приемник 3, если таковая поступает от D-триггера 7 на информащюнный вход приемника 3. После окончания синхроимпульса помехи на прямом выходе D-триггера 7 вновь устанавливается сигнал низкого уровня. Отрицательные импульсы помехи устройством не воспринимаются. Основным положительным эффектом в предлагаемом устройстве является упрощение его за счет исключения инверсного сиихроканала. При этом, введение в устройство элемента НЕ, D-триггера и элемента задержки позволяет сохранить идентичные выходные характеристики, что и в устройстве-прототипе. При использовании предлагаемого устройства получается значительный экономический эффект, обуслов.ченный техническими его преимуществами. Стоимость вновь введенньгх блоков значительно меньше стоимости прокладки кабеля линии связи. Экономический эффект возрастает в десятки раз при испольэовании предлагаемого устройства для рбслуж шния нескольких приемников и передатчиков, расположенных на значительных расстояниях друг от друга. Формула изобретения Устройство дпя передачи и приема информации, содержащее передатчик, информационный выход которого подключен к входу информационного канала, полусумматор, выход которого соединен с первым входом элемента И, приемник, шину нулевого потенциала и синхронизирующий канал, отличающееся тем, что, с целью упрощения, в него введены элемент памяти, элемент НЕ и элемент задержки, синхронизирующий выход передатчика через элемент задержки подключен к входу синхронизирующего канала, выход которого соединен через элемент НЕ с первым входом элемента памяти и непосредственно с первым входом полусумматора и вторым входом элемента И, выход которого подклю5970422

чен к синхронизирующе входу приемника выход иифсГрмационного канала соединен с вторым входом полусумматора и вторым входом элемента памяти, третий вход которого1. MECL Syctem desigh houd fook Motorola, подключен к шине нулевого потенциала, вы- s 1971. Р 65-67.

ход элемента памяти соединен с информацион-2. Авторское свидетельство СССР №611240,

ным входом, приелмика.кл. G 08 С 19/16, 1975 (прототип).

Источники информации, принятые во внимание при экспертизе

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приемаиНфОРМАции | 1979 |

|

SU841004A1 |

| Устройство для передачи и приемаиНфОРМАции | 1979 |

|

SU830481A1 |

| Устройство для передачи и приема сигналов | 1975 |

|

SU611240A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для сопряжения ЭВМ с линией связи | 1989 |

|

SU1693611A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| СПОСОБ ПРИЕМА-ПЕРЕДАЧИ ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ И СИСТЕМА ПРИЕМА-ПЕРЕДАЧИ ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 2003 |

|

RU2255425C1 |

| Устройство для передачи и приема информации | 1990 |

|

SU1837348A1 |

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

fui,1

Авторы

Даты

1982-10-30—Публикация

1980-10-08—Подача