приема - выдачи устройства и соединен с входами установки в О триггеров заявки и записи, информационные входы которых подключены к входу логической 1 устройства, выход второго элемента И подключен к входу записи первого регистра и соедиг иен с вторым входом элемента ИЛИ-НЕ вькод которого подключен к синхровходу триггера заявки, выход старших разрядов второго регистра подключен к входу второго дешифратора, выход. пятого элемента И подключен к входу четвертого элемента НЕ, выход второго элемента НЕ подключен к входу записи второго регистра, информационный вход которого соединен с информационным входом первого регистра, выход младших разрядов которого подключен к первому информационному входу второго коммутатора, второй информационньй и управляющий входы которого подключены соответственно к выходу дешифратора и к выходу второго старшего разряда первого регистра, первый старший разряд которого подключен к управляющему входу третьего коммутатора5 первый и второй информационные входы которого подключены к прямому и инверсному выходам второго коммутатора, а выход подключен к информационным выходам устройства с первого по Н-й адресные выходы устройства подключены к выходу четвертого коммутатора, первый информационньй вход которого подключен к выходу счетчика адреса, второй информационный

9272

вход четвертого: коммутатора подключен к выходу старших разрядов первого регистра и соединен с выходом младших разрядов второго регистра, управляющий вход четвертого коммутатора подключен к прямому выходу триггера синхронизации, второй вход пятого элемента И соединен с управляющим входом второго коммутатора, выход второго элемента задержки подключен к счетному входу счетчика адреса, выход третьего элемента И подключен к управляющему входу пятого коммутатора, информационный вход которого соединен с входом второго дешифратора, а выходы с первого по N-й подключены соответственно к выходам записи - считывания устройства с первого по N-й, первый и второй выходы второго дешифратс а подключены соответственно к управляюпд1м входам шестого и седьмого коммутаторов, выходы которых подключены к входам приемопередатчиков группы, первые информационные входы шестого и седьмого коммутаторов подключены к первой группе выходов четвертого коммутатора, вторая группа выходов которого подключена к N+1-му входу шестого коммутатора, входы с второго по N-й которс:о подключены соответственно к информационным входам устройства с второго по N-й, входы с второго по N+1-й седьмого коммутатора подключены соответственно к информационным входам устройства с первого по N-й.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Устройство для сопряжения цифровой вычислительной машины с линиями связи | 1983 |

|

SU1166123A1 |

| Устройство для обмена информацией | 1987 |

|

SU1481781A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОДЕССОРА С ПАМЯТЬЮ, содержащее группу приемопередатчиков, первый регистр, дешифратор, триггер выборки, дешифратор адреса, причем входы - выходы приемопередатчиков группы подключены к входам-выходам устройства, выходы приемопередатчиков группы подключены к входам первого регистра, старшие разряды первой группы выходов которого подключены к входам дешифратора, старшие разряды вькодов приемопередатчиков группы подключены к входам дешифратора адреса, выход которого подключен к информационному входу триггера выборки, отличающееся тем, что, с целью повьшения быстродействия, оно содержит второй регистр, семь коммутаторов, счетчик адреса, второй дешифратор, одиннадцать элементов И, триггер заявки, триггер синхронизации, триггер записи, пять элементов НЕ, первый и второй элементы задержки, элемент ШШ-НЕ, причем вход синхронизации адреса устройства через первый элемент НЕ подключен к входу второго элемента НЕ; выход которого подключен к синхровходу триггера выборки. инверсный выход которого подключен к первым инверсным входам первого и второго элементов И, вторые инверсные входы которых подключены соответственно к входам ввода и вывода устройства, а выходы подключены соответственно к первому входу элемента ИЛИ-НЕ и входу третьего элемента НЕ, выход которого подключен к синхровходу триггера записи, прямой и инверсный выходы которого подключены соответственно к первьм входам третьего и четвертого элементов И, вторые входы которых соединены с прямым выходом триггера синхронизации, а выходы подключены соответст(Л венно к входу пятого элемента И и управляющим входам приемопередатчиков группы,вход синхронизации устройства подключен к первым входам элементов И с шестого по одиннадцатый, вторые входы которых подключены соответственно к прямому и инверсному выходам триггера заявки, прямому и инг версному выходам триггера синхронисо зации, выходу пятого элемента И и ГС выходу четвертого элемента НЕ, вы ходы элементов И с шестого по одиню надцатый подключены соответственно к входам установки в 1 и установки в О триггера синхронизации, входам первого и второго элементов за- держки, первому и второму управляющим входам первого коммутатора, информационный, вход которого подключен к выходу дешифратора, а выход подключен к выходам разрешения выборки устройства с первого по N-й, выход первого элемента задержки через пятый элемент НЕ подключен к выходу подтверждения

Изобретение относится к автоматике и вычислительной технике и предназначено для сопряжения процессора мини- и микро-ЭВМ с памятью устройства отображения и редактирования информации.

Целью изобретения является повышение быстродействия за счет одновременной записи или считывания информации.

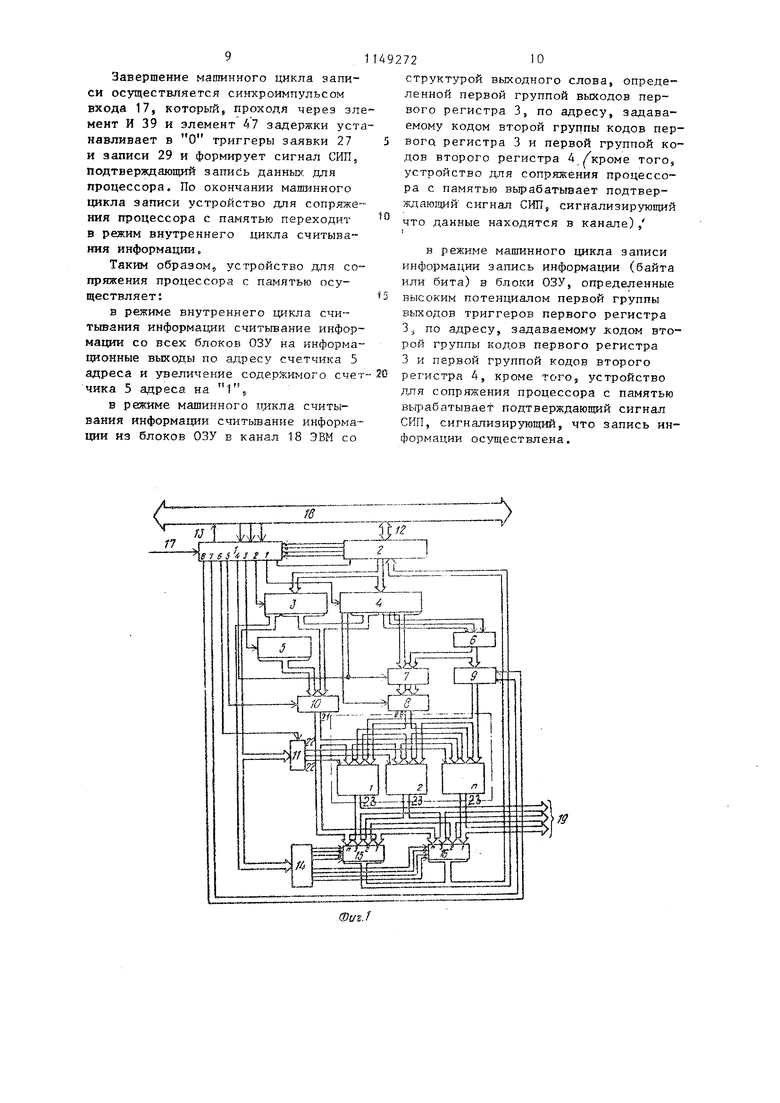

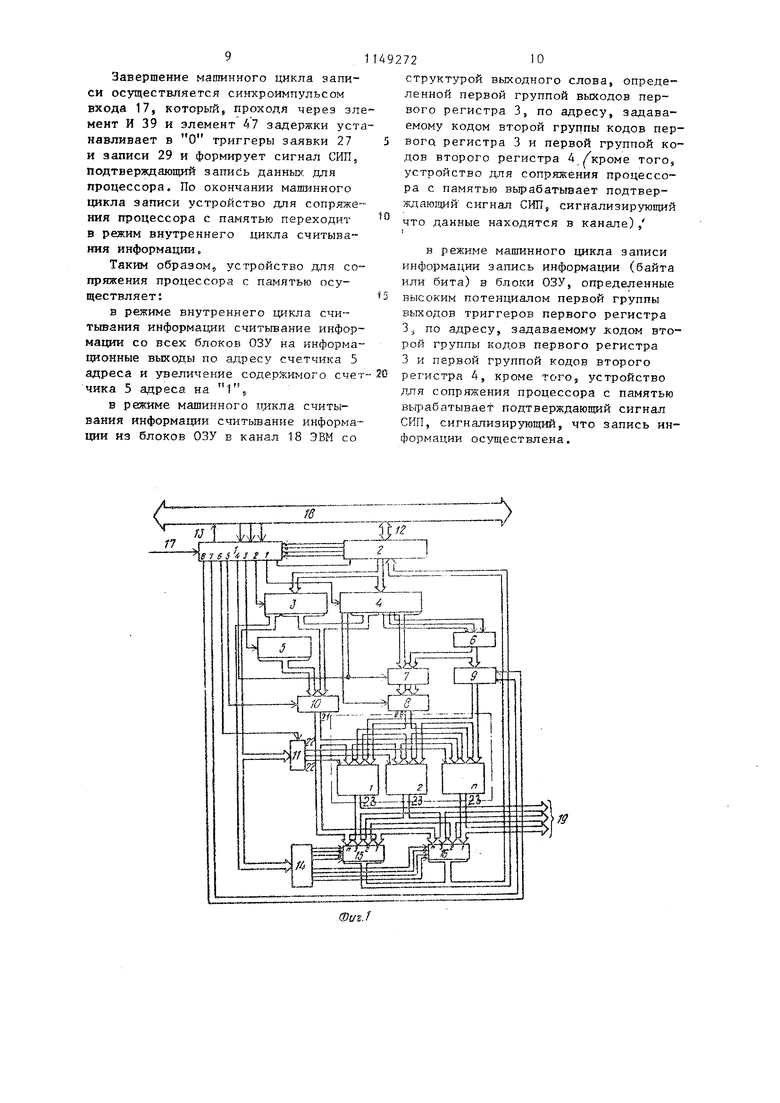

На фиг.1 представлена блок-схема устройства для сопряжения процессора с памятью. на фиг. 2 - блок-схема блока управления и синхронизации.

Устройство для сопряжения процессора с памятью содержит блок 1 управления и синхронизации, группу приемопередатчиков 2, первый и второй регистры 3 и 4, счетчик 5 адреса, дешифратор 6, первый, второй, третий, четвертый и пятый коммутаторы 7-11, группу входов - выходов 12, выход 13 подтверждения приема - выдачи, второй дешифратор 14, шестой и седьмой ком3

мутаторы 15 и 16, вход 17 синхроимпульсов, входы - выходы канала 18, выходы 19 разрешения, информационные 20, адресные 21, записи - считывания 22 входы и информационный вход 23.

Блок 1 управления и синхронизации содержит установочные входы 24 и 25 триггера выборки 26, заявки 27, синхронизации 28 и записи 29, дешифратор 30 адреса, элементы НЕ 31 и 32, первый и второй элементы И 33 и 34, элемент ИЛИ-НЕ 35, элемент НЕ 36, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И 37-43, элементы НЕ 44, восьмой и девятый элементы И 45 и 46, первый и второй элементы 47 и 48 задержки, элемент НЕ 49, группу входов 50 блока управления и синхронизации (входы адресации) группу входов - выходов 51, первый и второй входы 52 и 53, первый - восьмой выходы 54-61.

Работа устройства для сопряжения процессора с памятью осуществляется в следующих режимах:

внутреннего цикла считывания информации из всех блоков ОЗУ одновременно/

машинного цикла записи информации в блоки ОЗУ заданные первой группой кодов первого регистра 3J

машинного цикла считывания информации из блоков ОЗУ, определенных блоком 14 (блок 14 преобразует входной двоичный код в две группы управляющих сигналов).

Б исходном состоянии триггера выборки 26, заявки 27 и записи 29 блока 1 управления и синхронизации установлены в О, в первом и втором регистрах 3 и 4 хранится информация предшествующей операции, в счетчике 5 адреса - двоичный код адреса.

В режиме внутреннего цикла считывания информации, т.е. когда триггер 28 синхронизации блока И управления и синхронизации находится в нулевом состоянии, синхронизирующий импульс, поступакядий по входу 17 через блок 1 управления и синхронизации, поступает на вход счетчика 5 адреса и увеличивает содержимое счетчика 5 на 1, а проходя через элемент И 46 блока 1 управления и синхронизации, поступает на второй управляюидагй вход коммутатора 9, формируя тем самым на выходах коммутатора 9 импульсы разрешения по

92724

всем ячейкам блоков ОЗУ. При этом потенциал низкого уровня единичного выхода триггера 28 синхронизации блока 1 управления и синхронизации 5 формирует на пятом выходе блока 1 управления и синхронизагу и управляющий сигнал низкого уровня, который разрешает передачу информации на выходы коммутатора 10 с вторых информационных входов, т.е. с выходов счетчика 3 адреса, а через элемент И 41 блока 1 управления и синхронизации формирует управляющий сигнал низкого уровня на шестом выходе блока 1

5 управления и синхронизации, который формирует на выходах коммутатора 11 низкие потенциалы считьтания на всех ячейках ОЗУ. Таким образом, все . ячейки ОЗУ устанавливаются в состояние считьгоания по адресу счетчика 5 адреса. Импульсом разрешения с выходов коммутатора 9 осуществляется считывание информации со всех блоков ОЗУ.

В режимах машинного цикла, т.е. когда по каналу 18 от процессора в устройство для сопряжения процессора с памятью поступает адресная

0 -часть, банк ОЗУ, который совпадает с адресом устройства для сопряжения процессора с памятью, то синхронизирующий сигнал процессора СИЛ произведет установку триггере 26 выборки

блока 1 управления и синхронизации в единичное состояние и запись адресной части через приемопередатчики 2 в первый регистр 3. Низкий потенциал нулевого выхода триггера 26 выборки разрешает прием из канала сигналов КВвод или КВывод. Если по окончании адресной части обращения к каналу процессор вырабатывает сигнал КВвод, то этим сигналом в блоке 1 управления и синхронизации осуществляется установка триггера 27 заявки в единичное состояние. Триггер 29 записи блока t управления и синхронизации остается в исходном нулевом состоянии. Синхронизирующий импульс, поступающий по входу 17, переписьгоает содержимое , триггера 27 заявки в триггер 28 синхронизации, т.е. устанавливает его

5 в единичное состояние, тем самым переводит устройство для сопряжения процессора с памятью в режим машинного цикла считывания информации. Потенциал высокого уровня единич ного выхода триггера 28 синхронизации по пятому выходу блока 1 управления и синхронизации поступает на управляющий вход коммутатора 10 и разрешает передачу информации на вы ходы коммутатора 10 с первых информационных входов, т.е. с выходов первого и второго регистров 3 и 4, формирует на выходе элемента И 41 управляющий сигнал низкого уровня шестого выхода блока 1 управления и синхронизации5 который формирует на выходах коммутатора 11 низкие по тенциалы считывания на всех ячейках ОЗУ, а проходя через элемент И 43 и элемент НЕ 44, разрешает прохожде нию синхроимпульсу через элемент И 46 по восьмому выходу блока 1 управления и синхронизации. Синхроимпульс, поступающий по входу 17 че рез блок 1 управления и синхронизации по восьмому выходу, поступает на второй управляющий вход коммутатора 9, формируя тем самым на выходах коммутатора 9 импульсы разрешения по всем ячейкам ОЗУ. Таким образом, все ячейки ОЗУ устанавлива ются в состояние считывания информа ции по адресу, задаваемому кодом второй группы кодов первого регистр 3 и первой группой кодов второго регистра 4, Импульсами разрешения выходов коммутатора 9 осуществляется считывание информации с блоков ОЗУ на входы приемопередатчиков 2 через-коммутаторы 15 и 16,. управляю щие сигналы на которых заданы вторым дешифратором 14 с выходов перво группы кодов первого регистра 3. Высокие потенциалы единичного вы хода триггера 28 синхронизации и нулевого выхода триггера 29 записи формируют на первом выходе блока 1 управления и синхронизации разрешающий потенциал открывания приемопер датчиков 2, а синхроимпульс входа 17, поступивший через элемент И 39j через элемент 47 задержки осуществл ет установку в О триггеров заявки 27 и записи 29 и формирует подтверждающий сигнал СИП, который подается по каналу 18 в процессор, сигнализируя, что данные находятся в канале. По окончании машинного цикла считывания устройство для сопряжения процессора с памятью переходит в режим внутреннего цикла считывания информации, Если по окончании адресной части обращения к каналу процессор вьфабатывает сигнал КВывод, то этим сигналом в блоке 1 управления и синхронизации производится установка 1 триггеров заявки 27 и записи 29 и формирование импульса по второму выходу блока 1 управления и синхронизации, который осуществляет запись во второй регистр 4 информационной части канала, поступающей по каналу 18 от процессора через приемопередатчики 2. Синхронизирующий импульс, поступающий по входу 17, переписывает содержимое триггера 27 заявки в триггер 28 синхронизации, т.е. устанавливает его в единичное состояние, тем самым переводит устройство для сопряжения ;роцессора с памятью в режим машинного цикла записи информации. Триггер 29 записи блока 1 управления и синхронизации находится в единичном состоянии. Высокий потенциал единичного выхода триггера 28 синхронизации по пятому выходу блока 1 управления и синхронизации поступает на управляювщй вход коммутатора 10 и разрешает передачу информации на выходы коммута-т )ра 10 с первых информационных входе:н, т.е. с выходов первого и второго регистров 3 и 4, совместно с высоким потенциалом единичного выхода триггера 29 записи формирует на выходе элемента И 41 управляющий сигнал шестого выхода блока 1 управления и синхронизации, который разрешает передачу информации на выходы коммутатора 11 с первой,группы выходов первого регистра 3, т.е. формирует на выходах коммутатора 11 высокие потенциалы записи и низкие потенциалы считывания в соответствии с состоянием первой группы выходов триггеров первого регистра 3. Дальнейшая работа устройства для сопряжения процессора с памятью определена значениями старших разрядов информационной части второго регистра 4.( Если во второй старший разряд второго регистра 4 записано нулевое значение, то низкий потенциал с выхода триггера этого разряда разрейает передачу информации на выходы коммутатора 7 с вторых информационных входов, т.е. с выходов второй

группы вьгходов второго регистра 4, и через элемент И 43 и инвертор 44 разрешает прохождение синхроимпульса через элемент И 46 по восьмому выходу блока 1 управления и синхронизации, который поступает на второй управляющий вход коммутатора 9, формируя тем самым на выходах коммутатора 9 импульсы разрешения по всем ячейкам ОЗУ. Если в старшем разряде второго регистра 4 записано нулевое значение, то низкий потенциал выхода триггера этого разряда разрешает передачу информации на выходы коммутатора 8 прямого кода выходов коммутатора 7, в противном случав на выходы коммутатора 8 передаются инверсные коды выходов коммутатора 7 Таким образом, ячейки ОЗУ устанавливаются в состояние записи и считьшания информации, определяемое соответствующими состояниями первой группы выходов триггеров первого регистра 3, по адресу, задаваемому кодом второй группы кодов первого регистра 3 и первой группой кодов второго регистра 4. На всех информационных входах блоков ОЗУ присутствует прямой или инверсный код второй группы выходов второго регистра 4. Импульсами разрешения выходов коммутатора 9 осуществляется запись информации в блоки ОЗУ и считывание информации из блоков ОЗУ в соответствии с состоянием записи (считьшания) блока ОЗУ. Так как триггер 29 записи находится в единичном состоянии, то считываемая информация из блоков ОЗУ через коммутаторы 15 и 16 и приемопередатчики 2 в канал 18 ЭВМ не поступает. Таким образом, устройство для сопряжения процессора с памятью в данном случае осуществляет запись информации в блоки ОЗУ, определенные высоким потенциалом первой группы выходов, триггеров первого регистра 3. Запись информации в блоки ОЗУ производится в один выбранный блок ОЗУ или в ряд выбранных блоков ОЗУ одновременно.

Если во второй старший разряд второго регистра 4 записано единичное значение, то высокий потенциал выхода триггера этого разряда разрешает передачу информации на выход коммутатора 7 с первых информационных входов, т.е. с выходов дешифратора 6, входной код которого задан

тремя старшими разрядами второй группы выходов второго регистра 4, и через элемент И 43 разрешает прохождение синхроимпульса через элемент И 45 по седьмому выходу блока 1 управления и синхронизации, который поступает на первый управляющий вход коммутатора 9, формируя на выходах коммутатора 9 импульс разрешения на одном его выходе в соответствии с потенциалами входной информации (т.е. с выходами дешифратора 6), на остальных выходах коммутатора 9 присутствует потенциал низкого уровня.

Если в старшем разряде второго регистра 4 записано нулевое значение, то низкий потенциал выхода триггера этого разряда разрешает передачу информации на выходы коммутатора 8 прямого кода выходов коммутатора 7, в противном случае на выходы коммутатора 8 передаются инверсные коды выходов коммутатора 7. Таким образом ячейки ОЗУ устанавливаются в состояние записи и считьшания информации, определяемое соответствующими состояниями первой группы выходов триггеров первого регистра 3, по адресу, задаваемому кодом второй группы кодов первого регистра 3 и первой группой кодов второго регистра 4. На всех информационных входах: блоков ОЗУ присутствует прямой или инверсный код выходов деншфратора 6. Импульсом разрешения выхода коммутатора 9, который вырабатывается в соответствии с уровнем высокого потенциала выхода дешифратора 6, осуществляется запись информации (запись бита 1 или О) в блоки ОЗУ и считывание информации из блоков ОЗУ в соответствии с состояинем записи (считывания) блока ОЗУ. Так как триггер 29 записи находится в единичном состоянии, то считываемая информация из блоков ОЗУ через коммутаторы 15 и 16 и приемопередатчики 2 в канал 18 ЭВМ не поступает. Таким образом, устройство для сопряжения процессора с памятью в данном случае осуществляет запись бита 1 яли О в блоки ОЗУ, определенные высоким потенциало первой группы выходов триггеров первого регистра 3. Запись бита в блоки ОЗУ производится в -один шлбранный блок ОЗУ или в ряд выбранных блоков ОЗУ одновременно.

9

Завершение машинного цикла запи си осуществляется синхроимпульсом входа 17, который, проходя через элмент И 39 и элемент kl задержки устнавливает в О триггеры заявки 27 и записи 29 и формирует сигнал СИП;, подтверждающий запись данных. ,цля процессора. По окончании машинного цикла записи устройство для сопряжения процессора с памятью переходит в режим внутреннего цикла считывания информации„

Таким образоНф устройство для сопряжения процессора с памятью осуществляет;

в режиме внутреннего цикла считьгоания информации считывание информации со всех блоков ОЗУ на информационные выходы по адресу счетчика 5 адреса и увеличение содержимого счетчика 5 адреса на Г%

в режиме машинного тщкла считывания информации считьгоание информации из блоков ОЗУ в канал 18 ЭВМ со

14927210

структурой выходного слова, определенной первой группой выходов первого регистра 3, по адресу, задаваемому кодом второй группы кодов пер3 вогц регистра 3 и первой группой кодов второго регистра 4 /кроме того, устройство для сопряжения процессора с памятью вырабатывает подтверждающий сигнал CHIIj сигнализирующий что данные находятся в канале) /

в режиме машинного цикла записи информации запись информации (байта или бита) в блоки ОЗУ, определенные высоким потенциалом первой группы выходов триггеров первого регистра За по адресу, задаваемому кодом второй группь кодов первого регистра 3 и первой группой кодов второго регистра 4, кроме того, устройство для сопряжения процессора с памятью вырабатывает подтверждающий сигнал СИП, сигнализирующий, что запись информации осуществлена.

СЧ|

| Устройство для связи запоминающего и арифметического устройств | 1976 |

|

SU643878A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-07—Публикация

1983-07-07—Подача