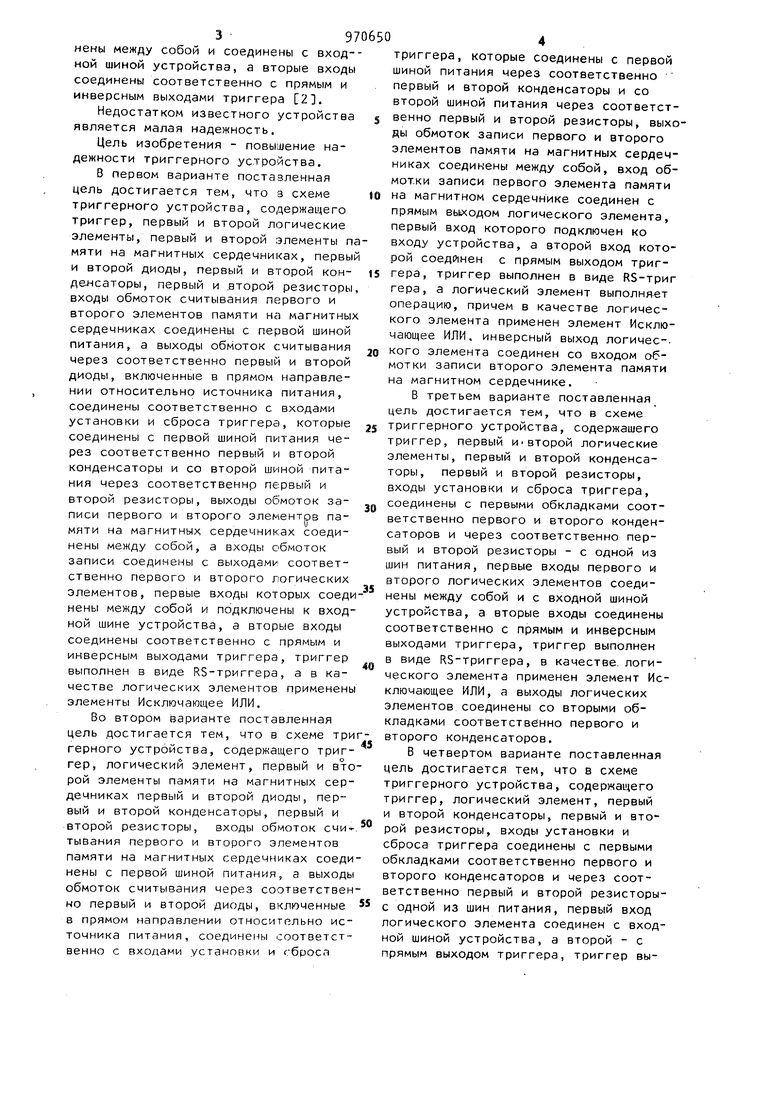

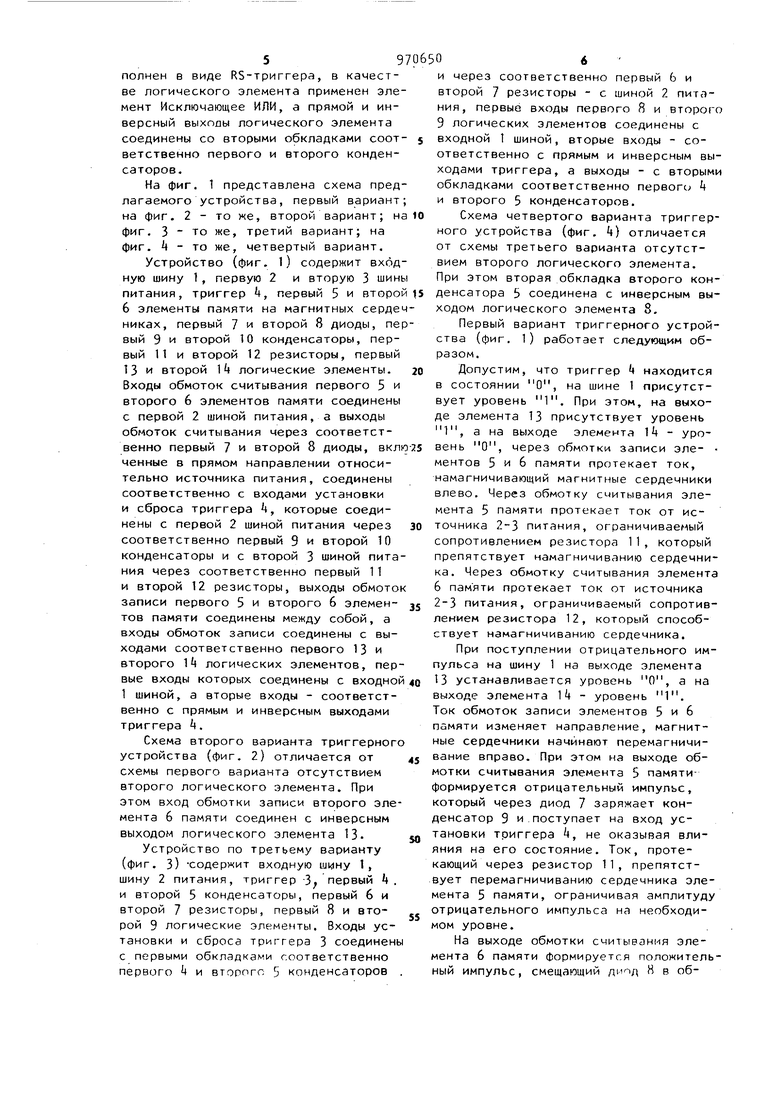

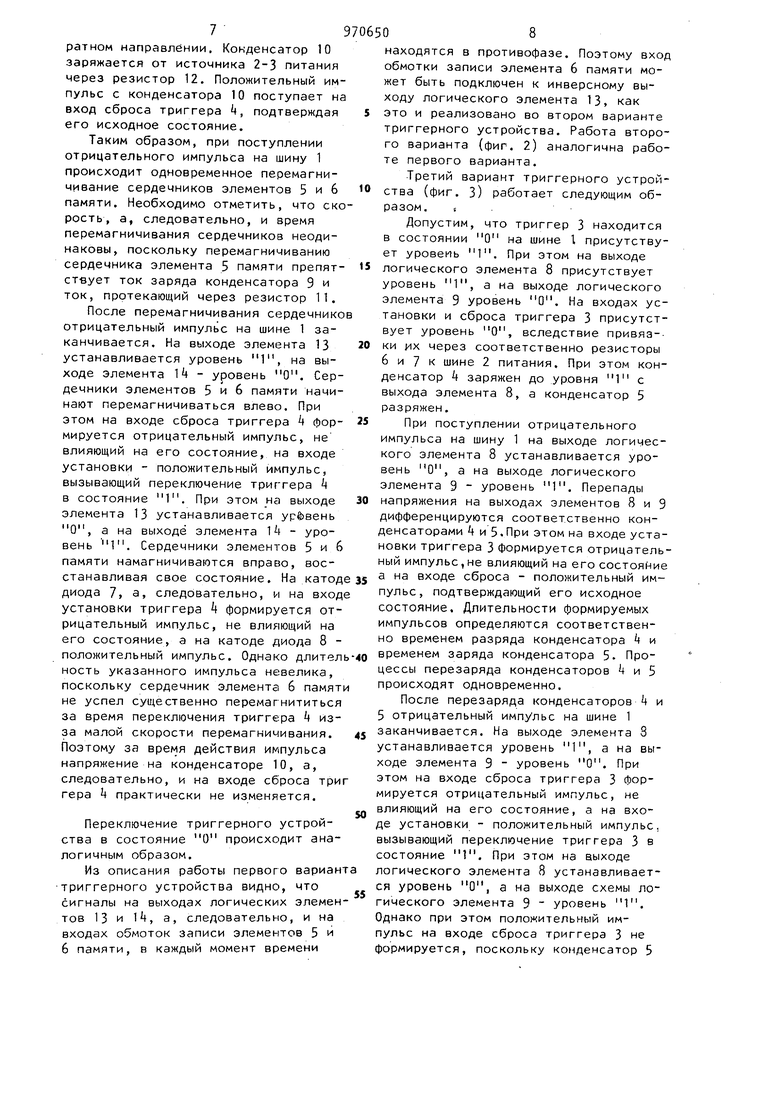

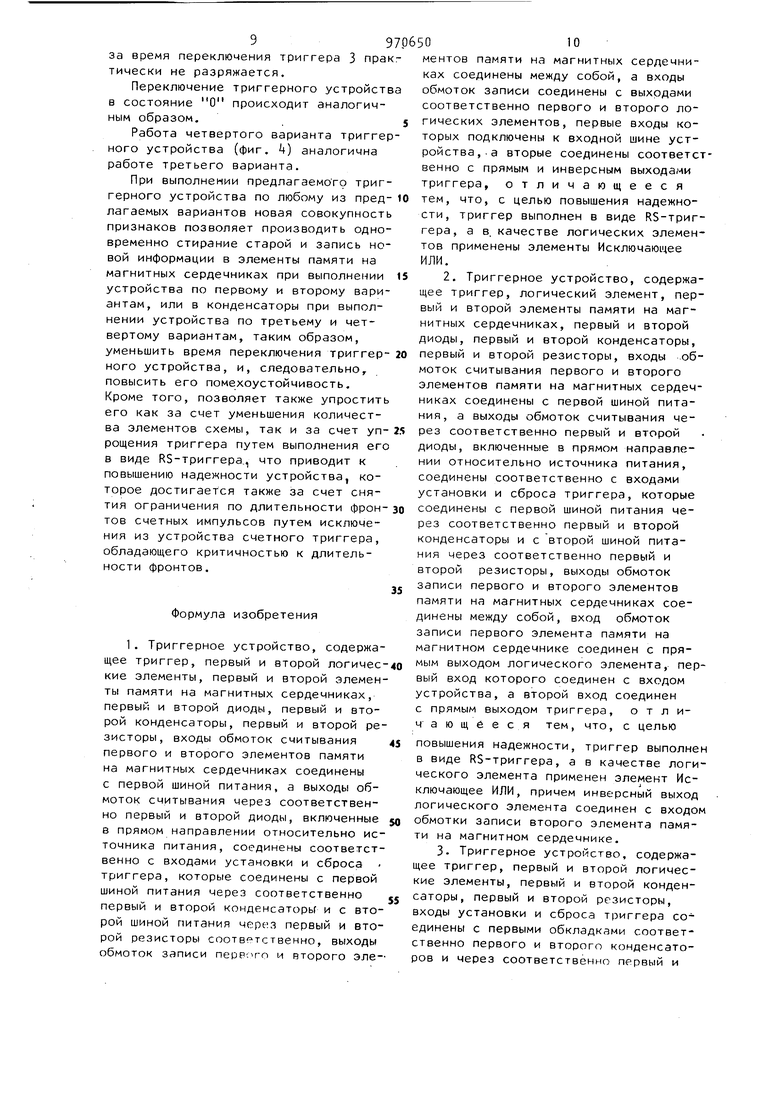

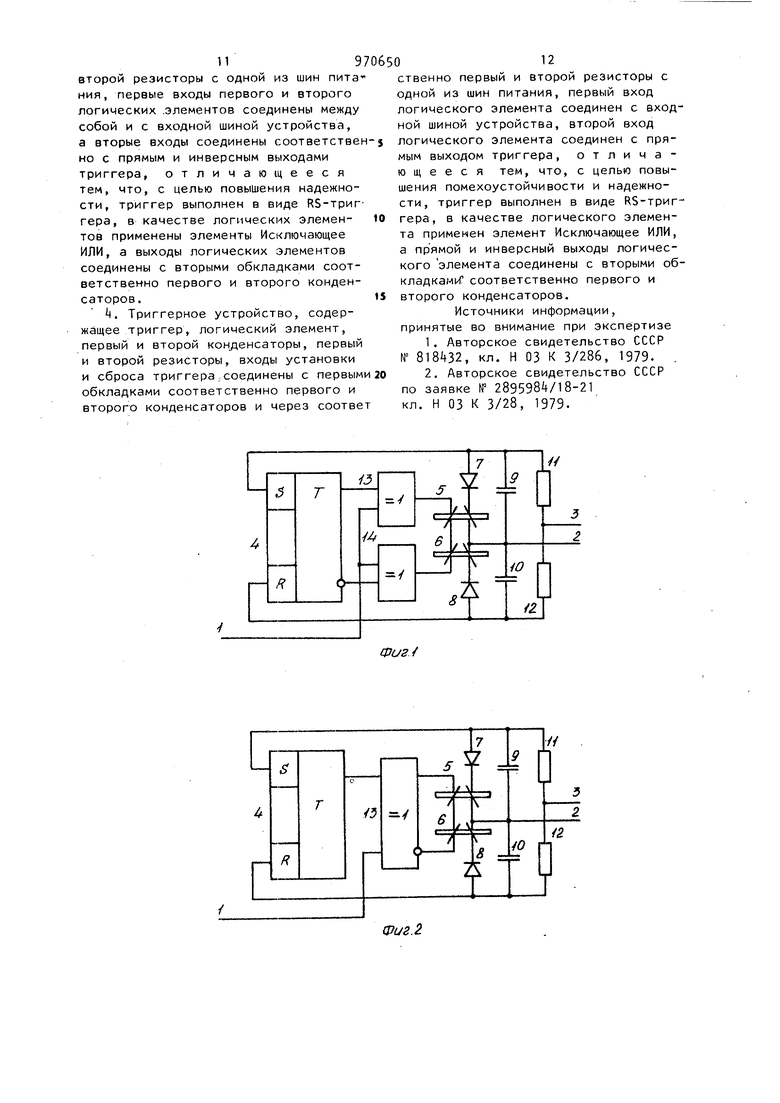

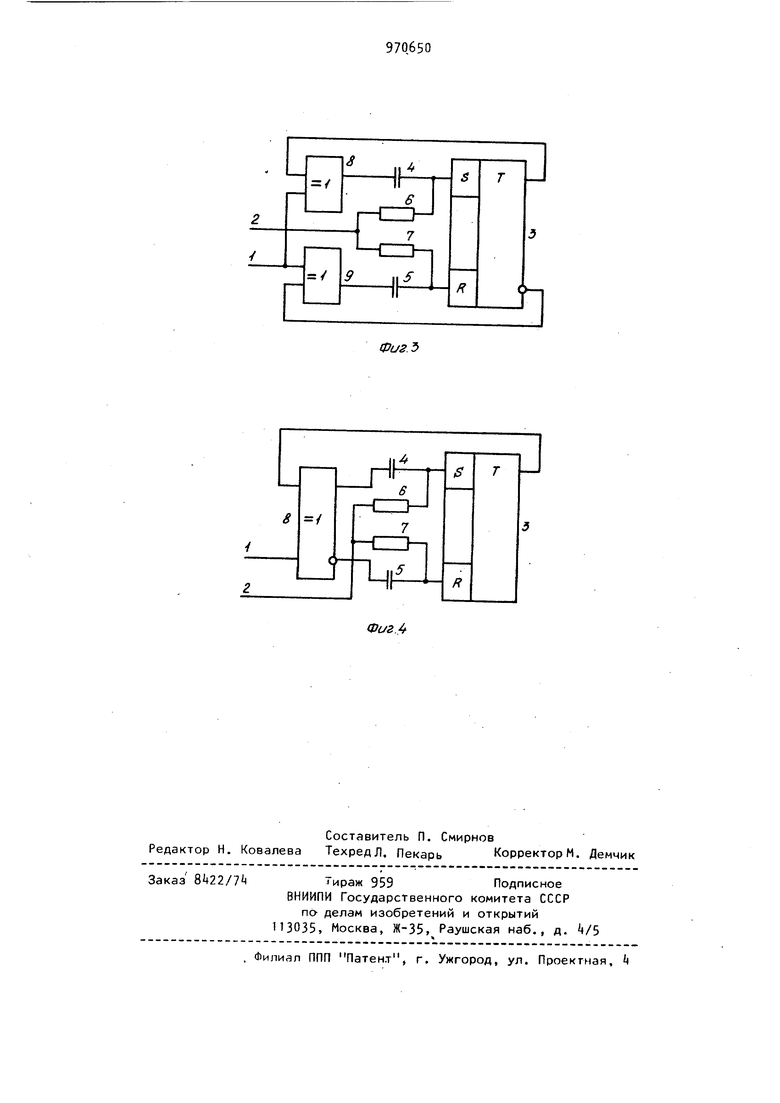

Изобретение относится к импульсяой технике и может быть использовано в устройствах вычислительной техники и систем управления. Известен двухустойчивый элемент, содержащий триггер, конденсаторный элемент.памяти и два элемента совпаде ния, первые входы которых соединены с управляющей шиной, выходы соответственно соединены с входами сброса и установки триггера, тактовый вход которого соединен с информационной шиной, прямой и инверсный выходы тригге ра соответственно подключены к входам конденсаторного элемента памяти, выхо ды которого соединены с вторыми входами соответствующих элементов совпадения 1 . Недостатками данного устройства яв ляются сложность и недостаточная помехоустойчивость. Известно также триггерное устройство, содержащее триггер, первый и второй логические элементы, первый и второй элементы памяти на магнитных сердечниках, первый и второй диоды, первый и второй конденсаторы, первый и второй резисторы, входы обмоток считывания первого и второго элементов памяти на магнитных сердечниках соединены с первой шиной питания, а выходы обмоток считывания через соответственно первый и -второй диоды, включенные в прямом направлении относительно источника питания, соединены соответственно с входами установки и сброса триггера, которые соединены с первой шиной питания через соответственно первый и второй конденсаторы и со второй шиной питания через соответственно первый и второй резисторы, выходы обмоток записи первого и второго элементов памяти на магнитных сердечниках соединены между собой, а входы обмоток записи соединены с выходами соответственно первого и второго логических элементов, первые входы которых объеди3 97 йены между собой и соединены с вход-ной шиной устройства, а вторые входы соединены соответственно с прямым и инверсным выходами триггера 21. Недостатком известного устройства является малая надежность. Цель изобретения - повышение надежности триггерного устройства. В первом варианте поставленная цель достигается тем, что з схеме триггерного устройства, содержаьцего триггер, первый и второй логические элементы, первый и второй элементы па мяти на магнитных сердечниках, первый и второй диоды, первый и второй конденсаторы, первый и .второй резисторы входы обмоток считывания первого и второго элементов памяти на магнитных сердечниках соединены с первой шиной питания, а выходы обмоток считывания через соответственно первый и второй диоды, включенные в прямом направлении относительно источника питания, соединены соответственно с входами установки и сброса триггера, которые соединены с первой шиной питания через соответственно первый и второй конденсаторы и со второй шиной питания через соответственнр первый и второй резисторы, выходы обмоток записи первого и второго элементов памяти на магнитных сердечниках соединены между собой, а входы обмоток записи соединены с выходами соответственно первого и второго логических элементов, первые входы которых соеди нены между собой и подключены к входной шине устройства, а вторые входы соединены соответственно с прямым и инверсным выходами триггера, триггер выполнен в виде RS-триггера, а в качестве логических элементов применены элементы Исключающее ИЛИ. Во втором варианте поставленная цель достигается тем, что в схеме три герного устройства, содержащего триггер, логический элемент, первый и вто рой элементы памяти на магнитных сердечниках первый и второй диоды, первый и второй конденсаторы, первый и второй резисторы, входы обмоток счи тывания первого и второго элементов памяти на магнитных сердечниках соеди нены с первой шиной питания, а выходы обмоток считывания через соответствен но первый и второй диоды, включенные в прямом направлении относительно источника питания, соединены соответственно с входами установки и сброса триггера, которые соединены с первой шиной питания через соответственно первый и второй конденсаторы и со второй шиной питания через соответственно первый и второй резисторы, выходы обмоток записи первого и второго элементов памяти на магнитных сердечниках соединены между собой, вход обмотки записи первого элемента памяти на магнитном сердечнике соединен с прямым выходом логического элемента, первый вход которого подключен ко входу устройства, а второй вход которой соединен с прямым выходом триггера, триггер выполнен в виде RS-триг гера, а логический элемент выполняет операцию, причем в качестве логического элемента применен элемент Исключающее ИЛИ. инверсный выход логичес-. кого элемента соединен со входом обмотки записи второго элемента памяти на магнитном сердечнике. В третьем варианте поставленная цель достигается тем, что в схеме триггерного устройства, содержащего триггер, первый Ивторой логические элементы, первый и второй конденсаторы, первый и второй резисторы, входы установки и сброса триггера, соединены с первыми обкладками соответственно первого и второго конденсаторов и через соответственно первый и второй резисторы - с одной из шин питания, первые входы первого и второго логических элементов соединены между собой и с входной шиной устройства, а вторые входы соединены соответственно с прямым и инверсным выходами триггера, триггер выполнен в виде RS-триггера, в качестве, логического элемента применен элемент Исключающее ИЛИ, а выходы логических элементов соединены со вторыми обкладками соответственно первого и второго конденсаторов. В четвертом варианте поставленная цель достигается тем, что в схеме триггерного устройства, содержащего триггер, логический элемент, первый и второй конденсаторы, первый и второй резисторы, входы установки и сброса триггера соединены с первыми обкладками соответственно первого и второго конденсаторов и через соответственно первый и второй резисторыс одной из шин питания, первый вход логического элемента соединен с входной шиной устройства, а второй - с прямым выходом триггера, триггер выполней в виде RS-триггера, в качестве логического элемента применен эле мент Исключающее ИЛИ, а прямой и инверсный выходы логического элемента соединены со вторыми обкладками соот ветственно первого и второго конденсаторов. На фиг. t представлена схема пред лагаемого устройства, первый вариант на фиг. 2 - то же, второй вариант; н фиг. 3 то же, третий вариант; на фиг. - то же, четвертый вариант. Устройство (фиг. 1) содержит вход ную шину 1, первую 2 и вторую 3 шин питания, триггер t, первый 5 и второ 6 элементы памяти на магнитных серде никах, первый 7 и второй 8 диоды, пе вый 9 и второй 10 конденсаторы, первый 11 и второй 12 резисторы, первый 13 и второй 1 логические элементы. Входы обмоток считывания первого 5 и второго 6 элементов памяти соединены с первой 2 шиной питания, а выходы обмоток считывания через соответственно первый 7 и второй 8 диоды, вкл ченные в прямом направлении относительно источника питания, соединены соответственно с входами установки и сброса триггера k, которые соединены с первой 2 шиной питания через соответственно первый 9 и второй 10 конденсаторы и с второй 3 шиной пита ния через соответственно первый 11 и второй 12 резисторы, выходы обмото записи первого 5 и второго 6 элементов памяти соединены между собой, а входы обмоток записи соединены с выходами соответственно первого 13 и второго I логических элементов, пер вые входы которых соединены с входно 1 шиной, а вторые входы - соответственно с прямым и инверсным выходами триггера k, Схема второго варианта триггерног устройства (фиг. 2) отличается от схемы первого варианта отсутствием второго логического элемента. При этом вход обмотки записи второго эле мента 6 памяти соединен с инверсным выходом логического элемента 13. Устройство по третьему варианту (фиг. 3) -содержит входную шину 1, шину 2 питания, триггер -3, первый . и второй 5 конденсаторы, первый 6 и второй 7 резисторы, первый 8 и второй 9 логические элементы. Входы установки и сброса триггера 3 соединен с первыми обкладками соответственно первого k и второго 5 конденсаторов и через соответственно первый 6 и второй 7 резисторы - с шиной 2 питания, первые входы первого 8 и второго 9 логических элементов соединены с входной t шиной, вторые входы - соответственно с прямым и инверсным выходами триггера, а выходы - с вторыми обкладками соответственно первого k и второго 5 конденсаторов. Схема четвертого варианта триггерного устройства (фиг. Ц) отличается от схемы третьего варианта отсутствием второго логического элемента. При этом вторая обкладка второго конденсатора 5 соединена с инверсным выходом логического элемента 8. Первый вариант триггерного устройства (фиг. 1) работает следукмцим образом. Допустим, что триггер находится в состоянии О, на шине 1 присутствует уровень 1. При этом, на выходе элемента 13 присутствует уровень 1, а на выходе элемента 1 it - уровень О, через обмотки записи элементов 5 и 6 памяти протекает ток, намагничивающий магнитные сердечники влево. Через обмотку считывания элемента 5 памяти протекает ток от источника 2-3 питания, ограничиваемый сопротивлением резистора 11, который препятствует намагничиванию сердечника. Через обмотку считывания элемента 6 памяти протекает ток от источника 2-3 питания, ограничиваемый сопротивлением резистора 12, который способствует намагничиванию сердечника. При поступлении отрицательного импульса на шину 1 на выходе элемента 13 устанавливается уровень О, а на выходе элемента 1+ - уровень 1. Ток обмоток записи элементов 5 и 6 памяти изменяет направление, магнитные сердечники начинают перемагничивание вправо. При этом на выходе обмотки считывания элемента 5 памятиформируется отрицательный импульс, который через диод 7 заряжает конденсатор 9 и поступает на вход установки триггера k, не оказывая влияния на его состояние. Ток, протекающий через резистор 11, препятствует перемагничиванию сердечника элемента 5 памяти, ограничивая амплитуду отрицательного импульса на необходимом уровне. На выходе обмотки считыван11Я элемента 6 памяти формируется положительный импульс, смещающий диод Н в обратном направлении. Конденсатор 10 заряжается от источника 2-3 питания через резистор 12. Положительный импульс с конденсатора 10 поступает на вход сброса триггера 4, подтверждая его исходное состояние.

Таким образом, при поступлении отрицательного импульса на шину 1 происходит одновременное перемагничивание сердечников элементов 5 и 6 памяти. Необходимо отметить, что скорость, а, следовательно, и время перемагничивания сердечников неодинаковы, поскольку перемагничиванию сердечника элемента 5 памяти препятстеует ток заряда конденсатора 9 и ток, протекающий через резистор 11.

После перемагничивания сердечнико отрицательный импульс на шине 1 заканчивается. На выходе элемента 13 устанавливается уровень 1, на выходе элемента 14 - уровень О. Сердечники элементов 5 и 6 памяти начинают перемагничиваться влево. При этом на входе сброса триггера формируется отрицательный импульс, не влияющий на его состояние, на входе установки - положительный импульс, вызывающий переключение триггера Ц в состояние 1. При этом на выходе элемента 13 устанавливается урй)вень О, а на выходе элемента 1 t - уровень 1. Сердечники элементов 5 и 6 памяти намагничиваются вправо, восстанавливая свое состояние. На катод диода 7, а, следовательно, и на вход установки триггера k формируется отрицательный импульс, не влияющий на его состояние, а на катоде диода 8 положительный импульс. Однако длител ность указанного импульса невелика, поскольку сердечник элемента 6 памят не успел существенно перемагнититься за время переключения триггера 4 изза малой скорости перемагничивания. Поэтому за время действия импульса напряжение на конденсаторе 10, а, следовательно, и на входе сброса три гера практически не изменяется.

Переключение триггерного устройства в состояние О происходит аналогичным образом.

Из описания работы первого вариан триггерного устройства видно, что сигналы на выходах логических элементов 13 и , а, следовательно, и на входах обмоток записи элементов 5 и 6 памяти, в каждый момент времени

находятся в противофазе. Поэтому вход обмотки записи элемента 6 памяти может быть подключен к инверсному выходу логического элемента 13, как это и реализовано во втором варианте триггерного устройства. Работа второго варианта (фиг. 2) аналогична работе первого варианта.

Третий вариант триггерного устройства (фиг. 3) работает следующим образом, t

Допустим, что триггер 3 находится в состоянии О на шине 1 присутствует уровень 1. При этом на выходе логического элемента 8 присутствует уровень 1, а на выходе логического элемента 9 уровень О. На входах установки и сброса триггера 3 присутствует уровень О, вследствие привяз-ки через соответственно резисторы 6 и 7 к шине 2 питания. При этом конденсатор 4 заряжен до уровня 1 с выхода элемента 8, а конденсатор 5 разряжен.

При поступлении отрицательного импульса на шину 1 на выходе логического элемента 8 устанавливается уровень О, а на выходе логического элемента 9 - уровень 1. Перепады напряжения на выходах элементов 8 и 9 дифференцируются соответственно конденсаторами k и 5.При этом на входе установки триггера 3 формируется отрицательный импульс,не влияющий на его состояние а на входе сброса - положительный импульс, подтверждающий его исходное состояние. Длительности формируемых импульсов определяются соответственно временем разряда конденсатора и временем заряда конденсатора 5. Процессы перезаряда конденсаторов и 5 происходят одновременно.

После перезаряда конденсаторов t и 5 отрицательный импульс на шине 1 заканчивается. На выходе элемента 8 устанавливается уровень 1, а на выходе элемента 9 - уровень О. При этом на входе сброса триггера 3 формируется отрицательный импульс, не влияющий на его состояние, а на входе установки - положительный импульс, вызывающий переключение триггера 3 в состояние 1. При этом на выходе логического элемента 8 устанавливается уровень О, а на выходе схемы логического элемента 9 уровень 1. Однако при этом положительный импульс на входе сброса триггера 3 не формируется, поскольку конденсатор 5 99 за время переключения триггера 3 прак тически не разряжается. Переключение триггерного устройств в состояние О происходит аналогичным образом, Работа четвертого варианта триггер ного устройства (фиг. k} аналогична работе третьего варианта. При выполнении предлагаемото триггерного устройства по любому из предлагаемых вариантов новая совокупность признаков позволяет производить одновременно стирание старой и запись новой информации в элементы памяти на магнитных сердечниках при выполнении устройства по первому и второму вариантам, или в конденсаторы при выполнении устройства по третьему и четвертому вариантам, таким образом, уменьшить время переключения триггерного устройства, и, следовательно, повысить его помехоустойчивость. Кроме того, позволяет также упростить его как за счет уменьшения количества элементов схемы, так и за счет упрощения триггера путем выполнения его в виде RS-триггера,, что приводит к повышению надежности устройства, которое достигается также за счет снятия ограничения по длительности фронтов счетных импульсов путем исключения из устройства счетного триггера, обладающего критичностью к длительности фронтов. Формула изобретения 1. Триггерное устройство, содержащее триггер, первый и второй логичес кие элементы, первый и второй элемен ты памяти на магнитных сердечниках, первый и второй диоды, первый и второй конденсаторы, первый и второй ре зисторы, входы обмоток считывания первого и второго элементов памяти на магнитных сердечниках соединены с первой шиной питания, а выходы обмоток считывания через соответственно первый и второй диоды, включенные в прямом направлении относительно ис точника питания, соединены соответст венно с входами установки и сброса триггера, которые соединены с первой шиной питания через соответственно первый и второй конденсаторы и с второй шиной питания через первый и второй резисторы соответственно, выходы обмоток записи первого и второго эле0памяти на магнитных сердечниментовках соединены между собой, а входы обмоток записи соединены с выходами соответственно первого и второго логических элементов, первые входы которых подключены к входной шине устройства,- а вторые соединены соответственно с прямым и инверсным выходами триггера, отличающееся тем, что, с целью повышения надежности, триггер выполнен в виде RS-триггера, а в. качестве логических элементов применены элементы Исключающее ИЛИ. 2.Триггерное устройство, содержащее триггер, логический элемент, первый и второй элементы памяти на ма1- нитных сердечниках, первый и второй диоды, первый и второй конденсаторы, первый и второй резисторы, входы обмоток считывания первого и второго элементов памяти на магнитных сердечниках соединены с первой шиной питания, а выходы обмоток считывания через соответственно первый и второй диоды, включенные в прямом направлении относительно источника питания, соединены соответственно с входами установки и сброса триггера, которые соединены с первой шиной питания через соответственно первый и второй конденсаторы и с второй шиной питания через соответственно первый и второй резисторы, выходы обмоток записи первого и второго элементов памяти на магнитных сердечниках соединены между собой, вход обмоток записи первого элемента памяти на магнитном сердечнике соединен с прямым выходом логического элемента, первый вход которого соединен с входом устройства, а второй вход соединен с прямым выходом триггера, отличающееся тем, что, с целью повышения надежности, триггер выполнен в виде RS-триггера, а в качестве логического элемента применен элемент Исключающее ИЛИ, причем инверсный выход логического элемента соединен с входом обмотки записи второго элемента памяти на магнитном сердечнике, 3.Триггерное устройство, содержащее триггер, первый и второй логические элементы, первый и второй конденсаторы, первый и второй резисторы, входы установки и сброса триггера соединены с первыми обкладками соответственно первого и второго конденсаторов и через соответственно первый и

второй резисторы с одной из шин питания, первые входы первого и второго логических .элементов соединены между собой и с входной шиной устройства, а вторые входы соединены соответствен но с прямым и инверсным выходами триггера, отличающееся тем, что, с целью повышения надежности, триггер выполнен в виде RS-триГ гера, в качестве логических элементов применены элементы Исключающее ИЛИ, а выходы логических элементов соединены с вторыми обкладками соответственно первого и второго конденсаторов.

i. Триггерное устройство, содержащее триггер, логический элемент, первый и второй конденсаторы, первый и второй резисторы, входы установки и сброса триггера .соединены с первыми обкладками соответственно первого и второго конденсаторов и через соответ

ственно первый и второй резисторы с одной из шин питания, первый вход логического элемента соединен с входной шиной устройства, второй вход логического элемента соединен с прямым выходом триггера, отличающееся тем, что, с целью повышения помехоустойчивости и надежности, триггер выполнен в виде RS-триггера, в качестве логического элемента применен элемент Исключающее ИЛИ, а прямой и инверсный выходы логического элемента соединены с вторыми обкладкам1/Г соответственно первого и второго конденсаторов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР N , кл. Н 03 К 3/286, 1979.

2.Авторское свидетельство СССР по заявке № 2895984/18-21

кл. Н 03 К 3/28, 1979.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерное устройство (его варианты) | 1982 |

|

SU1019594A1 |

| Триггерное устройство | 1979 |

|

SU813709A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1980 |

|

SU852131A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2001 |

|

RU2207716C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250556C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1983 |

|

SU1145890A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2248662C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250554C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250555C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2248663C1 |

т

/ л

3

МИШ

2

У

/2

o

&

I7

1

Авторы

Даты

1982-10-30—Публикация

1981-04-03—Подача