Изобретение относится к импульсной технике и может быть использовано при разработке запоминающих и счетных устройств автоматики и вычислительной техники.

Известен триггер, содержащий двухустойчивый элемент, инвертор, четыре элемента совпадения, два элемента памяти на магнитных сердечниках с прямоугольной петлей гистерезиса и обмотками записи и считывания, два диода, четыре резистора [1]

Указанный триггер имеет следующие недостатки.

Во-первых, поскольку энергия, затрачиваемая элементом памяти на восстановление состояния двухустойчивого элемента после его сбоя, не восстанавливается, то триггер не устойчив к воздействию многократных помех.

Во-вторых, наличие дополнительных резисторов на входах элементов совпадения, связанных с выходами обмоток считывания, вызывает уменьшение сопротивления нагрузки для полезного сигнала считывания и приводит к необходимости увеличения его мощности, а следовательно, к увеличению потребления триггера.

В-третьих, необходимость сохранения управляющего сигнала на входе триггера после переключения двухустойчивого элемента на время записи информации в элементы памяти делает невозможным построение на его основе целого ряда схем счетчиков импульсов (счетчиков импульсов в отраженном двоичном коде, синхронных счетчиков импульсов и пр.) без принятия специальных мер, вызывающих усложнение схемы.

Известно триггерное устройство, содержащее триггер, первый и второй элементы совпадения, первый и второй элементы памяти на магнитных сердечниках, первый и второй диоды, первый, второй, третий и четвертый резисторы, первый и второй конденсаторы, тактовый вход триггера соединен с входной шиной и первыми входами первого и второго элементов совпадения, выходы которых соединены соответственно с входами сброса и установки триггера, прямой и инверсный выходы которого соединены с входами обмоток записи соответственно первого и второго элементов памяти на магнитных сердечниках, первый и второй резисторы соединены с вторыми входами соответственно первого и второго совпадения, а третий и четвертый резисторы соединены с шиной питания, входы обмоток считывания первого и второго элементов памяти на магнитных сердечниках соединены с общей шиной, шина питания соединена с первым и вторым резисторами, вторые входы первого и второго элементов совпадения соединены с общей шиной соответственно через первый и второй конденсаторы, третий и четвертый резисторы соединены с входами обмоток записи соответственно первого и второго элементов памяти на магнитных сердечниках, выходы обмоток считывания первого и второго элементов памяти на магнитных сердечниках соединены с катодами соответственно первого и второго диодов, аноды которых соединены с вторыми входами соответственно первого и второго элементов совпадения [2]

Недостатком указанного триггерного устройства является необходимость сохранения управляющего сигнала на его входе после переключения триггера на время записи новой информации в элементы памяти на магнитных сердечниках, что делает невозможным построение на его основе целого ряда схем счетчиков импульсов (счетчиков импульсов в отраженном двоичном коде, синхронных счетчиков импульсов и т.д.) без принятия специальных мер, вызывающих усложнение схемы, и сужает функциональные возможности.

Целью изобретения является расширение функциональных возможностей.

Поставленная цель достигается тем, что в триггерное устройство, содержащее триггер, первый и второй элементы памяти на магнитных сердечниках, первый и второй элементы совпадения, первый и второй диоды, первый и второй конденсаторы, первый, второй, третий и четвертый резисторы, тактовый вход триггера соединен с входной шиной, входы обмоток считывания первого и второго элементов памяти на магнитных сердечниках соединены с общей шиной, а выходы обмоток считывания соединены с катодами соответственно первого и второго диодов, аноды которых соединены с общей шиной через соответственно первый и второй конденсаторы, и с шиной питания через соответственно первый и второй резисторы, входы обмоток первого и второго элементов памяти на магнитных сердечниках соединены с шиной питания через соответственно третий и четвертый резисторы, а выходы обмоток записи соединены между собой, введены первый и второй инверторы, входная шина устройства соединена через первый инвертор с первыми входами первого и второго элементов совпадения и через второй инвертор с выходами обмоток записи первого и второго элементов памяти на магнитных сердечниках, входы которых соединены с выходами соответственно первого и второго элементов совпадения, вторые входы которых соединены соответственно с прямым и инверсным выходами триггера, входы установки и сброса которого соединены с анодами соответственно первого и второго диодов.

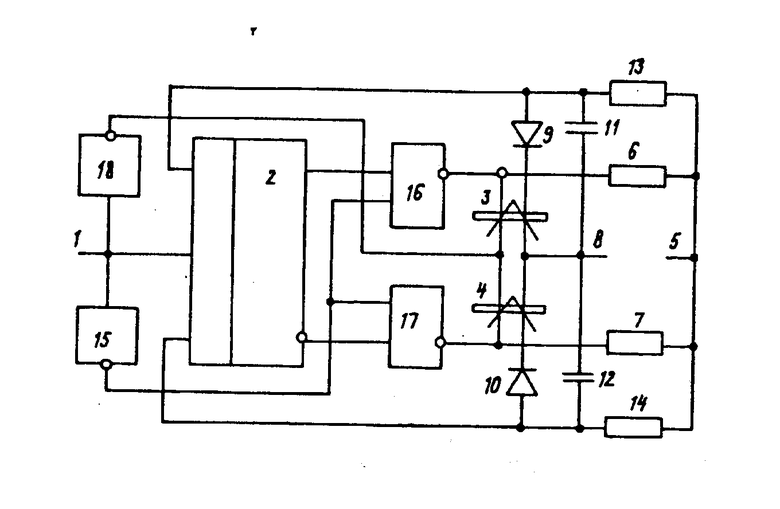

На чертеже представлена схема триггерного устройства.

На чертеже обозначено: входная шина 1, триггер 2, элементы памяти 3, 4 на магнитных сердечниках, шина 5 питания, резисторы 6, 7, общая шина 8, диоды 9, 10, конденсаторы 11, 12, резисторы 13, 14, инвертор 15, элементы 16, 17 совпадения, инвертор 18. Входная шина 1 соединена с тактовым входом триггера 2, входы обмоток записи элементов 3 и 4 памяти на магнитных сердечниках соединены с шиной 5 питания через соответственно резисторы 6 и 7, а выходы обмоток записи соединены между собой, входы обмоток считывания элементов 3 и 4 памяти соединены с общей шиной 8, а выходы указанных обмоток считывания соединены с катодами соответственно диодов 9 и 10, аноды которых соединены с общей шиной 8 через соответственно конденсаторы 11 и 12 и с шиной 5 питания через соответственно резисторы 13 и 14, входная шина 1 соединена через инвертор 15 с первыми входами элементов 16, 17 совпадения и через инвертор 18 с выходами обмоток записи элементов 3 и 4 памяти, входы которых соединены с выходами соответственно элементов 16 и 17 совпадения, вторые входы которых соединены соответственно с прямым и инверсным выходами триггера 2, входы установки и сброса которого соединения с анодами соответственно диодов 9 и 10.

Триггерное устройство работает следующим образом.

Допустим, что триггер 2 находится в состоянии логического "0", на шине 1 триггерного устройства присутствует уровень логического "0", при этом выходной транзистор инвертора 18 закрыт и не влияет на процессы, проходящие в схеме. На выходе инвертора 15 присутствует уровень логической "1". Выходной транзистор элемента 16 закрыт, а выходной транзистор элемента 17 открыт. Через резисторы 6 и 7 и выходной транзистор элемента 17 протекает ток от шины 5 питания к общей шине 8, при этом ток, протекающий через резистор 6, протекает через обмотку записи элементов памяти 3 и 4. Через обмотку считывания элемента 3 протекает ток, протекающий через резистор 13, через обмотку считывания элемента 4 протекает ток, протекающий через резистор 14. Магнитные сердечники элементов памяти намагничены влево. На входах сброса и установки триггера присутствует уровень логического "0".

При поступлении положительного импульса по шине 1 триггерного устройства открываются выходные транзисторы инвертора 15 и 18. Открывание выходного транзистора инвертора 15 вызывает закрывание выходных транзисторов элементов 16 и 17 совпадения. Токи, протекающие через резисторы 6 и 7, начинают протекать через открытый выходной резистор инвертора 18. При этом ток обмотки записи элемента памяти 4 изменяет направление и вызывает его перемагничивание вправо. На выходе обмотки считывания формируются импульс положительной полярности, смещающий диод 10 в обратном направлении.

Конденсатор 12 заряжается через резистор 14, на выходе сброса триггера 2 формируется импульс положительной полярности, подтверждающий его исходное состояние.

После перемагничивания сердечника элемента памяти 4 заканчивается положительный импульс на шине 1 триггерного устройства.

При этом переключается триггер 2, закрываются выходные транзисторы инверторов 15 и 18 и элемента 17 совпадения, открывается выходной транзистор элемента 16, замыкая цепь тока, протекающего через резисторы 6 и 7. При этом ток обмотки записи элемента памяти 3 изменяет направление и вызывает его перемагничивание вправо.

В процессе перемагничивания на выходе обмотки считывания формируется импульс отрицательной полярности, который не влияет на состояние триггера 2. Ток, протекающий через резистор 13, препятствует перемагничиванию, замедляя его и уменьшая амплитуду импульса. Переключение триггера в исходное состояние происходит аналогично.

При несанкционированном переключении триггера в состояние логической "1" выходной транзистор элемента 17 совпадения закрывается, а выходной транзистор элемента совпадения 16 открывается. Ток обмоток записи элементов памяти 3 и 4 изменяет направление и стремится перемагнитить сердечники вправо. На выходе обмотки считывания элемента памяти 4 формируется импульс положительной полярности, смещающий диод 10 в обратном направлении. Ток, протекающий через резистор 14, заряжая конденсатор 12, формирует импульс положительной полярности на входе сброса триггера 2, возвращающий триггер в исходное состояние.

Поскольку в процессе формирования импульса элемент 4 памяти, работает практически в режиме холостого хода, то сопротивление его обмотки записи довольно велико. В то же время происходит перемагничивание вправо и сердечника элемента 3 памяти. При этом на выходе обмотки считывания формируется импульс отрицательной полярности, диод 9 смещен в прямом направлении. Через обмотку считывания протекает ток, прошедший через резистор 13, и ток заряда конденсатора 11, препятствующие перемагничиванию сердечника. Практически за время формирования импульса, перемагничивания сердечника элемента памяти 3 не происходит.

После восстановления состояния триггера 2 происходит восстановление информации в элементах памяти

Из описания работы триггерного устройства видно, что во время действия входного импульса до переключения триггера производится стирание информации, записанной в магнитных сердечниках элементов памяти. Поэтому сигналы восстановления состояния триггера после его переключения в схеме не формируются. Следовательно, в рассматриваемой схеме исключается необходимость сохранения сигнала на входе триггерного устройства после переключения триггера, что снимает ограничение в его применении и расширяет функциональные возможности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерное устройство (его варианты) | 1982 |

|

SU1019594A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250554C1 |

| Триггерное устройство (его варианты) | 1981 |

|

SU970650A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1995 |

|

RU2106742C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2248663C1 |

| Триггерное устройство | 1979 |

|

SU813709A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250555C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2001 |

|

RU2207716C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250557C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2248662C2 |

Триггерное устройство, содержащее триггер, первый и второй элементы памяти на магнитных сердечниках, первый и второй элементы совпадения, первый и второй диоды, первый и второй конденсаторы, первый, второй, третий и четвертый резисторы, тактовый вход триггера соединен с входной шиной, входы обмоток считывания первого и второго элементов памяти на магнитных сердечниках соединены с общей шиной, а выходы обмоток считывания соединены с катодами соответственно первого и второго диодов, аноды которых соединены с общей шиной через соответственно первый и второй конденсаторы, и с шиной питания через соответственно первый и второй резисторы, входы обмоток записи первого и второго элементов памяти на магнитных сердечниках соединены с шиной питания через соответственно третий и четвертый резисторы, а выходы обмоток записи соединены между собой, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены первый и второй инверторы, входная шина устройства соединена через первый инвертор с первыми входами первого и второго элементов совпадения и через второй инвертор с выходами обмоток записи первого и второго элементов памяти на магнитных сердечниках, входы которых соединены с выходами соответственно первого и второго элементов совпадения, вторые входы которых соединены соответственно с прямым и инверсным выходами триггера, входы установки и сброса которого соединены с анодами соответственно первого и второго диодов.

Триггерное устройство, содержащее триггер, первый и второй элементы памяти на магнитных сердечниках, первый и второй элементы совпадения, первый и второй диоды, первый и второй конденсаторы, первый, второй, третий и четвертый резисторы, тактовый вход триггера соединен с входной шиной, входы обмоток считывания первого и второго элементов памяти на магнитных сердечниках соединены с общей шиной, а выходы обмоток считывания соединены с катодами соответственно первого и второго диодов, аноды которых соединены с общей шиной через соответственно первый и второй конденсаторы, и с шиной питания через соответственно первый и второй резисторы, входы обмоток записи первого и второго элементов памяти на магнитных сердечниках соединены с шиной питания через соответственно третий и четвертый резисторы, а выходы обмоток записи соединены между собой, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены первый и второй инверторы, входная шина устройства соединена через первый инвертор с первыми входами первого и второго элементов совпадения и через второй инвертор с выходами обмоток записи первого и второго элементов памяти на магнитных сердечниках, входы которых соединены с выходами соответственно первого и второго элементов совпадения, вторые входы которых соединены соответственно с прямым и инверсным выходами триггера, входы установки и сброса которого соединены с анодами соответственно первого и второго диодов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| SU, заявка, 2556932, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| SU, заявка, 2748994, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1997-09-10—Публикация

1980-03-24—Подача