(5) КОЛЬЦЕВОЙ СЧЕТЧИК

| название | год | авторы | номер документа |

|---|---|---|---|

| Кольцевой счетчик | 1981 |

|

SU999167A1 |

| Кольцевой счетчик | 1981 |

|

SU953740A1 |

| Кольцевой счетчик | 1985 |

|

SU1280696A1 |

| Кольцевой счетчик | 1980 |

|

SU940311A1 |

| Устройство для диагностики неисправностей многоярусных пирамидальных схем | 1980 |

|

SU980084A1 |

| Кольцевой счетчик | 1979 |

|

SU851783A1 |

| Кольцевой счетчик | 1978 |

|

SU752813A1 |

| Двоичный счетчик | 1983 |

|

SU1149402A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| Кольцевой счетчик | 1978 |

|

SU750740A1 |

1

Изобретение относится к автоматик ке и вычислительной технике м может быть использовано при реализации техх нических средств автоматики и вычислительной техники.

Известен кольцевой счетчик, содержащий входную шину, шину установки, разряды на Drтриггерах, первый и второй элементы И во всех разрядах, дополнительный элемент И и элемент HECl.

Однако данное устройство отличает ся недостаточно высокой достоверностью функционирования, сброс любого О-триггера в О приводит к переносу 1 на первый выход, и малым коэффициентом пересчетом п + 1, т.е. только на единицу больше, чем количество р-триггеров.

Наиболее близким по технической сущности является кольцевой счетчик, содержащий разряды на последовательно соединенных О-триггерах, О-вход

О-триггера первого разряда соединен с инверсным выходом О-триггера последнего разряда, тактовые входы . всех D-триггеров соединены с входной J шиной Г2|.

Недостатком известного устройства являются ограниченные функциональные возможности, так как он не имеет поtg зиционных выходов, и низкая достоверность функционирования - возможны сбои в виде лишних волн нулей и единиц. Цель изобретения - расширение функциональных возможностей и повышение достоверности функционирования.

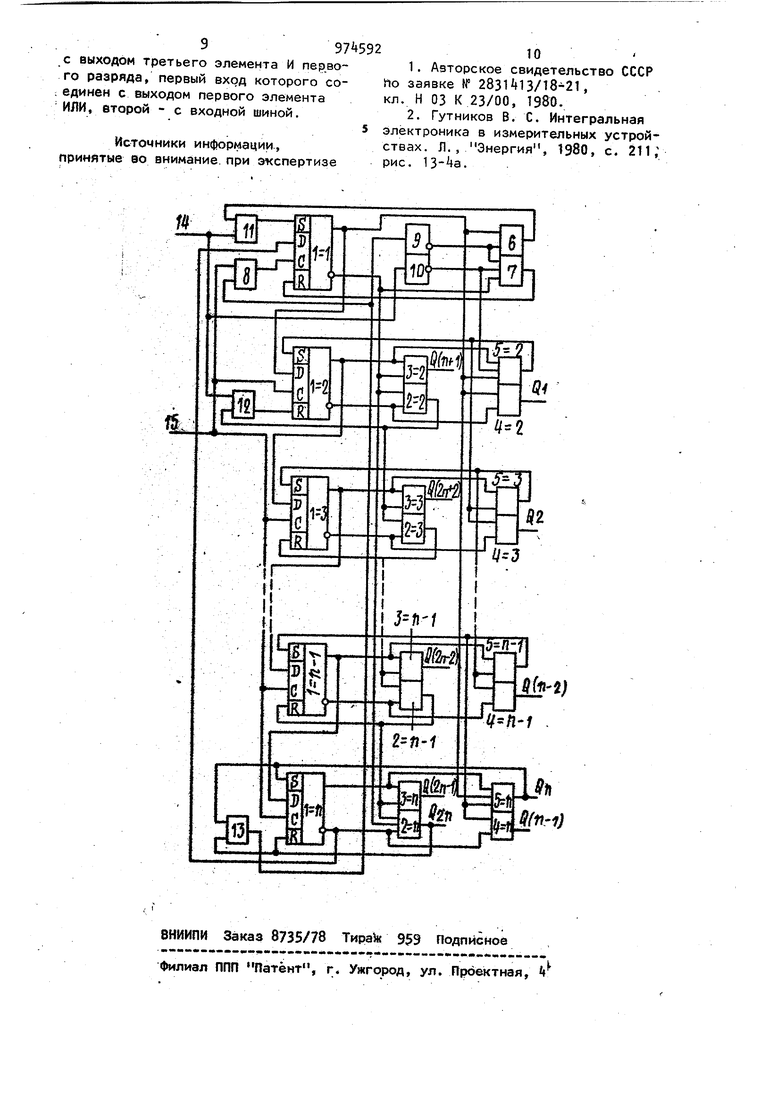

Поставленная цель достигается тем, что в кольцевой счетчик, содержащий разряды на последовательно соединенных D-триггерах, D-вход О-триггера М первого разряда соединен с инверсным выходом О-триггера последнего разряда, тактовые входы 0-триггеров со второго по последний разряд соединеНЫ с входной шиной, введены в каждый разряд, кроме первого, первый, второй, третий и четвертый элементы И, в первый разряд первый, второй и третий элементы И первого разряда, два элемента НЕ, три элемента ИЛИ, первые входы первого, третьего и второго четвертого элементов И каждого раз ряда, кроме первого, соединены соответственно с инверсным и прямым выходами D-триггера , а вторые входы первого, второго и третьего четвертого элементов И этих же разрядов соединены соответственно с инверсным и прямым выходами О-триггера первого разряда и выходами первых и четвертых элементов И предыдущих разрядов, первые входы первого и второго элементов И первого разряда соединены соответственно с инверсным и прямым Ъыходами D-триггера первого разряда, их вторые входы через первьй элемент НЕ соединены с выходом первого элемента ИЛИ, входы которого соединены с выходами первого и четвертого элементов И последнего разряда, третьи входы , первого и четвертого эле ментов И первого и второго разрядов через второй элемент НЕ соединены с шиной установки, третьи входы первого и четвертого элементов И последнего разряда соединены соответственно с четвертым и прямым выходами D-триггера первого разряда, входы установки в ноль D-триг геров всех разрядов, кроме второго, соединены с выходами первых элементов И своих разрядов, вход установки в ноль О-триггера второго разряда соединен с выходом второго элемента ИЛИ, входы которого соединены с шиной установки и с выходом первого длемента И второго разряда, входы установки в единицу D-триггеров всех раарядЬе, KpoMei первого, соединены с выходами четвертых элементов И своих разрядов вход установки в единицу первого разр яда соединен С выходом третьего элемента ИЛИ, входы которогосоединены с шиной установки и выходом втЬрого элемента И первого разряда, тактовый вход. D-триггера первого разряда соединен с выходом третьего элемента И первого разряда, первый вход которого соединен с выходом первого элемента ИЛИ, второй - с входной шиной. На чертеже представлена схема коль цевого счетчика. Устройство содержит D-тригперы 1«1, 1-2,..., элементы , 2-3,. , ....,, , .... tn; , ,..., 6-8 И, элементы 9, 10 НЕ, элементы11-13 ИЛИ, шину Н установки, тактовую шину 15. Структурно предлагаемое устройство состоит из п-разрядного кольцевого счетчика Джонсона, D-триггеры , 1-2,... с перекрестной связью между последним и первым разрядами дешифратора кодов счетчика Джонсона в позиционные сигналы, снимаемыес выходов, элементы И , ,.-., 3-2, ,.:., 4-2, ,...-п; ..., элементов обратной связиэлементов 8, 7 И, элементов управления элементами обратной связи - элементов 9, 10 НЕ, элементов тактирования D-триггера первого разряда - элементов ИЛИ 13 и И 8, элементов установки исходного состояния - элементов ИЛИ 11, 12. Кольцевой счетчик работает следующим образом. Сначала происходит последовательное заполнение логическими 1 всех разрядов, начиная с первого, а затем первый разряд переходит в состояние О и происходит обратный процесс: последовательное заполнение всех разрядов счетчика логическими 0. Коэффициент пересмета 2 п. Выходами кольцевого счетчика являются выходы элементов И дешифратора 2, ,... , 5, , ,..., . Установка исходного состояния осуществляется подачей 1 на шину 14 установки. Сигнал установки через элемент 10 НЕ отключает элементы 7, 6 И - обратнь е связи на входы установки в О и 1 0-триггеров первого и второго разрядов 1-1, и устанавливает их в 1 и.О. На выходе элемента И 4x2, первом позиционном выходе, появляется 1, что и соответствует исходному состоянию. После первого тактового импульса на выходах D-триггеров 1И, , 3 состояние 110 и 1 на выходе элемента . Состояние, последующих, после первого О-триггера с нулевым состоянием, 0-т{эиггеров не имеет значения - дешифратор формирует сигнал совпадения (логическую 1) единичных состояний Р-триггеров предыдущих от первого нулевого разряда с первым нулевым разрядом и второго сигнала совпадения быть не может. После второго тактового импульса на выходах D-триггеров

, 1 2, 1«3, Ui состояние 1110 и 1 на выходе элемента .4 и т. д,, после (п-2)-го тактового импульса на выходах D-триггеров 1Н.1, ,... , Ып состояние 11...10 и 1 на выходе 5 элемента ЛSM1, после (n-l)-ro тактового импульса D-триггеры всех разрядов установятся в 1 и Ч- будет на выходе элемента . В процессе первой половины счета - последовательного заполнения логическими 1 всех разрядов - сигналы (логические 1) с выходов элементов дешифратора - элеГментов ,, ,.. запрещают ложное переключение из 1 в О 0-три1- геров своих разрядов, блокируя ложный перенос, в результате сбоя, выходного позиционного сигнала назад в предыдущие разряды. Ложное переключение из 1 в О D-триггеров запреще-И но -элементном обратной связи - элементом 6. Ложное переключение D-триг- геров последующих от выходного сигнала не влияет на выходы кольцевого счетчика. Ложное переключение из О в 1 первого R-триггера с нулевым состоянием приводит к автоматическому переходу выходного сигнала в следующий разряд. Ложное переключение из О в 1 одновременно первого П-триг 30 гера с нулевым состоянием и последующих приводит к переносу выходного СИРнала через один и более разрядов. Таким образом, только ложное переключение из О в 1 подряд двух и более 35 D-триггеров причем обязательно, вместе с первым О-триггером с нулевым состоянием, приводит к переносу выходного сигнала на один и более разрядов.40

Логическая 1 с выхода элемента через элемент 13 ИЛИ открывает дополнительный элемент 8 и через элемент 9,отключает обратные связи D-триггера первого разряда - элемен- 4S ты 7, 6, разрешая его переключение. Следующим ri-M тактовым импульсом D-триггер переходит в О и на выходе элемента 1 и следующими тактовыми импульсами в D-триггеры раз-5о рядрв последоваГельно записываться нули. После (п+1)-го тактового импульс са на выходах D-триггеров 1 1, 1si2, 1-3 состояние 001С состояние последующих D-триггеров не влияет на выходы .. кольцевого счетчика/ и 1 на выходе элемента 3«3 и т. д., после (2п-2)-го тактового импульса на выходах D-триггеров. l-l, ,... , Isn состояние 00...01 и 1 на выходе элемента , после (2п-1)-го тактового импульса на выходах D-триггеров , ,..., состояние 00...00 и 1 на выходе элемента . В процессе второй половины счета, последоХательного заполнения нулями D-триггеров разрядов, сигналы-с выходов элементов дешифратора - элементов , 2-3,... запрещают ложное переключение D-триггеров своих разрядов из О в 1, запрещая перенос выходного сигнала назад, в предыдущие разряды. Ложное переключение из О в 1 D-триггера первого разряда запрещено элементом обратной связи - элементом 7. Ложное переключение из 1 в О первого D-триггера с единичным состоянием приводит к автоматическому переносу выходного позиционного сигнала в следующий разряд. Одновременное ложное переключени из 1 в О первого D-триггера с едничным состоянием и последующего (последующих/ приводит к переносу выходного позиционного сигнала на один (несколько) разрядов вперед. Ложное переключение D-триггеров последующих от выходного позиционного сигнала разрядов не влияет на выходы т. о. только ложное переключение из 1 в О одновременно двух и более D-триггеррв вместе с первым D-триггером с едийичным состоянием приводит к переносу выходного позиционного сигнала через один и более разрядов. Логическая 1 с выхода элемента через элемент 13 открывает дополнительный элемент 8 и через элемент 9 отключает обратные связи D-триггера первого разряда - элементы 7, 8, разрешая его переключение. Следующим 2 п-м тактовым импульсом в D-триггер записывается 1 и на выходе элемента 4-2 1 и последующими тактовыми импульсами в D-триггеры разрядов последовательно записываться единицы, т. е. процесс повторяется. Выход вми устройства служат выходы элементов , 3,..., 5, , ,... , , На выходах элементов , ,...п получены сигналы совпадения единичных состояний предыдущих разрядов с нулевым своего, на выходах , ,... получены сигналы совпадения нулевых состояний предыдущих разрядов с единичным состоянием своего, на выходах элементов и получены сигналй совпадения нулевых и единичных состояний всех разрядов. Такой принцип формирования выходных позиционных сигналов исключает появле ние на выходах устройства (выходах дешифратора) более одной 1, только одна 1 может быть на выходах кольцевого сметчика в любой момент време ,ни. Сигналы элементов дешифратора элементы , 5-3,... запрещают ложное переключение из 1 в О 0-триггеров своих разрядов, сигналы элементов дешифратора - элементов 2si2, ,...2rn запрещают ложное .переключение из О в 1 D-триггеI ров своих разрядов. Ложное переключе ние D-триггера первого разряда запре щено обратными связями - элементами 7,6. Принцип построения .дешифратора исключает исчезновение единицы и появление на выходах более одной единицы. Элементы 2-п и дополнительно соединены с инверсным и прямым выхода ми D-триггера первого разряда для уст ранения задержек исчезновения 1 на выходах устройства - элементах и . Задержка обусловлена-временем перехода из 1 в О последовательных цепочек элементов , ,-. 2вп-1 и , ,... . Элементы 7 и соединены через элемент VO с шиной установки для отключения обратной связи на время установки. На тактовый вход О-триггера сигна лы поступают только в моменты, когда все разряды находятся в 1 или в О, все остальное время ложное переключение О-триггера блокируется элементами обратной связи - элемен тами 7,8. Примененный дешифратор позволяет упростить установку за счет уменьшения количества связей, с шиной установки соединяются только два первых разряда.. Таким обрезом, введение в каждый разряд, кроме первого, четырех элементов И, в первый разряд двух элементов И, дополнительного элемента И два элемента НЕ, три элемента ИЛИ поз воляет получить позиционный код с высокой достоверностью -функционирования т. е. высокой помехоустойчивостью. Формула изобретения Кольцевой счетчик, содержащий разряды на последовательно соединенных О-тркггерах, 0-вход D-триггера первого разряда соединен с инверсным выхо978 дом D-триггера последнего разряда, тактовые .входы D-триггеров со второго по последний разряд соединены с входной шиной, отличающийс я тем, что, с целью расширения функциональных возможностей и повышения достоверности функционирования введены в каждый разряд, кроме первого, первый, второй,третий и четвертый элементы И, в первый разряд первый, второй и .третий элементы И первого разряда, два элемента НЕ, три элемента ИЛИ, первые входы первого, третьего и второго четвертого элементов И каждого разряда, кроме первого, соединены соответственно с инверсным и прямым выходами D-триггера, а вторые входы первого, второго и третьего четвертого элементов И этих же разрядов соединены соответственно с инверсным и прямым выходами D-триггера первого разряда и выходами первых и четвертых элементов И предыдущих разрядов, первые входы первого и второго элементов И первого разряда соединены соответственно с инверсным и прямым выходами D-триггера первого разряда, их вторые входы через первый элемент НЕ соединены с выходом первого элемента ИЛИ, входы которого соединены с.выходами первого и четвертого элементов И последнего разряда, третьи входы первого и четвертого элементов И первого и второго разрядов через втррой элемент НЕ соединены с шиной установки, третьи входы первого и четвертого элементов И последнего разряда соединены соответственно с 4eTBepTjb(M и .прямым выходами D-триггера первого разряда, входы установки в ноль О-триггеров всех разрядов, кроме второго соединены с выходами первых элементов И своих разрядов, вход установки в ноль D-триггера, второго разряда соединен с выходом второго элемента ИЛИ, входы которого соединены с шиной установки и с выходом первого элемента И второго разряда, входы установки в единицу D-триггеров всех разрядов, кроме первого, соединены с выходами четвертых -элементов И своих разрядов, вход. установки 8 единицу первого ра.зряда соединен с аыход(ж третьего элемента ИЛИ, входы которого соединены с шиной установки и вь4ходом второго элемента И первого разряда, тактовый вход О-триггера первого разряда соединен

с выходом третьего элемента И первого разряда/ первый вход которого со; единен с выходом первого элемента ИЛИ, второй - с входной шиной,

Истомники информации, принятые 90 внимание, при экспертизе

кл. Н 03 К 23/00, 1980.

электроника в измерительных устройствах. Л., Энергия, 1980, с. 211; рис. .

Авторы

Даты

1982-11-15—Публикация

1981-05-11—Подача