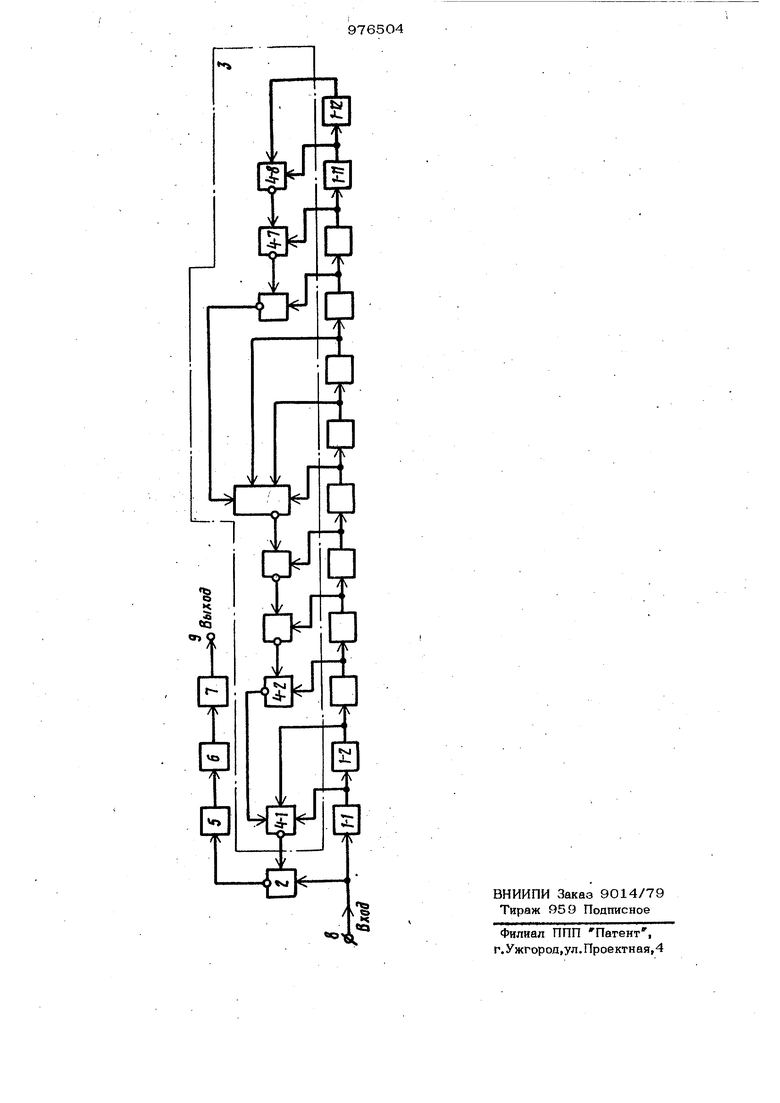

Изобретение относится к импульсной технике. Известен делитель частоты с дробным коэффициентом деления, содержащий блок деления с управляемым коэффициентом деления, блок сравнения кодов, входы которого соединены с выходами двух сумма торов, управляемый элемент задержки, включенный между входной шиной и входо блока деления, блок памяти, два ве Тиля, умножитель и делитель чисел, входы и выходы которых соединены с выходами и входами бло1са сравнения кодов С1 Однако данный делитель являетсй сяож ным. Наиболее близким к предлагаемому по технической сущности является делитель, содержащий опорный делитель частоту ва пятнадцати последовательно соединенных одноименными выходами триггерах, входной инвертор, выходной вентиль 2И-НЕ И логический формирователь периодичеокого строб-сигнала на вентилях И-НЕ со следующими I иерархическими связями: вход первого триггера соединен с источником делимой частоты чере инвертор, вход, которого также соединен с одним из входов выходного вентиля, дающего результирующий сигнал, а другой вход выходного вентиля соединен с выходом лошческого формирователя периодического строб-сигнала. Четыре входа первого вентиля И-НЕ соединены с входами второг(-пятого триггеров, а его пятый вход соединен с выходом второго вентиля И-НЕ, три входа )х торого сое;1 нены с входами шестого- росъмого триггеров, а его четвертый вход соединен с выходом третьего вентиля И-НЕ, даа входа третьего) вентиля И-НЕ соединены с входами девятого-десятого триггеров, а третий вход - с выходом четвертого вентшга И-НЕ, один вход которого соединен с входом одиннадцатого триггера, а другой - с выходом пятого вевтвля И-НЕ. один вход пятого вентиля . И-ИЕ соединен с входом двенадцатого триггера, а другсй с выходом шестого вентиля И-НЕ, три входа которого соединены с входами тринадцатого-пятнадцатого т риггеров, а четвертый - с выходсж пяг надпатого триггера С 2 . Однако данный делитель характеризуется недостаточной точностью коэффиггаев . та деления и малым динамическим диапазоном. Цель изобретения - повышение точности коэффициента деления. Поставленная цель достигается тем, что в делитель частоты с дробным коэффициентом деления, содержащий двенадцать последовательно вкЮоченных триггеров, вход первого из которых соединен с входной шиной и первым входом выходного элемента И-НЕ, логический формирователь строб-сигнала, состоящий вэ шест элементов И-НЁ, пергмый вход каждого из которых соединен с выходом последующе- го элемента И-НЕ, второй вход первого элемента И-НЕ соединен с выходом второго триггера, а выход первого .элемента И-НЕ соединен со вторым входом выходного элемента И-НЕ, введены три додол нительных триггера, включенных последовательно между выходом выходного элегмента И-НЕ и выходной шиной, а в логи ческий формирователь стро -сигнала введены седьмой и восьмой элементы И-НЕ, первый вход седьмого элемента И-НЕ сое динен с выходом восьмого элемента И-НЕ первый вход которого подключен к выходу двенадцатого триггера, причем третий вход первого элемента И-НЕ соединен с выходом первого триггера, входы пятого элемента И-НЕ соединены с выходами шестого, седьмого и восьмого триггеров, а вторые входы остальных элементов И-НЕ соединены соответственно с выходами остальных основных три1 геров. На чертеже приведена структурная электрическая схема предлагаемого делителя . Делитель частоты содержит триггеры 1-1+1-12, выходной элемент 2 И-НЕ, логический формирователь 3 строб-сигна ла, состоящий из элементов 4-1 4-8 И-НЕ, дополнительные триггеры 5. 7. Входной сигнал подан на входную шину 8 выходной сигнал снимается с выходной шины 9. Работа делителя частоты происходит следующим образом. При подаче на шину 8 гГериодического игнала на выходах триггеров 1-11 и l-i2 происхЬдит понижение данной частоты в 2048 и 4096 раз соответственно Но так как два сигнала находятся между собой в двухкратном частотном соотноше нии, то после их логического перемножения элементом 4-8 на выходе последнего снова возникает сигнал той же частоты, что и на выходе триггера 1-12, но уже со скважностью в 4 ед. Это и есть первоначальный строб-сигнал. В свою очередь, элемент 4-7 перемножает начальный строб-сигнал и сигнал поделенной входной частоты в1024раза, снимаемый с десятого триггера 1-10. Иначе говоря, сигнал триггера 1-10 стробируется начальным строб-сигналом элемента fe рёэультй1 ё ий четЬфех импульсов триггера 1-10 изымается один импульс элементом 4-7, то-есть наблю ается начальное понижение частоты в 4/3 раза. Поскольку по данной аналогии полученные на выходе элемента 4-7каждые три импульса из четырех являются стробирующими для сигнала входной частоты, поделенной уже в 512 раз и снимаемой с триггера 1-9, то на выходе элемента 4-8 частота триггера 1-9 уменьшится равномерно на три импульса из каждых восьми входных импульсов. Данная процедура эквивалентна уменьшению частоты в 8/5 раза. Сигнал элемента 4-6 понижает частоту триггера 1-8 с помощью элемента 4-5 в 16/11 раза за счет равномерного изъятия пяти импульсов из каждых шестнадцати входных импульсов входной частоты и снимаетлых с триггера 1-8. Проследив данный процесс изъятия более вьм сокочастотных. импульсов на каждом последующем преобразовании, можно обна- . ружить, что понижение частоты на выходе элемента 4-5 происходит монотонным образом в 117-128 раза элемента 4-4, в 139/256 раза элемента 4-3, в 373/ 512 раза элемента 4-2, в 651/1024 раза элемента 4-1 и, наконец, № 3445/ 4096 раза выходным элементом 2 путем стробирования каждых 4096 импульсов входной частоты периодическими 651 импульсами, образованными на выходе элемента 4-1, Именно в этом состоит сущность равномерного деления частоты путем изъятия определенным образом перечисленных импульсов вз входной последовательности на первом шаге. Второй окотательный шаг деления выполняется с помощью тригт ров 5-7. Таким образом, произведение данных целочисленного коэффициента деления, то-есть 8, и дробного, то-есть 4096/3445 « 1,188969521,... И дает максимально приближенный коэ4 фициент деления, заданный в самом нача а входная и выходная частоты оказывают ся в нужном соотношении. Структура данного делителя и соответствующие в нем связи между всемти элементами находятся на основе следук щего. алгоритма обработки заданного коэффишента деления 9,513 К ,(1+4 X (1 4-0,189125 где параметр п означает число дополни тельно введенных триггеров, а & - остальная добавка заданного коэффициента деления N. С учетом Д находим приведенную добавку л по формуле Л (1-д)/(1+Л)0,6819089... Далее, закодировав лриведенный коэффициент деления N, определяемый ка Д при соблюдешт переполнения последующи разрядов при многократном удвоении добавки Д получим следующий столбец чередующихся вертикальных двоичных ну лей и единиц 1,6819089 1,3638178 0,7276356 1,4552712 0,9105424 1,8210848 1,6421696 1,2843392 0,5686784; 1,1373568 0,2747136 0,5494272 и так далее. При этом закономерность в определении элементов делителя частоты перво го шага и связей между ними оказывает ся следующей: при данном прерванном ко дировании параметра М число всех значащих вертикальных до занятых единиц и нулей равно числу последовательно соедв ненных триггеров; верхняя единица столб ца соответствует первому триггеру, а прерванный последний нуль (может быть и единица) столбца соответствуют послед триггеру; количество элементов ИНЕ формирователя строб-сигнала равно числу прерываний и нулей столбца. Истинный дробный коэффициент всегда получается с ошибкой, определяемой степенью прерывания кодирования приведенного коэффициента N , погрешность можно значительно уменьшить и, следовательно, более точно пр близиться к заданному значению коэффициента путем дальнейшего продолжения кодирования г4 в столбце и дополнения делителя новыми трипперами, а формирователя - новыми элементами И-Iffi. В свою очередь, возможность неограниче ного повышения точности деления часто,ты с помощью усложнения структуры делителя и формирователя периодичесжо10 строб-сигнала при одновременном варьировании параметра п сввдетельствует о том, что предложенная общая структура делителя дает основное преимущество: входную частоту можно делить в любое дробног-десятичное число раз. Формула изобретения Делитель частоты с дробным коэффициентом деления, содержащий двенадцать последовательно включенных триггеров, вход первого та которых соединен с входной иганой и первым входом выходного элемента И-НЕ, логический формирователь строб-сигнала, состоящий из шести элементов MriHE, первый вход канодого из которых соединен с выходом последующего элемента И-НЕ, второй вход первого элемента И-НЕ соединен с выходом второго триггера, а выход первого элемента И-НЕ соединен с вторым входом выходного элемента И-НЕ, отличающийс я тем, что, с целью повышения точности коэффициента деления, в него введены три дополнительных триггера, ВКЛКУченных последовательно между выходам выходного элемента И-НЕ и выходной шиной, а в логический формирователь стро&-сигнала введены седьмой и восьмой элементы И-НЕ, первый вход седьмого соединен с выходом восьмого элемента И-НЕ, первый вход которого подключен к выходу двенадцатого триггера, причем третий вход первого элемента И-НЕ соединен с. выходом первого триггера, входы пятого элемента И-НЕ соединены с выходами шестого, седьмого к восьмого триггеров, а вторые входы остальных элементов И-НЕ соединены соответственно с выходами остальных основных триггеров. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 750744, кл. Н 03 К 23/02, 18.01.78. 2 Eeettrontcs, 1975, №18, с. 12-18.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на @ | 1982 |

|

SU1034198A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1981 |

|

SU1001534A1 |

| Делитель частоты | 1982 |

|

SU1019644A1 |

| Устройство для управления следящим приводом | 1985 |

|

SU1308988A1 |

| Устройство для воспроизведения цифровой информации с носителя магнитной записи | 1988 |

|

SU1571656A2 |

| Цифровой измеритель скважности прямоугольных импульсов | 1990 |

|

SU1725152A1 |

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

| Фазоимпульсный преобразователь | 1983 |

|

SU1161977A1 |

| Многофункциональное счетное устройство | 1985 |

|

SU1298911A2 |

| Устройство для управления следящим приводом | 1986 |

|

SU1416939A1 |

Авторы

Даты

1982-11-23—Публикация

1980-07-09—Подача