Изобретение относится к автоматик, и вычислительной технике, в частности к устройствам обработки информации, представленной в частотно-импульсной форме. Известно дифференцирующее устройство содержащее блок выделения разности П8 риодов, блок возведения в куб, элемент И и счетчик импульсов 1. Известно также дифференцирующее устройство, содержащее генератор импульсов, счетчик, блок управления, блок вычитания, группы элементов И и управляемые делители частоты 1,2. Недостатками известных устройств являются пониженная точность и ограниченный диапазон изменения входного сигнала. Наиболее близким по технической сущ ности является устройство для дифференцирования частоты следования импульсов, содержащее первый элемент И, подкпючен йый первым входом к входу дифференциру мой частоты, первому входу мнонштельно делительного блока, первому входу блока вычитания частот, первому входу чис.ло-импульсного запоминающего блока, соединенного частотным выходом со вторым входом блока вычитания частот и входом умножителя частоты, и к первому входу второго элемента И, второй вход которого подключен к первому входу тре.Tbeio..-элемента И и выходу первого тригг-ера, подключенного счетным входом через первый элемент задержки к выходу элемента И и первому входу второго триггера, соединенного вторым входом с выходом счетчика, шины управления реверсом которого подключены к выходам второго триггера, а счетный вход соединен с выходом третьего элемента И, подключенного вторым входом к входу первой опорной Частоты, первому входу формирователя стробов и второму входу число-импульсного . - запоминающего блока, соединенного третьим входом с первым выходом формирователя стробов и подключенного кодовым выходом к установочному входу счетчика, вход обнуления которого через второй элемент задержки соединен с входом управления за. пнсыо регистра памяти, выходом второго элемента И и входом третьего триггера, подключенного выходом к первому входу iieTBeptoro элемента И, соединенного Э7Орым входом с входом второй опорной частоты, третьим входом - с входом запуска устройства, а выходом - со счетным входом управляемого делителя частоты, подключенного управляющим входом к выходу регистра :памяти, информационный вход которого соединен с кодовым выходом счетчика, причем второй вход первого элемента И подключен к второму выходу формирователя стробов, соединенного вторым входом с входом запуска устройства и первьм входом пятяго элемента И, подключенного вторым входом к выходу блока вычитания частот и соединенного третьим входом с выходом четвертого триггера, подключенного входом к выходу множительно-делительного блока, а выход пятого элемента И соединен с первым входом элемента ИЛИ, подключенного выходом к выходу устройства и соединенного вторым входом с выходом множительно-делительного блока, второй вход которого подключен к выходу умножителя частоты, а третий вход соединен с выходом управляемого делителя частоты J5,

Недостатками известного устройства являются низкая точность и ограниченный диа пазон изменения входного сигнал а. Это обусловлено тем, что при увеличении значения производной увеличивается разность периодов, фиксируетлая за один цикл вычисления в счетчике, что приводит к уменьшению частоты следования импульсов на третьем входе множительно-делительного блока и повышению погрешности дискретности.

Целью изобретения является повышени точности дифференцирования и расширение диапазона изменения входного сигзала.

Цель достигается тем, что в устройство для дифференцирования частоты следования импульсов, содержащее первый элемент И, подключенный первым входсхм к входу дифференцируемой частоты устройства, , первому входу множнтепьно-де- лительного блока, первому входу блока вычитания частот, первому входу числоимпульсного запоминающего блока, соединенного частотным выходом со вторым входом блока вычитания частот и входом умножителя частоты, и к первому входу

второго элемента И, второй вход которого подключен к первому входу третьего элемента И и выходу первого триггера, подключенного счетным входом через первый элемент задержки к выходу первого элемента И и первому входу второго триггера, соединенного вторым входом с выходом счетчика, шины управления реверсом Которого Подключены к выходам второго .триггера, а счетный вход соединей с выходом третьего элемента И, поключенного вторым входом к входу первой опорной частоты устройства, первому входу формирователя стробов и второму входу чнсло-41мпульсного запоминающего блока, соединенного третьим входом с первым выходом формирователя стробов и подключенного кодовым выходом к устновочному входу счетчика, вход обнуления которого :через второй элемент задержки соединен с входом управления записью регистра памяти, выходом второ элемента И и входом третьего триггера, подключенного выходом к первому входу четвертого элемента И, соединенного вторым входом с входом второй опорной частоты устройства, третьим входом - с входом запуска устройства, а выходом со счетным входом управляемого делителя частоты, подключенного угфавляюш:им входом к выходу регистра памяти, информационный вход которого соединен с кодовым выходом счетчика, причем второ вход первого элемента И подключен к второму выходу форм фователя стробов, соединенного вторым входом с входом запуска устройства и первым входом пятого элемента И, подключенного вторым входом к выходу блока вычитания частот и соединенного третьим входом с выходом четвертого триггера, подключенного входом к выходу множительно-делительного блока, а выход пятого элемента И соединен с первым входом элемента ИЛИ подключенного выходом к выходу устройства, дополнительно введены блок задержки, блок сдвига фазы, элемент запрета и блок управления коррекцией, подключенный первым входом к входу дифференцируемой частоты устройства, вторым входом - к выходу умножителя частоты и первому входу блока сдвига фазы, третьим входом - к входу второй опорной частоты ус рройства, четвертым входом - к выходу управляемого делителя частоты и пфвому входу элемента запрета, а выходом - к первому входу блока задержки, соединенного вторым входом с выходом {«Ьюжительно-делительного

блока и подключенного выходом к второму входу элемента ИЛИ и второму входу блока сдвига фазы, выход которого соедит нен со вторым входом множительно-де-лительного блока, Подключенного третьикл. входом к выходу элемента запрета, соединенного вторым входом с входом дм})т ференцируемой qiacToTH.

KpoKire этого, блок управления коррекцией содержит первый и второй эа&лея- . ты И, соединенные первыми входами с первым входом блока управления коррекцией и подключенные вторыми входами к выходу первого триггера, соединенного первым входом с выходом второго элемента И, входом второго триггера и с первыми входами элементов И первой группы, подключенных вторыми входами к выходам разрядов первого счетчика и соединенных выходами с входами первого регистра памяти, выходы которого подключены к перв.ым входам элементов И второй группы, соединенных вторыми входами с выходом первого элемента задержки и подключенных выходами к входам разрядов .цервого счетчика, соединенного счетным входом с выходом элемента ИЛИ и подключенного входами управления реверсом к выходам третьего триггера, первый вход которого соединен с выходом первого счетчика и с первым входом третьего элемента И, а вторые входы третьего .триггера подключены к выходам четвертого и пятого элементов И, причем первый вход четвертого элемента И, соединенного вторым входом с выходом второго триггера, подключен к входу обнуления первого счетчика, входу первого элемента задержки и выходу шестого элемента И, соединенного первым входом с первым выхоаом четвертого триггера и с первым входом седьмого элемента Ни подключенного вторым входом к четвертому входу блока управления коррекцией ик входам восьмого и девятого элементов И, а выход восьмого элемента И, соединенного вторым входом с вторым выходом триггера, подключен черва второй элемент задержки к счетному входу пятого триггера, соединенного первым выходом с входом десятого в втсфым входом девятого элеметлтов И и подключенного вторым выходом к входам одиннадцатого и; двенадцатого элементов И прячем второй вход одиннадцатого элемента И, соединенного третьим входом со вторым входом блоке управления коррекцией, подключен к пер

вому выходу шестого триггера и к вторым входам третьего и двенадцатого элементов И, а выход третьего элемента И соединен с первыми входами чет5 вер того, шестого и седьмого триггеров и с входом третьего элемента , подключенного выходом к первым входам элементов И третьей группы, соединенных вторыми входами с выходами разрядов

i второго счетчика и подключенных выхода ми к входам второго регистра памяти, выходы которого соединены с выходом блока управления ко фекциёй, а вход второго счетчика подключен к выходу

5 двенадцатого элемента И, соединенного третьим входом с Шиной опорного сигнала, причем выход первого элемента И подключен к вторым входам первого и четвертого триггеров, выход девятого

t элемента И соединен со вторым входом шестого триггера, подключенного вторым выходом к третьему входу восьмого элемента И, а выход седьмого элемента И, соединенного вторым входом с третьим

i входом блока управления коррекцией и со в-эрым входом десятого элемента И подключен к первому входу элемента ИЛИ, соединенного вторым входом с выходом девятого элемента И и подключенного тре0 тьим входом I к выходу тринадцатого элемента И, ) первый вход которого соединен с выходом одиннадцатого элемента И и с первым входом пятого элемента И, а второй вход тринадцатого элемента И подключен к первому выходу седьмого триггера, соединенного вторым выходом со вторым входом пятого элемента И, подключенного выходом к второму, входу седьмого триггера.

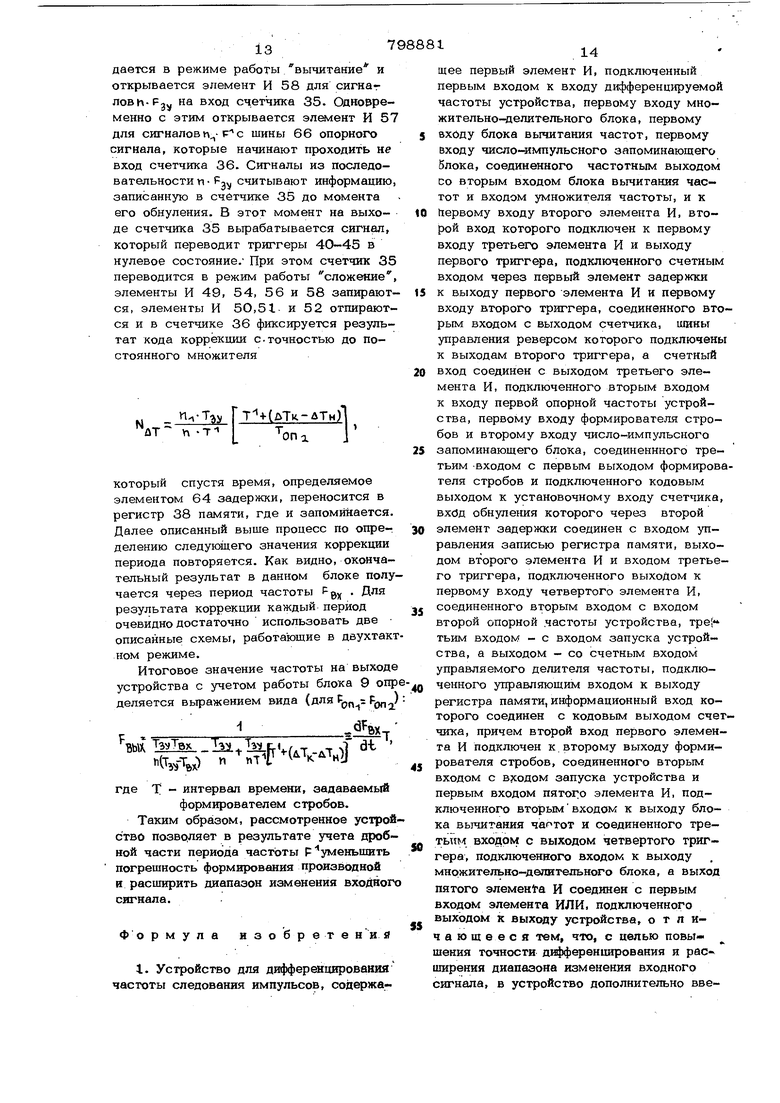

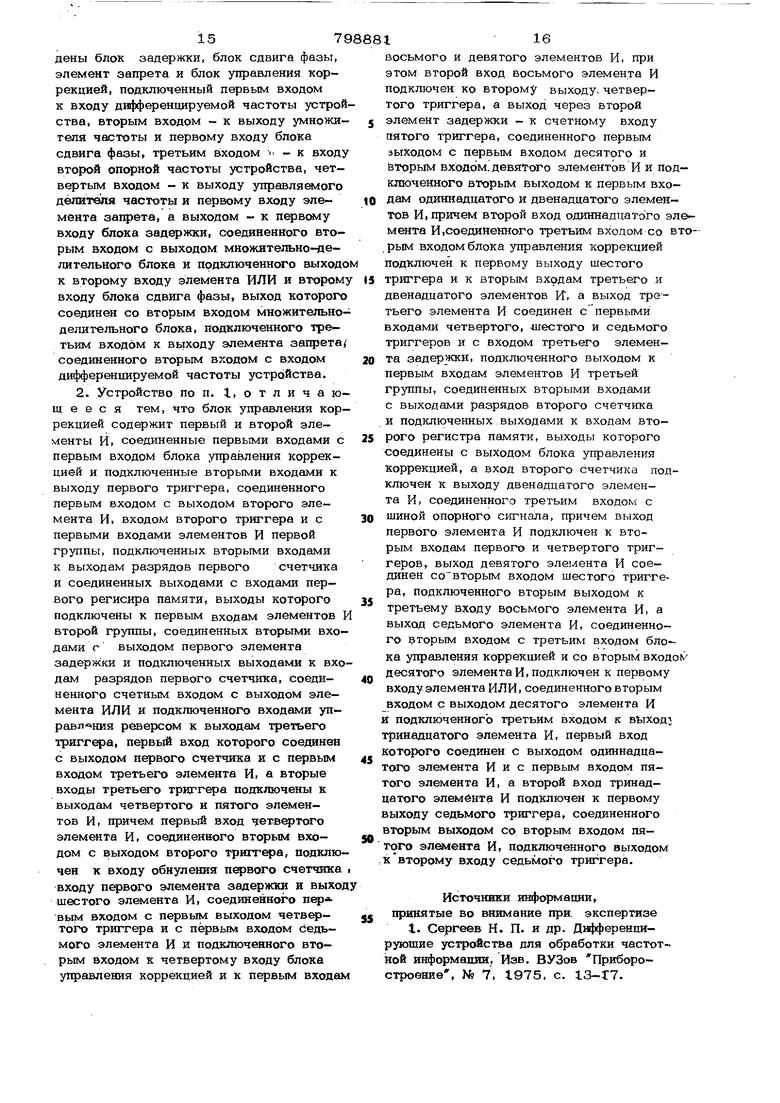

На фиг. 1 изображена 6пок-%:хема устрой ства для дпфференшфования частоты сле вания импульсов, на фиг. 2 - блок схема блока управления коррекцией.

5 Устройство содержит счетчик 1, yiip6u&- лявмый делитель 2 частоты, к ножительноделительньд ёлок 3, умножитель 4 частоты, регистр 5 памяти, блок 6 вычитания частот, число-импульсный запоминающий

Q блок 7, фог ироватеяь| 8 стробов,, блок 9 упрощения ксфрекоией,блок 10 задержки, блок tt сдвнга фэзы, элемент 12 запрета, первый, второ, третий и четвертый трнгг ы 13-16, с первого по пятый элеJ менты И 17-21, элемент ИЛИ 22, первый н второй элементы 23, 24 задержки, вход 25 Подачи дв{)ференцируемых частотно-41мпульсных сигналов, входы 26 и 27 и второй опорных частот, вход 28

и первый, второй, третий и четвертый входы 30-33 и выход 34 блока 9 управления коррекцией. Возможный вариант реализации блока 9 управления коррекцией (фиг.2) содержит первый и второй счетчики 35, 36, первый и второй регистры 37,38, с первого по седьмой триггеры 39-45., с первого по тринадцатый элементы И 46-58, первую, вторую и третью группы элементов И 59-61, первый, второй и третий элементы 62-64 задержки, элемент ИЛИ 65 и шину 66 опорного сигнала. Устройство для дифффенцирования работает следующим образом. В исходном состоянии счетчики, регистр и триггеры обнулены. Работа устройства начинается с подачи сигнала запуска на вход 28 устройства. При этом формирователь 8 стробов начинает периодическую выработку сигналов на своих выходах с периодом Т, которые подаются на вход элемента И 17 и на третий вход число-импульсного запоминающего блока 7 Причем первый сигнал после запуска с вы хода формирователя стробов 8 подается только на вход блока 7. С подачей указанного импульса на вход блока 7 под действием первого же сигнала входной дифференцируемой последовательности частоты РЙХ осуществляется запись и запоминание информации о периоде входной частоты в данный момент времени, а также преобразование запомненной информации в частоту следования импульсов которые непрерывно подаются на входы . блока 6 вычитания частот и умножителя -4 частоты, с выхода которого сигналы подаются на второй вход 31 блока 9 управления коррекцией и на вход блока 11 сдвига фазы. Следует отметить, что поскольку после подачи сигнала запуска результирующая последовательность на выходе множительно-делительного :блокаЗ появляется с некоторой задержкой, то до появления этой последовательности на вход выходного элемента ИЛИ 22 подается через элемент И 21 с выхода блока 6 вычитания частот последовательност неравномерной разностной частоты между входной частотой F и запомненной в блоке 7. При этом знак разности (производной) фиксируется на дополнительн ом выходе блока 6. о Управление подачей указаиной последовательности на выход, устройства осуществляется сигналами с входа 28 и с выхода триггера 16 КОТОРЫЙ запрещает прохождение сигналов

НИИ первого же сигнала на выходе множительно-делительного блока 3.

Работа основного тракта дифференцирования осуществляется следующим образом. При подаче следующего второго сигнала с выхода формирователя 8 стробов он подается на вход блока 7, а также на вход элемента И 17. При этом

осуществляется выдача запомненной в

блоке 7 информации в параллельном коде на счетчик 1 я запись в запоминающий блок 7 текущего значения периода частоты входных сигналов. В счетчике 1 осуIS .ществляется вычитание информации о периоде запомненной частоты и периоде текущего значения частоты. Это производится. следующим образом. Первый после момента подачи сигнала с выхода формирователя 8 стробов импульс входной частоты, подаваемый на вход 25, проходит через элемент И 17 и через элемент 23 задержки на счетный вход триггера 13, переводя его из нулевого в единичное состояние. Очевидно, что при этом сигнал не проходит на выход элемента И 18, так как отпирающий сигнал триггера 13 подается на его вход с задержкой за счет элемента 23 задержки. Одновременно сигнал с выхода элемента И 17 подается на вход триггера 14, переводя его в нулевое состояние, в результате чего счетчик I устанавливается в режим работы вычитание. С переводом триггера 13 в единичное состояние отпирающий сигнал с его выхода подается на элемент И 18 и элемент И 19. При этом через элемент И 19 на вход счетчика I начинают подаваться сигналы опорной частоты Р, с входа 26, которые вычитаются из информации, записанной в счетчике. I. Поступление сигналов на вход счетчика I осуществляется до М(1ента поступления следуквдего сигнала на вход 25. Этот сигнал проходит на выход элемента И 18, переводя триггер 15 в единичное состояние, и через время, определяемое элементом 23 задержки, переводит триггер 13 в нулевое состояние. В результате прекращается подача отпирающего напряжения на вход элемента И 19 и гфекращается подача сигналов опорной частоты на вход счетчика 1. При этом в у&л фиксируется инфорллация соответствующая разности периодов Tg входной частоты Р,и F аапомвеШой частоты F . Одновременно в результате п евода tpHrrepa 15 в единичное состояние .отпирается элемент И 2О для сигналов второй опорной частоты Fjjfjj . которые начинают проходить на вход управляемого делителя 2 и на четвертый вход 33 блока 9. Следует отметить, что в счетчике I всегда фиксируется абсолютное значение разности (по модулю). Если в процессе вычитания счетчик обнуляется, на его выходе вьфабатывается сигнал, который подается на второй вход триггера 14, переводя его из нулевого в единичное состояние. В результате .счетчик I переводится из режима вычитания в режим сложения и накапливается разность по абсолютному значению. Число импульсов, зафиксированное в счетчике I, определяется как П , где Т- - период сигналов первой опор ной частоты FQ После фиксирования информации о разности периодов в счетчике I под действием второго сигнала из последовательности входных сигналов (сигнала с выхо элемента И 18) информация, накопленная в счетчике I переписывается в регистр памяти, а счетчик 1 обнуляется. Процесс получения информации о разности двух периодов повторяется при периодической (с периодом т) подаче сиг налов с формирователя 8 стробов. Выходной код регистра 5 памяти управляет коэффициентом деления делителя 2, частота следования импульсов на выходе которого соответственно равна с 0 РОП. з Далее в множительно-делительном блоке 3 осуществляется операция перемножения входной частоты Pgy на предварительно умноженную на коэффициент в умножителе 4 запомненную частоту Р (с выхода запоминающего блока 7) и яе пон«о ИТОГО ппойявепения на частоту F ления этого произведения на частоту С этой целью на третий вход множи:-. тельно-Делительного блока 3 через схему 12 запрета импульса и вход ,33 блока 9 подаются сигналы с выхода делите ,ля 2 (сигналы, характеризующие Р. ) на первый вход блока 3 и на вход ЗО блока 9 Подаются сигналы входной ча&. готы F-v ина вто1рой вход блока 3 подаю ся сигналы частоты F сдвинутые по фазе в блоке Ц. При этом сигналы с выхода умножителя 4 частоты подаются на вход 31 блока 9. Следует OTMRтить, что подача одного из тлпульсов последовательности сигналов с выхода делителя 2 на третий вход множнтельноделительного блока 3 запрещается с помощью схемы запрета импульса, что необходимо для осуществления коррекции периода выходного сигнала. Схема элемента запрета при этом может быть реализована на основе триггера и элемента задержки. Результирующая частота на выходе множительно-делительного блока 3 равна - - опаРСигналы с выхода блока 3 подаются на второй вход блока 10 задержки на первый вход которого подаются сигналы с выхода 34 блока 9 управле1шя коррекцией периода выходной частоты, которые определяют необходимую величину задержки. Ьа выходе блока 10 формируются сигналы, характеризующие окончагельный резутътат, которые через элемент ИЛИ 22 поступают на выход 29 устройства. На выходе блока 11 сдвига фазы по сигналам с выхода блока 10 вьфабатываются сдвинутые по фазе сигналы с частотой Таким образом, чтобы отсутствовал сдвиг по отношению к сигналам с выхода блока 10 задержки, на выходе блока Ю имеют место сигналы, период которых изменен на величину, вырабатываемую в блоке 9 управления коррекцией.. Работа блока 9 осуществляется сле;дующим образом. Первый импульс частоты F , подаваеМый на вход 30, проходит через элемент И 47 на первые входы группы элементов И 59. Сигналы опорной частоты Рдр через открытый элемент И 52 и ИЛИ 65 проходят на вход счетчика 35, считающего- .,в прямом направлении. С приходом каждого -импульса частоты Р с входа 33 он проходит через ;огк рытый лемент И 51 на .вход установки в нуль счетчика 35 и через элемент 62 задержи - на вторые входы группы элеменов И 6О. этом информация в счетике 35 сбрасывается и затем подсчёт мпульсов осуществляется снова. Такой чет производится до момента прихода игнала частоты Р , который через отрытый элемент И 47 поступает на ервые входы пэ-уппы элементов И 59 н переводит триггеры 39 и 40 в единичное состояние. При этом из счетчика 35 в регистр 37 переносится информация . характеризующая интервал времени ДТ с момента подачи очередного импульса частоты F до момента поступления импульса частоты , в начале определения периода.. СледующийзаимпульсомР импульср обнуляет счетчик 35 и через время задержки, определяемое элементом 62, заносит информацию из регистра 37 опять в счетчик 35. Наряду с этим, упомянутый сигнал из последовательности с частотой F проходит через открытый элемент И 49 на вход триггера 41, переводя его в единичное состояние. В результате счетчик 35 переводится в режим работы вычитание . Далее осуществляется периодическое считывание записанной в счетчике 35 информации. Приче по достижении нулевого значения информации в счетчике 35 в процессе считывания на его выходе вырабатывается сиг нал, который переводит триггер 41 в нулевое состояние, в результате чего счет4Mk 35 переводится в режим работы сложение. Далее в счетчике 35 накапливается разность по абсолютному значению до момента прихода импульса из пос ледовательности Fgx либо из последо вательности F. .С приходом следующего импу са из последовательности f осуществляется сброс информации в счетчике 35, перевод его режим работы вычитание и запись в него $1нформации из регистра 37. Дан лее процесс повторяется. До момента прихода следукяцего импульса из последовательности Р вх который теперь уж€ проходит через открытый элемент И 46 он осуществляет перевод триггеров 39 к 42 соответственно в единичное и нулевое состояние. В результате элементы И 5 52 запираются соответственно для сигналов и f , которые теперь не подаются на вход счетчика 35 и на его шину установки в нуль, и в упомянутом счетчике фиксируется абсолютное значение разности между ЛТцДТц где ЛТ., интервал времени с моменту подачи тлпупъса частоты f до момента поступления им пульса частоты t: в конце определения периода. При этом состояние триггера 41 в мо мент определения разности характ изует ее знак. Нулевое состояние трште. ра означает знак плюс, а единичное минус. Как указывалось выше, для эффективного управления длительностью периода выходного сигнала (чтобы корректируюnlee воздействие в любом случае действовало в сторону увеличения периода) в процессе счета импульсов частоты F в устройстве для дй})ференцирования осуществляется запрет в подаче одного импульсе на третий вход множительно-дели ельного блока 3. Это приводит к тому, kro длительность периода выходного сигНала уменьшается на величину дериода В этом случае при положительном неотрицательном знаке разности лТц лТц, следует осуществлять задержку выходного сигнала, но Только на равную величину. Для получения правильного результата необходимо далее в зависимости от знака полученной разности получить сумму или разность упомянутой разности с периодом- : т , .. Это осуществляется следующим образом. С переводом триггера 42 в единичное состояние под действием сигнала Fgj открывается элемент И 53 для сигналов с частотой F . При этом первый после момента перевода триггера 42 в единичное состояние импульс из последовательности Р проходит на выход элемента И 53 и через время, определяемое элементом 63 задержки, переводит триггер 43 в единичное состоятие. .При этом открываются элементы И 54, 55 и на вход счетчика 35 начийают поступать импульсы опорной часто, которые подаются до момента поступления следующего сигнала из после-, довательности . Следующий импульс из последовательности Р проходит через открытые элементы И 53,54. В резуль-. тате триггер 44 пер одптся в единичное, а триггер 43 в нулевое состояние. При этом запирае чзя элемент И 55, прекращается подача импульсов Р{7пз.и в счетчике 35 фиксируется информация, либо f-UTK-uTn) - f ч. tТЧ(дТц-ЛТн) в зависимости от состояния триггера 41. Одновременно с запиранием элемента И 55 открьтается элемент И 56 для сигналов с.частотой м - Р При этом первый импульс с выхода И 56 проходит открытый элемент И 50 и устанавливает триггфы 41 и 45 в единичное состояние (или подтверждает единичное состояние триггера 4l). При эт,ом счетчик 35. иибо переводится, либо подтв ж. дается в режиме работы вычитание и открывается элемент И 58 для сигнаг noBh-Fg на вход счетчика 35. Однорременно с этим открывается элетлент И 57 для сигналов п-р с шины 66 опорного сигнала, которые начинают проходить не вход счетчика 36. Сигналы из последовательности п Fg, считывают информацию записанную в счетчике 35 до момента его обнуления. В этот момент на выходе счетчика 35 вьфабатывается сигнал, который переводит триггеры 40-45 в нулевое состояние. При этом счетчик 35 переводится в режим работы сложение элементы И 49, 54, 56 и 58 запираются, элементы И 5О,51 и 52 отпираются и в счетчике 36 фиксируется результат хода коррекшш с.точностью до постоянного множителя (ATit-uTH) Пл1% ЛТ П т который спустя время, определяемое элементом 64 задержки, переносится в регистр 38 памяти, где и запоминается. Далее описанный выше пропесс по определению следующего значения коррекции периода повторяется. Как видно, окончательный результат в данном блоке полу чается через период частоты Pg . Для результата коррекции каждый период очевидно достаточно использовать две описанные схемы, работающие в двухтак ном режиме. Итоговое значение частоты на выходе устройства с учетом работы блока 9 опр деляется вьфажением вида (для Ср„ Р,. , ,Мт HhU ТзуТвх ТЗУ г. ,1 dt 4W %Tf ( Т - интервал времени, задаваемый формирователем стробов. Таким образом, рассмотренное устрой ство позврляет в результате учета дробной части периода частоты Р уменьшить погрешность формирования производной и расширить диапазон изменения входног сигнала. Формула изобретен и я I. Устройство для дифференив эсвания частоты следования импульсов, содержащее первый элемент И, подключенный первым входом к входу дифференцируемой частоты устройства, первому входу множительно-делительного блока, первому входу блока вычитания частот, первому входу число-лмпульсного запоминающего блока, соединенного частотным выходом со вторым входом блока вычитания частот и входом умножителя частоты, и к первому входу второго элемента И, второй вход которого подключен к первому входу третьего элемента И и выходу первого тригг а, подключенного счетным входом через первый элемент задержки к выходу первого элемента И и первому входу второго триггера, соединенного вторым входом с выходом счетчика, ищны управления реверсом которого подключены к выходам второго триггера, а счетный вход соединен с выходом третьего элемента И, подключенного вторым входом к входу первой опорной частоты устройства, первому входу формирователя стробов и второму входу число-импульсного запоминающего блока, соединеннного третьим -входом с первым выходом формирователя стробов и подключенного кодовым выходом к установочному входу счетчика, вход обнуления которого через второй элемент задержки соединен с входом управления записью регистра памяти, выходом второго элемента И и входом третьего триггера, подключенного выходом к первому входу четвертого элемента И, соединенного вторым входом с входом второй опорной частоты устройства, тре тьим входом - с входом запуска устройства, а выходом - со счетным входом управляемого делителя частоты, подключенного управляющим входом к выходу регистра памяти, информационный вход которого соединен с кодовым выходом счетчика, причем второй вход первого элемента И подключен к. второму выходу формирователя стробов, соединенного вторым входом с входом запуска устройства и первым входом пятого элемента И, подключенного вторым входом к выходу блока вычитания чаотот и соединенного треть ш входом с выходом четвертого триггера, подключенного входом к выходу мнржительно-двлительного блока, а выход пятого элемен1га И соединен с первым входом элемента ИЛИ, подключенного выходом к выходу устройства, отличающееся тем, что, с целью повышения точности ди})ференшфования и расширения диапазона изменения входного игнала, в устройство дополнительно введены блок задержки, блок сдвига фазы, элемент запрета и блок управления коррекцией, подключенный первым входом к входу дифференцируемой частоты устройства, вторым входом - к выходу умножителя частоты и первому входу блока сдвига фазы, третьим входом - к входу второй опорной частоты устройства, четвертым входом - к выходу управляа лого делителя частоты и первому входу элемента запрета, а выходом - к первому входу блока задержки, соединенного вторым входом с выходом множительно-дели тельного блока и подключенного выходо к второму входу элемента ИЛИ и втором входу блока сдвига фазы, выход которого соединен со вторым входом множительноделительного блока, подключенного третьим входом к выходу элемента загфета/ соединенного вторьп входом с входом

дифференцируемой частоты устройства.

2. Устройство по п. 1,отлича ющ е е с я тем, что блок управления коррекцией содержит первый и второй элементы И, соединенные первыми входами с первым входом блока управления коррекцией и подключенные вторыми входами к выходу первого триггера, соединенного первым входом с выходом второго элемента И, входом второго триггера и с первыми входами элементов И первой группы, подключенных вторыми входами к выходам разрядов первого счетчика и соединенных выходами с входами первого регисира памяти, выходы которого подключены к первым входам элементов И второй группы, соединенных вторыми входами г выходом первого элемента задержки и подключенных выходами к входам разрядов первого счетчика, соединенного счетным входом с выходом элемента ИЛИ и подключенного входами управлчния реверсом к выходам третьего триггера, первый вход которого соединен с выходом первого счетчика и с первым вхсщом третьего элемента И, а вторые входы третьего триггера подключены к выходам четвертого и пятого элементов И, причем первый вход элемента И, соединенного вторым входом с выходом второго триггера, подключен к входу обнуления первого счетчика входу первого элемента задержки и выход шестого элетлента И, соединенного пер. вым входом с первым выходом четвертого триггера и с первым входом Седьмого элемента И и подключенного вторым входом к четвертому входу блока управления коррекцией и к первым входам

восьмого и девятого элементов И, при этом второй вход восьмого элемента И подключен ко второму выход у четвертого триггера, а выход через второй элемент задержки - к счетному входу пятого триггера, соединенного первым зыходом с первым входом десятого и Ьторьш входом, девятого элементов И и поключенного вторым выходом к первым входам одиннадцатого и двенадцатого элементов И, причем второй вход одиннадцатого эмента И,соединенного третьим входом со рым входом блока управления коррекцией подключен к первому выходу шестого триггера и к вторым входам третьего и двенадцатого элементов И, а выход тротьего элемента И соединен с первыми входами четвертого, шестого и седьмого триггеров и с входом третьего элемента задержки, подключенного выходом к первым входам элементов И третьей группы, соединенных вторыми входами с выходами разрядов второго счетчика и подключенных выходами к входам второго регистра памяти, выходы которого соединены с выходом блока управления коррекцией, а вход второго счетчика подключен к выходу двенадцатого элемента И, соединенного третьим входом с шиной опорного сигнала, причем выход первого элемента И подключен к вторым входам первого и четвертого триггеров, выход девятого элемента И соединен совторым входом шестого триггера, подключенного вторым выходом к третьему входу восьмого элемента И, а выход седьмого элемента И, соединенного вторым входом с третьим входом блока управления коррекцией и со вторым вход десятого элемента И, подключен к первому входу элемента ИЛИ, соединенного вторым входом с выходом десятого элемента И и подключенного третьим входом к вЪтход тринадцатого элемента И, первый вход которого соединен с выходом одиннадцатого элемента И и с первым входом пятого элемента И, а второй вход тринадцатого элемента И подключен к первому выходу седьмого триггера, соединенного вторым выходом со вторым входом пятого и, подключенного выходом ,к второму входу седьмого триггера.

Источники информации, пршштые во внимание при. экспертизе I. Сергеев Н. П. и др. Дм})ференцИрующие устройства для обработки частотной информации. Изв. ВУЗов Приборостроение, hfe 7, 1975, с. 13-Г7. 17 2. Авторское свидетельство СССР NO 604008, кп. С 06 С 7/18, 1976. 798881 18 3. Авторское свидетельство СССР № 525117, кл. G ОБ G 7/18. 1974 (прототип).

«SI

Авторы

Даты

1981-01-23—Публикация

1978-03-24—Подача