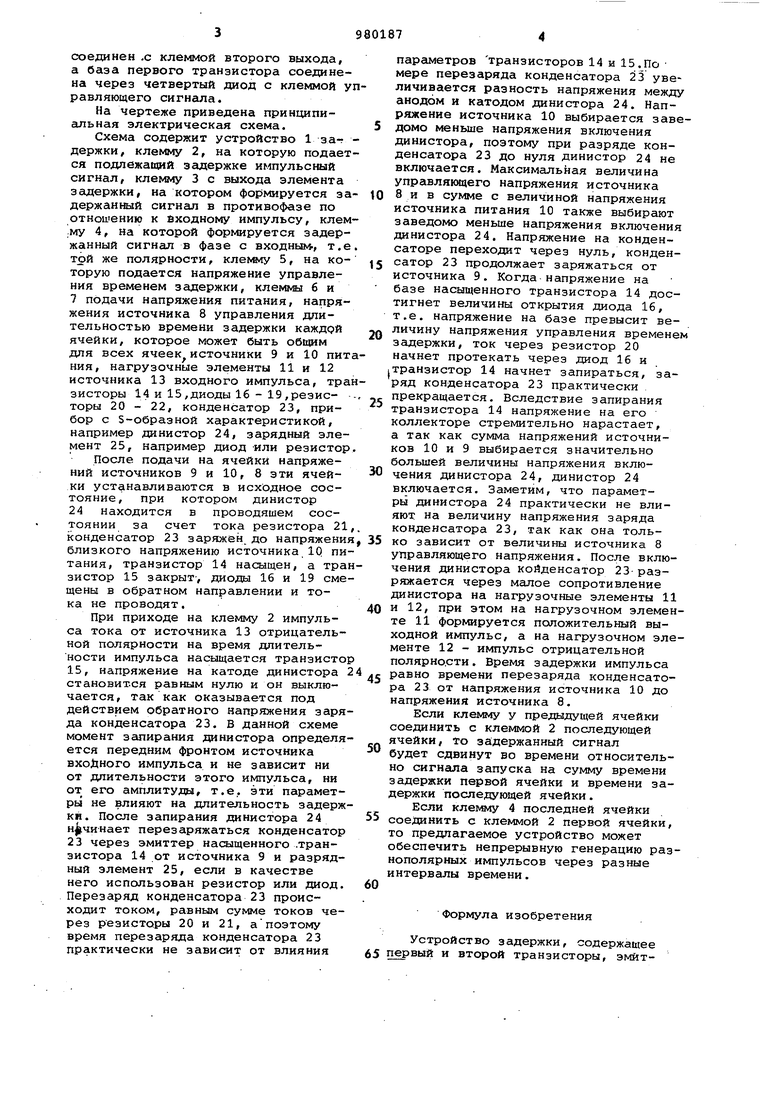

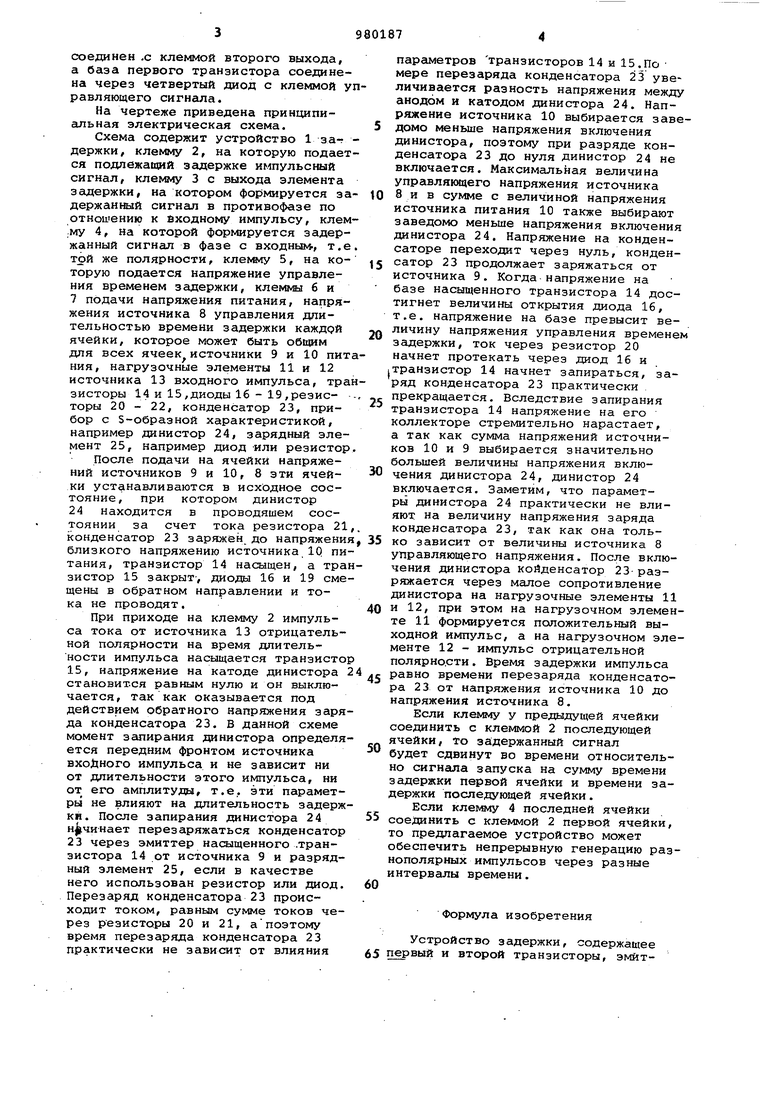

;54) УСТРОЙСТВО ЗАДЕРЖКИ Изобретение относится к устройст вам, обеспечивающим формирование на выходе импульса напряжения с задержкой на заданное время по отношению ко времени поступления на вход входного импульса, используемое, наприме в измерительной технике при определе нии временных интервалов, фазы сигна ла, для создания временных анализато ров, в блоках первичной обработки информации, и т.д. и относится к устройствам задержки,. выполненным на основе релаксаторов.. Известн.о устройство задержки, выполненное на основе ждущего мультивибратора с коллекторно-базовой связью с 3 Однако устройство имеет недостато ную точность. Известны также устройства, обеспечивающие более высокий результат в которых применены пусковые каскады на транзисторах, а также использованы токозадающие транзисторы L2J. Недостатками устройства задержки являются его сложность из-за использования больиого числа деталей,отсутствие на выходах импульсов разной полярности, а плавной регулировки времени задержки импульсов при помощи изменения амплитуды напряжения управляющего сигнала, малая крутизна переднего фронта выходного импульса и малая нагрузочная способность. Цель изобретения - расширение функциональных возможностей. Указанная цель достигается тем, что в устройстве задержки, содержащем первый и второй транзисторы, эмиттер последнего соединен с общей шиной, конденсатор, первый резистор, включенный в коллекторную цепь второго транзистора, второй резистор, включенный в базовую цепь первого транзистора, третий резистор, соединенный первым выводом с шиной источника питания, дополнительно введены четыре диода и прибор с S-образной вольт-амперной характеристикой, например диннстор, первый вывод которого соединен с вторым выводом третьего резистора, через первый диод с коллектором второго транзистора и через второй диод с клеммой первого выхода, а второй вывод соединен с коллектором первого транзистора, через третий диод с эмиттером первого транзистора и с первым выводом конденсатора, второй вывод которого соединен .с клеммой второго выхода, а база первого транзистора соединена через четвертый диод с клеммой у равляющего сигнгша. На чертеже приведена принципиальная электрическая схема. Схема содержит устройство 1 задержки, клемму 2, на которую подает ся подлежащий задержке импульсный сигнал, клемму 3 с выхода элемента задержки, на котором формируется за держангелй сигнал в противофазе по отношению к йходному импульсу, клем .му 4, на которой формируется задержанный сигнал в фазе с входные, т.е той же полярности, кпемму 5, на которую подается напряжение управления временем задержки, клем1 и б и 7 подачи напряжения питания, напряжения источника 8 управления длительностью времени задержки каждой ячейки, которое может быть обвдям для всех ячеек источники 9 и 10 пит ния, нагрузочные элементы 11 и 12 источника 13 входного импульса, тра зисторы 14 и 15,диоды 16 - 19,резисторы 20 - 22, конденсатор 23, прибор с S-образной характеристикой, например динистор 24, зарядный элемент 25, например диод «ли резистор После подачи на ячейки напряжеНИИ источников 9 и 10, 8 эти ячейки устанавливаются в исходное состояние, при котором динистор 24 находится в проводящем состоянии за счет тока резистора 21 конденсатор 23 заряжен, до напряжени близкого напряжению источника 10 пи тания, транзистор 14 насыщен, а тра зистор 15 закрыт-, диоды 16 и 19 сме щены в обратном направлении и тока не проводят. При приходе на клемму 2 импульса тока от источника 13 отрицательной полярности на время длительности импульса насыщается транзисто 15, напряжение на катоде динистора становится равным нулю и он выключается, так как оказывается под действием обратного напряжения заря да конденсатора 23. В данной схеме момент запирания динистора определя ется передним фронтом источника входного импульса и не зависит ни от длительности этого импульса, ни от его амплитуды, т.е. эти параметры не влияют на длительность задерж ки. После запирания динистора 24 н чи-нает перезаряжаться конденсатор 23 через эмиттер насыщенного .транзистора 14 от источника 9 и разрядный элемент 25, если в качестве него использован резистор или диод. Перезаряд конденсатора 23 происходит током, равным сумме токов через резисторы 20 и 21, а поэтому время перезаряда конденсатора 23 практически не зависит от влияния параметров транзисторов 14 и 15.По мере перезаряда конденсатора 23 увеличивается разность напряжения между анодом и катодом динистора 24. Напряжение источника 10 выбирается заведомо меныае напряжения включения динистора, поэтому при разряде конденсатора 23 до нуля динистор 24 не включается. Максимальная величина управляквдего напряжения источника В и в сумме с величиной напряжения источника питания 10 также выбирают заведомо меньше напряжения включения динистора 24. Напряжение на конденсаторе переходит через нуль, конденсатор 23 продолжает заряжаться от источника 9. Когда напряжение на базе насыщенного транзистора 14 достигнет величины открытия диода 16, т.е. напряжение на базе превысит величину напряжения управления временем задержки, ток через резистор 20 начнет протекать через диод 16 и транзистор 14 начнет запираться, заряд конденсатора 23 практически прекращается. Вследствие запирания транзистора 14 напряжение на его коллекторе стремительно нарастает, а так как сумма напряжений источников 10 и 9 выбирается значительно большей величины напряжения включения динистора 24, динистор 24 включается. Заметим, что параметры динистора 24 практически не влияют на величину напряжения заряда конденсатора 23, так как она только зависит от величины источника 8 управляющего напряжения. После включения динистора койденсатор 23 разряжается через малое сопротивление динистора на нагрузочные элементы 11 и 12, при этом на нагрузочном элементе 11 формируется положительный выходной импульс, а на нагрузочном элементе 12 - импульс отрицательной полярности. Время задержки импульса равно времени перезаряда конденсатора 23 от напряжения источника 10 до напряжения источника 8. Если клемму у предыдущей ячейки соединить с клеммой 2 последующей ячейки, то задержанный сигнал будет сдвинут во времени относительно сигнала запуска на сумму времени задержки первой ячейки и времени задержки последующей ячейки. Если кле1«му 4 последней ячейки соединить с клеммой 2 первой ячейки, то предлагаемое устройство может обеспечить непрерывную генерацию разнополярных импульсов через разные интервалы времени. Формула изобретения Устройство задержки, содержащее первый и второй транзисторы, эмйттер последнего соединен с общей шиной, конденсатор, первый резистор, включенный в коллекторную цепь второго транзистора, второй резистор, включенный в базовую цепь первого транзистора, третий резистор, соединенный первый выводом с шиной источника питания, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены четыре диода и прибор с Sобразной вольт-амперной характеристикой, например динистор, первый вывод которого соединен с вторлм выводом третьего резистора, через первый диод с коллектором второго транзис,то1эа и через второй диод с клеммой

первого выхода, а второй вывод соединен с коллектором первого транзистора, через третий диод с эмиттером первого транзистора и с первым ; выводом конденсатора, второй вывод которого соединен с клеммой второго выхода, а база первого транзистора соединена через четвертый диод с клеммой управляющего сигнала.

Источники информации,

принятые во внимание при экспертизе 1. Самойлов Л.К. Задержка информации в дискретной технике. - Сов,радио. М., 1973, с. 83, рис. 3,15.

2. Там же, с. 85, рис. 3.16 (прототип ).

Т- -н

Г

П

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для импульсно-фазового управления преобразователем | 1980 |

|

SU930564A1 |

| Ячейка временной задержки импульсов | 1980 |

|

SU945967A1 |

| Формирователь задержанных импульсов | 1973 |

|

SU790203A1 |

| Коммутатор | 1981 |

|

SU1014147A1 |

| Однотактный распределитель | 1976 |

|

SU598250A1 |

| Преобразователь неэлектрическойВЕличиНы B чАСТОТу | 1979 |

|

SU851768A1 |

| Транзисторное устройство формирования импульсов | 1980 |

|

SU938350A1 |

| Двухтактный инвертор | 1990 |

|

SU1746502A1 |

| Генератор импульсов | 1982 |

|

SU1111251A1 |

| Реле времени | 1981 |

|

SU1022252A1 |

Авторы

Даты

1982-12-07—Публикация

1981-03-09—Подача