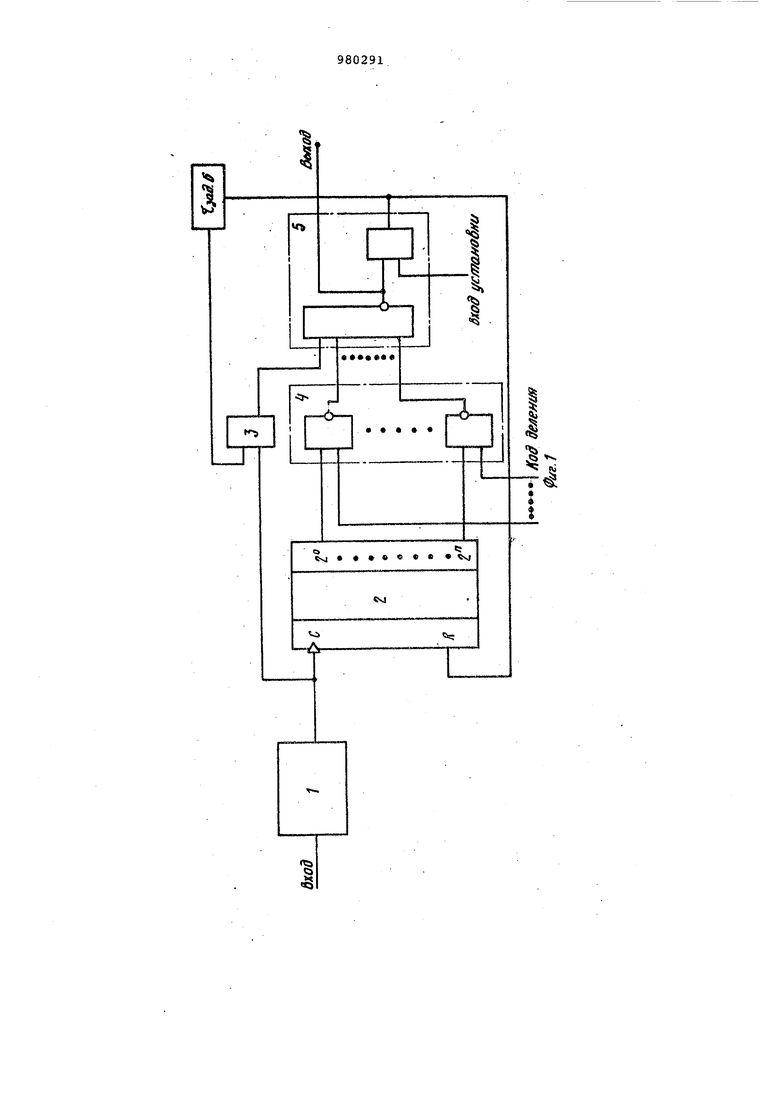

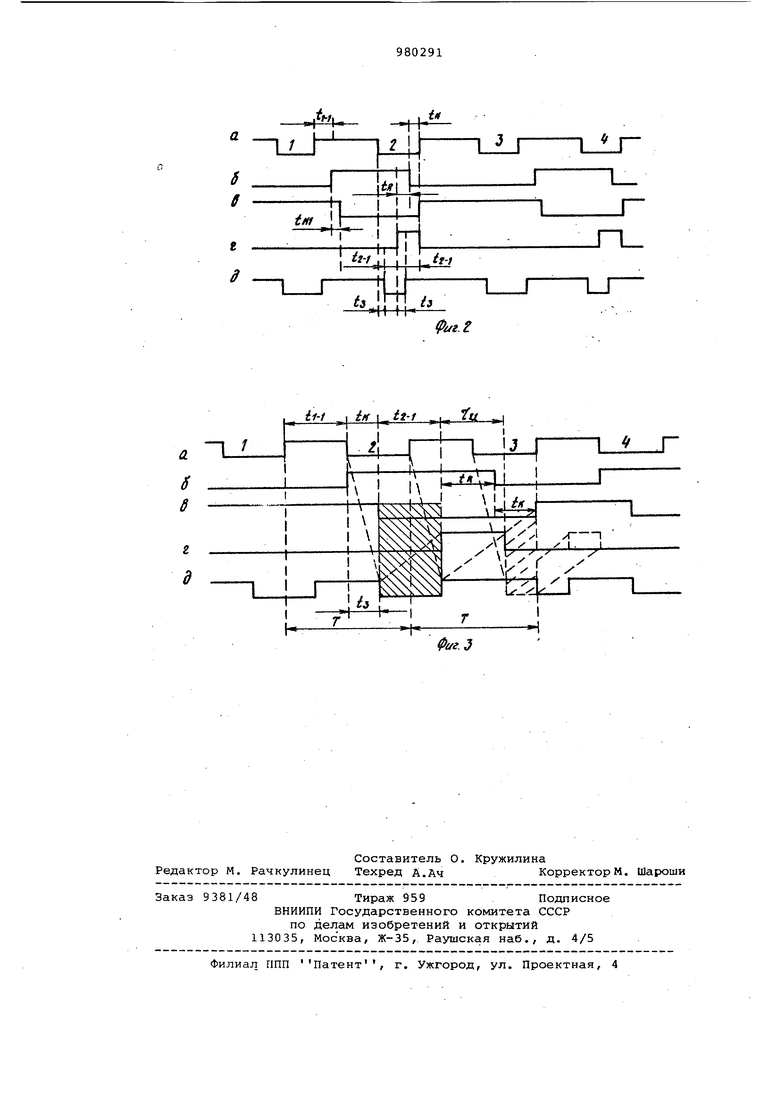

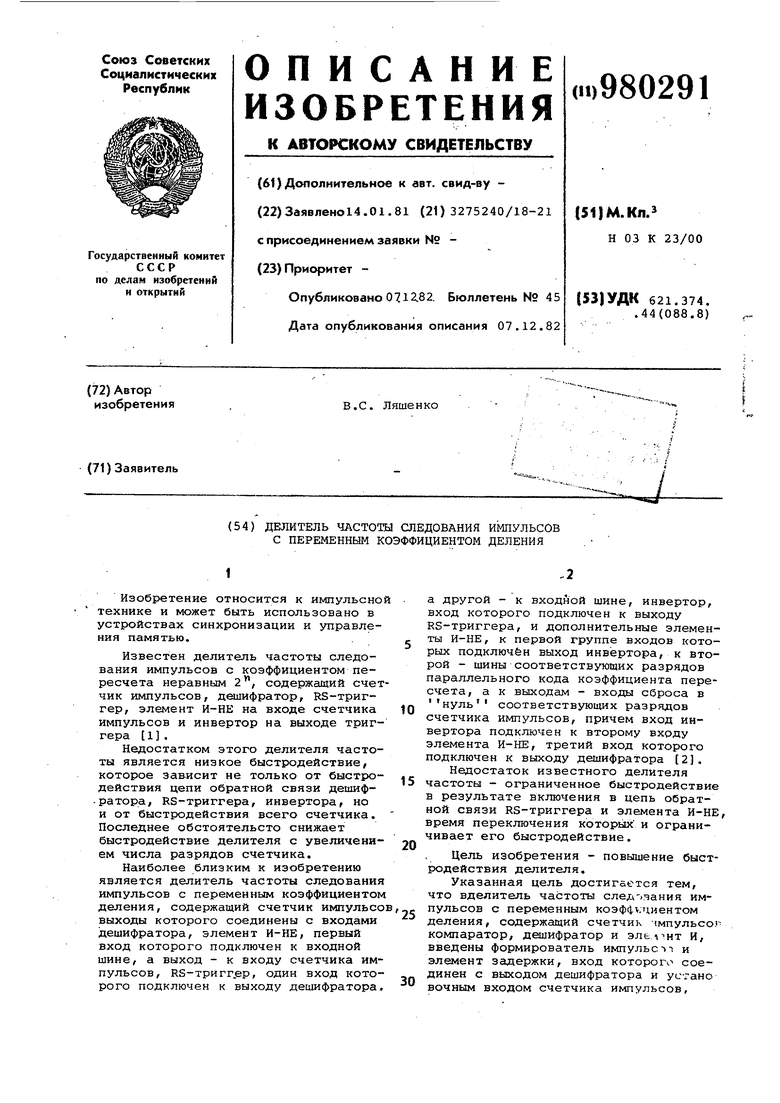

Изобретение относится к импульсно технике и может быть использовано в устройствах синхроиизации и управления памятью. Известен делитель частоты следования импульсов с коэффициентом пересчета неравным 2 , содержащий счет чик импульсов, дешифратор, RS-триггер, элемент И-НЕ на входе счетчика импульсов и инвертор на выходе триггера 1 . Недостатком этого делителя частоты является низкое быстродействие, которое зависит не только от быстродействия цепи обратной связи дешиф.ратора, RS-триггера, инвертора, но и от быстродействия всего счетчика. Последнее обстоятельсто снижает быстродействие делителя с увеличением числа разрядов счетчика. Наиболее близким к изобретению является делитель частоты следования импульсов с переменным коэффициентом деления, содержащий счетчик импульсо выходы которого соединены с входами дешифратора, элемент И-НЕ, первый вход которого подключен к входной шине, а выход - к входу счетчика им пульсов, RS-тригг.ер, один вход кото рого подключен к выходу дешифратора а другой - к входной шине, инвертор, вход которого подключен к выходу RS-триггера, и дополнительные элементы И-НЕ, к первой группе входов которых подключён выход инвертора, к второй - шины соответствующих разрядов параллельного кода коэффициента пересчета, а к выходам - входы сброса в нуль соответствующих разрядов счетчика импульсов, причем вход инвертора подключен к второму входу элемента И-НЕ, третий вход которого подключен к выходу дешифратора 2. Недостаток известного делителя частоты - ограниченное быстродействие в результате включения в цепь обратной связи RS-триггера и элемента И-НЕ, время переключения кбторьк и ограничивает его быстродействие. Цель изобретения - повышение быстродействия делителя. Указанная цель достигается тем, что вделитель частоты след эания импульсов с переменным коэф.циентом деления, содержащий счетчик чмпульсог компаратор, дешифратор и И, введены формирователь импульсчт и элемент задержки, вход которого соединен с выходом дешифратора и устано вочным входом счетчика импульсов. а выходит с первым входом элемента И второй вход которого соединен с выходом формирователя импульсов и счетным входом счетчика импульсов, а выход - с первым входом дешифратора, остальные входы которого соединены с соответствующими выходами компаратора, первые входы которого соединены jC разрядными выходами счетчика импуль сов, а вторые входы - с шинами кода деления. На фиг. 1 представлена структурная схема предлагаемого делителя частот на фиг. 2 и 3 - временные диаграммы, поясняющие его работу при коэффициенте деления, равном 2. Делитель содержит формирователь 1 импульсов, синхронный счетчик 2 импул11сов, элемент И 3, компаратор 4, выполненный на элементах И-НЕ, дешифратор 5 с установкой, реализующийся на многовходовых элементах ИЛИ и И-НЕ выход которого соединен с входом этого элемента ИЛИ, на второй вход которого подается сигнал установки, и элемент 6 задержки. Сигнал установки в работе делителя участия не принимает. Он служит либо для принудительной остановки делителя, либо для установки в ноль счетчика 2 при начальном включении до подачи входных импульсов. Счетчик 2 работает в двух режимах деление входных импульсов, частота которых меньше максимальной частоты деления, и деление -входных импульсов, частота которых равна максимальной частоте деления. Делитель частоты следования импул сов работает следующим образом. На счетчик 2 с формирователя 1 по ступают отрицательные импульсы (фиг. 2а) . Счетчик 2 срабатывает от 1. В начальперепада иэ ном состоянии подается положительный импульс на вход установки и счетчик сбрасывается в О, а на компарато 4 подается код деления, который определяет коэффициент деления (КД) КД К + 1, где К - двоичный код. При этом на всех выходах элементо И-НЕ компаратора 4, за исключением выхода, Соответствующего первому раз рйду, устанавливается О, а на выходе первого разряда - . После прохождения первого импульс первый разряд счетчика 2 перебрасывается (фиг. 26) через t - время срабатывания счетчика по счетному входу - и на выходе первого разряда компаратора 4 появляется через t время срабатывания компаратора .ноль (фиг. 2в). При появлении вт рого импульса первый разряд счетчика 2 через элемент 3 поступает на дешиф ратор 5 с задержкой, t (фиг. 2д), дешифрируется и с задержкой t - временем срабатывания дешифратора - поступаетна сброс счетчика 2 и на вход элемента 3 (фиг. 2г), считая, что одгО. После сброса счетчика 2 (время t,) схема готова к следующему импуль су. Последовательность импульсов (фиг. 2г) является последовательностью с необходимым коэффициентом деления. Для нормальной работы данного де.лителя необходимо подавать входные импульсы определенной длительности. Это связано с тем, что длительность импульса сброса должна закончиться Позже или одновременно с перепадом из нуля в единицу второго входного импульса, так как в противном случае счетчик 2 сбрасывается и сразу срабатывает от этого перепада. Импульс сброса образуется из второго входного импульса при появлении на выходе компаратора 4 нуля (фиг. 2в) и его длительность равна СБроса- ач Длительность импульса можно регулировать с помощью линии задержки, состоящей из одного или нескольких элементов И. Длительность входного импульса, следовательно, должна быть меньше и равна сумме задержек .-., Так как входной второй импульс прохо.дит через элемент 3 с задержкой tj (фиг. 2д), дешифратор 5 с эадержкой iH ( 2г) формирует на выходе элемента 3 длительность импульса сбрр са через t-j т PjciA Через время задержки дешифратора 5 t.-f импульс сброса обрывается (фиг. 2г) .. Следовательно, -rj,52(t,,U,,.,).,A . Рассмотрим работу делителя при работе на максимёшьной частоте. Для нормальной работы делителя й должно быть минимально, при котором возможна нормальная работа выбранной серии микросхем. Допустим что длительность входных импульсов равна или меньше времени срабатывания счетчика 2. -После перев единицу от пада из нуля первого импульса через t срабатывает первый разряд счетчика 2 (фиг.За,б) и на выходе компаратора 4 через 11 появляется нуль (фиг. Зв). Второй входной импульс, пройдя через элемент 3 с задержкой tэ(фиг. Зд) , попадает на дешифратор 5 и формирует импульс сброса с задержкой t (фиг.Зг От импульса сброса счетчик 2 через t сбрасывается (фиг. Зб) и затем через t устанавливается единица на выходе компаратора 4. При увеличении частоты третий импульс (фиг. За) пройдя через элемент 3 (фиг. Зд), может совпасть с временем отработки компаратора 4 (фиг. Зд,в) и образуется второй импульс сброса(показан на фиг. Зг пунктиром), который вызывает дополнительный сброс делителя. Поэтому, подав импульс сброса на элемент 3/ запрещается прохождение третьего импульса на сброс до момента установки компаратора 4. Время запрещения регулируется . Тем самым в момент прихода третьего импульса делительеще подготавливается к работе. Следовательно, минимальный период входных импульсов равен 2TH,.t.t,.4t, ,где t. - длительность импульсов сбро .% -Ьа-н з гаА. Счетчик 2 срабатывает от перепада из нуля в единицу с задержкой t (фиг. За.б) и с задержко t срабатывает компаратор 4(фиг.3б,в Сигнал с компаратора 4 и второй импульс, который проходит через элемен 3(фиг. Зд), поступает на дешифратор 5 и с задержкой t. (фиг. jr) появляется импульс сброса, который прохо дит через элемент 6 сТ.. . Элемент и дииифратор 5 обрываются. В случае, если длительность входных импульсов меньше времени задержек, то импульс сброса равен длительности входных импульсов. Следовательно, минимальный период входных импульсов равен ,-Ьа-1 г ад или ,j V. . Таким образом, предлагаемый делитель частоты отличается высоким быстродействием. Формула изобретения Делитель частоты следования импульсов с переменным коэффициентом деления, содержащий счетчик импульсов, компаратор, дешифратор и элемент И, отличающийся тем, что, с целью повышения быстродействия, в него введены формирователь импульсов и элемент задержки,вход которого соединен с.выходом дешифратора и установочнь1м входом счетчики импульсов, а выход - с первым входом элемента И, второй вход которого соединен с выходом формирователя импульсов и счетным входом счетчика импульсов, а выход - с первым входом дешифратора, остальные входы которого соединены с соответствующими выходами компаратора, первые входы которого соединены с разрядными выходами счетчика импульсов, а вторые входы - винами кода деления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 510785, кл. Н 03 К 23/00, 1973. 2.Авторское свидетельство СССР 696609, кл. Н 03 К 23/00, 1977.

Ч

«

1

р-

О

5

i

I

о

вч4

е: «м

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство определения временного положения импульсных сигналов | 1988 |

|

SU1596301A1 |

| Цифровой фазометр | 1984 |

|

SU1234782A1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2174705C2 |

| Устройство для измерения температуры | 1987 |

|

SU1506298A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Преобразователь значения коэффициента модуляции амплитудно-модулированного сигнала в цифровой код | 1986 |

|

SU1370618A1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2109399C1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В НАПРЯЖЕНИЕ | 1987 |

|

RU2056700C1 |

| МНОГОКАНАЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2177637C2 |

THi

f

Авторы

Даты

1982-12-07—Публикация

1981-01-14—Подача