ел

со

9

:о

Изобретение относится к импульсной технике и может быть использовано в измерительной аппаратуре для определения временного положения импульсных сигналов.

Целью изобретения является повышение точности работы устройства определения временного поло 1;ения импульсных сигналов.

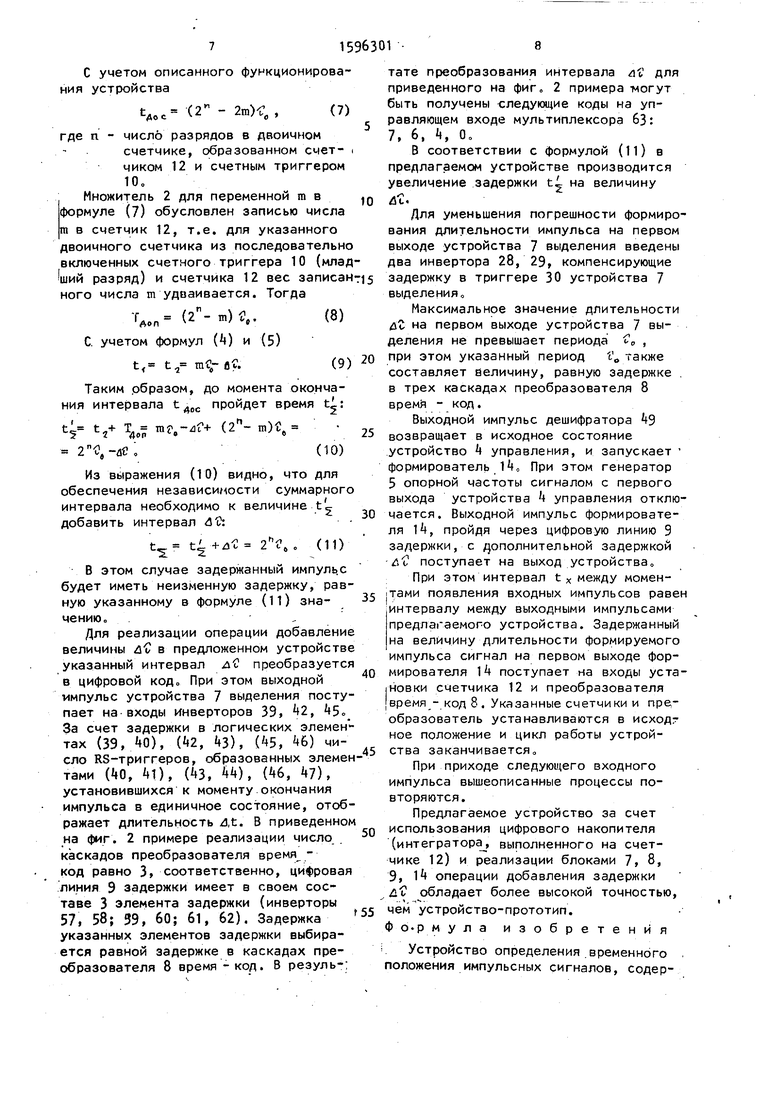

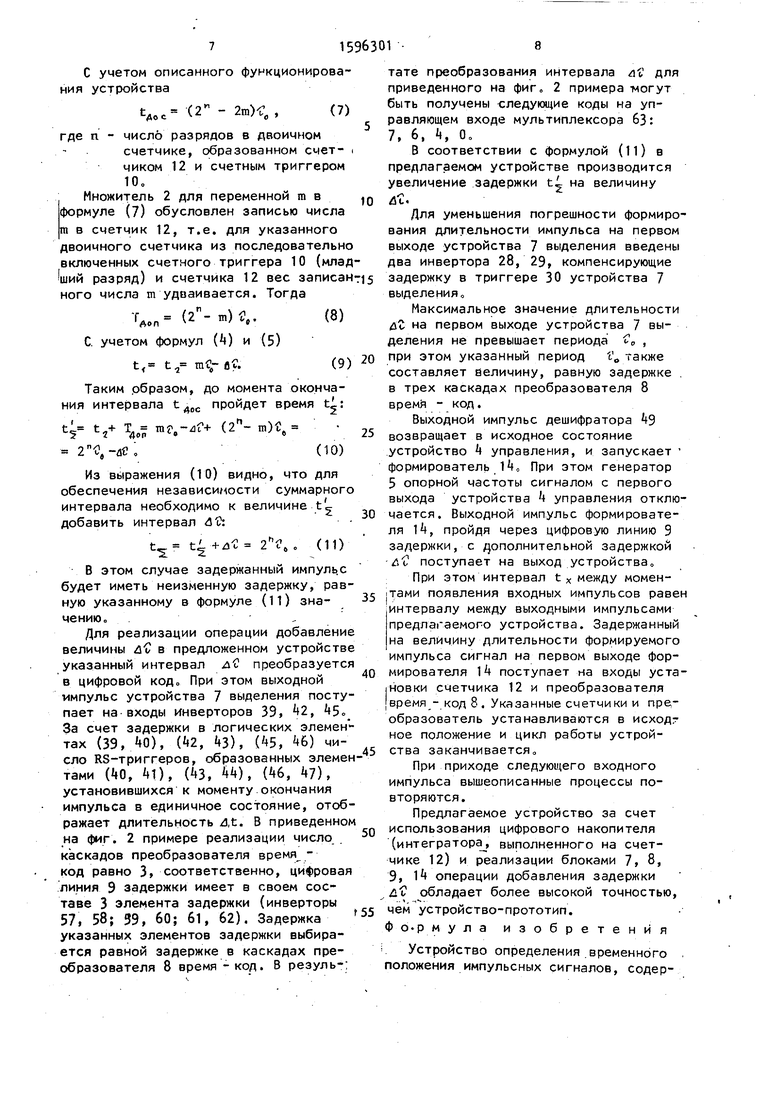

На фиг. 1 представлена функциональная сХема устройства; на фиго 2 - его прийципиальная схема

- Устройство содержит первый компа- . ратор 1, триггер 2, второй компаратор 3, устройство t управления, генератор 5 опорной частоты, делитель 6 напряжения, устройство 7, выделения, преобразователь 8 время - код,цифровую линию 9 задержки, счетный триггер 10, мультиплексор 11, счетчик 12, входную шину 13, формирователь 1А, источник 15 опорного напряжения, выходную шину 16.

Входная шина 13 подключена к первому входу первого компаратора 1 и к входу делителя 6 напряжения, выход которого подключен к. первому входу второго компаратора 3. Выход источника 15 опорного напряжения подключен к вторым входам первого и второго компараторов 1 и 3ч выходы которых подключен ны соответственно к первому и второму входам триггера 2, выход которого подключен к первым входам устройства 7 выделения и устройства управления, первый выход которого подключен к входу генератора 5 опорной частоты, выход которого подключен к первому информационному входу мультиплексора 11, счетному входУ счетного триггера 10 и к второму входу устройства 7 выделения, вход сброса которого подключен к второму выходу устройства управления, Первый, второй и третий выходы устройства 7 выделения подключены соответственно к входу преобразователя 8 время -код, к управляющему входу мультиплексора 11 и к входу сброса счетного триггера 10, выход которого подключен к второму информационному входу мультиплексора 11, выход которого подключен к счетному входу счетчика 12, выход переполнения которого подключен к второму входу устройства k управления /и к входу формирователя И, первый выход которого подключен к вхбдам сброса счетчика 12 и преобразователя

8 время -код,выход которого подключен к управляющему входу цифровой линии 9 задержки, информационный вход которой подключен к второму выходу формирователя 1. Выход цифровой линии 9 задержки является выходной шиной 1б устрОЙСТВЗо

Источник 15 опорного напряжения (фиг. 2) выполнен на потенциометре 17 подключенном к выводам источника питания Делитель 6 напряжения состоит из последовательно включенных резисторов 18 и 19. Первый и второй компараторы 1 и 3 выполнены соответственно на пороговых элементах 20, 21 , например на триггерах Шмидта. Триггер 2 состоит из D-триггера 22, D-гвход которого соединен с общей шиной.

Устройство 4 управления содержит D-триггеры 23, 2k, D-входы которых соединены с общей шиной, а также инверторы 25, 26

Устройство 7 выделения содержит элемент И 27, инверторы 28, 29 и D-триггер 30.

Генератор 5 опорной частоты выполнен по схеме с запаздывающей отрицательной обратной связью и содержит кольцевую цепочку инверторов 31, 32, 33 и буферный инвертор 3, включенный на выходе 35-генератора 5 опорной частоты.

Счетный триггер 10 реализован на Ь-триггере 36 с внешней связью его D-входа с его инверсным выходом.

Мультиплексор 11 содержит инвертор 37 и собственно коммутатор, выполненный на элементе 2И-2ИЛИ-НЕ 38.

Преобразователь 8 время - код содерг жит инвертор 39, элементы И-НЕ 0,1, инвертор k2, элементы И-НЕ , kk, инвертор 45 и элементы И-НЕ , 7„

Счетчик 12 с выходом переполнения выполнен на двоичном счетчике 8 с разрядными выходами и дешифраторе kS, выполненном на элементе И-НЕ с числом входов, равных числу выходов счетчика

формирователь И содержит триггер с раздельными установочными входами, выполненный на элементах И-НЕ 50 и 51, инверторы 52, 53, 5, времязадающий конденсатор 55 и резистор 5бо

Цифровая линия задержки состоит из трех последовательно включенных элементов задержки, образованных соответственно парами инверторов 57, 59, 60j 61, 62 и мультиплексора 63. Устройство работает следующим образом. В исходном состоянии триггер 2 находится в состоянии логического нуля, генератор 5 опорной частоты закрыт. На .первом и втором выходах устройства 7 выделения действует уровень логичес кого нуля, преобразователь 8 время код при этом закрыт и установлен в исходное состояние. На счетном входе счетчика 12 импульсы отсутствуют, так как мультиплексор 11 закрыт. На выходе дешифратора 9 импульсы также отсутствуют, в связи с чем на выход цифровой линии 9 задержки импульсные сигналы не поступают. В результате на выходе счетного триггера 10 присутствует уровень логического нуля. С выхода источника 15 опорного напряжения на вторые входы компараторов 1 и 3 подается постоянное напряжение. С приходом на вход устройства импульса входного сигнала начинается работа устройства. Первым при достиже нии входным напряжением опорного уров ня Up срабатывает компаратор 1 и его выходной перепад устанавливает триггер 2 в состояние логической единицы, С задержкой, равной t,, определяемой коэффициентом деления делителя 6 напряжения, равным 2, и крутизной нарастания входного напряжения,появляется перепад напряжения на выходе компаратора 3, который устанавливает триггер 2 в исходное состояние. При этом на выходе триггера 2 формируется импульс длительностью t,, В рассматриваемом случае предполагается линейность нара стания входного напряжения« С учетом изложенного могут быть записаны следующие соотношения: К - У2 Г t, к,/к, где К,, соответственно крутизна нарастания входного напряжения компаратора 1 и компаратора 3. Соотношение (k) определяет дальнейшую обработку выходного импульса триггера 2.длительностью t. Указанны импульс своим передним фронтом запускает устройство 4 управления, триггер 23, который устанавливает триггер 2j B состояние логической единицы.,-Логический инверсного выхода триггера 2 через два инвертора 25, 26 возвращает триггер 23 в исходное состояние. На выходе генератора 5 опорной частоты формируются импульсы. На втором выходе устройства t управления формируется короткий импульс, КСЦТОРЫЙ устанавливает триггер 30 в устройстве 7 выделения в состояние логического нуля на третьем выходе (инверсный выход триггера 30). Выходной импульс триггера 2 одновременно поступает на D-вход триггера 30 уст-; ройства 7 выделения Ближайший к моменту окончания импульса с выхода триггера 2 синхронизирующий перепад на выходе генератора 5 опорной частоты возвращает триггер 30 устройства 7 выделения в исходное состояние. При этом на выходе инвертора 37 (pea-лизует функцию.И-НЕ для негативной логики) формируется импульс длительностью Лс . Обозначив через m число периодов генератора опорной,частоты, попавших на интервал (t + C), запишем (t, ) , (5) При нахождении триггера 30 устройства 7 выделения в состоянии логической единицы на вход счетчика 12 проходят m импульсов. После переключения триггера 30 в нулевое состояние ранее удерживаемый в нулевом состоянии сигналом с третьего выхода устройства. 7 «вьщеления счетный триггер 10 разблокируется, мультиплексор 11 открывается по второму информационному входу. Происходит досчет счетчика 12 до заполнения импульсами поделенной частоты с выхода муг|ьтиплексора 11 . Дешифратор 9 в данном случае срабатывает при поступлении на вход счетчика 12 переполняющего импульса. Импульс переполнения с выхода дешифратора 9 возвращает устройство k управления в исходное состояние и запускает формирователь И. Очевидно, что интервал Т Доп о -AOC - время досчета счетчика t2 после включения в работу счетного триггера 10, с учетом описанного функционирования устройства (2 - 2тК„, (7) где п - число разрядов в двоичном счетчике, образованном смет- i чином 12 и счетным триггером 10, Множитель 2 для переменной га в формуле (7) обусловлен записью числа га в счетчик 12, т.е. для указанного двоичного счетчика из последовательно включенных счетного триггера 10 (млад ший разряд) и счетчика 12 вес записан ного числа m удваивается. Тогда Глоп ().. (8) С. учетом формул () и (5) t, t, mC-fiC. (9) Таким образом, до момента окончания интервала t пройдет время 4 Ч 40 mr. ( in)l), ,-dCl(10) Из выражения (10) видно, что для обеспечения независимости суммарного интервала необходимо к величине tL добавить интервал ЛС: t4 + 21 s: s в этом случае задержанный импуль.с будет иметь неизменную задержку, равную указанному в формуле (11) значению. Для реализации операции добавление величины dC в предложенном устройстве указанный интервал С преобразуется в цифровой коДо При этом выходной импульс устройства 7 выделения поступает на входы инверторов 39, 2, S За счет задержки в логических элементах (39, to), (2, k3}, (45, tb) число RS-триггеров, образованных элемен тами (ЦО, А1), (3, А4), (46, it7), установившихся к моменту окончания импульса в единичное состояние, отображает длительность Дt. В приведенном на фиг. 2 примере реализации число . каскадов преобразователя время код равно 3, соответственно, цифровая линия 9 задержки имеет в своем составе 3 элемента задержки (инверторы 57, 58; 39, 60; 61, 62). Задержка указанных элементов задержки выбирается равной задержке в каскадах преобразователя 8 время -код. В резуль-; тате преобразования интервала aS для приведенного на фиг, 2 примера -могут быть получены следующие коды на управляющем входе мультиплексора 63: 7, 6, i, 0„ В соответствии с формулой (П) в предлагаемом устройстве производится увеличение задержки t на величину Для уменьшения погрешности формирования длительности импульса на первом выходе устройства 7 выделения введены два инвертора 28, 29, компенсирующие задержку в триггере 30 устройства 7 выделения Максимальное значение длительности uZ на первом выходе устройства 7 выделения не превышает периода , при этом указанный период „ также составляет величину, равную задержке . в трех каскадах преобразователя 8 время - код. Выходной импульс дешифратора tS возвращает в исходное состояние устройство k управления, и запускает формирователь Ifо При этом генератор 5 опорной частоты сигналом с первого выхода устройства 4 управления отключается. Выходной импульс формирователя l4, пройдя через цифровую линию 9 задержки, с /дополнительной задержкой йс поступает на выход устройства. При этом интервал t между момен1тами появления входных импульсов равен интервалу между выходными импульсами предлагаемого устройства. Задержанный на величину длительности формируемого импульса сигнал на первом выходе формирователя 1 поступает на входы устаНовки счетчика 12 и преобразователя время -кол 8. Указанные счетчики и преобразователь устанавливаются в исходг ное положение и цикл работы устройства заканчивается При приходе следующего входного импульса вышеописанные процессы повторяются. Предлагаемое устройство за счет использования цифрового накопителя (интегратора, выполненного на счетчике 12) и реализации блоками 7, В, 9, I операции добавления задержки Л обладает более высокой точностью, чем устройство-прототип. о-р м ула изобретения Устройство определения.временного , оложения импульсных сигналов, содер

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1982 |

|

SU1119050A1 |

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1255984A2 |

| Цифровой регистратор повторяющихся сигналов | 1987 |

|

SU1610279A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1720160A1 |

| Преобразователь код-напряжение | 1988 |

|

SU1508348A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| Преобразователь кода во временной интервал | 1980 |

|

SU1007054A1 |

Изобретение относится к импульсной технике и служит для повышения точности работы устройства определения временного положения импульсных сигналов. Цель изобретения достигается за счет введения в устройство триггера 2, устройства 4 управления, генератора 5 опорной частоты, устройства 7 выделения, преобразователя 8 время-код, цифровой линии 9 задержки, счетного триггера 10, мультиплексора 11, счетчика 12, источника 15 опорного напряжения и новых функциональных связей. Кроме того, устройство содержит первый и второй компараторы 1 и 3, делитель 6 напряжения и формирователь 14. Повышение точности происходит в результате дискретной реализации интегратора, выполненного на счетчике 12, и введения поправки во временное положение выходного сигнала устройства, обусловленной случайным моментом срабатывания второго компаратора 3 в течение тактового интервала генератора 5 опорной частоты. 2 ил.

| Устройство для определения момента формирования стандартного импульса | 1985 |

|

SU1257603A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-09-30—Публикация

1988-11-09—Подача