(54) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ

f

Изобретение относится к вычислительной технике и может ейлть использовано для выполнения операций сложения и вычитания двсдачных данных по модулю 2-1 (п - целое, болыаее единицы).

Известно устройство для сложения чисел, состоящее из двух суглматоров и мультиплексора и позволяющее получить сумму двух чисел, представленных в системе остаточных классов остатками (2llJ и I bmodC2 -l), при этом операция суммирования выполняется на двух сумматорах одноврег менно, причем на первом сумматоре выполняется действие , на втором K+I-p ( модуль), при этом за истинный принимается результат одного из этих сумматоров в згшисимости от знака результата второго суглматора 1 .

Недостатком устройства является невысокое быстродействие за счет того, что операция К+1-р осуществляется путем последовательного включения сумматоров.

Наиболее близким к данному изобретению техническим решением является устройство для обработки данйых в системе остаточных классов по модулю , в котором используется п-разрядный сумматбр, на одни входы которого подается сигнал (, на другие - сигнал () ,при-; чем выход переноса старшего разряда связан со входом переноса младшего разряда, выходы сумматора связаны со входами п-входовой И-НЕ и первыми входами п двухвходовых схем

10 И, выходы KOTOfftix являются выходами устройства, вторые входы двухвходовых схем И связаны с выходом И-НЕ.Сигналы К и I могут подаваться на вход сумматора как в прямом, так

15 и в инверсном виде, что позволяет с помощью указанного устройства осугществлять опергщии сложения,вычитания, кодирования и декодирования сигналов по модулю 21

20

Однако, это устройство не позволяет повысить быстродействие по сравнению с предыдущим устройством,так как хотя операции суммирования проводятся на одном сумматоре, но они 25 выполняются (учитывая перенос) последовательно два раза.

Цель изобретения - повышение быстродействия .

Поставленная цель достигается тем,

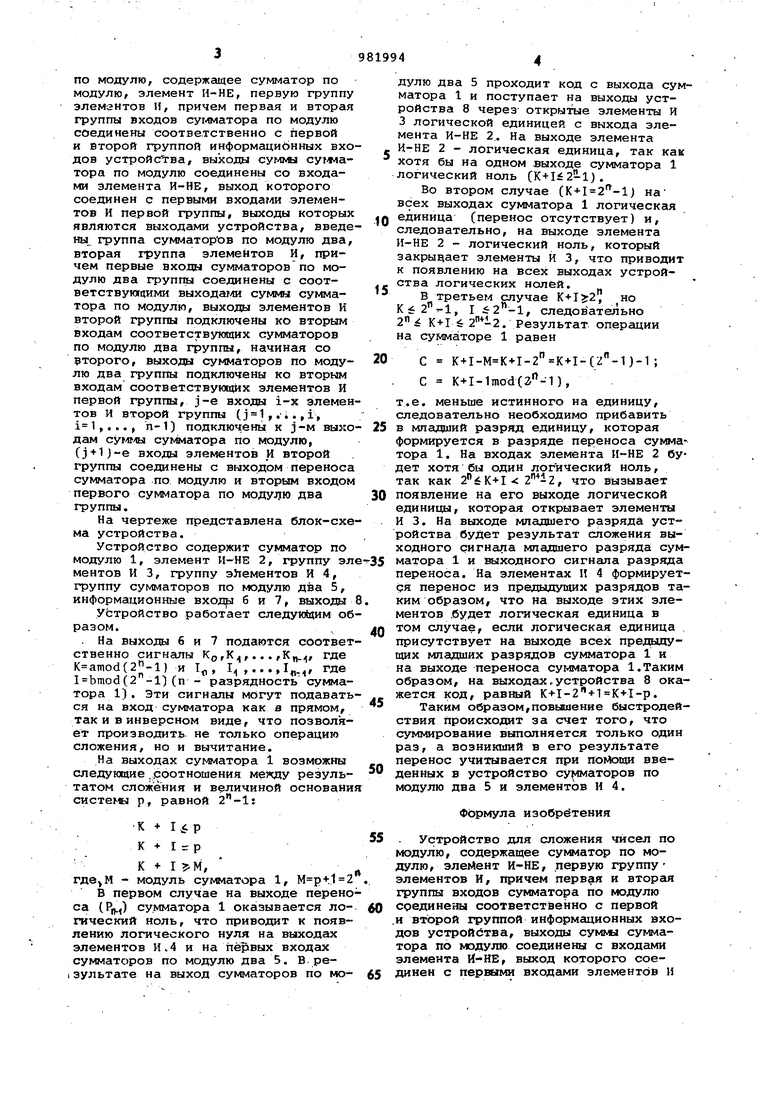

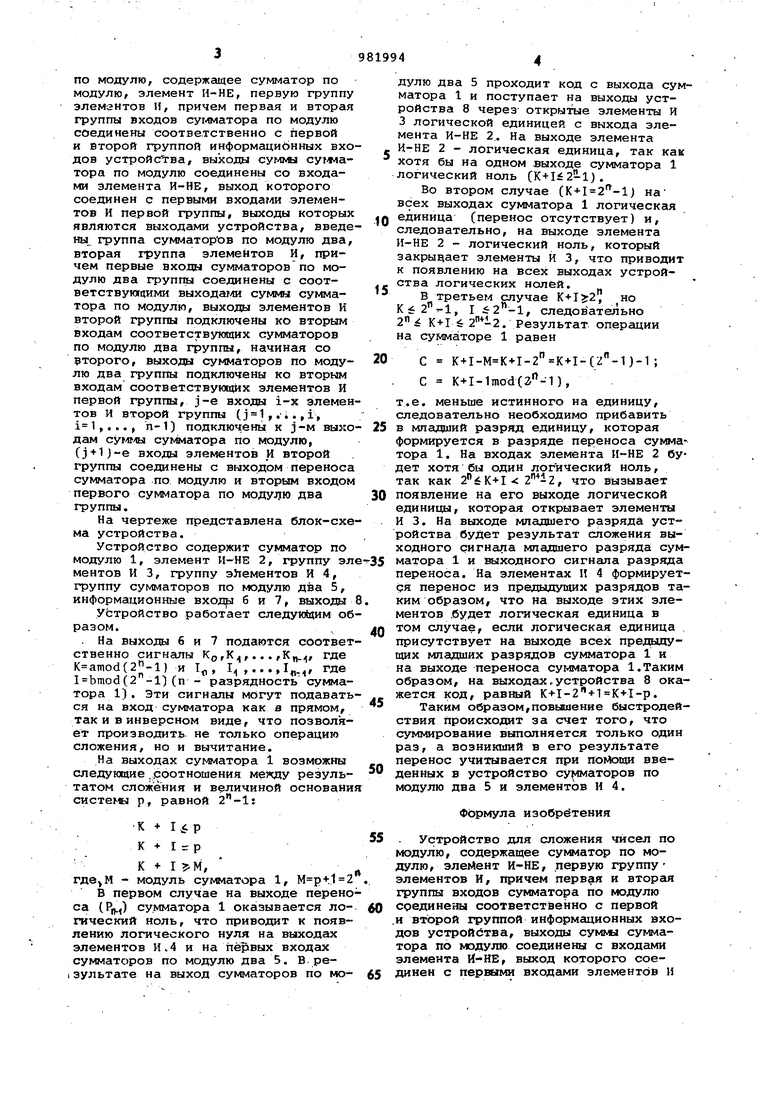

30 что в устройство для сложения чисел по модулю, содержащее сумматор по модулю элемент Н-НЕ, первую группу эяемгнтов И, причем первая и вторая группы входов сугиматора по модулю соединены соответственно с первой и второй группой информационных вхо дов устройсгва, выходы сумматор а по модулю соединены со входами элемента И-НЕ, выход которого соединен с первыми входами элементов И первой группы, выходы которых являются выходами устройства, введе ны группа сумматоров по модулю два, вторая группа элемейтов И, причем первые входы сумматоров по модулю два группы соединены с соответствующитют выходаг/ш суммы сумматора по модулю, выходы элементов И второй группы подключены ко вторым входам соответствующих сумматоров по модулю два группы, начиная со второго, выходы сумматоров по модулю два группы подключены ко вторым входам соответствующих элементов И первой группы, j-e входы i-x элемен тов И второй группы (,.i.,i, i,... п-1) подключены к j-м выхо дам cyfaia сугшат:ора по модулю, Cj-«-1J-e входы элементов И второй группы соединены с выходом переноса сумматора по модулю и вторым входом первого сумматора по MOjayj v) два группы. На чертеже представлена блок-схе ма устройства. Устройство содержит сумматор по модулю 1, элемент Н-НБ 2, группу эл ментов ИЗ, группу элементов И 4, группу сумматоров по модулю два 5, информационные входа б и 7, выходы уЬтройство работает следую1чим об разом. . На выходы 6 и 7 подаются соответ ственно сигналы K(j,K,... ,К,, где (2j|-l) и 1 , 1,...,„.,, где (2 -1)(п - разрядность сумматора 1) . Эти сигналы могут подавать ся на вход сумматора как в прямом, так и в инверсном виде, что позволяет производить не только операцию сложения, но и вычитание. На выходах сумматора 1 возможны следующие ..соотношения между результатом сложения и величиной основани системы р, равной К I.C.P К + I р К + I 9.М, - модуль сумматора 1, В первом случае на выходе перено са (Р) сумматора 1 оказывается логический ноль, что приводит к появлению логического нуля на выходах элементов и на первых входах сумматоров по модулю два 5. В. реi зультате на выход сумматоров по модулю два 5 проходит код с выхода сумматора 1 и поступает на выходы устройства 8 через открытые элементы И 3 логической единицей с выхода элемента И-НЕ 2.. На выходе элемента И-НЕ 2 - логическая единица, так как хотя бы на одном выходе сумматора 1 логический ноль CK+Ii2-l). Во втором случае ( ) на всех выходах сумматора 1 логическая единица (перенос отсутствует) и, следовательно, на выходе элемента И-НЕ 2 - логический ноль, который закрывает элементы И 3, что приводит к появлению на всех выходах устройства логических нолей. В третьем случае но , Г , следов ательно K+I . Результат операции на cy 4мaтope 1 равен С K+I-M K-t-I-2 K+I-()-1 ; С K+I-1mod(), т.е. меньше истинного на единицу, следовательно необходимо прибавить в младший разряд единицу, которая формируется в разряде переноса сумматора 1. На входах элемента И-НЕ 2 будет хотя бы один логический ноль, так как 2бК- -1 , что вызывает появление на его выходе логической единицы, которая открывает элемен-пл И 3. На выходе младшего разряда устройства будет результат сложения выходного сигнала младшего разряда сумматора 1 и выходного сигнала разряда переноса. На элементах И 4 формируетдя перенос из предыдущих разрядов таким образом, что на выходе этих элементов .будет логическая единица в том случае, если логическая единица присутствует на выходе всех предадущих младших разрядов сумматора 1 и на выходе переноса суг-матора 1. Таким образом, на выходах,устройства 8 окажется код, равный К- -1-2 + 1 К+1-р. Таким образом,повышение быстродействия происходит за счет того, что суммирование выполняется только один раз, а возникший в его результате перенос учитывается при по1)щи введенных в устройство су аторов по модулю два 5 и элементов И 4. Формула изобретения Устройство для сложения чисел по модулю, содержащее сумматор по модулю, элемент И-НЕ, первую группу элементов И, причем первая и вторая группы входов сумматора по модулю соединены соответственно с первой и второй группой информационных входов устройства, выходы суммы сумматора по модулю соединены с входами элемента Й-НЕ, выход которого соединен с первыми входами элементов И

,первой группы, выходы которых являются выходами устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит группу сумматоров по модулю два, вторую группу элементов И, причем первые входы сумматоров по модулю два группы соединены с соответствующими выходами суммыг сумматора по мо дулю, выходы элементов И второй группы под1слючены к вторым входам соот1ветствующйх сумматоров по модулю два группы, начиная с второго выiхода сумматоров по модулю два группы подключены к вторым, входам соот981994

ветствующих элементов И первой группы, j-e входы i-x элементов И второй группы (j 1,.,.,i; ,...,n-1) подключены к j -м выходам суммл. сумматора по модулю, {j +1.) -е входы элементов И второй группы соединены с выходом переноса сумматора по гюдулю и вторым входе первого сумматора по модулю два группы.

Источники информации, принятые во внимание при экспертизе

1,Патент Великобритании №1513101, кл. G 4 А, опублик. 1979. ,

2. Патент США 4187549,кл.346-176, опублик. 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКАПЛИВАЮЩИЙ СУММАТОР-ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2021 |

|

RU2764876C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ОТ ЧИСЛА | 2000 |

|

RU2209460C2 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления | 1991 |

|

SU1784974A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2021632C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР-ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2021 |

|

RU2763988C1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Матричное устройство для умножения чисел по модулю 2 @ -1 | 1985 |

|

SU1254471A1 |

Авторы

Даты

1982-12-15—Публикация

1981-04-10—Подача