Х| СО СА СЛ ГО ГО

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих арифметических уст- poucfBax выполнения операции деления.

Известно устройство для деления, содержащее регистры делимого, делителя и частного, блок деления усеченных чисел, два узла коррекции частного, блок умножения, два вычитателя, сумматор-вычитатель, коммутатор и блок управления,

В данном устройстве в блок деления усеченных чисел поступает (k+ 1) разрядов делимого и делителя. За один такт формируется k-разрядное число. Недостатком этого устройства является низкое быстродействие, вызванное большим временем срабатывания блока деления усеченных чисел.

Наиболее близким по технической сущности к изобретению является устройство для деления, содержащее регистры делимого, делителя и частного, блок деления усеченных чисел, формирователь цифр частного (в прототипе он называется узлом коррекции частного), блок умножения, два вычитателя, группу сумматоров-вычмтате- лей (в прототипе она состоит из двух сумма- торов-вычитателей), коммутатор и блок управления, причем вход данных устройства соединен с информационными входами первой группы коммутатора и с информационными входами регистра де- дителя, выходы которого соединены с входами первой группы блока умножения, выходы коммутатора соединены с информационными входами регистра делимого, выходы старших разрядов которого соеди- ены с входами делимого блока деления усеченных чисел, входы делителя которого соединены с выходами старших разрядов регистра делителя, выходы регистра делимого соединены с входами уменьшаемого первого вычитателя, входы вычитаемого и заема которого соединены с выходами первой и второй групп блока умножения соответственно, выходы разности и заема первого вычитателя соединены с входами уменьшаемого и вычитаемого второго вычитателя соответственно, выход знакового разряда которого соединен с первым управляющим входом формирователя цифр частного, с управляющими входами сумма- торов-вычитателей группы и первым входом блока управления, выходы второго вычитателя соединены с входами первого слагаемого каждого сумматора-вычитателя группы и с информационными входами второй группы коммутатора, информационные

входы остальных групп которого соединены с выходами соответствующих сумматоров- вычитателей группы, выходы блока деления усеченных чисел соединены с входами второй группы блока умножения и информационными входами формирователя цифр частного, выходы которого соединены с информационными входами регистра частного, синхровход которого соединен с входом

синхронизации устройства и с синхровхода- ми регистров делимого и делителя и блока управления, первый выход которого соединен с первым управляющим входом коммутатора, второй и третий выходы блока

управления соединены с входами разрешения записи регистров делимого и делителя соответственно, выходы регистра делителя соединены с входами второго слагаемого первого и второго сумматоров-вычитателей,

выходы знакового разряда которых соединены с вторым и третьим управляющими входами формирователя цифр частного и вторым и третьим входами блока управления.

В данном устройстве в блок деления

усеченных чисел поступает k разрядов делимого и делителя. За один такт формируется k-разрядное частное. По сравнению с предыдущим устройством

данное устройство обладает большим быстродействием, так как в блок деления усеченных чисел поступает меньшее количество разрядов делимого и делителя, и поэтому время его срабатывания меньше. Однако быстродействие данного устройства сравнительно низкое, что является его недостатком.

Цель изобретения - повышение быстродействия устройства за счет получения в каждом такте его работы большего количества цифр частного при той же длительности такта.

Поставленная цель достигается тем, что

в устройство для деления, содержащее регистры делимого, делителя и частного, блок деления усеченных чисел, формирователь цифр частного, блок умножения, два вычитателя, группу сумматоров-вычитателей,

коммутатор и блок управления, причем вход данных устройства соединен с информационными входами первой группы коммутатора и с информационными входами регистра делителя, выходы которого соединены с

входами первой группы блока умножения, выходы коммутатора соединены с информационными входами регистра делимого, выходы старших разрядов которого соединены с входами делимого блока деления усеченных чисел, входы делителя которого соединены с выходами старших разрядов регистра делителя, выходы регистра делимого соединены с входами уменьшаемого вычитателя, входы вычитаемого и заема которого соединены с выходами первой и второй групп блока умножения соответственно, выходы разности и заема первого вычитателя соединены с входами уменьшаемого и вычитаемого второго вычитателя соответственно, выход знакового разряда которого соединен с управляющим входом формирователя цифр частного и с управляющими входами сумматоров-вычи- тателей группы, выходы второго вычитателя соединены с входами первого слагаемого каждого сумматора-вычитателя группы и с информационными входами второй группы коммутатора, информационные входы остальных групп которого соединены с выходами соответствующих сумматорое- вычитателей группы, выходы блока деления усеченных чисел соединены с входами второй группы блока умножения и информаци- онными входами первой группы формирователя цифр частного, выходы которого соединены с информационными входами регистра частного, синхровход которого соединен с входом синхронизации устройства и с синхровходами регистров делимого и делителя и блока управления, первый выход которого соединен с первым управляющим входом коммутатора, второй и третий выходы блока управления соединены с входами разрешения записи регистров делимого и делителя соответственно, введен формирователь дополнительных цифр частного и формирователь кратных, информационные входы которого соединены с выходами регистра делителя, входы второго слагаемого каждого сумматора-вычитателя соединены с выходами соответствующей группы формирователя кратных, выход знакового разряда второго вычитателя соединен с первым входом формирователя дополнительных цифр частного, остальные входы которого соединены с выходами знакового разряда соответствующих сумматоров-вычитателей группы, выходы первой группы формирователя дополнительных цифр частного соединены с информационными входами второй группы формирователя цифр частного, выходы второй группы формирователя дополнительных цифр частного соединены соответственно с остальными управляющими входами коммутатора.

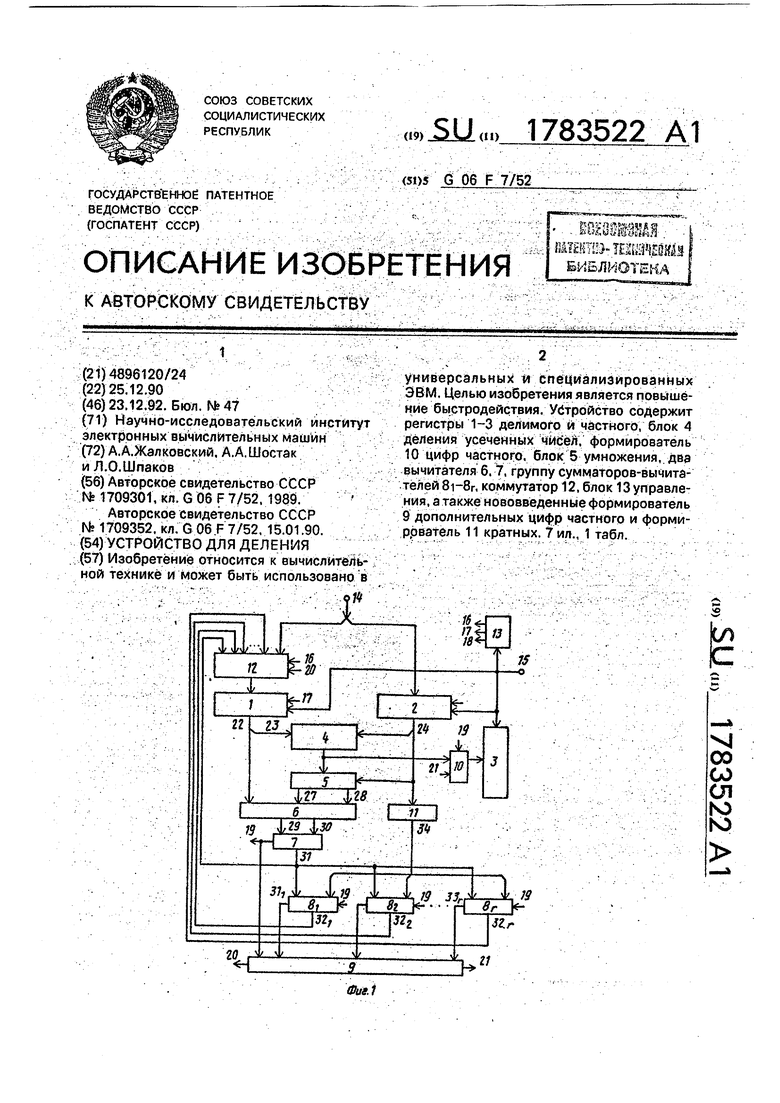

На фиг. 1 приведена структурная схема устройства для деления; на фиг. 2 - функциональная схема формирователя дополнительных цифр частного для конкретного случая; на фиг. 3 - функциональная схема формирователя цифр частного для конкрет- 5 ного случая; на фиг, 4 - структурная схема формирователя кратных для конкретного случая; на фиг. 5 - функциональная схема одного разряда коммутатора для конкретного случая; на фиг. 6 - структурная схема

10 блока деления усеченных чисел; на фиг. 7 - структурная схема блока управления.

Устройство для деления (фиг. 1) содержит регистры 1-3 соответственно делимого, делителя и частного, блок 4 деления усечен15 ных чисел, блок 5 умножения, первый 6 и второй 7 вычитатели, группу сумматоров- вычитателей 81-8г(где г- количество сумматоров-вычитателей, необходимых для получения конкретного количества цифр

0 частного за один такт), формирователь 9 дополнительных цифр частного, формирователь 10 цифр частного, формирователь 11 кратных, коммутатор 12, блок 13 управления, вход 14 данных устройства и вход 1S

5 синхронизации устройства. Вход 14 данных устройства соединен с информационными входами первой группы коммутатора 12 и с информационными входами регистра 2 делителя, выходы которого соединены с ехо0 дами первой группы блока 5 умножения и с информационными входами формирователя 11 кратных, выходы коммутатора 12 соединены с информационными входами регистра 1 делимого, выходы 23 старших

5 разрядов которого соединены с входами делимого блока 4 деления усечённых чисел, входы делителя которого соединены с выходами 25 старших разрядов регистра 2 делителя, выходы 22 регистра 1 делимого

Q- соединены с входами уменьшаемого первого вычитателя б, входы вычитаемого и заема которого соединены с выходами первой 27 и второй 28 групп блока 5 умножения соответственно, выходы 29 разности и 30 заема

5 первого вычитателя 6 соединены с входами уменьшаемого и вычитаемого второго вычитателя 7 соответственно, выход 19 знакового разряда которого соединен с управляющим входом формирователя 10

л цифр частного и с управляющими входами сумматоров-вычитателей 8i-8r группы, выходы 31 второго вычитателя 7 соединены с входами первого слагаемого каждого сум- матора-вычитателя 8i-8r группы и с инфорj мационными входами второй группы коммутатора 12, информационные входы с третьей по (г+2)-ю групп которого соединены с выходами соответственно сум- маторов-вычитателей 8i-8r групп, выходы

26 блока 4 деления усеченных чисел соедийены с входами второй группы блока 5 умножения и информационными входами первой группы формирователя 10 цифр частного, выходы которого соединены с информационными входами регистра 3 частного, синхровход которого соединен с входом 15 синхронизации устройства и с синхровходами регистров 1, 2 делимого и делителя и блока 13 управления, первый выход 16 которого соединен с первым управляющим входом коммутатора 12, второй 17 и третий 18 выходы блока 13 управления соединены с входами разрешения записи регистров t, 2 делимого и делителя соответственно, входы второго слагаемого каждого сумматора-вычитателя 8i-8r соединены с выходами 34 соответствующей группы формирователя 11 кратных, выход 19 знакового разряда второго вычитателя 7 соединен с первым входом формирователя 9 дополнительных цифр частного, остальные входы которого соединены с выходами 33i-33r знакового разряда соответствующих сумма- торов-вычитателей 8i-8r группы, выходы 21 первой группы формирователя 9 дополнительных цифр частного соединены с информационными входами второй группы формирователя 10 цифр частного, выходы 20 второй группы формирователя 9 дополнительных цифр частного соединены соответственно с остальными управляющими входами коммутатора 12.

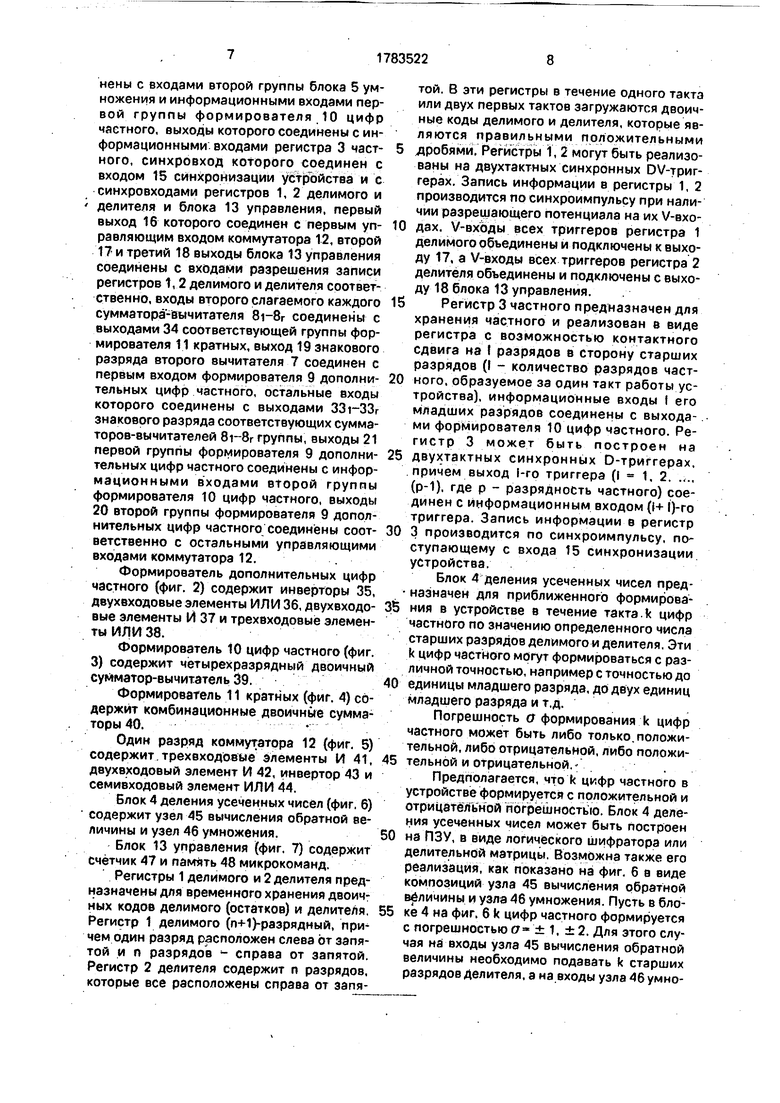

Формирователь дополнительных цифр частного (фиг. 2) содержит инверторы 35, деухвходовые элементы ИЛИ 36, двухвходо- вые элементы И 37 и трехвходовые элементы ИЛИ 38.

Формирователь 10 цифр частного (фиг. 3) содержит четырехразрядный двоичный сумматор-вычитатель 39.

Формирователь 11 кратных (фиг. 4) содержит комбинационные двоичные сумматоры 40.

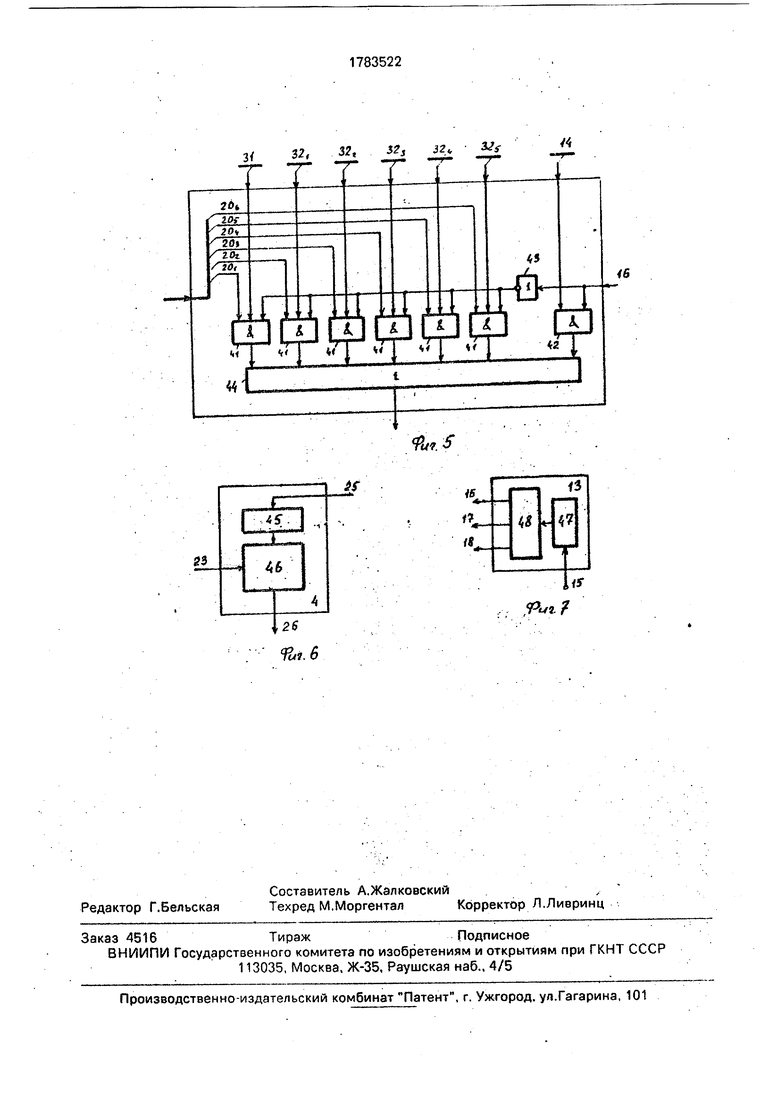

Один разряд коммутатора 12 (фиг. 5) содержит трехвходовые элементы И 41, двухвходовый элемент И 42, инвертор 43 и семивходовый элемент ИЛИ 44.

Блок 4 деления усеченных чисел (фиг. 6) содержит узел 45 вычисления обратной величины и узел 46 умножения.

Блок 13 управления (фиг. 7) содержит счетчик 47 и память 48 микрокоманд.

Регистры 1 делимого и 2 делителя предназначены для временного хранения двоичных кодов делимого (остатков) и делителя. Регистр 1 делимого (п+1)-разрядный, причем один разряд расположен слева от запятой и п разрядов - справа от запятой. Регистр 2 делителя содержит п разрядов, которые все расположены справа от запятой. В эти регистры в течение одного такта или двух первых тактов загружаются двоичные коды делимого и делителя, которые являются правильными положительными

дробями. Регистры 1, 2 могут быть реализованы на двухтактных синхронных DV-триг- герах. Запись информации в регистры 1, 2 производится по синхроимпульсу при наличии разрешающего потенциала на их V-BXOдах. V-входы всех триггеров регистра 1 делимого объединены и подключены к выходу 17, а V-входы всех триггеров регистра 2 делителя объединены и подключены с выходу 18 блока 13 управления.

Регистр 3 частного предназначен для хранения частного и реализован в виде регистра с возможностью контактного сдвига на I разрядов в сторону старших разрядов (I - количество разрядов частного. образуемое за один такт работы устройства), информационные входы I его младших разрядов соединены с выходами формирователя 10 цифр частного. Регистр 3 может быть построен на

двухтактных синхронных D-триггерах.

причем выход 1-го триггера (I 1, 2

(р-1), где р - разрядность частного) соединен с информационным входом (И- }-го триггера. Запись информации в регистр

3 производится по синхроимпульсу, поступающему с входа 15 синхронизации устройства.

Блок 4 деления усеченных чисел пред- назначен для приближенного формирования в устройстве в течение такта k цифр частного по значению определенного числа старших разрядов делимого и делителя, Эти k цифр частного могут формироваться с различной точностью, например с точностью до

единицы младшего разряда, до двух единиц младшего разряда и т.д.

Погрешность О формирования k цифр частного может быть либо только положительной, либо отрицательной, либо положительной и отрицательной.

Предполагается, что k цифр частного в устройстве формируется с положительной и отрицательной погрешностью. Блок 4 деления усеченных чисел может быть построен

на ПЗУ, в виде логического шифратора или делительной матрицы. Возможна также его реализация, как показано на фиг. 6 в виде композиций узла 45 вычисления обратной величины и узла 46 умножения. Пусть в блоке 4 на фиг. 6 k цифр частного формируется с погрешностью a ± 1, ±2. Для этого случая на входы узла 45 вычисления обратной величины необходимо подавать k старших разрядов Делителя, а на входы узла 46 умножения - (k+1) старших разрядов делимого (или остатка) и (k+1) старших разрядов обратной величины.

Для доказательства этого нужно показать, что при делении в блоке 4 деления усеченных чисел значения (k+ 1) старших разрядов делимого X (или остатка) на значение k старших разрядов делителя Y. при условии, что 1/2$ Y 1,0 Х 2Y, а на выходе узла 45 обратной величины форми- руется (k+ t) старших разрядов значения обратной величины, разность между значением k-разрядного частного, сформированным в блоке 4, и значением k старших разрядов частного, полученным при деле- нии полноразрядных чисел, не превышает (по абсолютному значению) величины, равной двум единицам младшего разряда истинного значения частного (вес младшего разряда разрядного частного равен 2

Для этого надо доказать, что

ЯР

X .г okio-l-i - о у z J l у1 - -

где Xi - значение (k+1) старших разрядов делимого X (или остатка);

YI - значение старших разрядов делителя Y;

{А - целая часть числа А;

- масштабный коэффициент, обеспечивающий представление k старших разрядов истинного частного в виде целого числа;

2k - масштабный коэффициент, обеспечивающий представление k+1 старших разрядов значения обратной величины делителя в виде целого числа;

2 - масштабный коэффициент, обеспе- чивающий представление старших разрядов предсказываемого частного в виде целого числа.

Значение младших разрядов делимого X и делителя Y равно Х2 X - Х1 и Y2 Y - Y1 соответственно.

С учетом этого данное неравенство представляют в виде системы неравенств

Анализ левых частей неравенств позволяет заметить, что максимальные значения достигаются: для первого неравенства - при (Y2 Y2min 0, а для второго - приХ2 0. Следовательно, систему неравенств можно переписать следующим образом:

Г

2.

510 15

30

35

40

45

20

25

Производят некоторые эквивалентные преобразования:

г Х1 + Х2 |гП Г XI L-Yl J +

Y1

Х2

Y1

Х1 ok.f

|( Х2 girf

+ { Y1 -,

3где {А} - дробная часть числа А XI # 2- - -g- -Xl j- - - 7K - x1#r2 j f

r(X1 2 fL/X1 ( 1 2 f YI 2 j2 /J-Г- 2 1 i Г IX1 2 J+L(Y1 2 J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления | 1979 |

|

SU773618A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ, Целью изобретения является повышение быстродействия. Устройство содержит регистры 1-3 делимого и частного, блок 4 деления усеченных чисел, формирователь 10 цифр частного, блок 5 умножения, два вычитателя 6.7, группу сумматоров-вычита- телей , коммутатор 12, блок 13 управления, а также нововведенные формирователь 9 дополнительных цифр частного и форми- ррватель 11 кратных. 7 ил., 1 табл.

Х1 +Х2 k-n Y1 -{-Y2J

V

- Ы 1Ы

г Х1 +Х2 кч- L Y1 +Y2J

Y1

.

так как

-{xi{).

{-yj-2kJ-2 Ч 0 при любых допустимых значениях X и Y,

-

Х1

Y1 +Y2

2И +

Х1 Y2

Y1 (Y1 +Y2

,k-, , Г/ Х1 k- У2 +ЦУ1+У2 2 /

Г Х1 Y22k4n

Y1(Y1 +Y2) JJ

С учетом этого систему неравенств мож- . но представить в следущем виде:

Г Х2 gkL Y1

И , Г ГXI „k- l, J + LCYT2 J +

21 - №21 HVr2kj2- } 2

Г X1Y2 2H1 т- LY1(Y1+Y2)Z J

+ г /L-xi2й} 4+ L IYI + Y2 J +

{

Y2 Х1 Y2

Y1 (Y1 +Y2)

-()- .

(х, J2- } Ј2

Так как целая часть суммы двух правиль- 35 ных дробей может быть равна 0 или 1, а целая часть разности двух правильных дробей может быть равна 0 или -1, то для доказательства полученной системы достаточно показать, что40

(

х1 Y2

Y1(Y1 + Y2)

.

Из первого неравенства вытекает, что должно выполняться неравенство Х2 2 Y1, которое справедливо при любых Х2и Y1:

X2max 2k 1(2 k-2 n). 2-1.2k-n-1 Y1m|n s2-1

Из второго неравенства вытекает, что должно выполняться неравенство Х2- Y2 2k 1 2 Y1(Y1 + Y2), которое справедливо при любых XI, Y1 и Y2:

5 0

0

Y2max 2k-1 (2 k-2-n)-2k 1 2-1

- Y1min 2 a X1 2(Y1 + Y2),

что и требовалось доказать.

Таким образом, k-разрядное частное, полученное на выходе блока 4 деления усеченных чисел от деления (k+1) старших разрядов делимого (или остатка) и к старших

0 разрядов делителя, при условии формирования на выходе узла 45 обратной величины (k+1) старших разрядов значения обратной величины, либо равно истинному k-разряд- ному частному, что отличается от него не

5 более чем на две единицы младшего разряда истинного значения k-разрядного частного (вес младшего разряда k-разрядного частного равен .

В блоке .5 умножения осуществляется

0 перемножение k-разрядного частного, сформированного на выходах 26 блока 4 и поступающего на вторую группу входов блока 5, и n-разрядного делителя, хранимого в регистре 2 и поступающего на первую груп5 пу входов блока 5 умножения с выходов 24 регистра 2. На выходах 27 и 28 первой и второй групп блока 5образуется произведение в двухрядном коде (в виде двух чисел). Блок 5 умножения - комбинационного типа

0 и может быть реализован, например, в виде совокупности из n/k k-рэзрядных двоичных умножителей.

Первый вычитатель б - комбинационного типа и выполнен по принципу еычитателя без распространения заема. В вычитателеб осуществляется вычитание из содержимого регистра 1 делимого произведения, сформированного на выходах 27 и 28 блока 5 умножения в двухрядном коде. Результат вычитания образуется на выходах 29 и 30 соответственно разности и заема еычитателя б в двухрядном коде.

Второй вычитатель 7 предназначен для вычитания из значения разности, сформи5 ровэнной на выходах 29 первого еычитателя б, значения заема, образованного на выходах 30 этого же еычитателя 6. Второй вычи- татель 7 - комбинационного типа с ускоренным распространением заема. Он может быть заменен быстродействующим сумматором, если информацию, поступающую на его вход вычитаемого, проинверти- ррвать, а на вход переноса сумматора Подать сигнал логической единицы. Выход

5 19 знакового разряда второго вычитателя 7 соединен с управляющими входами сумма- торов-вычитэтелей группы и формирователя 10 цифр частного, а также с первым входом формирователя 9 дополнительных цифр частного.

Сумматоры-вычитатели группы осуществляют сложение или вычитание двух операндов в зависимости от значения управляющего сигнала на выходе 19 знакового разряда вычитателя 7. Первым операндом для всех сумматоров-вычитателей является промежуточное значение остатка, образованного на выходах 31 второго вычитателя 7. Вторым операндом для сумматора- вычитателя 8t является одинарное значение делителя, сдвинутое на (k+ m-2) разрядов вправо от запятой, т.е. значение Y-2 , где m - количество формируемых в устройстве дополнительных цифр частного. Для сумматоров-вычитателей 82,8з, 84 и т.д. вторым операндом являются соответственно значения МО, , 4,у.2 и т.д. Количество сумматоров-вычитателей 8 группы определяется по формуле ((7тах + 1)-1. где о шах -максимальная по абсолютной величине погрешность формирования в блоке 4 цифр частного. Для определенности при описании предлагаемого устройства предполагают, что k 4. m ш 1 и -2 а 2. Тогда количество сумматоров-вычитателей 8 группы будет равно 5. Сумматоры-вычитатели 8i-8s могут быть построены на основе сумматора с управляемым инвертором на входе подачи второго операнда. В формирователе 9 по значениям знаковых разрядов второго вычитателя 7 и сумматоров-вычитателей 8i-8r образуется m допол- нительных цифр частного, а также корректирующие цифры частного.

Последние алгебраически подсуммиру- ются в формирователе 10 цифр частного к k-разрядному частному, полученному на выходах 26 блока 4.

В результате этого на выходах формирователя 10 получается 1 k+ m цифр частного. Одновременно с этим без каких-либо дополнительных аппаратурных затрат в формирователе 9 образуется унитарный код для управления коммутатором 12. На фиг. 2 приведена функциональная схема одного из вариантов реализации формирователя 9 для принятых выше значений т 1 и Отахш 2. а его таблица истинности представлена ниже.

Первый (самый левый) разряд в колонке выходов 21 первой группы формирователя 9 является самым старшим, а третий разряд - самым младшим. Максимальное значение этого 3-разрядного кода равно пяти. По связям 211 и 21г на выход 21 поступают две корректирующие цифры частного, по связям 21з - одна дополнительная цифра частного. По единичному значению первого (самого левого) разряда в колонке выходов

20 второй группы осуществляется передача через коммутатор 12 информации с выходов 31 второго вычитателя 7, по единичному значению второго разряда - с выходов 32 5 первого сумматора-вычитателя 8i, no единичному значению третьего разряда - с выходов 322 второго сумматорэ-вычитателя 82 и т.д.

Формирователь 10 предназначен для

0 формирования I цифр частного в текущем

такте (фиг. 3). На его информационные вхо ды первой группы поступает k 4 разрядов

частного с выходов 26 блока 4, которые

сформированы с погрешностью а 0, + 1.

5 + 2. На информационные входы второй группы формирователя 10 подаются три цифры частного с выходов 21 формирователя 9, причем две старшие из них (связи 211 и 212) являются корректирущими и поступа0 ют на младшие разряды сумматора-вычитателя 39, а младшая цифра (связь 21з) является дополнительной. Она присовокупляется к цифрам частного со стороны самого младшего разряда.

5 Сумматор-вычитатель 39 настраивается управляющим сигналом либо на сложение, либо на вычитание при значениях соответственно логического нуля и логической единицы с выхода 19 знакового разряда

0 второго вычитателя 7. На выходах формирователя 10 образуется точное значение t k+m цифр частного.

Формирователь 11 кратных предназначен для формирования кратных значений

5 делителя. На фиг. 4 изображена структурная схема формирователя 11 для пяти кратных значений делителя, которые необходимы при принятых допущениях: -2 $ а 2, т 1. Одно-, двух- и четырехкратные Знамения де0- лителя формируются посредством монтажа, трехкратное значение формируется путем сложения одно- и двукратного значений делителя на первом сумматоре 40, а пятикратное значение делителя формируется путем

5 сложения одно- и четырехкратного значений делителя на втором сумматоре 40.

Коммутатор 12 предназначен для передачи на информационные входы регистра 1 делимого информации с (г+2)-х направлений

0 г - количество сумматоров-вычитателей 8) через соответствующие группы входов. Функциональная схема одного разряда коммутатора 12 для случая, когда г 5, показана на фиг. 5. Для его работы необходи5 мо (г+ 2) управляющих входов. (г+1)-разрядный унитарный код с выходов 20 формирователя 9 управляет подачей информации с выходов 31. 321, 32а. 32з. 324. 32г только в случае, если значение упрэвляющего сигнала с первого выхода 16 блока 13 управления равно нулю. В противном случае информация в регистр 1 делимого посту- пает с информационного входа 14 устройства.5

Блок 13 управления координирует работу узлов и блоков устройстёа приГвыполне- нии в нем операции деления двух чисел. Он может быть реализован самыми р азличиы- ми методами и средствами. На фиг. 7 прибё- 10 дена структурная схема возможной реализации блока 13 на основе счетчика 47 и памяти 48 микрокоманд. Счетчик 47 - накапливающего типа и предназначен для естественной адресации микрокоманд. Вход 15 счета счетчика соединен с входом 15 синхронизации устройства. В качестве памяти 48 микрокоманд может быть применена быстродействующая постоянная память емкостью 3t, где t - число тактов работы 20 устройства. В самом начале работы устройства счетчик 47 устанавливается 8 некоторое исходное состояние, например сбрасывается в ноль (на фиг. 7 цепь установки счетчика 47 в исходное состояние не по- 25 казана).

Устройство работает следующим образом. Перед началом выполнения собственно деления в регистр 1 делимого и регистр 2 делителя заносится n-разрядный код де- 30 лимогои n-разрядный код делителя соответственно, счетчик 47 блока 13 управления устанавливается в исходное состояние (делимое загружается в п младших разрядов регистра 1, в старший разряд которого за- 35 писывается ноль). Предполагается, что делимое и делитель - правильные положительные нормализованные дроби Процесс определения р-разрядного частного состоит из р/ тактов, в каждом из 40 которых формируется I двоичных цифр ча- стного.

Для упрощения пояснения работы устройства предполагают, что к 4, т 1 и -2 7 2. Тогда, как указывалось ранее, ко- 45 личество г сумматоров-вычитателей 8 равно пяти и общее число формируемых в такте цифр частного I k+m - 5.

Каждый такт начинается с определения 4-разрядного частного в блоке 4 с погреш- 50 ностью ст. На входы блока 4 (см. фиг. 6) при этом поступает значение (k+1) старших разрядов делимого (один разряд слева от запятой, остальные справа от запятой) и значение k старших разрядов делителя (все 55 разряды расположены справа от запятой) Затем 4-разрядное частное, образованное на выходах 26 блока 4, умножается на п-раэ- рядный делитель в блоке 5 умножения, а на

выходах 31 вычитателя 7 через время, равное времени срабатывания первого 6 и второго 7 вычитателей, образуется промежуточное значение остатка, равное разности между предыдущим остатком и полученным произведением. Положительный знак этого промежуточного значения остатка означает, что 4-разрядное частное сформировано либо точно, либо с недостатком. Поэтому в этом случае логический ноль с выхода 19 знакового разряда второго вычитателя 7 настраивает сумматоры-вычита- тели на вычитание соответствующих кратных значений делителя из промежуточного значения остатка, а сумматор-вы- читатель 39 формирователя 10 - на сложение.

По комбийаЦии значений знаковых разрядов сумматоров-вычитателей 8i-8s можно судить о разнице между истинным значением 4-разрядного частного и полученным значением 4-разрядного частного на выходах 26 блока 4 и одновременно определить дополнительную пятую младшую цифру частного в данном такте. Так, например, если значения выходов знакового разряда сумматоров-бычитателей 81-85 равны соответственно О, О, О, 1, 1, то значение k-разрядного частного, сформированного на выходах 26 блока 4, меньше истинного k-рэзрлдного частного на единицу младшего разряда (на выходы двух младших разрядов сумматора-вычитателя 39 по линиям связи 21г, 212 подается двоичный код 01, который подсуммируется к k-разрядному частному, сформированному в блоке 4). Значение дополнительной цифры частного, которая поступает в формирователь 10 по линии связи 21з и присовокупляется к k-разрядному со стороны самого младшего разряда, равно единице. На выходах 20 формирователя 9 одновременно будет образован унитарный код 000100, по которому в регистр 1 делимого через коммутатор 12 запишется со сдвигом влево на пять разрядов значение остатка с выходов 32з сум- матора-вьТчитэтеля 8з. Если же промежуточное значение остатка на выходах 31 второго вычитателя 7 имеет отрицательный знак (т.е. единичное значение сигнала на выходе 19), то сумматоры-вычи- татели 81-85 группы настраиваются на сложение промежуточного значения остатка с кратными делителя, а сумматор-вычитатель 39 формирователя 10 - на вычитание Если, например, значения выходов знаковых разрядов сумматоров-вычитателей 81-85 равны соответственно 1. 1, О, О, О, то значение k-разрядного частного, сформированного на выходах 26 блока 4. больше истинного

к-разрядного частного на две единицы Младшего разряда (на входы двух младших разрядов сумматора-вычитателя 39 по лини- йм се«зи 211. 212 подается двоичный код 10, который вычитается из k-разрядного частного, сформированного в блоке 4). Значение дополнительной цифры частного, которая поступает в формирователь 10 по Линии связи 21з и присовокупляется к k-раз- рядному частному со стороны самого млад- шего разряда, равно единице.

На выходах 20 формирователя 9 будет при этом генерироваться код 000100я, по которому в регистр 1 делимого через коммутатор 12 запишется значение остатка с вы- ходов 32з сумматора-вычитателя 8з. В конце каждого такта деления 5-разрядное частное записывается в младшие 5 разрядов регистра 3, освобожденные в результате сдвига в регистре 3 информации на 5 разрядов в сто- рону старших разрядов.

Технико-экономическое преимущество устройства для деления по сравнению с прототипом состоит в повышении быстродействия, так как время выполнения деления двух чисел сокращается на 15-40% в зависимости от разрядности частного и количества получаемых за один такт дополнительных цифр частного.

Ф о р м у л а и з о б р е те н и я

Устройство для деления, содержащее регистры делимого, делителя и частного, блок деления усеченных чисел, формирователь цифр частного, блок умножения, два вычитателя, группу сумматоров-вычитэте- лей, коммутатор и блок управления, причем вход данных устройства соединен с информационными входами первой группы коммутатора и с информационными входами регистра делителя, выходы которого соединены с входами первой группы блока умножения, выходы коммутатора соединены с информационными входами регистра делимого, выходы старших разрядов которого соединены с входами делимого блока деления усеченных чисел, входы делителя которого соединены с выходами старших разрядов регистра делителя, выходы регистра делимого соединены с входами умень- шаемого первого вычитателя, входы вычитаемого и заема которого соединены с

выходами первой и второй групп блока умножения соответственно, выходы разности и заема первого вычитателя соединены с входами уменьшаемого и вычитаемого второго вычитателя соответственно, выход знакового разряда которого соединен с управляющим входом формирователя цифр частного и с управляющими входами сумма- торов-вычитателей группы, выходы второго вычитателя соединены с входами первого операнда каждого сумматора-вычитателя группы и с информационными входами второй группы коммутатора, информационные входы остальных групп которого соединены с выходами соответствующих сумматоров- вычитателей группы, выходы блока деления усеченных чисел соединены с входами второй группы блока умножения и с и н форма-, ционными входами первой группы формирователя цифр частного, выходы которого соединены с информационными входами регистра частного, синхровход которого соединен с входом синхронизации устройства и с синхровходами регистров делимого и делителя и блока управления, первый выход которого соединен с первым управляющим входом коммутатора, второй и третий выходы блока управления соединены с входами разрешения записи регистров делимого и делителя соответственно, отличающееся тем. что, с целью повышения быстродействия, в него введен формирователь дополнительных цифр частного и формирователь кратных, информационные входы которого соединены с выходами регистра делителя, входы второго операнда каждого сумматора-вычитателя группы соединены с выходами соответствующей группы формирователя кратных, выход знакового разряда второго вычитателя соединен с первым входом формирователя дополнительных цифр частного, остальные входы которого соединены с выходзми знакового разряда соответствующих суммэто- ров-вычитателей группы, выходы первой группы формирователя дополнительных цифр частного соединены с информационными входами второй группы формирователя цифр частного, выходы второй группы формирователя дополнительных цифр частного соединены соответственно с остальными управляющими входами коммутатора.

t

CO Щ GZJ

3

ч

QZj

1

«L

7t

35

f

/

Vul 2

.3 /

7L

г

32, 32t Ms зг. Us

/4

ui.$

Ч

$Ъг

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1992-12-23—Публикация

1990-12-25—Подача