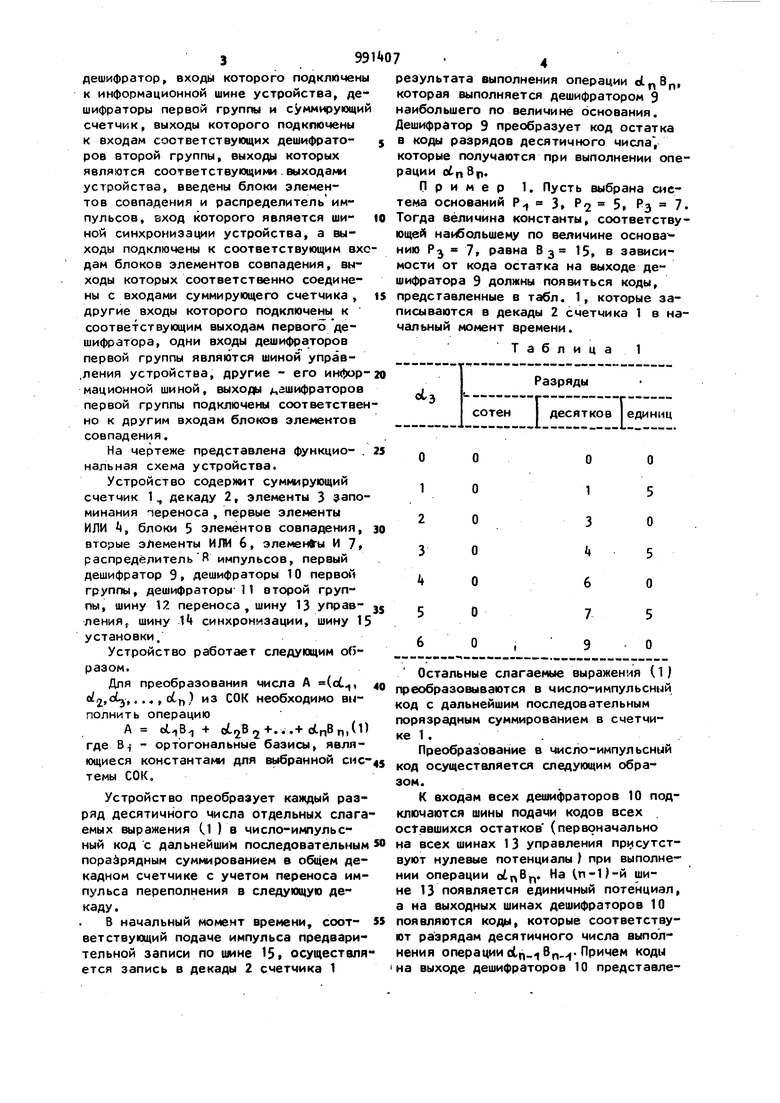

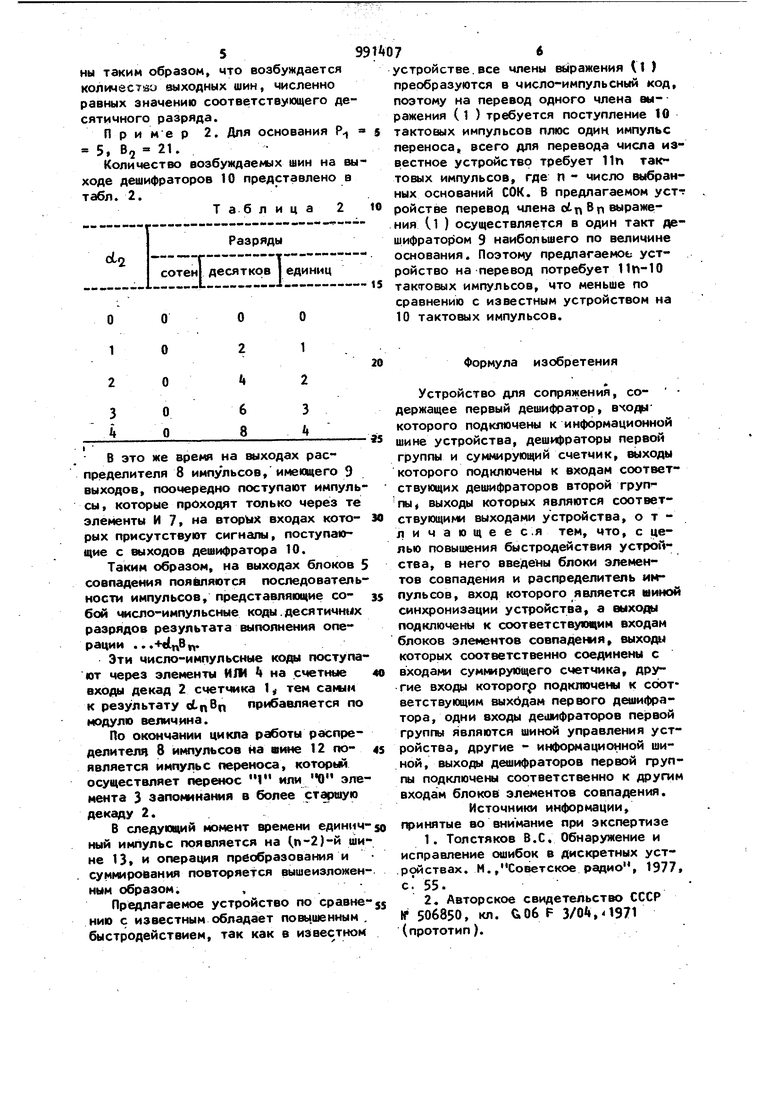

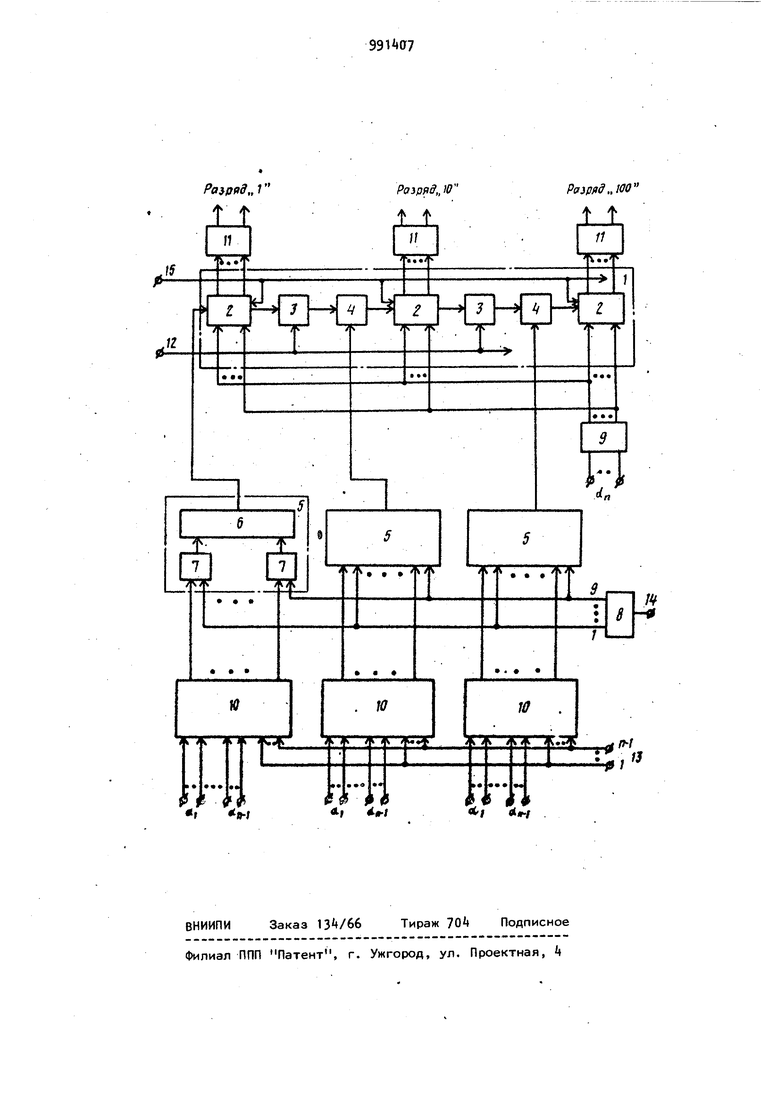

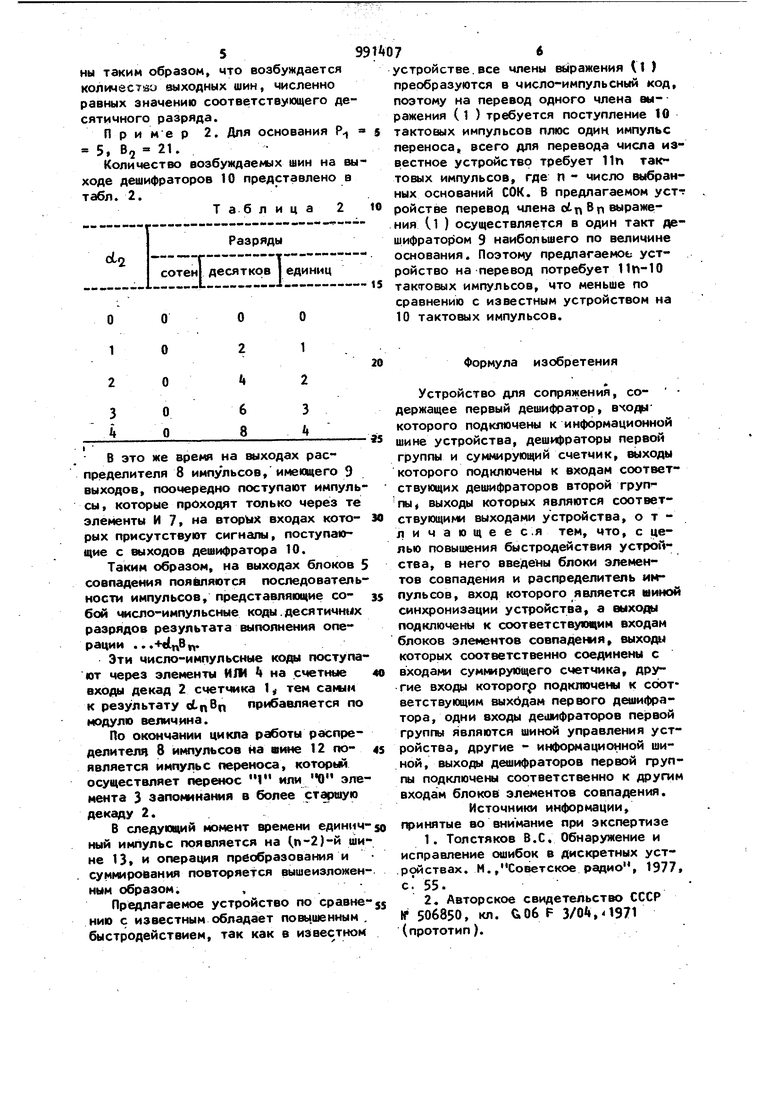

Изобретение относится к вычислительной технике и может быть использовано для сопряжения с вычислительными устройствам, функционирующими в системе остаточных классов (СОК ), а также в устройствах передачи данных, использующих коды СОК. Известно устройство для декодирования кодов, представленных в СОК, содержащее вычитающие счетчики, выходы которых подключены к входам пер вого логического элемента И, выход к торого подключен к первому входу триггера, выход которого подключен к первому входу второго логического элемента И, генератор тактовых импульсов, сЬединенный с вторым входом второго логического элемента И, выхо которого соединен с тактовыми входа и вычитающего счетчика и входом сум мирующего счетчика, второй вход триг гера соединен с шиной подачи импульра записи f 1Однако это устройство обладает малым быстродействием, так как велико время перевода кода, представленного в СОК в позиционный код. Наиболее близким к изобретению по технической сущности является устройство, содержащее суммирующий декадный счетчик, выходы переноса декад которого через элементы запоминания переноса и элементы ИЛИ подключены к счетным входам последующей декады суммирующего декадного счетчика, выходы каждой декады которого соединены с cooтвeтcтвyющи в дешифраторами индикации, дешифраторы, а также декадные счетч ики и элементы И с запоминанием С2 . Недостатками известного устройства являются пониженное быстродействие и сложность. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее первый дешифратор, входы которого подключены к информационной шине устройства, дешифраторы первой группы и суммирующий счетчик, выходы которого подключены к входам соответствующих дешифраторов второй группы, выходы которых являются соответствующими.выходами устройства, введены блоки элементов совпадения и распределитель импульсов, вход которого является шиной синхронизации устройства, а выходы подключены к соответствующим вхо дам блоков элементов совпадения, выходы которых соответственно соединены с входами суммирующего счетчика , другие входы которого подключены к соответствующим выходам первого дешифратора, одни входы дешифраторов первой группы являются шиной управ,ления устройства, другие - его информационной шиной, выходы .ашифраторов первой группы подключеил соответствен но к другим входам бло1«эв элементов совпадения. На чертеже представлена функцио- . нальная схема устройства. Устройство содержит суммирующий счетчик 1, декаду 2, элементы 3 запоминания переноса , первые элементы ИЛИ , блоки 5 элементов совпадения, вторые элементы ИШ 6, элеменК-ы И 7, распределитель R импульсов, первый дешифратор 9, дешифраторы 10 первой группы, дешифраторы П группы, шину 12 переноса , шину 13 управлениЯ; шину синхронизации, шину 15 установки. Устройство работает следующим о(5разом. Для преобразования числа А (о(., о..оэ п из СОК необходимо выполнить операцию А oL.,B + 2+ где В - ортогональные базисы, являющиеся константами для выбранной сиетемы СОК. Устройство преобразует каждый разряд десятичного числа отдельных слагаемых выражения Cl ) в число-импульсный код с дальнейшим последовательным пора рядным суммированием в общем декадном счетчике с учетом переноса импульса переполнения в следующую декаду. В начальный момент времени, соответствующий подаче импульса предварительной записи по шине 15. осуществляется запись в декады 2 счетчика 1 результата выполнения операции , которая выполняется дешифратором 9 наибольшего по величине основания. Дешифратор 9 преобразует код остатка в коды разрядов десятичного числа, которые получаются при выполнении операции otnSp. Пример 1. Пусть выбрана сиетема оснований Р 3 Р2 5, РЭ 7. Тогда величина константы, соответствующей на1 ольшему по величине основа нию PJ 7, равна 83 15, в зависимости от кода остатка на выходе дешифратора 9 должны появиться коды, представленные в табл. 1, которые записываются в декады 2 счетчика 1 в начальный момент времени. Таблица 1 Остальные слагаемые выражения (1) преобразовываются в число-импульсный код с дальнейшим последовательным порязрадным суммированием в счетчике 1 .. Преобразование в число-импульсный од осуществляется следующим образом. К входам всех дешифраторов 10 подключаются шины подами кодов всех ос±авшихся остатков (первоначально на всех шинах 13 управления npt icyTCTвуют нулевые потенциалы ) при выполнении операции . На п-1)-й шине 13 появляется единичный потенциал, а на выходных шинах дешифраторов 10 появляются коды, которые соответствуют разрядам десятичного числа выполнения операции оС.Вп.. Причем коды на выходе дешифраторов 10 представлены таким образом, что возбуждается количество выходных шин, численно равных значению соотв етствующего де сятичного разряда. При ме р 2. Для основания Р 5, В, 21. Количество возбуждаемых шин на в ходе дешифраторов 10 представлено а табл. 2. Таблица 2 в это же время на выходах распределителя 8 импульсов,имеющего 9 выходов, поочерёдно поступают импульсы, которые проходят только через те элементы И 7, на вторых входах которых присутствуют сигналы, поступающие с выходов дешифратора 10. Таким образом, на выходах блоков 5 совпадения появляются последовательности импульсов, представляющие собой число-импульсные коды.десятичж х разрядов результата выполнения операции ..,, Эти число-импульсные коды поступают через элементы ИШ 4 на счетные входы декад 2 счетчика 1« тем самян к результату П| ибавлявтся по модулю величина. По окончании цикла работы распределителя 8 импульсов на шине 12 гюявляется импульс переноса, который осуществляет перенос 1 или Ч) элемента 3 запоминания в более старв ю декаду 2. В следующий момент времени единичный импульс появляется на (,п-2)-й шине 13 и операция преобразования и суммирования повторяется вышеизложенным образом,, Предлагаемое устройство по сравне нию с известным обладает повы.шенным . быстродействием, так как в известном 76 устройстве, все члены выражения СМ преобразуются в число-импульсный код, поэтому на перевод одного члена выражения ( 1 ) требуется поступление 10 тактовых импульсов плюс один импульс переноса, всего для перевода числа известное устройство требует 11п тактовых импульсов, где п - число выбранных оснований СОК. В предлагаемом уст-: ройстве перевод члена oL т) В п выражения (.1 ) осуществляется в один такт дешифратором 9 наибольшего по величине основания. Поэтому предлагаемое устройство на перевод потребует lln-10 тактовых импульсов, что меньше по сравнению с известным устройством на 10 тактовых импульсов. Формула изобретения Устройство для сопряжения, со- держащее первый дешифратор, входыкоторого подключены к информационной шине устройства, дешифраторы первой группы и суммирующий счетчик, выходы которого подключены к входам соответствующих дешифраторов второй груп rttif выходы ютторых являются соответствующими выходами устройства, о т л и ч а ю щ е е с.я тем, что, с целью повышения быстродействия устройства, в него ввeдevlы блоки элементов совпадения и распределитель инпульсов, вход которого является шиной синхронизации устройства, а выходы подключены к соотеетствукйцим входам блоков элементов совпаде «1Я, выходы которых соответственно соединены с входами суммирующего счетчика, другие входы которогр подключены к соответствующим шлхддам первого дешифратора, одни входы дешифраторов первой групгы являются шиной управления устройства, другие - информационной шиной, выходы дешифраторов первой группы подключены соответственно к доугим входам блоков элементов совпадения. Источники информации, принятые во внимание при экспертизе 1.Толстяков B.C. Обнаружение и исправление ошибок в дискретных устройствах. И.,Советское радио, 1977, с 55. 2.Авторское свидетельство СССР IP 506850, кл. йОбР 3/04,41971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования кода системы остаточных классов в десятичный код | 1984 |

|

SU1167600A1 |

| Устройство для декодирования кодов представленных в системе остаточных классов | 1973 |

|

SU506850A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Устройство для формирования импульсных последовательностей | 1977 |

|

SU669478A1 |

| Цифроаналоговый измеритель средней частоты | 1991 |

|

SU1775678A1 |

| Цифровые вторичные часы | 1988 |

|

SU1511733A1 |

| Устройство для записи параметров движения | 1984 |

|

SU1273811A1 |

| Цифровой фазометр | 1973 |

|

SU477362A1 |

| Триггерное устройство | 1971 |

|

SU437225A1 |

Авторы

Даты

1983-01-23—Публикация

1981-07-28—Подача