(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771660A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU641441A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1149243A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

...I

Изобретение относится к области цифровой вычислительной техники и может быть исполь зовано при построении устройств преобразования информации.

Известен преобразователь двоичного кода в двоично-десятичный, содержащий регистр двоичного кода, шифратор двоичных эквивалентов распределитель импульсов, выходы которого через элементы И соединены со входами шифратора, суммирующую декаду, коммутатор и регистр двоично-десятичного числа, входы которого через коммутатор соединены с выходами суммирующей декады 1.

Недостатком устройства является егр, относительно большая сложность и невысокое быстродействие..

Наиболее близким решением данной технической задачи является преобразователь двоиЧг ного кода в двоично-десятичный, содержащий регистр двоичного кода, распределитель импульсов, шифратор К двоичных счетчиков, где К - число десятиодых разрядов, информационные входы которых соединены с первой группой выходов 1Ш1фратора, группу элеменi тов НЕ, первую группу элементов И, входы которых соединены с .выходами соответствующих двоичных счетчиков, вторую группу элементов И, выходы которых соединены со счет-, ными входами соответствующих двоичных счетчиков, первые входы через элементы НЕ соединены с выходами элементов И первой труппы, а вторые входы с шиной такто- . вых импульсов, К последовательно соединенных счетных декад, первый элемент И, входы которого соед1шены с выходами элементов И первой группы, а выход соединен с управляющим входом распределителя импульсов 12.

Недостатком известного устройства является относительно низкое быстродействие, связанное с последовательной обработкой двоичных разрядов и большим временем их преобразования.

Целью предлагаемого изобретения является сокращение времени преобразования.

Это достигается тем, что преобразователь

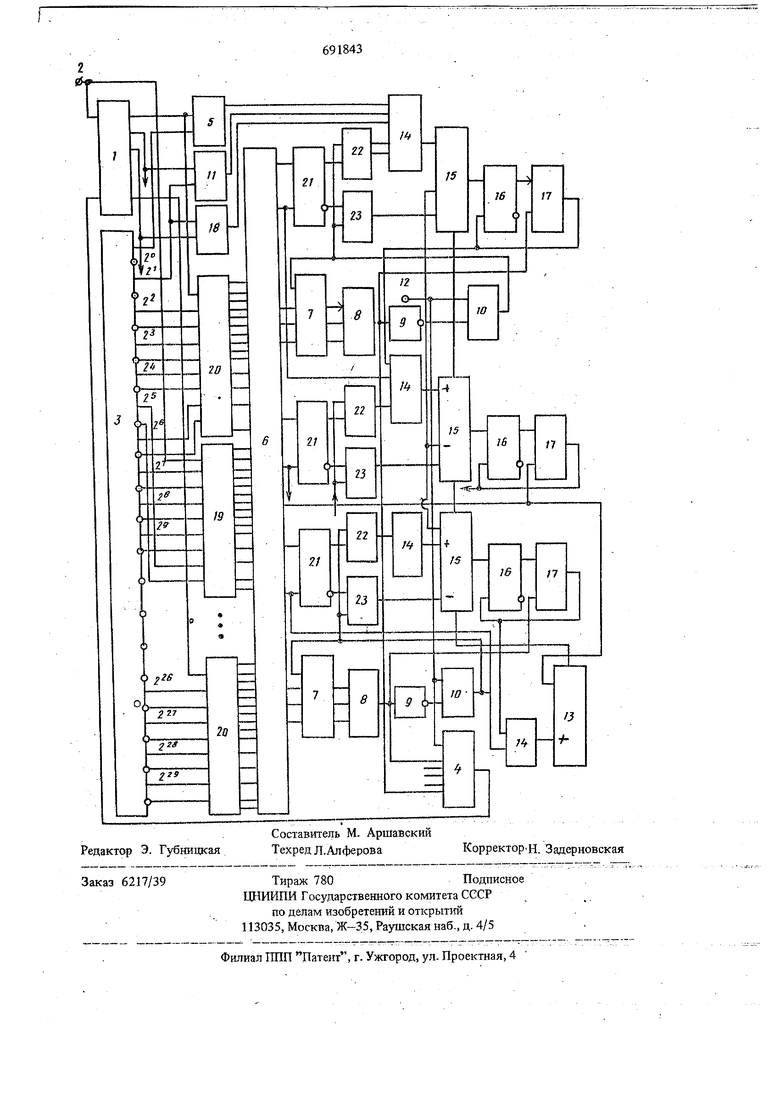

содержит первую и вторую группы дешифратоipOB, первую и вторую группы триггеров, груп пу элементов ИЛИ, третью, четвертую и пятую группы элементов И, второй, третий и четвертый элементы И, счетные декады выполнены реверсивными, информационные входы всех дешифраторов соединены с соответствующими выходами регистра двоичного кода, а выхо(Цы - со входами шифратора, тактовые входы дешифраторов соединены с соответствующими выходами распределителя импульсов, первые входы триггеров первой группы соединены с выходами переполнения соответствующих счетных декад, а выходы - с первыми входами элементов И третьей группы, вторые входы которых соединены с вбтхбдами элементов И первой группы соседней старшей счетной декады, выходы элементов И третьей группы соединены со вторыми входами соответствующих триггеров первой группы и с. первыми входами группы элементов ИЛИ, первые и вторые входьг триггеров второй группы соединены со вто рой и третьей группой выходов шифратора, единичные и нулевые выходы соединены с пер выми входами элементов И четвертой и,пятой групп, вторьге входы которых соединены с вы ходами элементов И второй группы, выходы элементов И четвертой группы соединены со вторыми входами группы элементов ИЛИ, третьи входы которых соединены с третьей группой выходов шифратора, а вьисоды - с суммирующими входами соответствующих счет ных декад, выходы элементов И пятой группы соединены с входами вычитания счетных декад первые входы второго, третьего и четвертого элементов И соединены с первым, вторым и третьим выходами распределителя импульсов соответственно, вторые входы второго и третье го элементов И соединены с первым и вторым выходами регистра двоичного кода, второй вход четвертого элемента И соединен со вторым выходом регистра двоичного кода, выходы второго, третьего и четвертого элементов И соединены со входами первого из элементов в группе элементов ИЛИ. Блок - схема предложенного преобразоватё ля представлена на чертеже,Преобразователь двоичного кода в десятичный Содержит распределитель импульсов I, первый вход которого соединен с первой управляющей входйой шиной 2, регистр 3 двои ного кода, первый элемент 4 И, второй элемент 5 И, шифратор 6, двоичные счетчики 7, первую группу 8 элементов И, группу 9 элементов НЕ и вторую грутту 10 элементов И, второй элемент 11 И, управляющую входную шину 12, десятичный счетчик (на чертеже не выделен), содержащий последнюю декаду 13, группу 14 элементов ИЛИ, счетные декады 15 перйую группу 16 триггеров и третью группу 17 элементов И, четвертый элемент 18 И, первую и вторую грутшы дешифраторов 19-20, вторую группу триггеров 21, четвертые и пятые группы 22--23 элементов И. В исходном положении распределитель им|Пульсов 1 выключен, двоичные счетчики 7, счетные декады 13 и 15 десятич1гого счетчика и триггеры первой группы 16 находятся в нулевом состоянии. Работа предлагаемого устройства основана на параллельном суммировании в счетных декадах 15 чисел, которые соответствуют сумме весов одновременно опрашиваемых и имеющих единичное состояние разрядов двоичного кода. Числа 1, 2, 3, 4 и 5 суммируются обычным путем, а числа 6, 7, 8 и 9 заменяются соответственно на чисЛа 4, 3, 2 и 1 в шифраторе 6 и подаются на вычитающий вход соответствующей декады 15, при этом на суммирующий вход следующей старшей счетной декады 15 или 13 подается импульс из шифратора 6 через группу 14 элементов ИЛИ, соответствующий записи единищ 1 в соседнюю старщую счетную декаду 15 или 13. Таким образом, максимально возможное число импульсов на выходе любого элемента И второй группы 10 равно пяти. Предлагаемое устройство работает следующим образом. На шину 2 подается сигнал начало, который включает распределитель импульсов 1 и одновременно с помощью дешифратора 19 первой группы и шифратора 6 устанавливает в счетных декадах 15 десятичного счетчика числа, соответствующие сумме весов одновременно опрашиваемых и имеющих единичное состояние разрядов двоичного кода. В нашем примере на .чертеже показаны дешифраторы, рассчитанные на дешифрование 4eTiiipex разрядов двоичного кода каясдьШ, как наиболее приемлемые. Однако в предлагаемом устройстве могут использоваться и другие дешифраторы, например, рассчитанные на дешифрование двух, трех, пяти и более разрядов двоичных кодов. Тактовые импульсы с управляющей шины 12 через открытые первый элемент 4 И и распределитель 1 импульсов последовательно появляются на выходах распределителя импульсов 1 и подключают разряды 2° и 2двоичного кода с помощью элементов 5, 11 и 18 И и группы 14 элементов ИЛИ к суммирующему входу первой счетной декады 15 десятичного счетчика, а остальные разряды, кроме разрядов, подключенных к входам первого дешифратора 19, через дешифраторы 20 ко входам шифратора 6. При наличии I в разрядах 2 и 2 двоичного кода в первую счетную декаду 15 записываются с помощью трёх импульсов опроса числа, соответствующие весу данных разрядов. Одновремешю с опросом разряда 2° производится опрсус разрядов, подключенных к дешифратору 20, второй группы, например, разрядов 2, 1, 2 и 2, как показано на чертеже. , При наличии 1 во всех этих разрядах или хотя бы в одном из них. дешифратор 20 формирует только один импульс на том одном выходе, который соответствует сумме весов тех разрядов из всех опрашиваемых, которые имеют состояние 1. Под воздействием зтого импульса шифратор 6 устанавливает в двоичны счетчиках 7 числа, соответствующие сумме весов одновременно опрашиваемых и имеюших единичное состояние разрядов двоичного кода. Как только состояние любого из двоичных счетчиков 7 станет не нулевым, первый элемент 4 И закроется и дальнейший опрос разрядов двоичного кода прекратится. При этом триггеры второй группы 21 импульсами с соот ветствующих выходов шифратора б устанавли;ваются в положение, соответствующее суммиро ванию или вычитанию в соответствующей счетной декаде 15 десятичного счетчика. При установке соответствующего триггера второй группы 21 в положение, соответствующее вычитанию, на суммирующий вход следующей старшей декады 15 или 13 подается импульс, соответствующий записи едшшцы, из шифратора 6 через группу 14 элементов ИЛИ. После этого начинается параллельная перезапись чисел из двоичных счетчиков 7 в счетные декады 15 с помощью тактовых импульсов, поступающих с управляющей шины 12 на вторые входы элементов И второй группы 10. При наличии 1 на соответствующих первых входах этих элементов И на их выходах появляются сигналы, которые поступают на вычитание в соответству щие двоичные счетчики 7, через элементы И четвертой труппы 22 и элементы ИЛИ группы 14 на сложение или через элементы И пятой группы 23 на вычитание в соответствующи . счетные декады 15. Появляющийся при этом импульс переноса в какой-либо декаде 15 запоминается соответствующим триггером из перовой группы 16. После окончания счета в следующей старшей счетной декаде 15 открывается соответствующий элемент И третьей группы 17 и производится в данной декаде 15 регистрашш импульса переноса, при этом триггер первой группы 16 возвращается в исходное положение. Только после установления всех двоичных счетчиков 7 в нулевое состояние про должается дальпейщий спрос разрядов двоичного кода. Вторым импульсом опроса производит ся одновременно включение элемента 11 И и дешифратора 20, третьим импульсом опроса - элемента 18 И и следующего дешифратора в группе 20. Остальные импульсы опроса включают по одному следующему дешифратору груп пы 20. Последний импульс опроса одновременно с включением последнего дешифратора групр 1 20 выключает распределитель импульсов 1. В десятичном счетчике буде1 записано число, соответствующее данному двоичному коду. Время преобразования двоичного кода в де-, сятячный равно, -Ггт-Лн Sa,-b-i), где Т - период следования импульсов тактовой частоты; П - количество необходимых импульсов опроса, зависящее от количества дво- , ичных разрядов и количества одновременно Опрашиваемых разрядов . двоичного кода; aj 1при наличии хотя бы одного разряда, имеющего единичное состояние, из всех одновременно опрашиваемых разрядов соответствующим дешифратором, в противном случае aj 0; bj - наиболее десятичное число, записываемое в один из двоичных счетчиков при одновременном опросе нескольких разрядов двоичного кода с помощью определенного дешифратора. Из приведенного на чертеже примера конкретного исполнения устройства можно сделать вывод, что кол1нество необходимых импульсов для опроса 10 разрядов двоичного кода равно 3, для опроса 20 разрядов - 4, для опроса 30 разрядов - 6. - Максимальное время преобразования 10-раэрядного двоичного кода равно 7 периодам тактовой частоты, 20-разрядного двоичного кода - 23 периодам тактовой частоты, 30-разрядного двоичного кода - 35 периодам тактовой частоты, то есть по сравнению с известньш устройством время преобразования уменьшено в 6-8 раз. Использование новых элементов не приводит к усложнению устройства, так как при этом значительно упрощаются распределитель импульсов и двоичные счетчики 7, используются инверсные выходы регистра 3 двоичного кода с целью применения наиболее простых дещифраторов групп 19, 20. Параллельное суммирование в декадах 15 чисел, которые соответствуют сумме весов одновременно опрашиваемых и имеющих единичное состояние разрядов двоичного кода, способствует повьппению быстродействия преобразователя. Ф о р м ула изобретения Преобразователь двоичного кода в двоичнодесятичный, содержащий регистр двоичного коpa, распределительимпульсов, шифратор К двоичных счетчиков, где К-число десятичных раз- г рядрв, информациоиные входы которых соединеш 1 с первой группой выходов шифратора, группу элементов НЕ, первую группу элементов И, входы которых соединены с выходами соответствзтощих двоичных счетчиков, вторую груплу элементов И, выходы которых соединены со счетными входами соответствзтоших двоичнь1Х счетчиков, первые входы элементов И второй группы через элементы НЕ группы соединены с выходами элементов И первой группы, а вторые входы - с шиной тактовых импульсов, К последовательно соединенных счетных декад, первый элемент И, входы которого соединень с выходами элементов И первой группы, а выход соединен с управляющим входом распределителя импульсов, отличающ и и с я тем, что, с целью сокращения бремени преобразования, он содержит первую и вторую группы дешифраторов, первую и вторую группь триггеров, группу элементов ИЛИ, третью, четвертую и пятую группы элементов И второй, третий и четвертый элементы И, счетные декады выполнены реверсивными, инфор: мащюнные входь всех дешифраторов соединены с соответствующими выходами регистра двоичного кода, а выходы - со входами ишфратора, тактовые входы дешифраторов соединены с соответствующими выходами распределителя импульсов, первые входы триггеров первой группы соединены с выходами переполнения соответствующих счетных декад, а вькоды - с первыми входами элементов И третьей группы, вторые входы которых соединены с выходами элементов Ив первой группы сосед8ней старшей счетной декады, выходы элем ентов И третьей группы соединены со вторыми входами соответствующих триггеров первой группы и с первыми входами группы элементов ИЛИ, первые и вторые входы триггеров второй группы соединены со второй и третьей группой выходов шифратора, единичные и нулевые выходы соединены с первыми входами элементов И четвертой и пятой групп, вторые входа которых соединены с выходами элементов И второй группы, выходы элементов И четвертой группы соединены со вторыми входами группы элементов ИЛИ, третьи входы которых соединены с третьей группой выходов шифратора, а выходы - с суммирующими входами соответствующих счётных декад, выходы элементов И пятой группы соединены с входами вьиитания счетных декад, первые входы второго, и третьего, и четвертого элементов И соединены с первым, вторым и третьим выходами распределителя импульсов соответственно, вторые входы второго и третьего элементов И соединены с первым и вторым выходами регистра двоичного кода, второй вход четвертого элемента И соединен со вторым выходом регистра двоичного кода, выходы второго, третьего и четвертого элементов И соединены со входами первого из элементов в группе элементов ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 468236, кл. G 06 F 5/02 от 1973. 2.Авторское свидетельство СССР N 525944, кл. G 06 F 5/02 от 1976.

Авторы

Даты

1979-10-15—Публикация

1977-07-05—Подача