(54) УСТРОЙСТВО СОПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

| Устройство для сопряжения | 1978 |

|

SU723561A1 |

| Устройство для отображения информации | 1988 |

|

SU1603365A1 |

| Устройство для ввода информации | 1987 |

|

SU1522189A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Устройство синтаксически управляемого перевода | 1986 |

|

SU1399767A1 |

| Устройство для сопряжения телеграфных каналов с вычислительной машиной | 1978 |

|

SU748403A1 |

| Устройство для сопряжения ЭВМ с каналом передачи данных | 1989 |

|

SU1647580A1 |

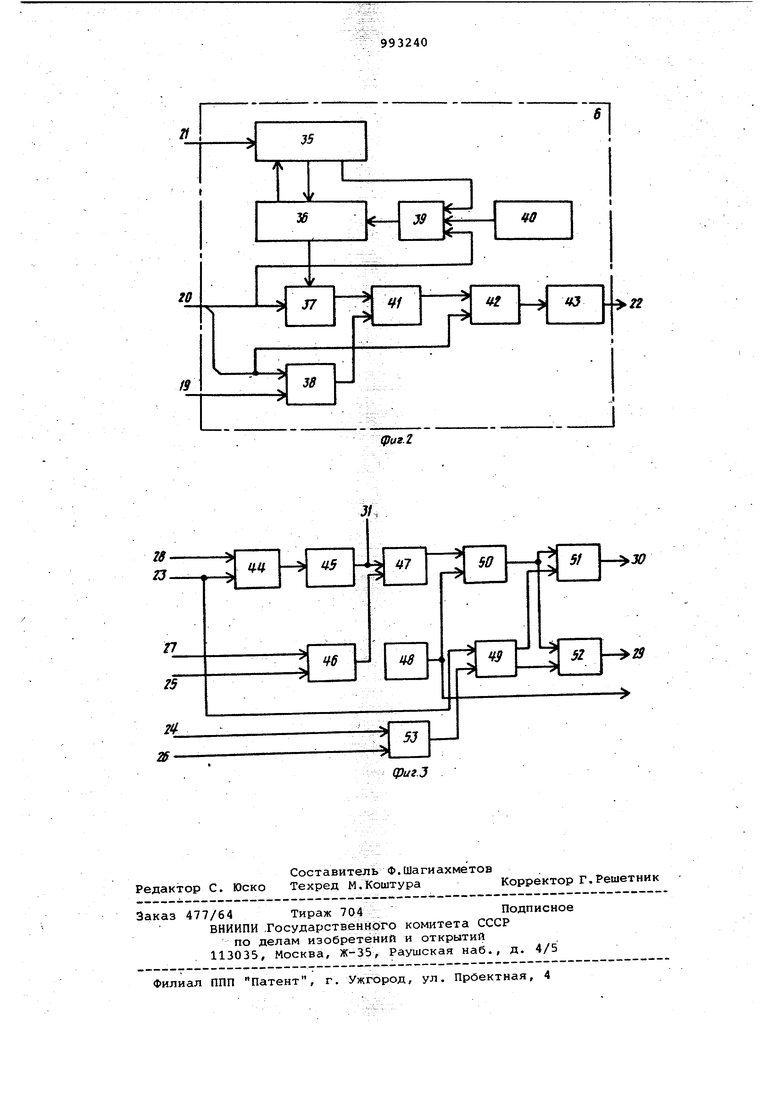

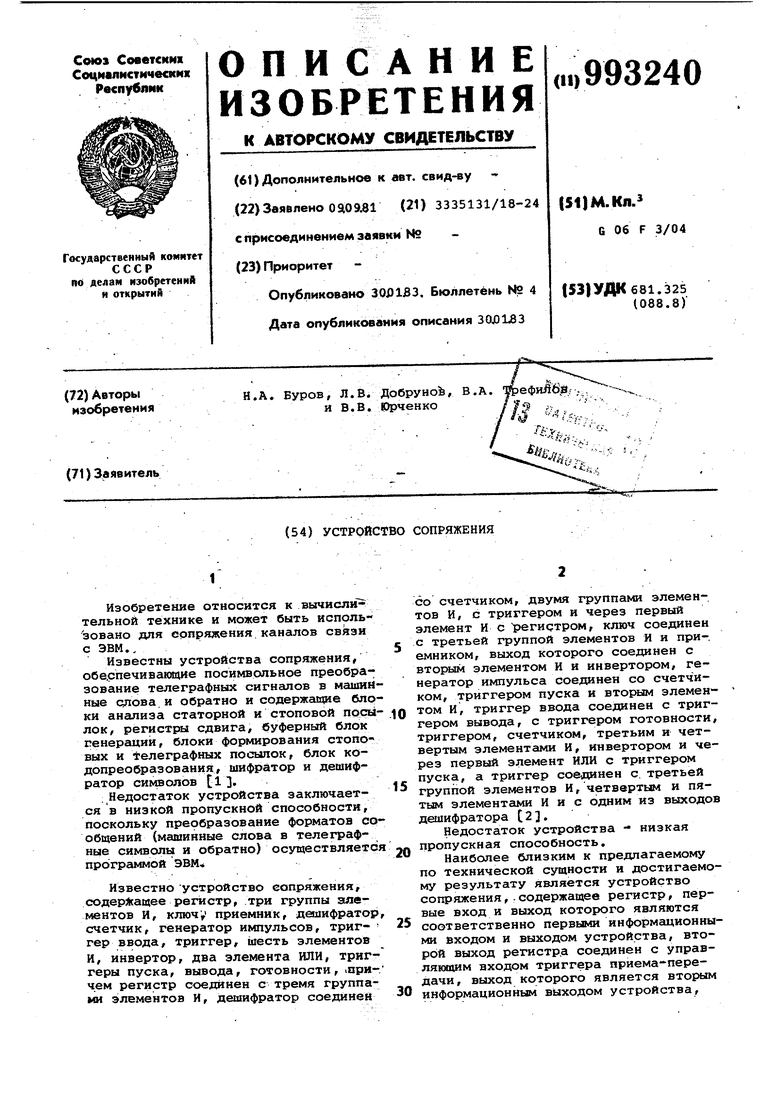

Изобретение относится к вычисли тельной технике и может быть использовано для сопряжения каналов связи с ЭВМ., Известны устройства сопряжения, обе.спечиваквдие посимвольное преобразование телеграфных сигналов в машин ные суюва.и обратно и содержавшие бло ки анализа статорной и стоповой посы лок, регистры сдвига, буферный блок генераций, блоки формирования стоповых и телеграфных посылок, блок кодопреобраэования, шифратор и дешифратор символов ti 3 : Недостаток устройства заключается в низкой пропускной способности, поскольку преобразование форматов со общений (машинные слова в телеграфные символы и обратно) осуществляетс прбграммой ЭВМ Известно устройство еопряжения, содержащее регистр, три группы элементов И, ключ) приемник, дешифратор счетчик, генератор импульсов, триггер ввода, триггер, iaecxb элементов И, инвертор, два элемента ИЛИ, триггеры пуска, вывода, готовности, .причем регистр соединен с тремя группами элементов И, дешифратор соединен со счетчиком, двумя группами элементов И, с триггером и через первый элемент И с регистром, ключ соединен с третьей группой элементов И и при-. емником, выход которого соединен с вторым элементом И и инвертором, генератор импульса соединен со счетчиком, триггером пуска и вторым элементом И, триггер ввода соединен с триггером вывода, с триггером готовности, триггером, счетчиком, третьим и четвертым элементами И, инвертором и через первый элемент ИЛИ с триггером пуска, а триггер соединен с. третьей группой элементов И, четвертым и пятым элементами И и с одним из выходов дешифратора С 2. Недостаток устройства - низкая пропускная способность. Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство сопряжения,-содержащее регистр, первые вход и выход которого являются соответственно первыми информационными входом и выходом устройства, второй выход регистра соединен с управляюпшм входом триггера приема-передачи, выход которого является вторым информационным выходом устройства. третий выход соединен с входом деши ратора посыпок, а третий вход - с вт рым информационным входом устройств и входом генератора одиночного импульса, выход которого подключен к синхронизирующему входу формирователя управляющих сигналов и первому входу триггера приема-передачи, сое диненного вторым входом с первым вх дом триггера ГОТОВНОСТР, а первым вы ходом - с вторым входом первого эле мента И и вторым входом формировате ля управляющих сигналов, третий вход которого и второй вход второго элемента И подключены к второму выходу триггера приема-передачи, выходы дешифраторс1 посылок и счетчика символов подключены к соответствующим входам первого элемента ИЛИ, соединенного выходом с вторым входом триггера готовности, формирователь управляющих сигналов, соединенный тактовым выходом с вторым входом регистра и счетным входом счетчика, первым входом - с входом Конец слова устройства, четвертый и пятый входы формирователя управляющих сигналов соединены соответственно с синхронизирующими выходами дешифратора посылок и счетчика символов, управляющие которых подключены к первому входу триггера, вторым входом соединенного с выходом второго элемента ИЛИ, к управляющему входу счетчика импульсов и первому выхо ду счетчика импульсов и управляющему входу генератора одиночных импульсов а второй, выход и первый вход - к соответствующим входам второго элемента ИЛИ, два элемента И, подключенные первыми входами к выходу триггера готовности, а выходами - к соотвётствующим управляющим выходам устройства 3 . Недостаток устройства - сравнит льно невысокая пропускная способность, обусловленная тем, что преобраэование информации осуществляется программным способом после ввода в ЭВМ. Цель изобретения - повьошение пропускной способности. , Поставленная цель достигается тем что в устройство сопряжения, содержащее генератор синхронизации, первый выход которого соединен со счетным входом счетчика импульсов, счетчик символов, выходы счетчика импульсов и счетчика символов соединены с первым и вторым признаковыми входами блока управления, триггер готовности, первый выход которого соединен с первыми входами элементов И первой группы и первым входом элемента ИЛИ, регистр информации, втору группу элементов И и триггер приемапередачи введены коммутатор, преобразователь формата .данных, регистр состояния, дешифратоо конца передачи, дешифратор кода управления, наборный блок, блок буферной пайяти и генератор меток времени, причем первый вход устройства соединен со счетным входом счетчика символов, информационными входами блока управления и преобразователя формата данных, выход которого и первый выход регистра состояния через элементы И второй группы соединены с информационным входом регистра информации, выход которого соединен с вторыми вхо дами элементов И первой группы, третьи входы которых и второй вход элемента ИЛИ соединены с первым выходом дешифратора конца передачи,второй выход которого соединен с первым установочным входом блока управления, выход наборного блока соединен с входом коммутатора, первый - пятый выходы которого соединены с входом генератора синхронизации, информационным входом счетчика импульсов, запускающим входом генератора меток времени, информационным входом счетчика символов и разрешающим входом блока управления, первый, второй кодовые и запускающий выходы которого, соединены соответственно с информационными входами регистра состояния, дешифратора конца передачи и входом триггера готовности, второй выход которого соединен с управляющим входом регистра состояния, второй и третий выходы регистра состояния соединены соответственно с управляющим входом регистра информации и вторым установочным входом блока управления, выходы элементов И первой группы соединены с третьим входом элемента ИЛИ, выход элемента ИЛИ соединен с информационным входом блока буферной памяти, первый управляющий вход и выход которого соединены соответственно с выходом триггера приема-передачи и первым выходом устройства, выход генератора меток времени соединен с первым входом триггера приемапередачи и вторым управляющим входом блока буферной памяти, второй выход генератора синхронизации соединен с управляющим входом генератора меток времени, тактовый и информационный входы, первый и второй выходы дешифратора кода управления соединены соответственно с третьим выходом генератора синхронизации, вторым входом устройства, вторым входом триггера приема-передачи и вторым выходом устройства, разрешающий выход блока Управления соединен с управляющим входом преобразователя формата данных. Преобразователь формата данных выполнен в виде сдвигового регистра, вход которого соединен с информациейным входом преобразователя, выход старших разрядов сдвигового регистра соединен с выход9м преобразователя, а сдвиговый йход сдвигового регистра соединен с управляющим входом преобразователя, Блок управления содержит четыре группы элементов И, два элемента ИЛИ генератор одиночных импульсов, два триггера и генератор тактовых импуль сов, причем информационный вход блок соединен с первыми входами элементов И, первой группы, разрешаюахий вход блока соединен с вторыми входами эле ментов И первой группы и первым входом первого триггера, выходы элементов И первой группы соединены с входом генератора одиночных импульсов, выход которого соединен с запускаюc№M выходом блока и первым входом второго триггера, выход которого сое динен с первыми входами элементов И второй группы, выход генератора тактовых импульсов соединен с разрешающим, выходом блока и вторыми входами элементов И второй группы, ВЕЗХОДЫ элементов И второй группы соединены с первыми входами элементов И третьей и четвертой групп, выходы элементов И третьей группы являются вторым кодовым выходом блока, выходы элемен тов И четвертой группы являются первым кодовым выходом блока, первый и второй установочные входы блока че реэ первый элемент ИЛИ соединены с вторым входом второго триггера, первый и второй установочные входыблока через второй элемент ИЛИ соединены с вторым входом первого триггера, первый и второй выхода которого соединены соответственно с вторыми входами элементов И третьей и четвертой групп. : На фиг. 1 представлена структурная схема устройства; на фиг. 2 структурная схема блока буферной памяти; на фиг. 3 - структурная схема блока управления. Устройство сопряжения (фиг. Ij содержит преобразователь 1 формата данных, вторую группу 2 элементов И, регистр 3 информации, первую группу 4 элементов И, элемент ИЛИ 5, блок 6 буферной памяти, блок 7 управления, регистр 8 состояния, триггер 9 готовности, доиифратор 10 онца пере дачи, счетчик 11 символов, коммутатор 12, счетчик 13 импульсов, генера тор 14 синхронизации, наборный блок 15, генератор 16 меток времени, триг гер 17 приема-передачи, дешифратор 18 кода управления, управляющие вхо ды 19 и 20, информационный вход 21 и выход 22 блока буферной памяти, разрешающий вход 23, первый признако вый вход 24, первый установочный вхо 25, второй признаковый вход 2б,второй установочный вход 27, информационный вход 28, первый кодовый выход 29, второй кодовый выход 30 и V запускающий выход 31 блока управления, первый 32 и второй 33 вхояьа и выход 34. Блок, буферной памяти (фиг. 2) содержит регистры 35 и 36, группы 37 39 элементов И, генератор 40, группу 41 элементов ИЛИ, .группу 42 элементов И, усилитель 43. Блок управлен 1я (фиг. 3) содержит группу 44 элементов И, генератор 45 одиночных импульсов, элемент ИЛИ 46, триггер 47, генератор 48 такто.вых импульсов, триггер 49, группы 50 - 52 элементов И, элемент ИЛИ 53. Преобразователь 1 формата данных предназначен для преобразования входной информации в телетайпный код и представляет собой электронный шифратор. Вторая группа 2 элементов И исключает прохождение информации в регистр 3, если триггер готовности 9 не в исходном состоянии.Регистр 3 предназначен для временного хранения информации. Первая группа 4 элементов И исключает считывание информации с регистра 3, если триггер готовности 9 или дешифратор 10 не в исходном состоянии. Элемент ИЛИ 5 Для развязки выходов блоков 4, Эй 10. Блок буферной памяти- для согласования параметров устройства с линией связи. Регистр 8 управляет преобразованием информации регистра 3 в последовательный код и исключает запись информации в регистр 3 во время передачи. Триггер 9 готовности предназначен для подачи череэ элемент ИЛИ 5 сигнала Готовность к выводу, а на группу 4 элементов И - сигнала для исключения считывания информации с регистра 3. Дешифратор 10 по сигналу с блока 7 прекращает передачу информации и выдает сигнал в ЭВМ Конец передачи. Счетчик символов 11 осуществляет подсчет символов, поступающих на вход устройства, и выдает сигнал об окончании передачи информации в ЭВМ. Коммутатор 12 предназначен для распределения информации от наборного блока-15. Счетчик. 13 импульсов выдает сигнал на прекращение передачи информации в ЭВМ. Генератор 1.4 служит для синхронизации работы устройства. Наборный блок 15 предназначен для задания режима работы устройст ва. Генератор 16 предназначен для получения и передачи импульсов стабилизированной частоты.и заданной про-, должительности, соотйетствующих one ративному времени.Триггер 17 приемапередачи предназначен для выдачи сигнала на блок б, на отключение выхода элемента ИЛИ 5 при поступлении сигнала с генератора 16 ИЛИ из дешифратора 18, Дешифратор 18 предназначен для преобразования информации из машинного кода в сигналы управления, регистр 35 предназначен для записи, хранения и выдачи информации в регистр 36. Регистр 36 преобразует информацию -ИЗ параллельного кода в последовательный и выдает информации в первую группу 37 элементов И. Группа 37 элементов И управляет передачей информации из регистра 36 через группу 41 элементов ИЛИ. Группа 38 элементов И управляет передачей импульсов от входа 19 через группу 41 элементов ИЛИ. Группа 39 элементов И управляет считыванием информации из регистра 35. Генератор 40 предназначен для формирования тактовых импульсов. Группа 41 элементов ИЛИ предназначена Для развязки информационного канала и выхода генератора 16. Группа 42 элементов И предназначена для исключения возможности прохождения информации в линию связи в режиме приема. Усилитель 43 - ivin согласования параметров устройства с линией связи.

Устройство работает следую1цим образом.

Режим передачи: с наборного блока 15 производится приведение и исходное состояние регистров 3 и 8, дешифратора 10, счетчиков 11 и 13, триггера 9 готовности и запуск генераторов 14 и 16. Информация, поступающая на вход устройства, проходит на преобразователь 1 формата данных блок 7 управления и счетчик 11 символов. В преобразователе 1 поступающие сигналы преобразуются в 25-разрядный код и через группу 2 элементов И записывается в регистр 3. Триггер 9 готовности после подачи на его вход управляющих импульсов с блока 7 управления выдает сигнал в линию связи о готовности вывода информации,а также сигнал, запирающий группу 4 элементов И, для исключения возможности считывания информации из регистра 3. После передачи сигналга о готовности вывода информации на вход регистра В с триггера 9 готовности поступает импульс запуска.С выхода регистра В идет импульс, запирающий группу 2 элементов И, и импульс запуска на регистр 3, в котором 25-разрядный параллельный код преобразуется в последовательный и выдается через группу 4 элементов И, элемент ИЛИ 5, блок б буферной памяти в линию связи. При достижении заданного количества символов в счетчик 11 или количества импульсов времени в счетчик 13 из блока 7 управления выдается импульс запуска на дешифратор 10, который выдает сигнал на группу 4 элементов И, прекращающий передачу информации, и сигнал об окончании передачи в линию связи через элемент ИЛИ 5 и блок 6 буферной памяти. Генератор 16 через блок 6 буферной памяти передает в линию связи импульсы эталонной частоты.

Режим приема; информация от ЭВМ по телеграфному каналу связи,посту- пает на дешифратор 18, который с поступлением синхроимпульса включается в режим приема. Поступающая информация декодируется и с выхода дешифратора 18 поступает на исполнительные устройства. Во время приема с дешифратора 18 на триггер 17 приема-передачи идет сигнал для исключения возможности передачи информации в линию связи, по окончании приема триггер 17 возвращается в исходное состояние.

Предлагаемое изобретение по сравнению с известным устройством позволяет увеличить пропускную способность , так как за счет введения новых узлов и связей реализуется возможность осуществления кодопреобразования в самом ус- ройстве без использования специального программного обеспечения ЭВМ.

Формула изобретения

1Устройство сопряжения, содержащее генератор синхронизгщии, первый выход которого соединен со счетным входом счетчика импульсов, счетчик символов, выходы счетчика импульсов и счетчика символов,соединены с первым, и вторым признаковь1ми входами

блока управления, триггер готовности, первый выход которого соединен с первыми входами элементов И первой группы и первым входом элемента ИЛИ, регистр информации, вторую группу элементов И и триггер приема-передачи, отличающееся тем, что, с целью повышения пропускной способности, оно содержит коммутатор, преобразователь формата данных, регистр

состояния, дешифратор конца передачи , дешифратор кода управления, наборный блок, блок буферной памяти и генератор меток времени, причем первый вход устройства соединен со счетным входом счетчика символов,информационными входами блока управления и преобразователя формата данных, выход которого и первый выход регистра состояния..через элементы И второй группы соединены с информационным

входом регистра информации, выход ко-; торого соединен с вторыми входами элементов И первой группы, третьи входы которйх и второй вход элемента ИЛИ соединены с первым выходом дешиф5 ратора конца передачи, второй выход

которого соединен с первым установочным входом блока управления, выход наборного блока соединен с входом коммутатора, первый - пятый выходы которого соединены с входом генератора синхронизации, информационным входом счетчика импульсов, запускающим входом генератора меток времени, и.нформационным входом счетчика символов и разрешающим входом блока управления, первый, второй кодовые и запускающий выходы которого соед инены соответственно с информационными входами регистра состояния, дешифратора конца передачи и входом триггера готовности , второй выход которого соединен о управляющим входом регистра состояния, второй и третий выходы регистра состояния соединены соответственно с управляющим входом регистра информации и вторым установочным входом блока управления, выходы элементов И первой группы соединены с третьим входом элемента ИЛИ, выход элемента ИЛИ соединен с информационным входом блока буферной памяти, первый управляющий вход и выход которого соединены соответственно с выходом триггера приема-передачи и первым выходом устройства, выход генератора меток времени соединен с первым входом триггера приемапередачи и вторым управляющим входом блока буферной памяти, второй выход генератора синхронизации соединен с управляющим входом генератора меток времени, тактовый и информационный

входы, первый и второй выходы дешифратора кода управления соединены соответственно с третьим выходом генератора синхронизации, вторым входом устройства, вторым входом триггера

, приема-передачи и вторым выходом устройства, разрешающий выход блока управления соединен с управляющим входом преобразователя формата данных . .

первого триггера, выходы элементов И первой группы соединены с входом генератора одиночных импульсов, выход которого соединен с запускающим выходом блока и первым входом второго триггера, выход которого соединен с первыми входами элементов И второй группы, выход генератора тактовых импульсов соединен с разрешающим выходом блока и вторыми входами элементов И второй группы, выходы элементов И второй группы соединены с первыми входами элементов И третьей и четвертой групп, выходы элементов И третьей группы являются вторым кодовым выходом блока, выходы элементов И четвертой группы являются первым кодовым выходом блока, первый и второй установочные входы блока через первый элемент ИЛИ соединены с вторым входом второго триггера, первый и второй установочные входы блока через второй элемент ИЛИ соединены с вторым входом первого триггера,первый и второй выходы которого соединены соответственно с вторыми

элементов И третьей и четвертой групп.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1983-01-30—Публикация

1981-09-09—Подача