Изобретение относится к вычислительной технике и может быть использовано для сопряжения электронных вычислительных машин с интерфейсом типа общая шина (ОШ) с удаленными абонентами.

Известно устройство для сопряжения ЭВМ с абонентом, содержащая два блока канальных приемников, блок канальных

приемопередатчиков, дешифратор адреса, генератор синхросимволов, блок прерывания, регистр адреса вектора прерывания, мультиплексор данных, блок шифрации управляющих сигналов, блок преобразования параллельного кода в последовательный и обратно, буферный регистр, коммутатор режима, регистр режима.

Это устройство имеет следующие недостатки.

1.Обмен данными между ЭВМ м устройством сопряжения (УС) осуществляется в несколько этапов: сначала передается через общую шину в ЭВМ адрес вектора прерывания, затем считывается содержимое

,регистра режима (для определения причины прерывания) и, наконец, считывается или записывается байт данных в бло преобразований параллельного кода в последовательный и обратно. Такой алгоритм обмена увеличивает время занятости ОШ прл обмене информацией устройства сопряжения с ЭВМ,

2.В устройстве сопряжения не осуществляется предварительная обработка блоков (пакетов) информации в последовательном коде, например, не определяется начало и конец принимаемых блоков данных в синхронных протоко1ах, не выбрасываются на приеме из потока информации и не вставляются на передаче в поток информации так называемые бит-стаффмн- ги - в протоколах HDLC, X.25. Поэтому ОШ оказывается чрезмерно загружена передачей избыточной информации, принимаемой от абонента, что, во-первых, ограничивает количество подобных устройств сопряжения, подключаемых к ЭВМ, а, во-эторых, загружает ЭВМ выполнением значительной работы по удалению из потока данных избыточной информации.

3.В устройстве сопряжения происходит искажение принимаемых данных в синхронном режиме работы блока преобразования параллельного кода в последовательный и обратно вследствие того, что тактовая частота, поступаемая из генератора синхро- символов, никак не синхронизирована с фронтами битов данных, поступающих из канала связи через буферный регистр.

4.Неэффективно обеспечен приоритет приемника над передатчиком, реализованный на уровне программы. Прм возникновении программных задержек возможны потери принимаемой информации из-за наложения нескольких символов информации в буферном регистре приемника блока преобразования параллельного кода о последовательный и обратно.

При переходе в неисправное состояние ЭВМ, работающей с данным устройством сопряжения, устройство сопряжения не имеет возможности работать во всех режимах с другой ЭВМ, подключенной к этой же общей шине, так как УС подсоединено к конкретной ЭВМ по шинам прерываний.

Наиболее близким к предлагаемому устройству является устройство для сопряжб

ния цифровой вычислительной машины с линиями связи, содержащее дешифратор, регистр режимов, блок прерываний, блок управления, первый и второй коммутаторы,

первый и второй блоки приемопередатчиков, преобразователь последовательного кода 0 параллельный и обратно, блок прямого доступа в памя гь, первый и второй блоки выдачи адреса, регистр состояния, регистр

0 входной информации, регистр выходной информации, третий коммутатор, триггер вы- Оора каналз, первый и второй элементы ИЛИ. Информационный вход регистра режимов и выход первого коммутатора под5 ключейы к выходной и входной информационным шинам ЦВМ, вход де- шисЬратора соединен с адресной шиной ЦВМ, выход запроса на прерывание блока прерываний и выход сопровождения вы0 ходной информации блока управления - с одноименными входными шинами ЦВМ, вход ответа на прерывание блока прерываний и вход сопровождения входной информации - с выходными одноименными

5 шинами ЦВМ. Шинные входы и выходы первого и второго блоков приемопередатчиков подлючены к первой и второй линиям связи. Информационные входы первого и второго блоков приемопередатчиков соеди0 йены с последовательным выходом преобразователя последовательного кода в параллельный и обратно, информационные выходы первого и второго локов приемопередатчиков - соответственно с первым и

5 вторым входами второго коммутатора, выход которого соединен с последовательным входом преобразователя последовательного кода в параллельный и обратно, вход разрешения преобразования и выход конца

0 преобразования которого соединены с соответствующими выходом и входом блока управления, первый и второй выходы дешифратора - соответственно с входами разрешения приема регистра режимов и

5 блока управления, управляющий вход первого коммутатора - с выходом разрешения передачи блока управления, вход режима передачи блока управления - с выходом соответствующего разряда регистра режимов,

0 вход разрешения прерывания блока прерываний - с выходом соответствующего разряда регистра режимов. Выход требования прямого доступа в память и вход разрешения прямого доступа в память блока прямо5 го доступа в память подключены к одноименным входум выходу ЦВМ, выходы разрешения приёма входной информации блока прямого доступа в память и блока управления соединены с входами первого элемента ИЛИ, выход которого соединен с

тактовым входом регистра входной информации, информационный вход которого, а также информационные входы первого и второго блоков выдачи адреса подключены к информационной шине ЦВМ, Выход регистра выходной информации соединен с первым информационным входом третьего коммутатора и первым входом команды блока управления, второй информационный вход третьего коммутатора - с выходом кода состояния блока управления, выход третьего коммутатора - с параллельным информационным входом преобразоавтеля последовательного кода в параллельный и обратно, параллельный выход которого - с информационным входом регистра входной информации, выход которого соединен с вторым входом команды блока управления и первым информационным входом второго коммутатора, тактовый вход регистра выходной информации - с выходом второго элемента ИЛИ, входы которого соединены с выходами разрешения приема выходной информации блока управления и блока прямого доступа в память, первый и второй выходы разрешения выдачи адреса которого соединены с соответствующими входами первого и второго блоков выдачи адреса соответственно, входы выбора которых соединены с третьим и четвертым выходами дешифратора соответственно. Выходы первого и второго блоков выдачи адреса соеди- неныс вторым и третьим

информационными выходами второго коммутатора, четвертый информационный вход которого - с выходом регистра состояния, вход которого - с информационным выходом блока управления. Входы запроса на прерывание и запроса доступа в память блока прерываний и блока прямого доступа в память соответственно соединены с выходами соответствующих разрядов регистра состояния, вход режима прямого доступа в память блока прямого доступа в память - с выходом соответствующего разряда регистра режимов. Вход триггера выбора канала соединен с выходом соответствующего разряда регистра режимов, прямой и инверсный выходы триггера выбора канала - с разрешающими входами первого и второго приемопередатчиков. Блок управления содержит дешифратор, коммутатор, счетчик, первый, второй и третий регистры, элемент И,элемент задержки, причем первый, второй и третий входы дешифратора являются соответственно входом режима передачи, входом разрешения приема и входом сопровождения входной информации блока управления, первый и второй информационные входы коммутатора соединены соответственно с первой и второй группами входов дешифратора и являются первым и вторым входами команды блока управления, 5 четвертый вход дешифратора, счетный вход счетчика, тактовые входы второго и третьего регистров соединены между собой и являются входом конца преобразования блока управления, первый выход дешифра0 тора - с входом элемента задержки, выход которого - с тактовым входом первого регистра и первым входом элемента И, второй вход которого - с вторым выходом дешифратора, а выход элемента И - с входом запи5 си счетчика, информационный вход которого соединен с выходом коммутатора, третий информационный вход которого соединен с первой группой выходов дешифратора. Выход счетчика соединен с пятым

0 входом дешифратора, вторая группа выходов дешифратора - с информационным входом первого регистра, выход которого соединен с информационным входом второго регистра, первый и второй выходы ко5 торого являются выходом разрешения передачи, выходом начала преобразования блока управления. Третий выход соединен с шестым входом дешифратора. Группа выходов второго регистра является информа0 ционным выходом блока управления. ья группа выходов дешифратора соединена с информационным входом третьего регистра, первый, второй выходы которого являются выходами разрешения приемэ

5 входной информации и выходной информации блока соответственно. Группа выходов третьего регистра является выходом кода состояния блока, причем блок прямого доступа в память содержит регистр запросов,

0 первый и второй элементы И, элемент ИЛИ и дешифратор. Вход регистра запросов является входом запросов прямого доступа в память блока, выходы регистра соединены с группой входов дешифратора и с входами

5 элемента ИЛИ, выход которого соединен с первыми входами первого и второго элементов И, второй вход первого элемента И - с выходом первого триггера, а выход первого элемента И -с установочным входом второго триггера, сбросовый вход которого

0 соединен с первым выходом дешифратора, а инверсный вы/од второго триггера - с первым входом дешифратора и сбросовым входом первого триггера, установочный вход которого соединен с вторым входом

5 дешифратора и является входом разрешения прямого доступа в память блока. Первый, второй, третий и четвертый выходы дешифратора являются первым и вторым выходами разрешения выдачи адреса блока и выходами приема входной информации

и выходной информации блока. Второй вход второго элемента И является входом режима прямого доступа в память блока, а выход второго элемента И, единичный выход второго триггера и шестой выход дешифратора образуют выход требования прямого доступа в память блока, причем блок выдачи адреса содержит j счетчик, элемент НЕ, первый и второй эле- , менты И, элемент ИЛИ, элемент задержки и регистр. Первый вход первого элемента И и вход элемента НЕ образуют вход выбора блока, второй вход первого элемента И соединен с выходом элемента НЕ, а выход первого элемента И соединен с входом записи счетчмха, информационный вход которого является информационным входом блока. Счетный вход счетчика соединен с выходом элемента задержки, выход счетчика - с инфорационным входом регистра, выход которого является выходом блока, а тактовый вход регистра соединен с выходом элемента ИЛИ, первый вход которого соединен с входом элемента задержки и выходом второго элемента И, первый вход которого и второй вход элемента ИЛИ образуют вход выдачи адреса, а второй вход второго элемента И соединен с входом набора блока.

Недостатками этого устройства .являются:

1.Не осуществляется предварительная обработка блоков (пакетов) данных, принимаемых от абонента или выдаваемых абоненту, например, не удаляются синхросимволы, необходимые для поддержания символьной синхронизации в каналах связи, не выбрасываются на приеме из потока данных и не вставляются на передаче в поток данных так называемые бит-стаф- финги - в протоколах HDLC, X.25, что, во-первых, увеличивает время обмена с ЭВМ, во-вторых, препятствует подключению к ЭВМ большего количества подобных устройств сопряжения, в-третьих, загружает ЭВМ выполнением значительной работы по удалению из потока данных избыточной информации, по разделению принятой информации на блоки данных и по вставлению в передаваемые данные необходимой избыточной информации.

2.Передача векторов прерываний в ЭВМ осуществляется за два этапа обращения ЭВМ к УС: сначала передается адрес вектора прерываний, а затем содержимое регистра состояния с информацией о причине, вызвавшей прерывание, что также увеличивает время занятости общей иыны при обмене информацией между УС и ЭВМ.

3.При обмене с ЭВМ по прямому доступу в память (ПДП) в случае неисправности в ЭВМ, либо в адресной части устройства сопряжения возможно зависание ОШ вследствии того, что устройство сопряжения не может принудительно снять собственные сигналы и освободить ОШ.

4.В устройстве сопряжения происходит потеря принимаемых блоков данных в слу0 чае, когда ЭВМ не успевает занести новый адрес в блок выдачи адреса, а данные из канала связи уже приняты в преобразователь последовательного кода в параллельный и обратно.

5 5. При переходе в неисправное состояние ЭВМ, работающей с данным устройством сопряжения, устройство сопряжения не имеет возможности работать с другой ЭВМ, подключенной к этой ОШ, вследствие того,

0 что оно подключено по шинам прерываний к конкретной ЭВМ.

Целью изобретения является сокращение времени обмена с ЭВМ.

Согласно предлагаемому изобретению

5 устройство, содержащее дешифратор, регистр режимов, первый и второй коммутаторы, блок приемопередатчиков, преобразователь последовательного кода в параллельный и обратно, блок прямого до0 ступа в память, регистр состояния, причем вход дешифратора соединен с адресной шиной ЭВМ, шинные входы и выходы блока приемопередатчика подключены к линии связи, а информационный выход приемопе5 редатчика соединен с первым входом второго коммутатора, введены блок предварительной обработки принимаемой информации, блок предварительной обработки передаваемой информации, блок фор0 мирования запросов прямого доступа к памяти, шифратор приоритетов, регистр системных прерываний, шифратор управляющих сигналов, таймер, регистр номера ЭВМ, блок шинных формирователей управляю5 щих сигналов, блок захвата общей шины,причем, первый вход управления блока предварительной обработки принимаемой информации соединен с выходом регистра режимов, с первыми управляющими входа0 ми блока предварительной обработки передаваемой информации, шифратора управляющих сигналов, второго коммутатора, второй информационный вход которого соединен с информационным выходом пре

5 образователя последовательного кода в параллельный и обратно, являющимся входом готовности абонента, первый информационный выход второго коммутатора - с первым входом примопередатчика, второй информационный вход которого соединен с

последовательным выходом блока предварительной обработки передаваемой информации и с третьим информационным входом второго коммутатора, четвертый информационный вход которого соединен с выходом блока шинных формирователей управляющих сигналов, с вторым управляющим входом шифратора управляющих сигналов, с первыми управляющими входами дешифратора, блока захвата общей шины, первого коммутатора, таймера, блока прямого доступа в память, преобразователя последовательного кода в параллельный и обратно, второй управляющий вход которого соединен с первым управляющим выходом шифратора управляющих сигналов, с первыми управляющими входами шинного формирователя управляющих сигналов, регистра номера ЭВМ, регистра системных прерываний, регистра состояния, блока формирования запросов прямого доступа к памяти, регистра режима, с вторыми управляющими входами блока прямого доступа в память, первого коммутатора, таймера, блока предварительной обработки передаваемой информации, блока предварительной обработки принимаемой информации, третий управляющий и последовательный входыкоторогосоединеныссоответствующими выходами второго коммутатора и с третьим управляющим входом блока предварительной обработки передаваемой информации, последовательный вход которого соединен с соответствующим выходом преобразователя последовательного кода в параллельный и обратно, вход синхронизации передаваемой информации которого соединен с соответствующим выходом блока предварительной обработки передаваемой информации, четвертый управляющий вход которого соединен с управляющим выходом преобразователя последовательного кода в параллельный и обратно, с первым информационным входом регистра состояний, с четвертым управляющим входом блока предварительной обработки принимаемой информации, последовательный выход и выход синхронизации принимаемой информации которого соединены с соответствующими входами преобразователя последовательного кода в параллельный и обратно, выход готовности приема и готовности выдачи которого соединены с пятым управляющим входом блока предварительной обработки передаваемой информации, с соответствующими входами блока формирования запросов прямого доступа к памяти, первые два выхода которого являются запросами на прямой доступ к памяти на передачу принятых от абонента данных в ЭВМ и подключены к соответствующим входам блока прямого доступа в память, третий выход блока формирования запросов прямого доступа к 5 памяти является запросом на прямой доступ к памяти на выдачу данных из ЭВМ к абоненту и подключен к соответствующему входу блока прямого доступа в память, информационный вход-выход которого соеди0 нен с выходом регистра системных прерываний, с информационными входами регистра режима, шифратора управляющих сигналов, регистра номера ЭВМ, с первым информационным входом-выходом пер5 вого коммутатора, со входом-выходом преобразователя последовательного кода в параллельный и обратно, адресный вход которого соединен с адресным входом шифратора управляющих сиг0 налов, с первыми адресными входами-выходами первого коммутатора, блока прямого доступа в память, первые выходы которого являются подтверждениями запросов прямого доступа к памяти и

5 соединены с третьим управляющим входом шифратора управляющих сигналов, со вторыми управляющими входами блока форми- рования запросов прямого доступа к памяти, четвертый выход которого является

0 идентификатором канала прямого доступа к памяти, осуществляющего передачу в ЭВМ принятых от абонента данных, и соединен с первым информационным входом регистра системных прерываний, вторая группа ин5 формационных входов которого соединена с первым выходом шифратора приоритетов, второй выход которого является запросом на прямой доступ к памяти на передачу прерываний и подключен к соответствующему

0 входу блока прямого доступа в память, третий выход которого является общим признаком конца счета всех каналов блока прямого доступа в память и соединен со вторым информационным входом регистра

5 состояния, третий информационный вход которого соединен с соответствующим выходом блока предварительной обработки принимаемой информации, а выход регистра состояния соединен с информационным

0 входом шифратора приоритетов, с третьим управляющим входом блока формирования запросов прямого доступа к памяти, с четвертым управляющим входом шифратора управляющи с сигналов, с вторым управляю5 щим входом блока захвата общей шины, третий управляющий вход которого соединен с выходом управления блока прямого доступа в память, с вторым управляющим входом шинного формирователя управляющих сигналов, с третьими управляющими

входами первого коммутатора и таймера, выход которого соединен с четвертым информационным входом регистра состояния, второй управляющий вход которого соединен с вторым управляющим выходом шифратора управляющих сигналов, первый выход блока захвата общей шины соединен с информационным входом шинного формирователя управляющих сигналов, третий управляющий вход которого соединен с вторым выходом блока захвата общей шины, с разрешающим входом регистра номера ЭВМ, с третьим управляющим входом блока прямого доступа в память, управляющий вход-выход которого соединен с входом-выходом шинного формирователя управляющих сигналов, разрешающий вход которого соединен с пятым управляющим входом шифратора управляющих сигналов, с выходом дешифратора, второй выход которого является собственным адресом устройства сопряжения и соединен с соответствующим входом регистра системных прерываний, входы готовности преобразователя последовательного кода в параллельный и обратно являются выходами готовности абонента и подключены к соответствующим выходам второго коммутатора, выход регистра номера ЭВМ соединен с адресным входом дешифратора, с вторым адресным входом-выходом первого коммутатора и с адресной шиной ЭВМ, шина данных ЭВМ подключена ко второму информационному входу-выходу первого коммутатора, шина управления ЭВМ подключена к входу-выходу шинного формирователя управляющих сигналов.

Сопоставительный анализ предлагаемого решения с прототипом показывает, что предлагаемое устройство отличается наличием новых блоков: блока предварительной обработки принимаемой информации, блока предварительной обработки передаваемой информации, блока формирования запросов прямого доступа к памяти шифратора приоритетов, регистра системных прерываний, шифратора управляющих сигналов, таймера, регистра номера ЭВМ, блока шинных формирователей управляющих сигналов, блока захвата общей шины - и их взаимосвязями с остальными элементами схемы.

Таким образом, предлагаемое устройство соответствует критерию изобретения новизна.

Сравнение предлагаемого решения с другими техническими решениями показывает, что все введенные блоки широко известны. Однако при их введении в указанной связи с остальными элементами схемы в

предлагаемое устройство для сопряжения ЭВМ с абонентом, вышеуказанные блоки в их совокупности обеспечивают устройству новое качество, а именно, сокращение

времени обмена с ЭВМ, повышение надежности. Это позволяет сделать вывод о соответствии технического решения критерия существенные отличия.

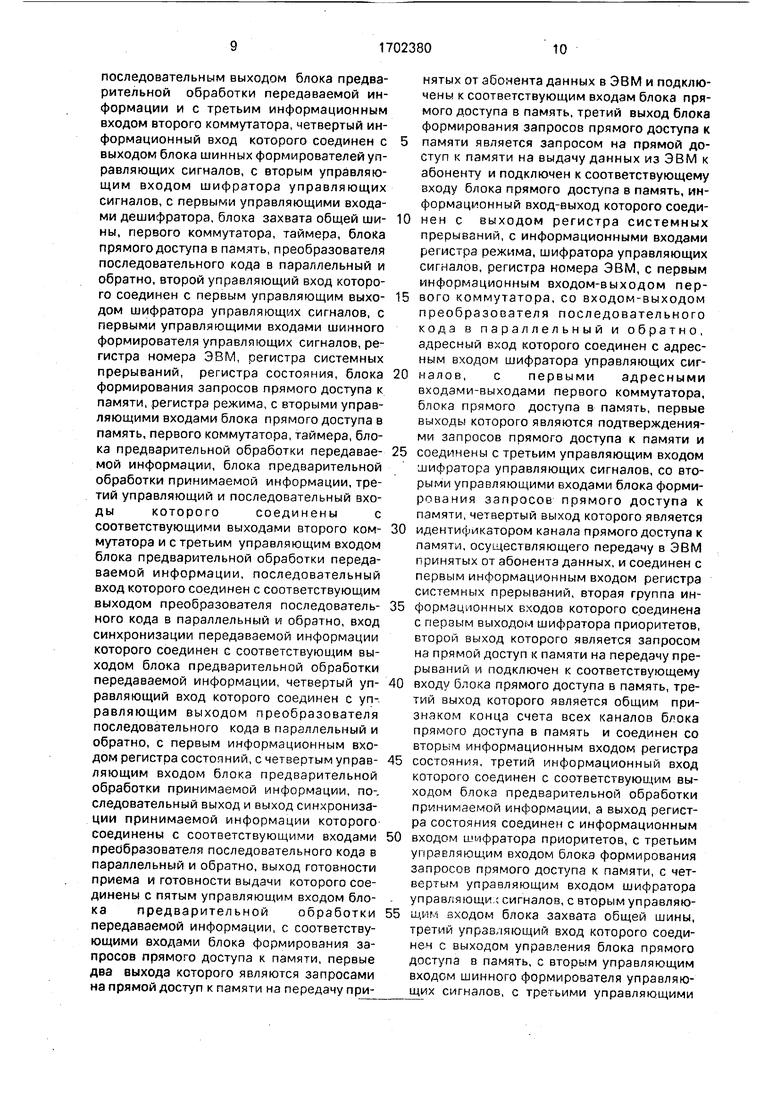

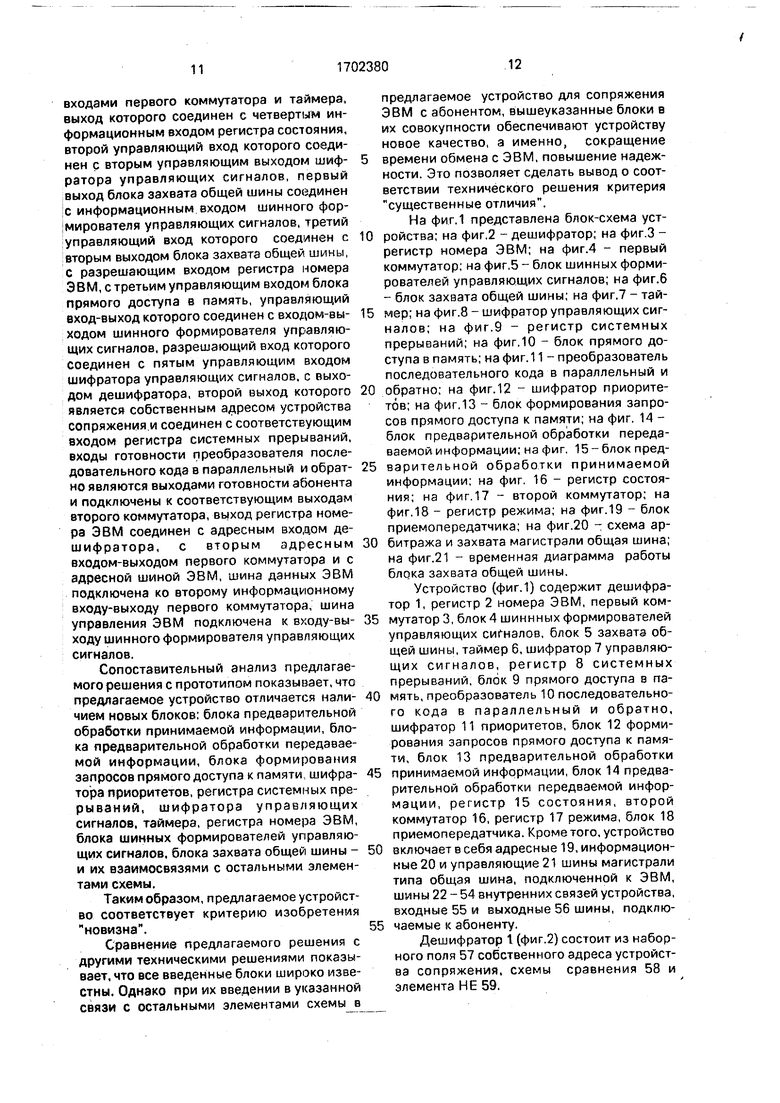

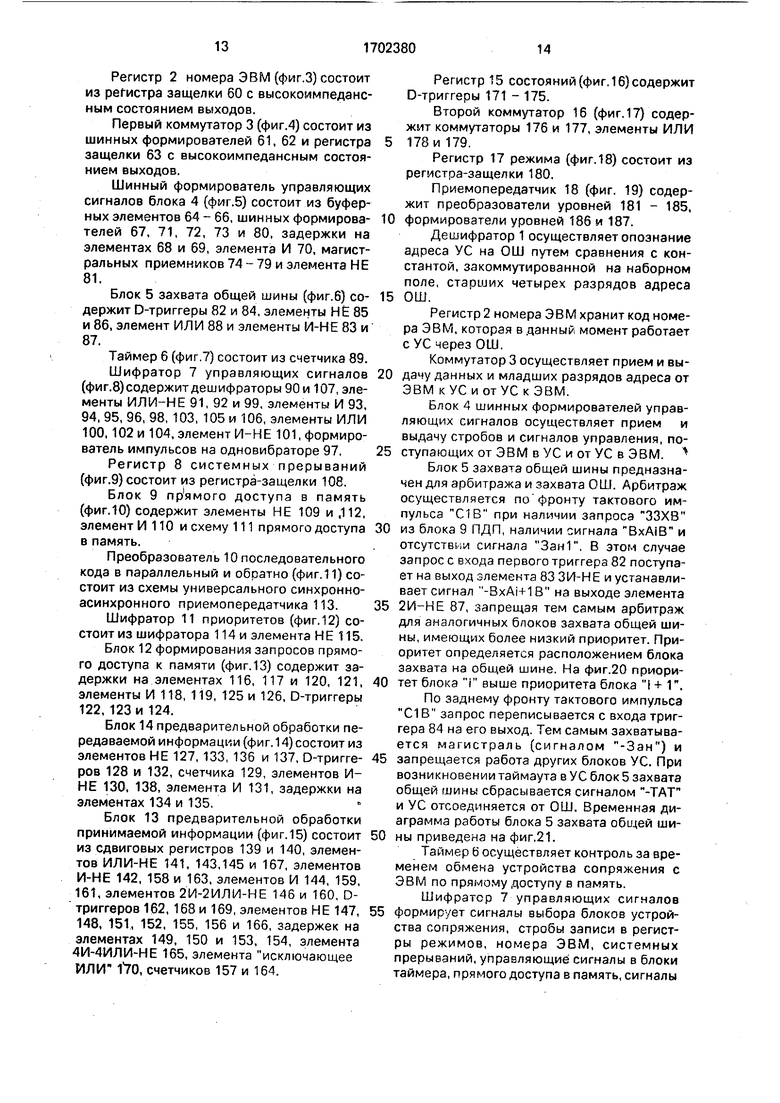

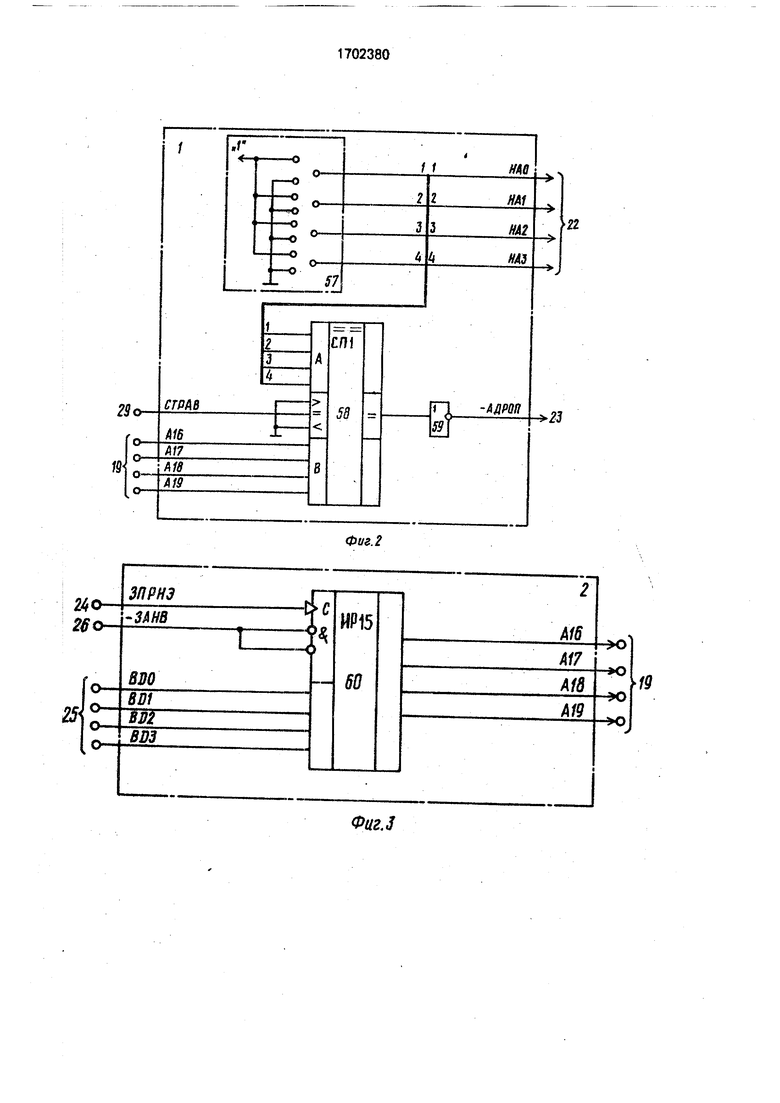

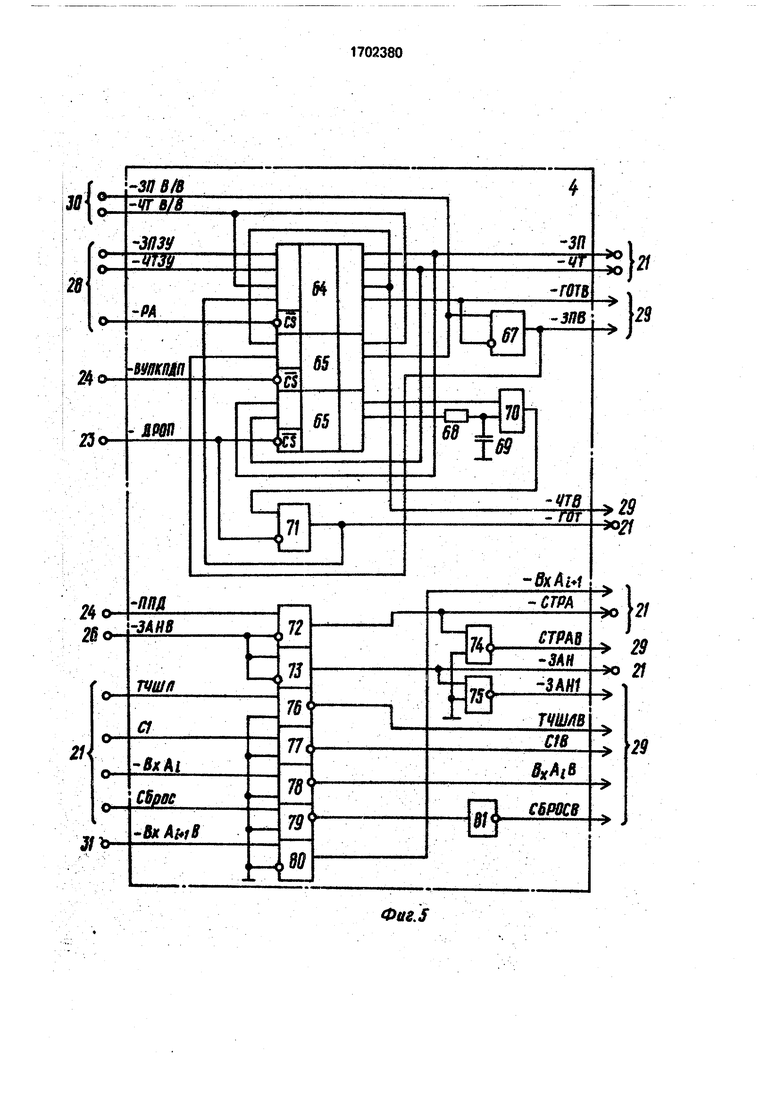

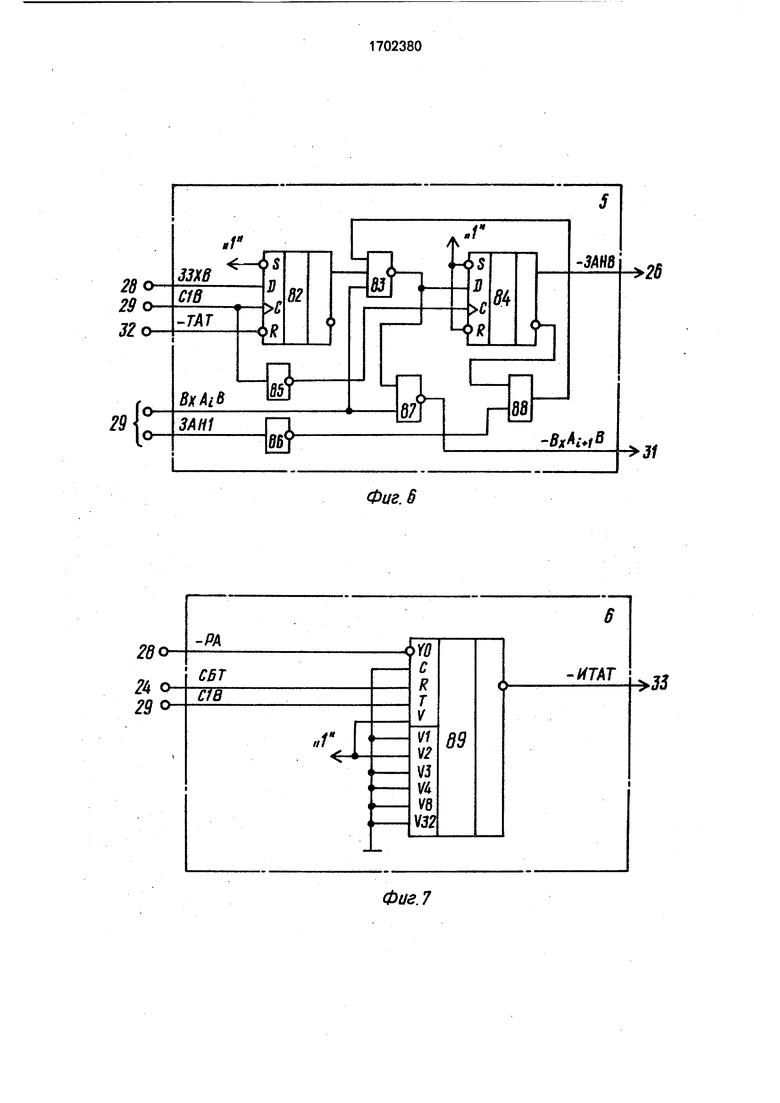

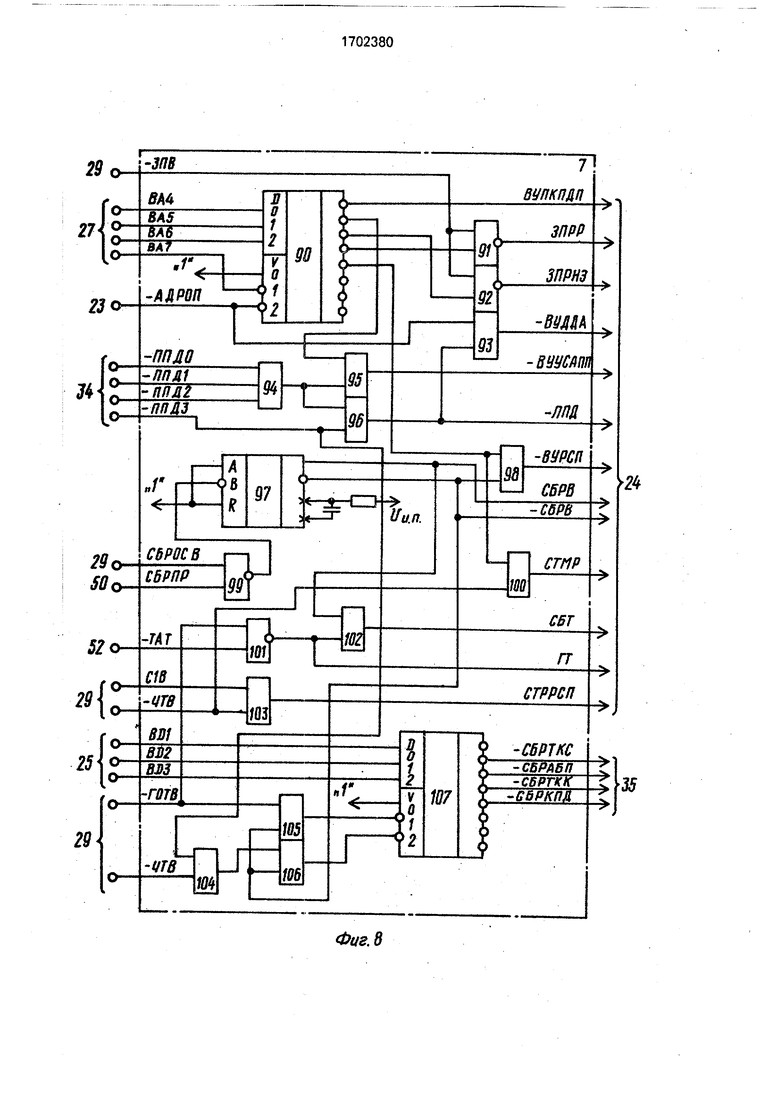

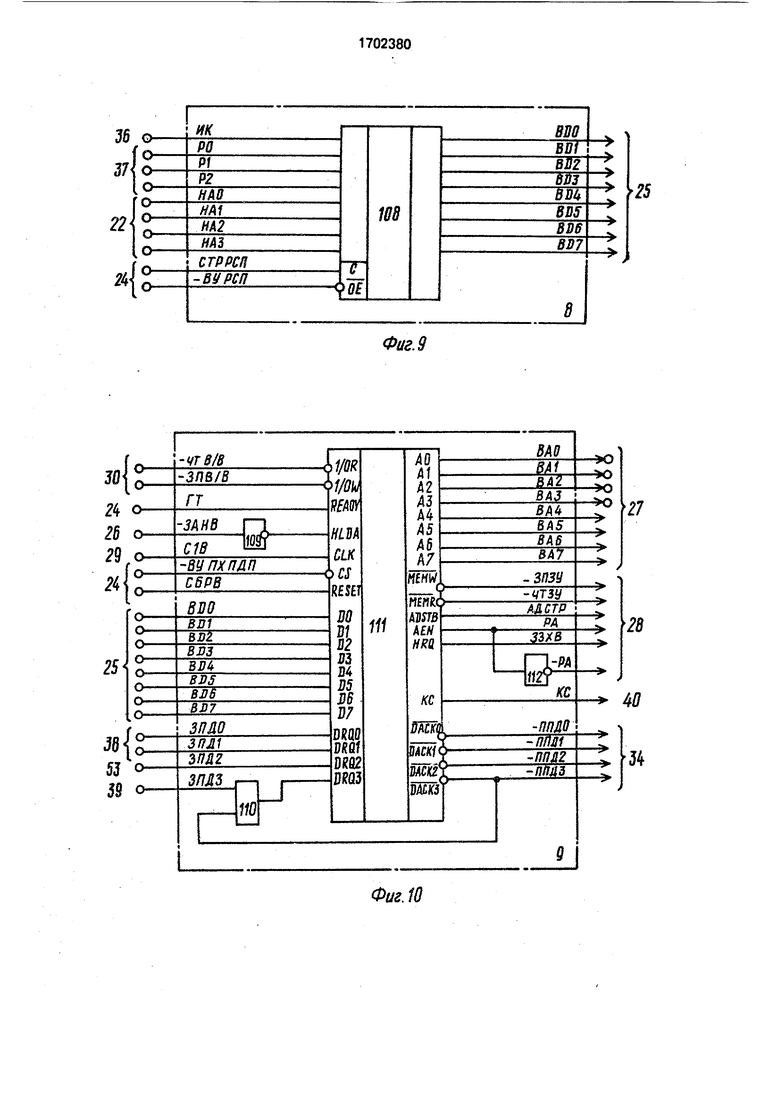

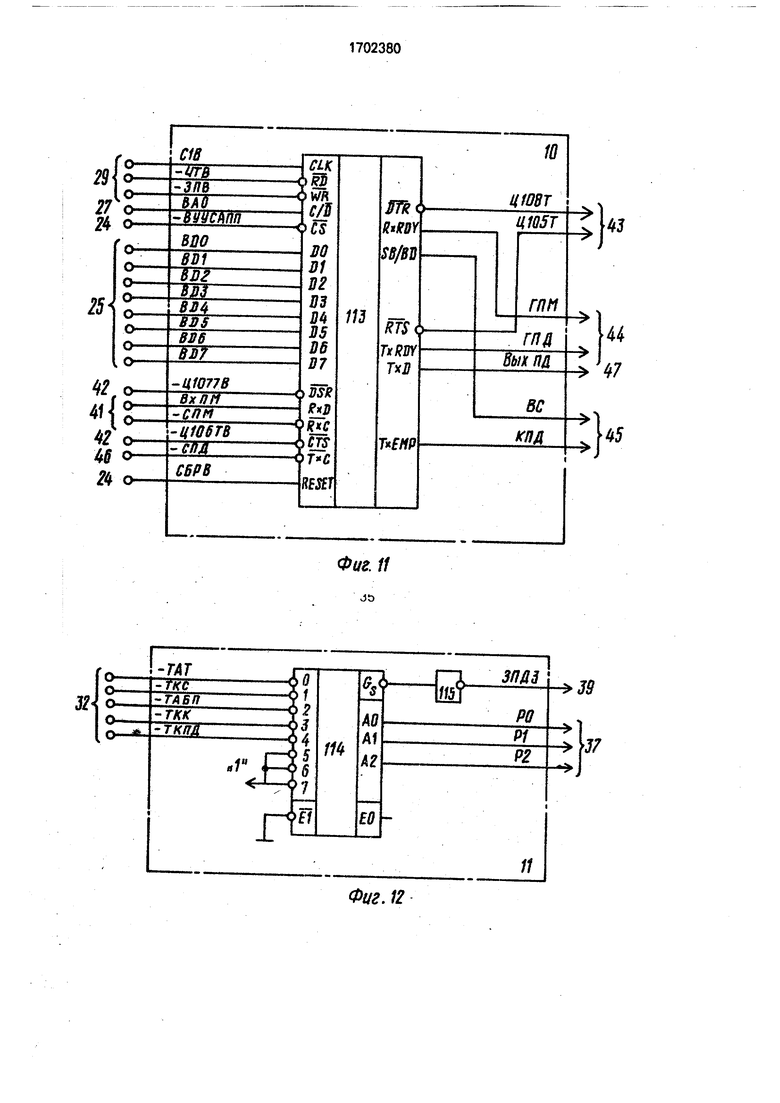

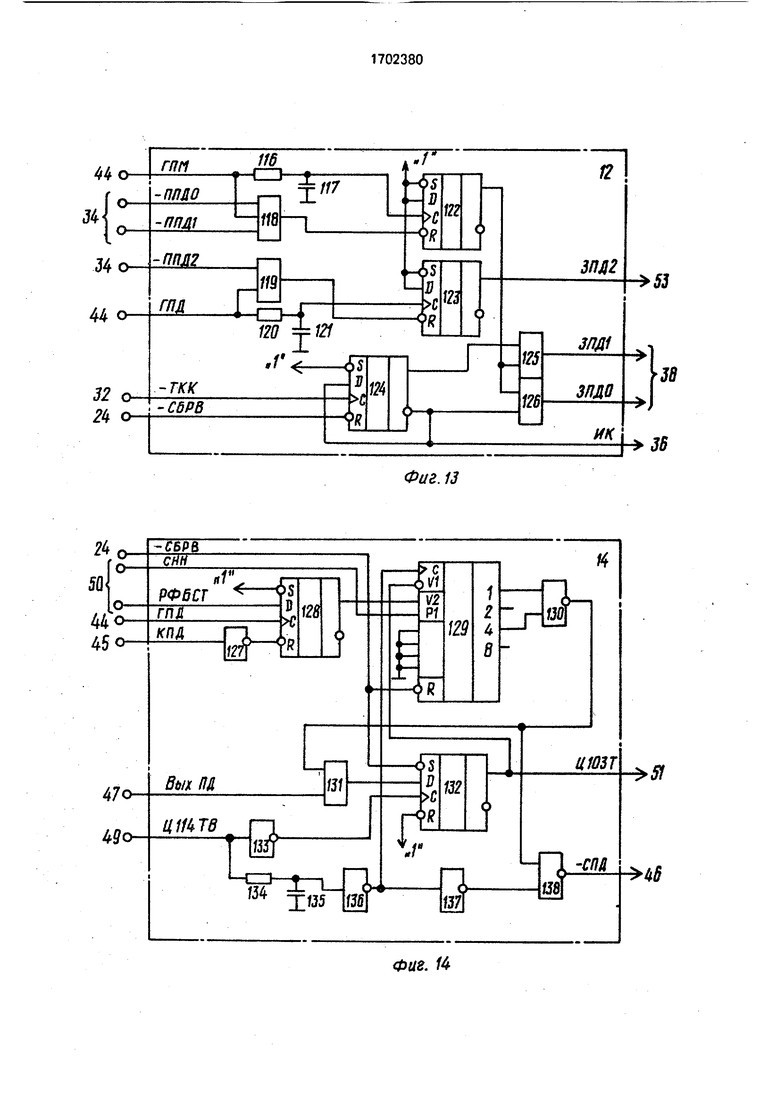

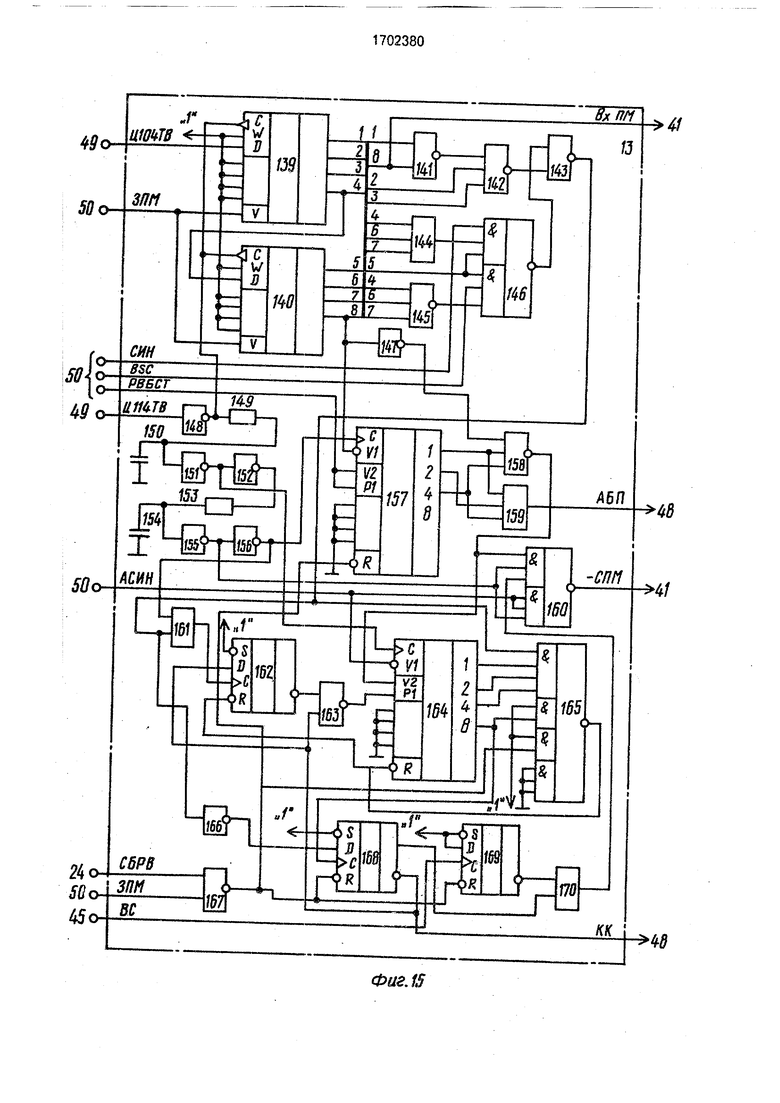

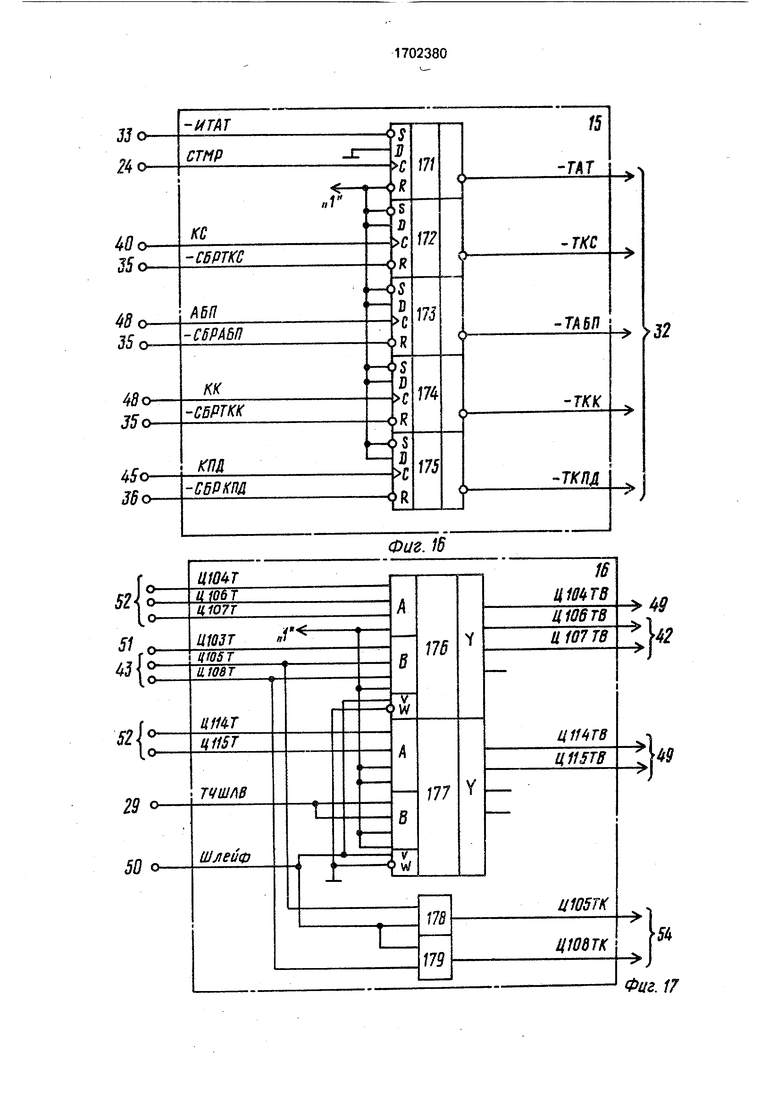

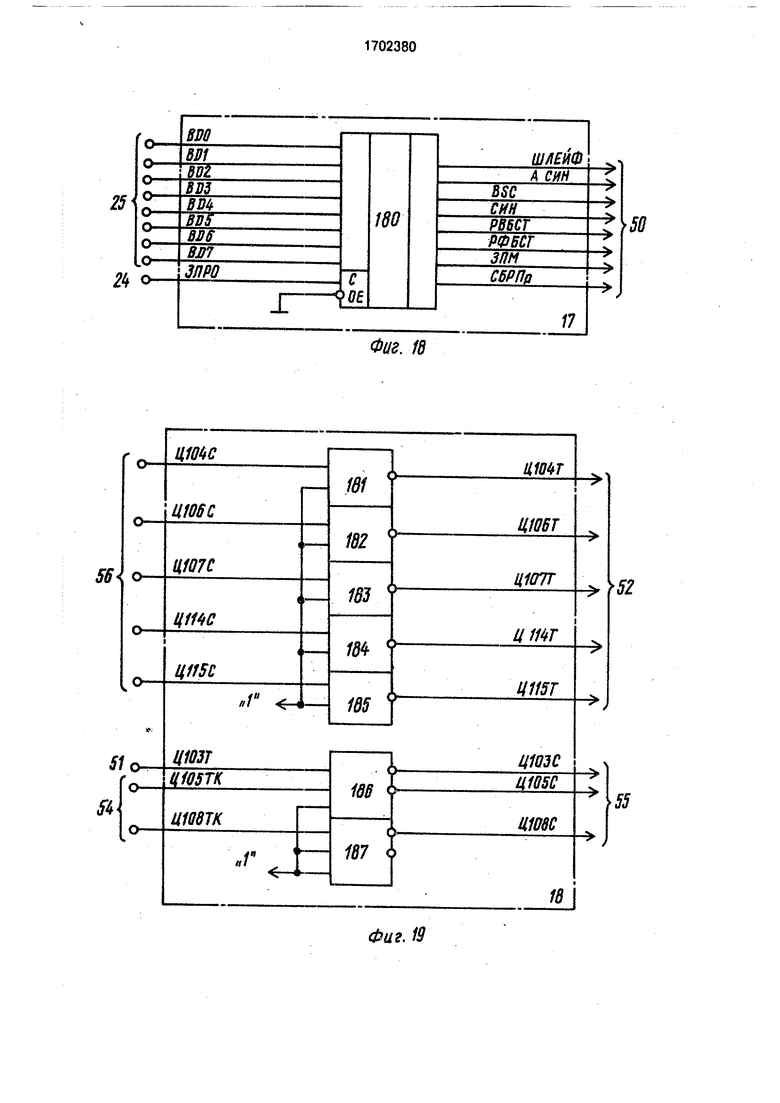

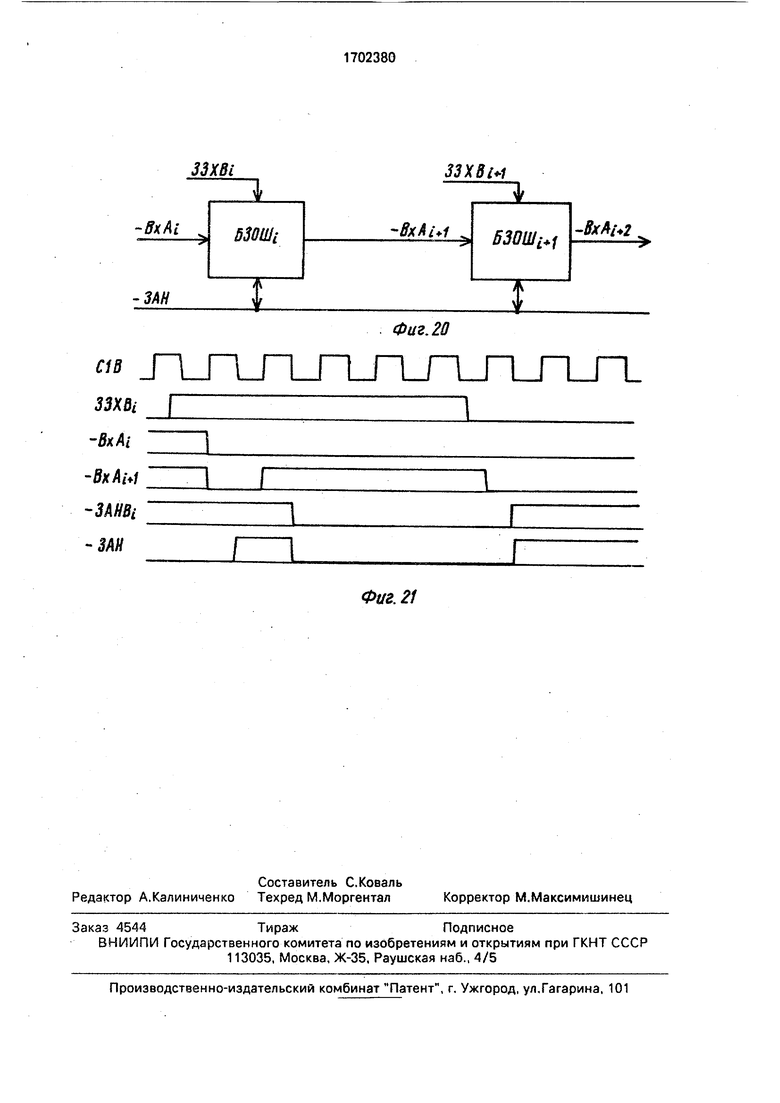

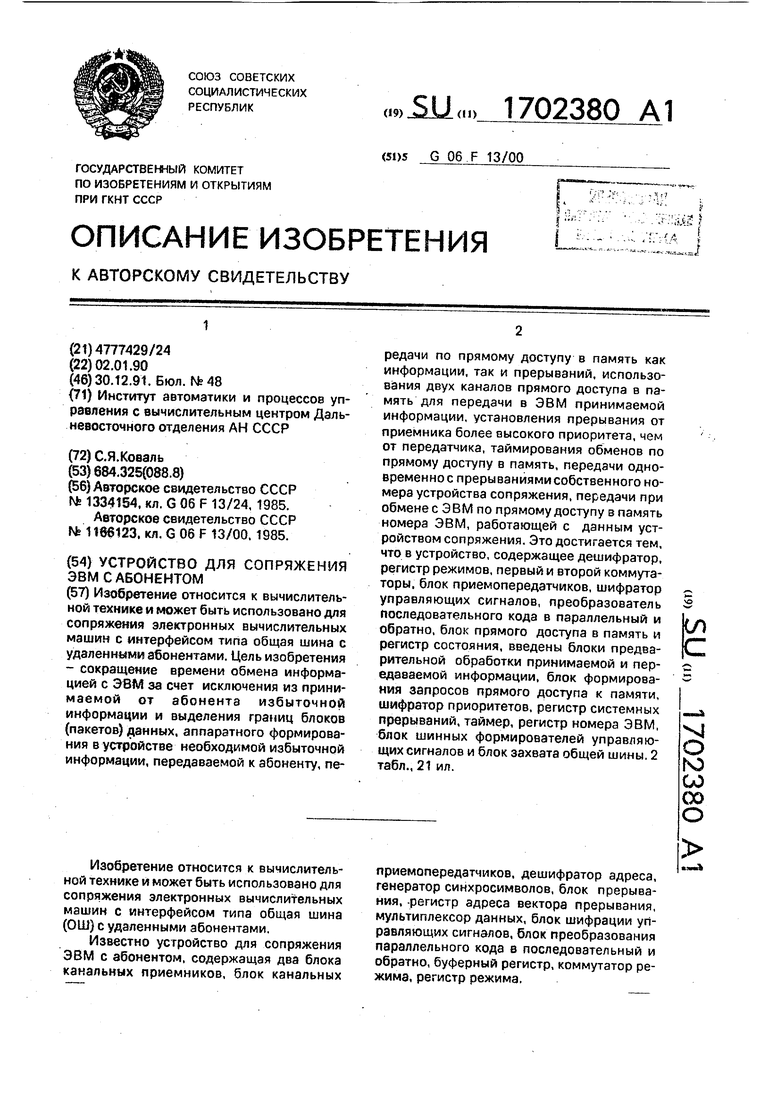

На фиг.1 представлена блок-схема устройства; на фиг,2 - дешифратор; на фиг.З - регистр номера ЭВМ; на фиг.4 - первый коммутатор; на фиг,5 - блок шинных формирователей управляющих сигналов; на фиг.6 - блок захвата общей шины; на фиг.7 - таймер; на фиг.8 - шифратор управляющих сигналов; на фиг.9 - регистр системных прерываний; на фиг.10 - блок прямого доступа в память; на фиг. 11 - преобразователь последовательного кода в параллельный и

обратно; на фиг. 12 - шифратор приоритетов; на фиг.13 - блок формирования запросов прямого доступа к памяти; на фиг. 14 - блок предварительной обработки передаваемой информации; на фиг. 15 - блок предварительной обработки принимаемой информации; на фиг. 16 - регистр состояния; на фиг. 17 - второй коммутатор; на фиг.18 - регистр режима; на фиг.19 - блок приемопередатчика; на фиг.20 - схема арбитража и захвата магистрали общая шина; на фиг.21 - временная диаграмма работы блока захвата общей шины.

Устройство (фиг.1) содержит дешифратор 1, регистр 2 номера ЭВМ, первый коммутатор 3, блок 4 шиннных формирователей управляющих сигналов, блок 5 захвата общей шины, таймер 6, шифратор 7 управляющих сигналов, регистр 8 системных прерываний, блок 9 прямого доступа в память, преобразователь 10 последовательного кода в параллельный и обратно, шифратор 11 приоритетов, блок 12 формирования запросов прямого доступа к памяти, блок 13 предварительной обработки

принимаемой информации, блок 14 предварительной обработки передваемой информации, регистр 15 состояния, второй коммутатор 16, регистр 17 режима, блок 18 приемопередатчика. Кроме того, устройство

включает в себя адресные 19, информационные 20 и управляющие 21 шины магистрали типа общая шина, подключенной к ЭВМ, шины 22 - 54 внутренних связей устройства, входные 55 и выходные 56 шины, подключаемые к абоненту.

Дешифратор t (фиг.2) состоит из наборного поля 57 собственного адреса устройства сопряжения, схемы сравнения 58 и элемента НЕ 59.

Регистр 2 номера ЭВМ (фиг.З) состоит из регистра защелки 60 с высокоимпеданс- ным состоянием выходов.

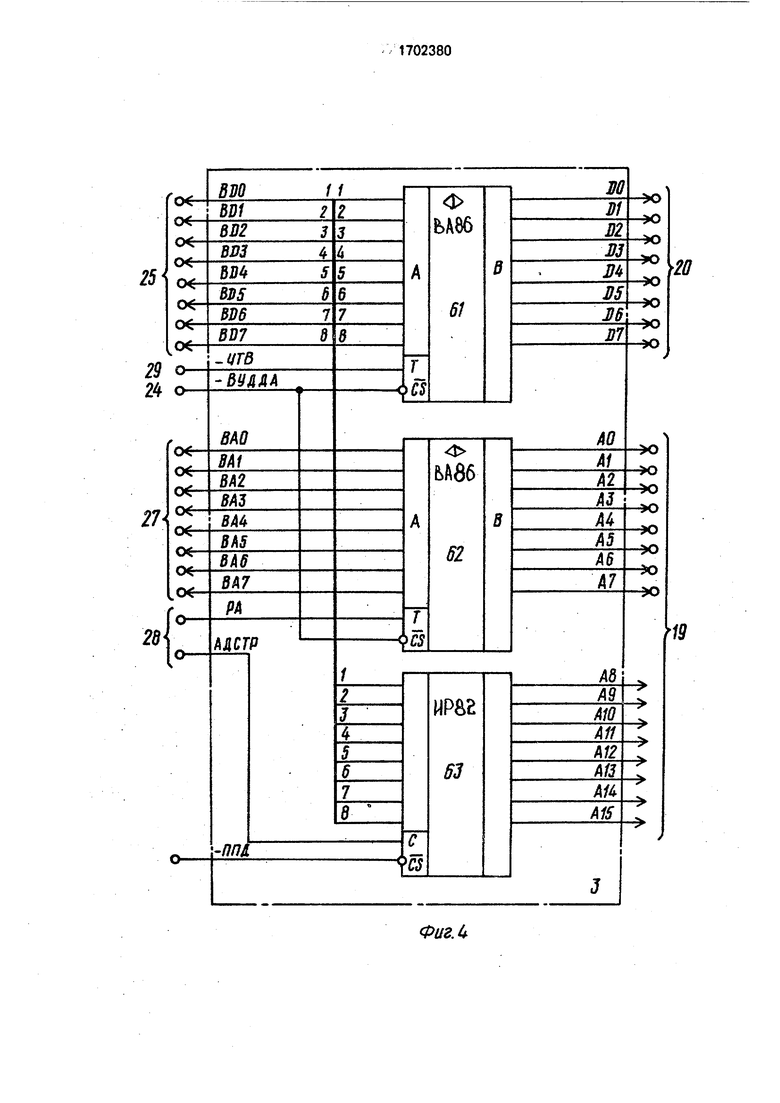

Первый коммутатор 3 (фиг.4) состоит из шинных формирователей 61, 62 и регистра защелки 63 с высокоимпедансным состоянием выходов.

Шинный формирователь управляющих сигналов блока 4 (фиг.5) состоит из буферных элементов 64 - 66, шинных формирователей 67, 71, 72, 73 и 80, задержки на элементах 68 и 69, элемента И 70, магистральных приемников 74 - 79 и элемента НЕ 81.

Блок 5 захвата общей шины (фиг.6) содержит D-триггеры 82 и 84, элементы НЕ 85 и 86, элемент ИЛИ 88 и элементы И-НЕ 83 и 87.

Таймер 6 (фиг.7) состоит из счетчика 89.

Шифратор 7 управляющих сигналов (фиг.8) содержит дешифраторы 90 и 107, элементы ИЛИ-НЕ 91, 92 и 99, элементы И 93, 94, 95, 96, 98, 103, 105 и 106, элементы ИЛИ 100,102 и 104, элемент И-НЕ 101, формирователь импульсов на одновибраторе 97,

Регистр 8 системных прерываний (фиг.9) состоит из регистра-защелки 108.

Блок 9 пр ямого доступа в память (фиг.10) содержит элементы НЕ 109 и .112, элемент И 110 и схему 111 прямого доступа в память.

Преобразователь 10 последовательного кода в параллельный и обратно (фиг. 11) состоит из схемы универсального синхронно- асинхронного приемопередатчика 113.

Шифратор 11 приоритетов (фиг.12) состоит из шифратора 114 и элемента НЕ 115.

Блок 12 формирования запросов прямого доступа к памяти (фиг. 13) содержит задержки на элементах 116, 117 и 120, 121, элементы И 118, 119, 125 и 126, D-триггеры 122, 123 и 124.

Блок 14 предварительной обработки передаваемой информации (фиг. 14) состоит из элементов НЕ 127,133, 136 и 137, D-тригге- ров 128 и 132, счетчика 129, элементов И- НЕ 130, 138, элемента И 131, задержки на элементах 134 и 135.

Блок 13 предварительной обработки принимаемой информации (фиг. 15) состоит из сдвиговых регистров 139 и 140, элементов ИЛИ-НЕ 141, 143,145 и 167, элементов И-НЕ 142, 158 и 163, элементов И 144, 159, 161, элементов 2И-2ИЛИ-НЕ 146 и 160, D- триггеров 162, 168 и 169, элементов НЕ 147, 148, 151, 152, 155, 156 и 166, задержек на элементах 149, 150 и 153, 154, элемента 4И-4ИЛИ-НЕ 165, элемента исключающее ИЛИ f70, счетчиков 157 и 164.

Регистр 15 состояний (фиг, 16) содержит D-триггеры 171 - 175.

Второй коммутатор 16 (фиг. 17) содержит коммутаторы 176 и 177, элементы ИЛИ 5 178 и 179.

Регистр 17 режима (фиг. 18) состоит из регистра-защелки 180.

Приемопередатчик 18 (фиг. 19) содержит преобразователи уровней 181 - 185, 0 формирователи уровней 186 и 187.

Дешифратор 1 осуществляет опознание адреса УС на ОШ путем сравнения с константой, закомментированной на наборном поле, старших четырех разрядов адреса 5 ОШ.

Регистр 2 номера ЭВМ хранит код номера ЭВМ, которая в данный момент работает с УС через ОШ.

Коммутатор 3 осуществляет прием и вы- 0 дачу данных и младших разрядов адреса от ЭВМ к УС и от УС к ЭВМ.

Блок 4 шинных формирователей управляющих сигналов осуществляет прием и выдачу стробов и сигналов управления, по- 5 ступающих от ЭВМ в УС и от УС в ЭВМ. Блок 5 захвата общей шины предназначен для арбитража и захвата ОШ. Арбитраж осуществляется по фронту тактового импульса С1В при наличии запроса ЗЗХВ 0 из блока 9 ПДП, наличии сигнала BxAiB и отсутствии сигнала Зан1, В этом случае запрос с входа первого триггера 82 поступает на выход элемента 83 ЗИ-НЕ и устанавливает сигнал -BxAi+18 на выходе элемента 5 2И-НЕ 87, запрещая тем самым арбитраж для аналогичных блоков захвата общей шины, имеющих более низкий приоритет. Приоритет определяется расположением блока захвата на общей шине. На фиг.20 приори- 0 тет блока i выше приоритета блока i +1. По заднему фронту тактового импульса С1В запрос переписывается с входа триггера 84 на его выход. Тем самым захватывается магистраль (сигналом -Зан) и 5 запрещается работа других блоков УС. При возникновении таймаута в УС блок 5 захвата общей шины сбрасывается сигналом -ТАТ и УС отсоединяется от ОШ. Временная диаграмма работы блока 5 захвата общей ши- 0 ны приведена на фиг.21.

Таймер 6 осуществляет контроль за временем обмена устройства сопряжения с ЭВМ по прямому доступу в память.

Шифратор 7 управляющих сигналов 5 формирует сигналы выбора блоков устройства сопряжения, стробы записи в регистры режимов, номера ЭВМ, системных прерываний, управляющие сигналы в блоки таймера, прямого доступа в память, сигналы

общего сброса УС и сбросов разрядов регистра состояния.

Регистр 8 системных прерываний запоминает и выдает в ЭВМ код наиболее приоритетного признака прерывания, собственный адрес УС и признак канала прямого доступа в память, осуществляющего передачу в ЭВМ принимаемых от абонента данных в текущий момент.

Блок 9 прямого доступа в память осуществляет обмен с ЭВМ на внепроцессорном уровне, реализован на элементе КР580ВТ57 и представляет собой программируемый контроллер прямого доступа в память (ПКПДП).

Преобразователь 10 последовательного кода в параллельный и обратно реализован на элементе КР580ВВ51А и представляет собой универсальный синхронно-асинхронный приемопередатчик (УСАПП) и осуществляет преобразование принятой от ЭВМ по двухнаправленным шинам ВДО - ВД7 информации в параллельном формате в последовательный формат на выходе, а также обратное преобразование информации, принятой в последовательном формате, с выдачей ее на шине ВДО - ВД7.

Шифратор 11 приоритетов осуществляет шифрацию признаков прерываний, выдает код самого приоритетного признака, а также формирует запрос на прямой доступ в память и реализован на микросхеме К155ИВ1.

Блок 12 формирования запросов ПДП предназначен для формирования запросов в блок прямого доступа в память на передачу в ЭВМ принятых от абонента данных или на считывание из ЭВМ данных, предназначенных для передачи к абоненту.

Блок 13 предварительной обработки принимаемой информации осуществляет выделение блоков данных из общего потока принимаемой от абонента информации в синхронных протоколах, формирует признаки прерывания конец кадра(КК)и принята абортирующая последовательность (АБЦ), удаляет бит-стаффинги из потока информации в протоколах Х.25, HDLC.

Блок 14 предварительной обработки передаваемой информации обеспечивает вставление бит стаффингов в блоки данных в протоколах Х.25, HDLC.

Регистр 15 состояния хранит результаты действий, выполненных в УС.

Коммутатор 16 обеспечивает работу устройства в режиме Шлейф. В этом режиме УС отключается от абонента, при этом поток информации в последовательном формате с выхода блока предварительной обработки передаваемой информации поступает через коммутатор на вход блока предварительной обработки принимаемой информации.

Регистр 17 режима задает различные режимы работы УС.

Приемопередатчик 18 обеспечивает согласование сигналов УС и абонента.

Устройство работает следующим образом,

Со стороны общей шины устройство представляет собой поле адресов шириной 20 разрядов. Старшие 4 разряда на ОШ являются полем номеров устройств, подключенных к данной ОШ, в том числе ЭВМ. Младшие разряды (А15 - АО ) являются полем адресов ЭВМ.

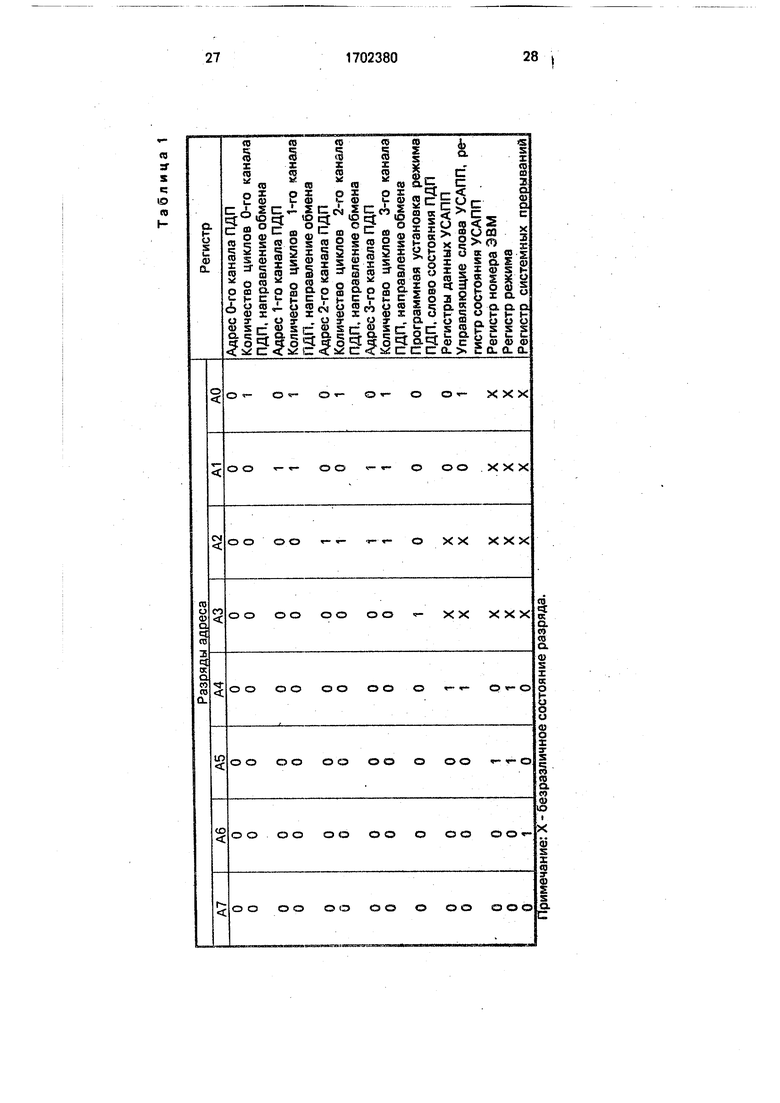

Аресация внутри устройства сопряжения осуществляется в соответствии с табл. 1.

Назначение разрядов регистров. Регистр 2 номера ЭВМ (РНЭ):

0разряд РНЗ (запись) - бит адреса А16 ОШ;

1разряд РНЭ (запись) - бит адреса А 17 ОШ;

2 разряд РНЭ (запись) - бит адреса А18 ОШ;

3 разряд РНЭ (запись) - бит адреса А19 ОШ.

ПРИМЕЧАНИЕ: Содержимое РНЭ используется при обмене с ЭВМ в режиме прямого доступа к памяти для задания номера ЭВМ, работающей с данным УС.

Регистр 17 режима (РР):

Ор РР - режим Шлейф (выходы УС замыкаются нз собственные входы);

1р РР - асинхронный режим;

2р РР - режим протокола

Зр РР - синхронный (диагностический); 4р РР - разрешение выбрасывания бит-стаффинга ;

5р РР - разрешение формирования бит-стаффинга ;

6р РР - запрет приема; 7р РР - программный сброс.

Регистр 15 состояний (PC):

Op PC - бит ошибки (тайм-аут) (ТАТ);

1р PC - бит конца счета (ТКС);

2р PC - бит приема абонирующей по- следовательности (ТАБП);

Зр PC - бит конца кадра );

4р PC - бит конца передачи (ТКПД).

Регистр 8 системных прерываний (РСП);

Ор РСП - идентификатор канала ПДП, осуществляющего передачу в ЭВМ принятой от абонента информации;

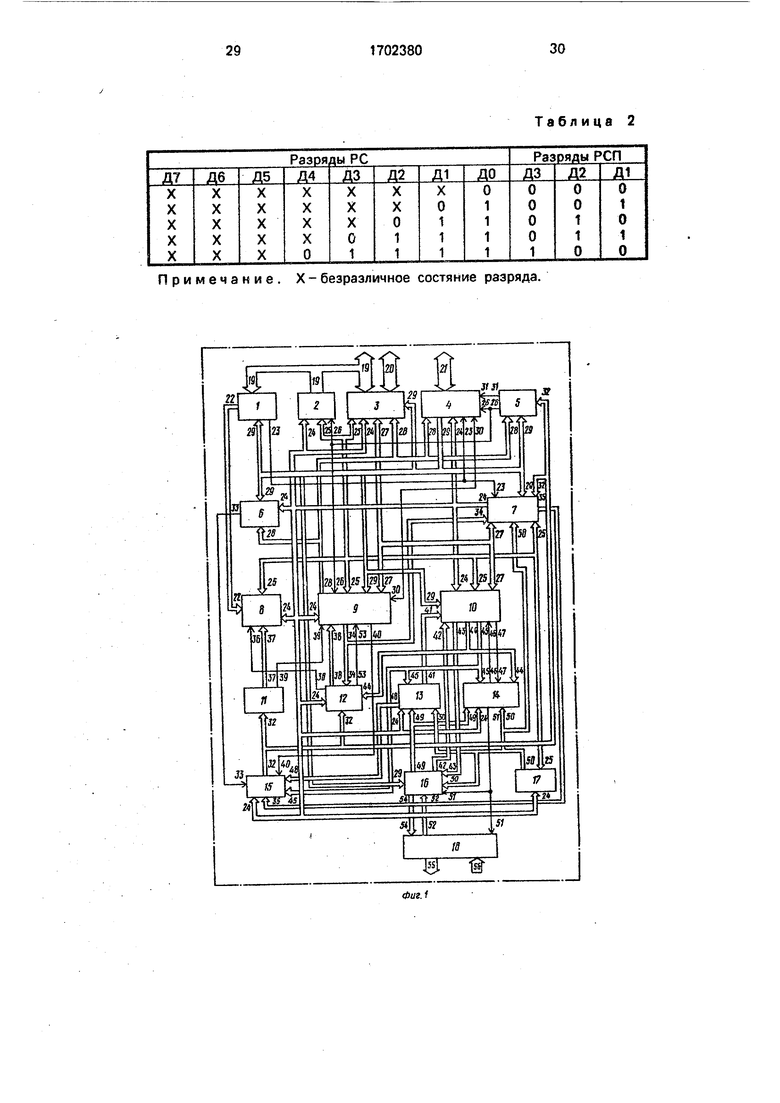

1, 2, Зр РСП - код наиболее приоритетного прерывания в регистре состояний (соответствие разрядов PC коду в РСП показано в табл.2);

4, 5, 6, 7р РСП - собственный номер УС.

Со стороны общей шины устройство обеспечивает обмен на программном уровне с внутренними регистрами устройства и обмен по прямому доступу в память.

Обмен ЭВМ с внутренними регистрами устройства начинается с выставления адреса регистра на шины адреса 19, который стробируется сигналом -СТРА, поступающим через приемник 74 на вход схемы 58 сравнения.

Адрес устройства задается пользователем посредством наборного поля 57 перемычек, размещенных в дешифраторе 1. При совпадении адреса регистра и кода, установленного в дешифраторе, а также при по- ступлениисигнала СТРАВ

вырабатывается сигнал -АДРОП, разрешающий работу элементов 66 и 71 в блоке 4 и дешифратора 90 в блоке 7.

Драйверы данных 61 и младших разрядов адреса 62 первого коммутатора 3 открываются сигналом -ВУДДА, поступающим из блока 7. Драйвер 63 старших разрядов адреса открывается только при обмене по прямому доступу в память сигналом -ППД.

Разряды А4 47 через драйвер адреса 62 поступают на дешифратор 90, который формирует сигналы выбора регистров. Информационные сигналы поступают по шине 20 и через драйверданных 61 поступают на внутреннюю шину данных ВДО - ВД7. Направление передачи адреса определяется сигналом РА, поступающим из блока 9 ПДП. При обмене на программном уровне адрес поступает в устройство, при обмене в режиме прямого доступа в память адрес выдается из устройства на ОШ.

Программа ЭВМ записывает управляющую информацию в регистр 2 номера ЭВМ и в регистр 17 режимов, программируются режимы работы преобразователя 10 последовательного кода в параллельный и обратно и блока 9 прямого доступа в память. В зависимости от содержимого регистра 17 режима и регистра режима преобразователя 10 устройство работает в одном из вы бранных режимов: Х.25, BSC, асинхронном.

Обмен по прямому доступу в память осуществляется следующим образом.

Обмен по ПДП начинается с возникновения одного из запросов ЗПДО, ЗПДГ, ЗПД2 в блоке 12 формирования запросов ПДП или запроса ЗПДЗ из шифратора 11 приоритетов. Если размаскирован соответствующий канал блока 9 ПДП, то блок 9 ПДП формирует ёигнал запроса захвата ЗЗХЕГ общей шины, поступающий на вход блока 5

ЗАХВАТА общей шины. Если общая шине находится в состоянии Не занято, то есть сигнал -ВхАГ находится в состоянии О, а сигнал -Зан - в состоянии 1, то блок 5 5 захвата общей шины формирует сигналы -ЗанВ и -ВхАМВ, которые через магистральные передатчики 73 и 80 блока 4 шин- ных формирователей управляющих сигналов выдаются на общую шину и пере0 водят ее в состояние Занято. Одновременно сигнал -ЗанВ поступает на вход блока 9 прямого доступа в память, разрешая дальнейшую его работу, а также открывает выходы регистра 2 номера ЭВМ, выдавая

5 на общую шину код той ЭВМ, которая будет работать с этим УС. Блок 9 ПДП формирует сигналы РА и -РА. которые соответственно в коммутаторе 3 задают направление передачи младших разрядов адреса АО - А7 из

0 УС на ОШ, а в блоке 4 шинных формирователей управляющих сигналов открывают буферный элемент 64, разрешают работу таймера 6. Затем блок 9 ПДП выдает по шинам данных ВД О - ВД 7 старший байт

5 адреса памяти и записывает его сигналом АД СТР в регистр 63 коммутатора 3. После этого блок 9 ПДП формирует один из сигна- лов подтверждения ПДП -ППДО - ППДЗ, которые объединяются по ИЛИ в

0 шифраторе 7 управляющих сигналов на элементах 94,96,93 и далее как сигналы -ППД и -ВУДДА открывают регистр 63, драйверы данных и адреса 61, 62 коммутатора 3. Выданный на ОШ адрес сопровождается

5 сигналом -СТРА, который формируется шинным формирователем 72. Блок 9 ПДП при чтении из ОЗУ ЭВМ формирует сигнал -ЧТЗУ, а затем сигнал -ЗПВ/В, ОЗУ выдает информацию на ОШ и подтверждает ее

0 достоверность сигналом -Гот, по которому на шинном формирователе 67 формируется сигнал -ЗПВ и информация записывается в преобразователь 10 последовательного кода в параллельный и обратно. При записи

5 информации в ОЗУ блок 9 ПДП формирует сигнал -ЧТВ/В, а затем -ЗПЗУ. Информация может считываться или из преобразо- вателя 10 последовательного кода в параллельный и обратно, или из регистра 8

0 системных прерываний, и по сигналу - ЗПЗУ, который через буферный элемент 64 блока 4 шинного формирователя управляющих сигналов поступает на ОШ как сигнал -ЗП, записывается в ОЗУ. Цикл обмена по

5 ПДП заканчивается при получении сигнала ГТ блоком 9 ПДП. Этот сигнал поступает из блока 7 шифратора управляющих сигналов с элемента 101 И-НЕ, на который поступают сигналы с двух направлений: с общей шины - через буферный элемент 64 (сигнал

ТотВ) или с выхода D-триггера регистра 15 состояния (сигнал -ТАТ).

Время обмена с ЭВМ по прямому доступу в память контролируется таймером б. В случае, если длительность цикла ПДП превышает предельно установленное время, то таймер 6 формирует сигнал ИТАТ, по ко- торому в регистре состояния формируется соответствующий признак, и обмен по ПДП принудительно завершается, Признак тайм-аут сбрасывается сигналом СТРМ, формируемом на элементе 100 по окончании программного чтения регистра системных прерываний. Остальные признаки регистра состояния сбрасываются раздельно по окончании чтения регистра системных прерываний в цикле ПДП; сбрасывается тот признак, который передан в ЭВМ, Для связи блока с удаленным абонентом используется как стартстопный метод передачи, так и синхронный, как биториен- тированные протоколы, так и синхронные. При стартстопном методе передачи знаки передаются как отдельные элементы и могут отделяться произвольными интервалами времени, В начале каждого знака вводится стартовая посылка, равная О, длительностью 1; 1,5. 2 бита. Для обеспечения перехода от предыдущего знака к последующему каждому знаку придается стоповая посылка, равная 1.

При синхронном методе передачи знаки передаются блоками, между которыми передаются синхросимволы - это байтори- ентированные протоколы.

В биториентированных протоколах, например, Х.25, HDLC, данные передаются блоками и разделятся синхросимволами, называемыми флагами (код ОПИЛО), а для отделения флагов от данных вводятся так называемые бит-стаффинги, т.е. после пяти 1 вставляется О. На приемнике бит-стаффинги должны удаляться из потока информации.

После установки устройства в исходное состояние аппаратным или программным способом устанавливается один из режимов работы: Х.25, BSC, асинхронный - в регистре режима. Затем программируется режим работы в преобразователе 10 параллельного кода в последовательный и обратно и в блоке 9 прямого доступа в память, в котором канал передатчика (2-й канал) замаскирован.

При работе в режимах Х.25, ВВС в преобразователе 10 программируется синхрон- ный режим передачи с внутренней синхронизацией по одному синхросимволу: 01111110 - в режиме Х.25 или 00010110 - в режиме 8SC. Данные и синхросимволы

выдаются из преобразователя 10 по цепи Выход на вход блока 14 предварительной обработки передаваемой информации, а затем по цепи Ц103Т на приемопередатчик

18 и далее на вход абонента.

Передача информации от ЭВМ к абоненту осуществляется следующим образом.

По окончании программирования пре0 образователя 10 на выходе ТПД формируется сигнал и на последовательном выходе выдается последовательность флаг. Сигнал ТПД поступает в блок 12 формирования запросов и через элемент задержки 120

5 и 121 взводит D-триггер 123, с выхода которого сигнал ЗПД2 поступает в блок 9 прямого доступа в память как запрос на прямой доступ по 2-му каналу. При передаче последнего бита флага в преобразова0 теле 10 формируется сигнал КПД, означающий, что буфер передатчика в преобразователе 10 пуст и может быть принят символ информации на передачу. Этот сигнал устанавливает признак прерывания в

5 регистре 15 состояний на D-триггере 175, сигнал -ТКПД поступает в шифратор 11 приоритетов, где формируется 3-битовый код прерывания, а также с выхода элемента 115 выдается сигнал ЗПДЗ, являющийся

0 запросом на прямой доступ по 3-му каналу блока 9 прямого доступа в память. Блок 9 прямого доступа в память организует цикл обращения к памяти той ЭВМ, чей номер записан в регистре 2 номера ЭВМ, по адре5 су, запрограммированному в счетчике адреса 3-го канала блока 9, и записывает в память ЭВМ содержимое регистра 8 системных прерываний. ЭВМ, определив, что получен признак КПД, записывает

0 дополнительно в регистр 17 режима бит РФБСТ и размаскирует 2-й канал блока 9 прямого доступа в память, записав в него слово режима с разрядом Д2-1. Далее блок 9 прямого доступа в память организует цикл

5 прямого доступа в память, считывает из памяти ЭВМ байт данных и записывает его в регистр передаваемых данных преобразователя 10 параллельного кода в последовательный и обратно. При этом в

0 преобразователе 10 сбрасывается сигнал ТПД. Перед началом передачи записанного байта данных в середине последнего бита флага вновь формируется сигнал ГПД, по которому взводится триггер 128, разре5 шающий формирование бит стаффинга в передаваемый поток информации. Подсчет передаваемых битое осуществляется на счетчике 129. При подсчете 5 единиц формируется сигнал -БСТ на элементе 130, который запрещает перепад сигнала СПД, т.е. на вход преобразователя 10 не поступает тактовая частота передачи. И тот же сигнал -БСТ через элемент 131 поступает на вход триггера 132 и переписывается на его выход по фронту сигнала Ц114В. При наличии 0м на выходе триггера 132 по фронту задержанной частоты Ц114В счетчик 129 сбрасывается. Далее циклы формирования бит-стаффингов в информации повторяются.

По окончании передачи последнего символа к абоненту счетчик передаваемых битов в блоке 9 прямого доступа в память исчерпывается и на выходе КС формируется сигнал, который устанавливает соот- ветствующий признак в регистре 15 состояний. Содержимое регистра 8 системных прерываний передается в ЭВМ, которая затем считывает слово состояния блока 9 прямого доступа в память, определяет от какого канала ПДП возник признак КС и если это канал передатчика, то он маскируется Запись данных в преобразователь 10 приостанавливается и при передаче последнего бита последнего записанного байта в преобразователе формируется сигнал КПД, который сбрасывает триггер 128. УСАПП111 автоматически выдает по выходу Вых ПД синхросимвол, являющийся кодом Флага. Сигнал КПД формирует в регистре 15 состояний признак прерывания, который передается в ЭВМ, и цикл передачи блоков данных повторяется.

Прием информации от абонента осуществляется следующим образом.

Сигналы 56 от абонента поступают в приемопередатчик 18 и из него, как информационные сигналы 52, поступают на коммутатор 16. С выхода коммутатора 16 сигналы 42 готовности абонента поступают на вход преобразователя 10 последовательного кода в параллельный и обратно, а сигналы Ц104ТВ и Ц115ТВ поступают соответственно на последовательный и тактовый входы блока 13 предварительной об- работки принимаемых данных. В асинхронном режиме работы тактовая частота приема -СЛМ формируется в блоке 13 на элементе 160 2И-2ИЛИ-НЕ. В режимах Х.25, BSC после программирования блоков и регистров УС тактовая частота -СПМ формируется на элементе 160 до тех пор, пока УСАПП 111 не войдет во внутренний синхронизм. При этом формируется сигнал ВС, который взводит Ь-триггер 169, и сиг- налом с элемента 170 блокируется формирование тактовой частоты -СПМ.

Рассмотрим далее прием и предварительную обработку принимаемых данных в блоке 13, реализованного в качестве примера, для приема и обработки информации, кратной байту, за исключением (в протоколе Х.25) обработки абортирующей последовательности и последовательностей Флаг следующего вида 011111101111110.

Информация в последовательном формате поступает на вход Ц104ТВ сдвигового регистра на элементах 139 и 140. Информация с выхода сдвигового регистра в параллельном формате дешифрируется на наличие последовательности синхросимвол на элементах 141-146. При дешифрации последовательности синхросимвол сигналом с выхода элемента 161 взводится D-триггер 162, разрешающий работу счетчика 164. Счетчик 164 досчитывает до 7 и если с выхода элемента 143 поступает на вход элемента 165 сигнал 1, то на его выходе появляется сигнал, сбрасывающий триггер 162 и счетчик 164. В этом же такте триггер 162 вновь взводится и цикл повторяется. Если в сдвиговый регистр на элементах 139 и 140 поступает информация, отличающаяся от последовательности синхросимвол, то на выходе элемента 143 при счете 7 счетчика 164 отсутствует 1 и счетчик досчитывает до 8. По этому сигналу взводится триггер 168, означающий, что из линии связи принимается блок (пакет) данных, на выходе элемента 170 появляется 1, разрешающая формирование тактовой частоты приема -СПМ с элемента 170. По сигналу 8 со счетчика 164 на элементе 165 также формируется сигнал сброса триггера 162 и счетчика 164. Далее цикл приема информации повторяется, при этом счетчик 164 считает до 8. При получении от абонента последовательности синхросимвол на выходе элемента 143 формируется 1 и, при наличии сигнала на выходе 8 счетчика 164, триггер 168 сбрасывается, прекращается формирование тактовой частоты -СПМ и преобразователь 10 прекращает прием информации. По сбросу триггера 168 формируется сигнал -КК, который взводит триггер признака прерывания в регистре 15 состояний.

В режиме Х.25 выбрасывание бит-стаф- финга осуществляется следующим образом.

Счетчик 157 подсчитывает количество Г, поступающих на вход сигнал ВхПМ) преобразователя 10 последовательного кода в параллельный и обратно. При подсчете пяти 1 и при наличии на входе ВхПМ О на выходе элемента 160 формируется сигнал, блокирующий выдачу тактовой частоты -СПМ на один такт.

Если на вход ВхПМ поступило 7 Г, то с выхода элемента 159 выдается сигнал

АБП, который взводит соответствующий признак в регистре 15 состояний.

Признак конец кадра (сигнал -ТКК) переводит триггер 124 блока 12 формирования запросов ПДП в другое состояние. Состояние триггера 124 контролируется при чтении регистра 8 системных прерываний как идентификатор канала ПДП. В зависимости от состояния триггера 124 блока 12 запросы на прямой доступ к памяти поступают либо на 0-й канал блока 9 ПДП, либо на 1-й. Таким образом, выделенные из по тока информации смежные блоки данных передаются в ЭВМ по разным каналам блока 9 ПДП. Этим обеспечивается приоритет для принимаемых данных по отношению к передаваемым на уровне блоков данных. Такая организация приема данных наиболее эффективна при приеме коротких блоков данных, В этом случае требования ко времени перепрограммирования принявшего блок данных канала НДП менее жестки. Приоритет приемника над передатчиком по другим признакам прерываний обеспечивается шифратором приоритетов.

Раздельное применение в режимах Х.25 и HDLC разрядов РВБСТ, РФБСТ и СЫН обеспечивает дополнительные диагностические возможности блоков УС, работающих на прием и на передачу информации от абонента.

По сравнению с прототипом предлагаемое устройство сопряжения сокращает время обмена информацией абонента с ЭВМ и обеспечивает более высокую надежность за счет исключения из принимаемой от абонента избыточной информации и выделения границ блоков (пакетов) данных, за счет аппаратного формирования в устройстве необходимой избыточной информации, передаваемой к абоненту, за счет передачи по прямому доступу в память как информации, так и прерываний, за счет использования двух каналов прямого доступа в память для передачи в ЭВМ принимаемой информации, за счет установления прерываниям от приемника более высокого приоритета, чем от передатчика, за счет контроля времени обмена с ЭВМ по ПДП, что позволяет исключить зависания системы путем принудительного окончания операций обмена, превышающих предельно установленное время обмена УС с ЭВМ, за счет передачи одновременно с прерываниями собственного номера УС, за счет передачи при обмене с ЭВМ по ПДП номера ЭВМ, работающей с предлагаемым устройством сопряжения.

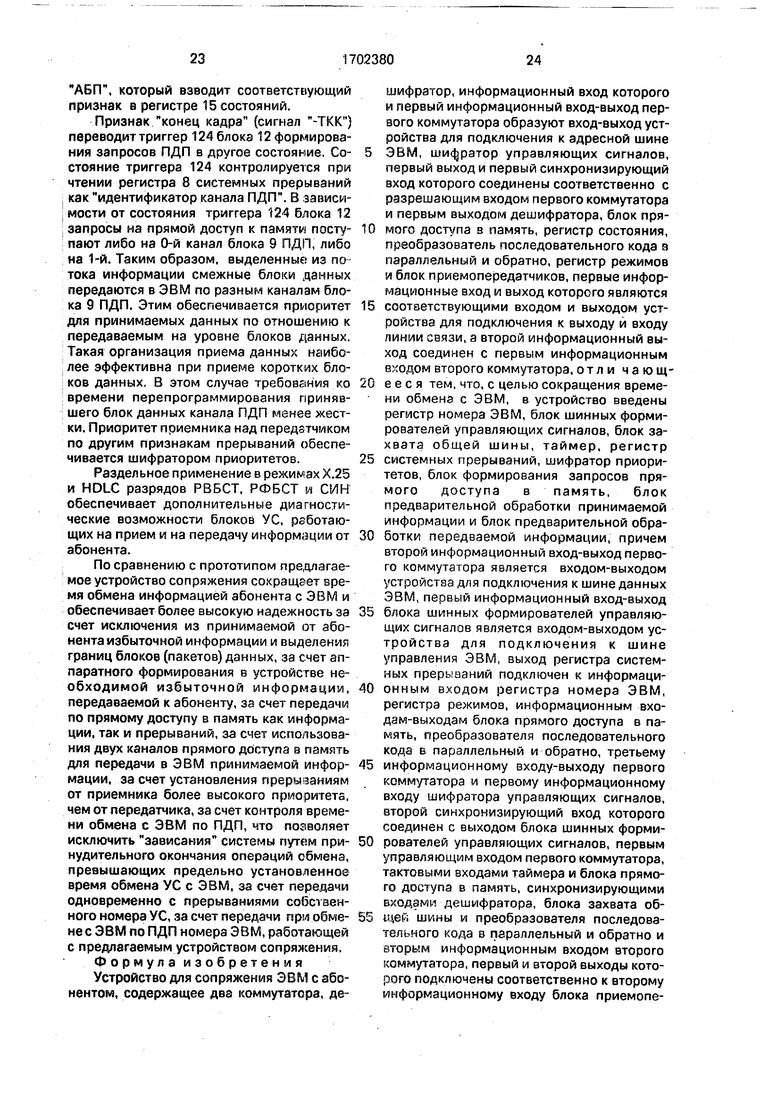

Формула изобретения

Устройство для сопряжения ЭВМ с абонентом, содержащее два коммутатора, дешифратор, информационный вход которого и первый информационный вход-выход первого коммутатора образуют вход-выход устройства для подключения к адресной шине

ЭВМ, шифратор управляющих сигналов, первый выход и первый синхронизирующий вход которого соединены соответственно с разрешающим входом первого коммутатора и первым выходом дешифратора, блок пря0 мого доступа в память, регистр состояния, преобразователь последовательного кода в параллельный и обратно, регистр режимов и блок приемопередатчиков, первые информационные вход и выход которого являются

5 соответствующими входом и выходом устройства для подключения к выходу и входу линии связи, а второй информационный выход соединен с первым информационным входом второго коммутатора, отли чающ0 е е с я тем, что, с целью сокращения времени обмена с ЭВМ, в устройство введены регистр номера ЭВМ, блок шинных формирователей управляющих сигналов, блок захвата общей шины, таймер, регистр

5 системных прерываний, шифратор приоритетов, блок формирования запросов прямого доступа в память, блок предварительной обработки принимаемой информации и блок предварительной обра0 ботки передваемой информации, причем второй информационный вход-выход первого коммутатора является входом-выходом устройства для подключения к шине данных ЭВМ, первый информационный вход-выход

5 блока шинных формирователей управляющих сигналов является входом-выходом устройства для подключения к шине управления ЭВМ, выход регистра системных прерываний подключен к информаци0 онным входом регистра номера ЭВМ, регистра режимов, информационным входам-выходам блока прямого доступа в память, преобразователя последовательного кода в параллельный и обратно, третьему

5 информационному входу-выходу первого коммутатора и первому информационному входу шифратора управляющих сигналов, второй синхронизирующий вход которого соединен с выходом блика шинных форми0 рователей управляющих сигналов, первым управляющим входом первого коммутатора, тактовыми входами таймера и блока прямого доступа в память, синхронизирующими входами дешифратора, блока захвата об5 щеР шины и преобразователя последовательного кода в параллельный и обратно и вторым информационным входом второго коммутатора, первый и второй выходы которого подключены соответственно к второму информационному входу блока приемопередатчиков и первым синхронизирующим входам блоков предварительной обработки принимаемой и предаваемой информации, разрешающие входы Я входы сброса которых соединены соответственно с выходом регистра режимов и первым выходом шифратора управляющих сигналов, вторым информационным входом подключенного к адресным входам-выходам первого коммутатора и блока прямого доступа в память и разрешающему входу преобразователя последовательного кода в параллельный и обратно, вход выборки, вход готовностей и информационный последовательный вход которого подключены соответственно к пер- вому выходу шифратора управляющих сигналов, третьему выходу второго коммутатора и первому выходу блока предварительной обработки принимаемой информации, а выход запроса данных - к третьему информационному входу второго коммутатора, упрвляющим входом соединенного с выходом регистра режимов и первым управляющим входом шифратора управляющих сигналов, третий информаци- онный вход блока приемопередатчиков и четвертый информационный F ход второго коммутатора соединены с первым выходом блока предварительной обработки передаваемых данных, входы готовности данных, второй синхронизирующий вход и второй выход которого подключены соответственно к выходам готовностей, последовательных данных и синхронизации и входу синхронизации передачи преобразователя последовательного кода в параллельный и обратно, соединенного выходами готовностей и синхронизации соответственно с входом готовности блока формирования запроса прямого доступа в память и с пер- вым информационным входом регистра состояния и вторым синхронизирующим входом блока предварительной обработки принимаемой информации, второй выход которого подключен к второму информаци- онному входу регистра состояния, третий и четвертый информационные входы которого соединены соответственно с выходом таймера и выходом конца счета блока прямого доступа в память, первый и второй входы запроса и выход подтверждения запроса которого соединены соответственно с первым и вторым выходами и входом подтверждения запроса блока формирования запросов прямого доступа к памяти, входы синхронизации сброса и третий выход которого подключены соответственно к выходу регистра состояния, первому выходу шифратора управляющих сигналов и первому информационному входу регистра системных прерываний, входы сброса и синхронизации и выход регистра состояния соединены соответственно с вторым и первым выходами и вторым управляющим входом шифратора управляющих сигналов, разрешающий вход которого подключен к выходу подтверждения запросов блока прямого доступа к памяти, синхронизирующий выход которого подключен к разрешающему входу таймера, второму управляющему входу первого коммутатора, информационному входу блока захвата общей шины и первому информационному входу блока шинных формирователей управляющих сигналов, первый, второй ч третий разрешающие входы и второй информационный вход которого соединены соответственно с первыми выходами шифратора управляющих сигналов и дешифратора и первым и вторым выходами захвата of щей шины, вход сброса которого подключен к выходу регистоа состояния и информационному входу шифратора приоритетов, соединенного первым выходом с вторым информаци- онным входом регистра системных прерываний, третий информационный вход и управляющий вход которого соединены соответственно с вторым выходом дешифратора и первым выходом шифратора управляющих сигналов, выход регистра номера ЭВМ соединен с входом-выходом устройства для подключения к адресной шине ЭВМ, а синхровход - с первым выходом шифратора управляющих сигналов, синхровходом регистра режимов и входом режима блока прямого доступе в память, третий запросный вход и управляющий вход-выход которого соединены соответственно с вторым выходом шифратора приоритетов и вторым информационным входом-выходом блока шинных формирователей управляющих сигналов, первый выход блока захвата общей шины подключен к разрешающему входу регистра номера ЭВМ и информационному входу блока прямого доступа к. памяти.

примечание: X - безразличное состояние разряда.

Таблице 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронной вычислительной машины с абонентами | 1976 |

|

SU642701A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения цифровой вычислительной машины с линиями связи | 1983 |

|

SU1166123A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения ЭВМ с внешним абонентом | 1988 |

|

SU1594553A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1283779A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения электронных вычислительных машин с интерфейсом типа общая шина с удаленными абонентами. Цель изобретения - сокращение времени обмена информацией с ЭВМ за счет исключения из принимаемой от абонента избыточной информации и выделения границ блоков (пакетов) данных, аппаратного формирования в устройстве необходимой избыточной информации, передаваемой к абоненту, передачи по прямому доступу в память как информации, так и прерываний, использования двух каналов прямого доступа в память для передачи в ЭВМ принимаемой информации, установления прерывания от приемника более высокого приоритета, чем от передатчика, таймирования обменов по прямому доступу в память, передачи одновременно с прерываниями собственного номера устройства сопряжения, передачи при обмене с ЭВМ по прямому доступу в память номера ЭВМ, работающей с данным устройством сопряжения. Это достигается тем, что в устройство, содержащее дешифратор, регистр режимов, первый и второй коммутаторы, блок приемопередатчиков, шифратор управляющих сигналов, преобразователь последовательного кода в параллельный и обратно, блок прямого доступа в память и регистр состояния, введены блоки предварительной обработки принимаемой и передаваемой информации, блок формирования запросов прямого доступа к памяти, шифратор приоритетов, регистр системных прерываний, таймер, регистр номера ЭВМ, блок шинных формирователей управляющих сигналов и блок захвата общей шины. 2 табл., 21 ил. сл с х| О ГО 00 ш о

Примечание. Х-безразличное состяние разряда.

Фцг.З

25

29 24

2д

-20

19

Фиг. U

21

J/Ъ

Фиг.д

Фиг. 7

Фиг. в

Фиг. 9

Фиг. 10

29

{

27 24

25

U 4f

4/

40

Д

Ф#г tf

47

)

45

Фиг. 12

to

TW

/K

#

o#

°0f o

.г

Ug

ftl

Й

з ff s

r4

Lm

mw

ОДР

.SLU

r-a

5§

iJr-Jm

qg№-|i

fowl Д

OrE

«ШД

J5

H /Ш

o

if

Sw

-o

We

-o

Л«7/ ,Г

-otf

08C20/.l

Фие. 16

56

Я

Фиг. 1д

52

55

Фиг. 19

ШВ1

-ЗАН

1

J.

HZL

33 X В М

I

. Фиг. 20

Фиг. 21

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения цифровой вычислительной машины с линиями связи | 1983 |

|

SU1166123A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1991-12-30—Публикация

1990-01-02—Подача