Изобретение относится к умпульсной технике и может быть использовано в автоматике и вычислительной технике для контроля импульсных последовательностей. .,

Известно устройство для контроля импульсных последовательностей, содержащее триггеры, входные и выходные шины lj.

Наиболее близким к предлага1емому по технической сущности является устройство для контроля последовательности чередования асинхронныхимпульсных сигналов, содержащее rt. каналов с триггером, двумя входными и одной выходной шиной в кг1ждом из каналов |2j.

Недостатком известных устройств является невысокая достоверность контроля.

Цель изобретения - повышение достоверности контроля.

Поставленная цель достигается ; тем, что в устройство для контроля последовательности чередования асинхронных импульсных сигналов, содер жащее н каналов с триггером, двумя входными и одной выходной шиной в ; каждом из каналов, в каждый канал введены второй триггер и вторая выходная шина, статичесК 1е входы установки в О всех триггеров соединены между собой и подключены к первой входно шине, динамический вход установки в 1 первого триггера каждого канала кроме первого подключен к прямому выходу второго триггера, динамическому входу установки в О первого триггера и второй выходной

10 шине предыдущего канала, при этом в каждом канале динамический вход установки в 1 второго триггера соединен с второй входной шиной, а динамический вход установки в О 15с инверсным выходом первого триггера и с первой выходной шиной.

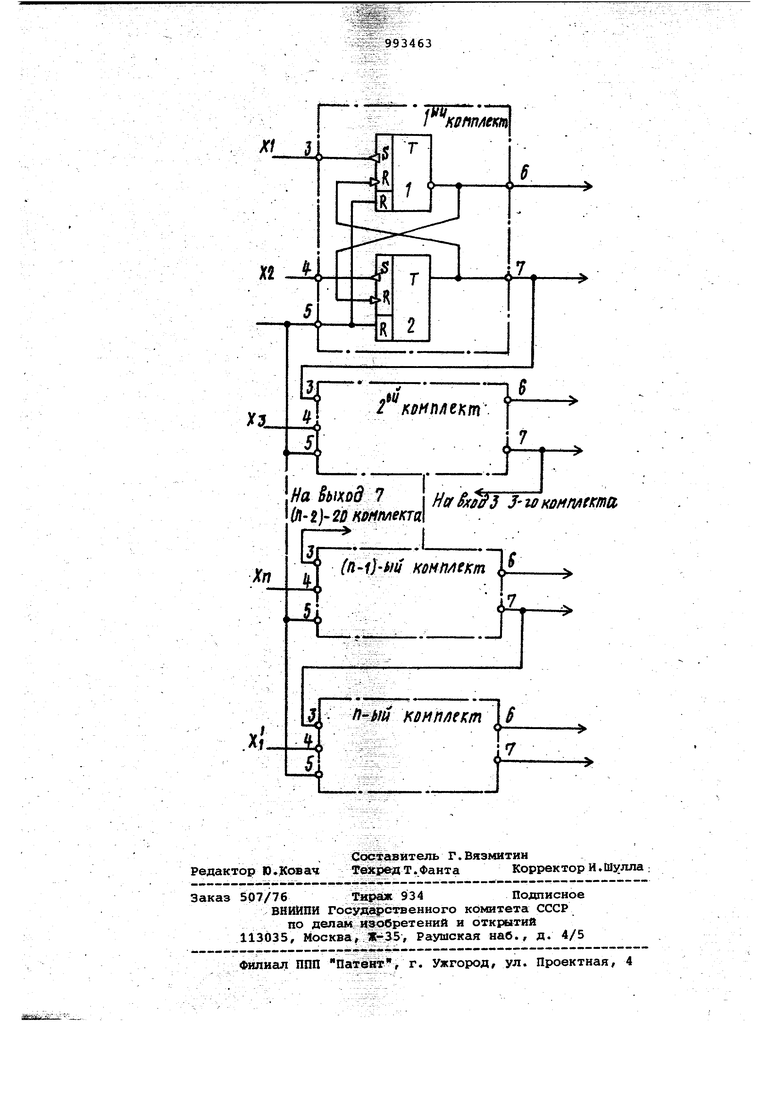

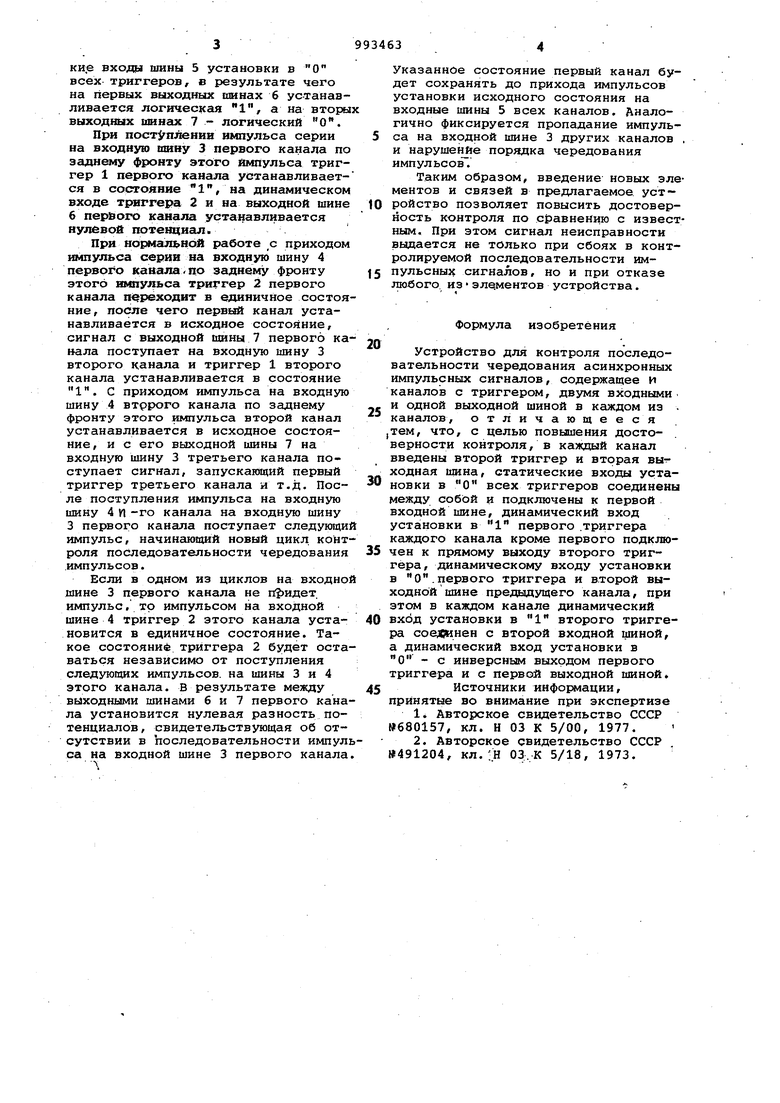

На чертеже приведена принципиальная электрическая схема предлагаемого устройства.

20

Устройство содержит и каналов с триггерами 1 и 2 в каждом канале и входными 3-5 и выхс дными б и 7 шина ми.

Устройство для контроля последо25вательности чередования асинхронных импульсных сигналов работает следующим образом.

Исходное состояние устройства задается, импульсом установки исходного

30 состояния, поступающим на статически,е входы шины 5 установки в О всех триггеров, в результате чего на первых выходных шинах 6 ус-танавливается логическгш 1, а на вторы выходных шинг1Х 7 - логический О.

При пост гплении импульса серии на входную шину 3 первого канала по заднему фронту этого импульса триггер 1 первого канала устанавливается в состояние 1, на динамическом входе триггера 2 и на выходной шине 6 пер&ого канала устанавливается нулевой потенциал.

При нормал ной работе с приходом импульса серии на входную шину 4 первого канала.по заднему Фронту этого импульса триггер 2 первого канала переходит в единичное состояние, после чего первый канал устанавливается в исходное состояние, сигнал с выходной шины 7 первого канала поступает на входную шину 3 второго канала и триггер 1 второго канала устанавливается в состояние 1. С приходом импульса на входную шину 4 втррого канала по заднему фронту этого импульса второй канал устанавливается в исходное состояние, и с его выходной шины 7 на входную шину 3 третьего канала поступает сигнал, запускающий первый триггер третьего канала и т.д. После поступления импульса на входную шину 4 П -го канала на входную шину 3 первого канала поступает следующи импульс, начинающий новый цикл контроля последовательности чередования .импульсов.

Если в одном из циклов на входно шине 3 первого канала не гфидет. импульс, то импульсом на входной шине 4 триггер 2 этого канала установится в единичное состояние. Такое состояние триггера 2 будет оставаться независимо от поступления следующих импульсов, на шины 3 и 4 этого канала. В результате между выходными шинами 6 и 7 первого канала установится нулевая разность потенциалов , свидетельствующая об отсутствии в последовательности импулса на входной шине 3 первого канала

Указанное состояние первый канал будет сохранять до прихода импульсов установки исходного состояния на входные шины 5 всех каналов. Диалогично фиксируется пропадание импульса на входной шине 3 других каналов . и нарушение порядка чередования импульсов.

Таким образом, введение новых элементов и связей в предлагаемое устройство позволяет повысить достоверность контроля по сравнению с известным. При этом сигнал неисправности выдается не только при сбоях в контролируемой последовательности импульсных сигналов, но и при отказе любого, изэлементов устройства.

Формула изобретения

Устройство для контроля последовательности чередования асинхронных импульсных сигналов, содержащее и каналов с триггером, двумя входными

и одной выходной шиной в каждом из . каналов, отличающееся ,тем, что, с целью повышения достоверности контроля, в каждый канал введены второй триггер и вторая вы ходная йшна, статические входы установки в О всех триггеров соединены между собой и подключены к первой входной шине, динамический вход установки в 1 первого .триггера каждого канала кроме первого подклю5 чен к прямому выходу второго триггера, динамическому входу установки в О.первого триггера и второй выходной шине предыдущего канала, при этом в каждом канале динамический

0 вход установки в 1 второго триггера сое;винен с второй входной шиной, а динамический вход установки в О - с инверсным выходом первого триггера и с первой выходной шиной

5 Источники информации,

принятые во внимание при экспертизе

1 Авторское свидетельство СССР №680157, кл. Н 03 К 5/00, 1977. 2. Авторское свидетельство СССР . 491204, кл.:Н 03.К 5/18, 1973.

XIИ

- Тта----I

Г xfffm/ifml

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля импульсных последовательностей | 1990 |

|

SU1795539A1 |

| Трехканальное резервированное устройство для синхронизации сигналов | 1983 |

|

SU1221769A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1984 |

|

SU1221771A1 |

| Синхронизатор импульсов | 1990 |

|

SU1746520A2 |

| Способ формирования частотно-импульсных сигналов датчика перемещения и устройство для его осуществления | 1976 |

|

SU905993A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Устройство для контроля последовательности чередования импульсных сигналов | 1985 |

|

SU1256184A1 |

| Устройство для контроля резервированного генератора | 1987 |

|

SU1457147A1 |

| Устройство управления трехфазным асинохронным электродвигателем криогенной системы с защитой от обрыва фазы | 1989 |

|

SU1791893A1 |

| Устройство для контроля последовательности чередования импульсов | 1987 |

|

SU1497729A1 |

.Xl.

1

5

} ймплект §

7

Авторы

Даты

1983-01-30—Публикация

1981-07-08—Подача